Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB OTG                                     |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                     |

| Number of I/O              | 65                                                                             |

| Program Memory Size        | 192KB (65.5K x 24)                                                             |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 80-TQFP                                                                        |

| Supplier Device Package    | 80-TQFP (12x12)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj192gb108-i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|          |                     | Pin Number     |                 |     |                 |                                          |

|----------|---------------------|----------------|-----------------|-----|-----------------|------------------------------------------|

| Function | 64-Pin<br>TQFP, QFN | 80-Pin<br>TQFP | 100-Pin<br>TQFP | I/O | Input<br>Buffer | Description                              |

| RF0      | 58                  | 72             | 87              | I/O | ST              | PORTF Digital I/O.                       |

| RF1      | 59                  | 73             | 88              | I/O | ST              |                                          |

| RF2      | —                   | 42             | 52              | I/O | ST              |                                          |

| RF3      | 33                  | 41             | 51              | I/O | ST              |                                          |

| RF4      | 31                  | 39             | 49              | I/O | ST              | -                                        |

| RF5      | 32                  | 40             | 50              | I/O | ST              |                                          |

| RF8      | —                   | 43             | 53              | I/O | ST              |                                          |

| RF12     | _                   |                | 40              | I/O | ST              | -                                        |

| RF13     | _                   | _              | 39              | I/O | ST              |                                          |

| RG0      | _                   | 75             | 90              | I/O | ST              | PORTG Digital I/O.                       |

| RG1      | _                   | 74             | 89              | I/O | ST              |                                          |

| RG2      | 37                  | 47             | 57              | I   | ST              |                                          |

| RG3      | 36                  | 46             | 56              | I   | ST              | -                                        |

| RG6      | 4                   | 6              | 10              | I/O | ST              |                                          |

| RG7      | 5                   | 7              | 11              | I/O | ST              | -                                        |

| RG8      | 6                   | 8              | 12              | I/O | ST              |                                          |

| RG9      | 8                   | 10             | 14              | I/O | ST              |                                          |

| RG12     | _                   | _              | 96              | I/O | ST              | -                                        |

| RG13     | _                   |                | 97              | I/O | ST              | -                                        |

| RG14     | _                   | _              | 95              | I/O | ST              |                                          |

| RG15     | _                   | _              | 1               | I/O | ST              | -                                        |

| RP0      | 16                  | 20             | 25              | I/O | ST              | Remappable Peripheral (input or output). |

| RP1      | 15                  | 19             | 24              | I/O | ST              |                                          |

| RP2      | 42                  | 54             | 68              | I/O | ST              |                                          |

| RP3      | 44                  | 56             | 70              | I/O | ST              | -                                        |

| RP4      | 43                  | 55             | 69              | I/O | ST              | -                                        |

| RP5      | _                   | 38             | 48              | I/O | ST              |                                          |

| RP6      | 17                  | 21             | 26              | I/O | ST              |                                          |

| RP7      | 18                  | 22             | 27              | I/O | ST              |                                          |

| RP8      | 21                  | 27             | 32              | I/O | ST              |                                          |

| RP9      | 22                  | 28             | 33              | I/O | ST              | -                                        |

| RP10     | 31                  | 39             | 49              | I/O | ST              | 1                                        |

| RP11     | 46                  | 58             | 72              | I/O | ST              | 1                                        |

| RP12     | 45                  | 57             | 71              | I/O | ST              | 1                                        |

| RP13     | 14                  | 18             | 23              | I/O | ST              | 1                                        |

| RP14     | 29                  | 35             | 43              | I/O | ST              | 1                                        |

| RP15     |                     | 43             | 53              | I/O | ST              | 1                                        |

| RP16     | 33                  | 41             | 51              | I/O | ST              | 1                                        |

| RP17     | 32                  | 40             | 50              | I/O | ST              | 1                                        |

| RP18     | 11                  | 15             | 20              | I/O | ST              | 1                                        |

| RP19     | 6                   | 8              | 12              | I/O | ST              | 1                                        |

#### **TABLE 1-4**: PIC24FJ256GB110 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

Legend: TTL = TTL input buffer ANA = Analog level input/output ST = Schmitt Trigger input buffer  $I^2C^{TM} = I^2C/SMBus$  input buffer

## 2.2 Power Supply Pins

### 2.2.1 DECOUPLING CAPACITORS

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A 0.1  $\mu$ F (100 nF), 10-20V capacitor is recommended. The capacitor should be a low-ESR device with a resonance frequency in the range of 200 MHz and higher. Ceramic capacitors are recommended.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is no greater than 0.25 inch (6 mm).

- Handling high-frequency noise: If the board is experiencing high-frequency noise (upward of tens of MHz), add a second ceramic type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to each primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible (e.g., 0.1  $\mu$ F in parallel with 0.001  $\mu$ F).

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB trace inductance.

### 2.2.2 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits including microcontrollers to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device, and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F.

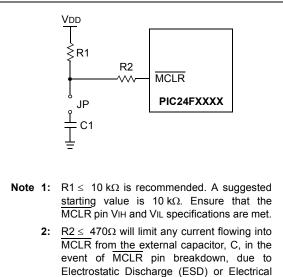

## 2.3 Master Clear (MCLR) Pin

The MCLR pin provides two specific device functions: device Reset, and device programming and debugging. If programming and debugging are not required in the end application, a direct connection to VDD may be all that is required. The addition of other components, to help increase the application's resistance to spurious Resets from voltage sags, may be beneficial. A typical configuration is shown in Figure 2-1. Other circuit designs may be implemented, depending on the application's requirements.

During programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the  $\overline{\text{MCLR}}$  pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R1 and C1 will need to be adjusted based on the application and PCB requirements. For example, it is recommended that the capacitor, C1, be isolated from the  $\overline{\text{MCLR}}$  pin during programming and debugging operations by using a jumper (Figure 2-2). The jumper is replaced for normal run-time operations.

Any components associated with the  $\overline{\text{MCLR}}$  pin should be placed within 0.25 inch (6 mm) of the pin.

### FIGURE 2-2: EXAMPLE OF MCLR PIN CONNECTIONS

Overstress (EOS). Ensure that the MCLR pin

VIH and VIL specifications are met.

### TABLE 4-28: SYSTEM REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7   | Bit 6  | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|--------|--------|---------|--------|--------|-------|-------|--------|--------|-------|---------------|

| RCON      | 0740 | TRAPR  | IOPUWR | _      | _      | _      | _      | СМ     | PMSLP  | EXTR    | SWR    | SWDTEN | WDTO  | SLEEP | IDLE   | BOR    | POR   | Note 1        |

| OSCCON    | 0742 | _      | COSC2  | COSC1  | COSC0  | _      | NOSC2  | NOSC1  | NOSC0  | CLKLOCK | IOLOCK | LOCK   | _     | CF    | POSCEN | SOSCEN | OSWEN | Note 2        |

| CLKDIV    | 0744 | ROI    | DOZE2  | DOZE1  | DOZE0  | DOZEN  | RCDIV2 | RCDIV1 | RCDIV0 | CPDIV1  | CPDIV0 | _      | _     | _     | _      | —      | _     | 0100          |

| OSCTUN    | 0748 | _      | _      | _      | _      |        | _      | _      | _      | _       |        | TUN5   | TUN4  | TUN3  | TUN2   | TUN1   | TUN0  | 0000          |

| REFOCON   | 074E | ROEN   | —      | ROSSLP | ROSEL  | RODIV3 | RODIV2 | RODIV1 | RODIV0 | -       |        | —      | —     | _     | _      |        |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: The Reset value of the RCON register is dependent on the type of Reset event. See Section 6.0 "Resets" for more information.

2: The Reset value of the OSCCON register is dependent on both the type of Reset event and the device configuration. See Section 8.0 "Oscillator Configuration" for more information.

#### TABLE 4-29: NVM REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4   | Bit 3       | Bit 2  | Bit 1  | Bit 0  | All<br>Resets   |

|-----------|------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|---------|-------------|--------|--------|--------|-----------------|

| NVMCON    | 0760 | WR     | WREN   | WRERR  | —      | _      | _      | _     | _     | -     | ERASE | _     | —       | NVMOP3      | NVMOP2 | NVMOP1 | NVMOP0 | 0000 <b>(1)</b> |

| NVMKEY    | 0766 | _      | _      | —      | —      | _      | _      | _     | _     |       |       | ١     | VMKEY R | egister<7:0 | >      |        |        | 0000            |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Reset value shown is for POR only. Value on other Reset states is dependent on the state of memory write or erase operations at the time of Reset.

#### TABLE 4-30: PMD REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8 | Bit 7  | Bit 6  | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|--------|-------|--------|--------|-------|--------|--------|--------|--------|--------|---------------|

| PMD1      | 0770 | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | -      | —      | _     | I2C1MD | U2MD   | U1MD  | SPI2MD | SPI1MD | —      | _      | ADC1MD | 0000          |

| PMD2      | 0772 | IC8MD  | IC7MD  | IC6MD  | IC5MD  | IC4MD  | IC3MD  | IC2MD  | IC1MD | OC8MD  | OC7MD  | OC6MD | OC5MD  | OC4MD  | OC3MD  | OC2MD  | OC1MD  | 0000          |

| PMD3      | 0774 | _      | _      | _      | _      | —      | CMPMD  | RTCCMD | PMPMD | CRCMD  | _      | _     | _      | U3MD   | I2C3MD | I2C2MD | _      | 0000          |

| PMD4      | 0776 | _      | _      | _      | _      | _      | _      | _      |       | _      | UPWMMD | U4MD  | _      | REFOMD | CTMUMD | LVDMD  | USB1MD | 0000          |

| PMD5      | 0778 | —      | _      | —      | _      | _      | —      | —      | IC9MD | _      | —      | —     | —      | —      | _      | _      | OC9MD  | 0000          |

| PMD6      | 077A | _      |        | _      | _      |        |        | _      | _     |        | _      | _     |        |        | —      | _      | SPI3MD | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

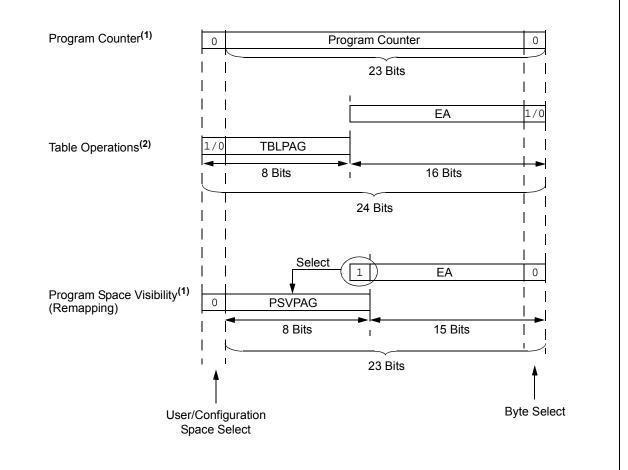

### TABLE 4-31: PROGRAM SPACE ADDRESS CONSTRUCTION

|                          | Access        |                              | Prograi   | m Space A           | Adress          |                    |  |  |  |

|--------------------------|---------------|------------------------------|-----------|---------------------|-----------------|--------------------|--|--|--|

| Access Type              | Space         | <23>                         | <22:16>   | <15>                | <14:1>          | <0>                |  |  |  |

| Instruction Access       | User          | 0                            |           |                     | 0               |                    |  |  |  |

| (Code Execution)         |               | 0xx xxxx xxxx xxxx xxxx xxx0 |           |                     |                 |                    |  |  |  |

| TBLRD/TBLWT              | User          | TB                           | LPAG<7:0> |                     | Data EA<15:0>   |                    |  |  |  |

| (Byte/Word Read/Write)   |               | 02                           | xxx xxxx  | XXXX XXXX XXXX XXXX |                 |                    |  |  |  |

|                          | Configuration | TB                           | LPAG<7:0> | Data EA<15:0>       |                 |                    |  |  |  |

|                          |               | 1:                           | xxx xxxx  |                     |                 |                    |  |  |  |

| Program Space Visibility | User          | 0 PSVPAG<7                   |           | 7:0> Data EA<14     |                 | :0> <sup>(1)</sup> |  |  |  |

| (Block Remap/Read)       |               | 0                            | XXXX XXX  | κx                  | x xxx xxxx xxxx |                    |  |  |  |

**Note 1:** Data EA<15> is always '1' in this case, but is not used in calculating the program space address. Bit 15 of the address is PSVPAG<0>.

### FIGURE 4-5: DATA ACCESS FROM PROGRAM SPACE ADDRESS GENERATION

- **Note 1:** The LSb of program space addresses is always fixed as '0' in order to maintain word alignment of data in the program and data spaces.

- **2:** Table operations are not required to be word-aligned. Table read operations are permitted in the configuration memory space.

## 5.2 RTSP Operation

The PIC24F Flash program memory array is organized into rows of 64 instructions or 192 bytes. RTSP allows the user to erase blocks of eight rows (512 instructions) at a time and to program one row at a time. It is also possible to program single words.

The 8-row erase blocks and single row write blocks are edge-aligned, from the beginning of program memory, on boundaries of 1536 bytes and 192 bytes, respectively.

When data is written to program memory using TBLWT instructions, the data is not written directly to memory. Instead, data written using table writes is stored in holding latches until the programming sequence is executed.

Any number of TBLWT instructions can be executed and a write will be successfully performed. However, 64 TBLWT instructions are required to write the full row of memory.

To ensure that no data is corrupted during a write, any unused addresses should be programmed with FFFFFFh. This is because the holding latches reset to an unknown state, so if the addresses are left in the Reset state, they may overwrite the locations on rows which were not rewritten.

The basic sequence for RTSP programming is to set up a Table Pointer, then do a series of TBLWT instructions to load the buffers. Programming is performed by setting the control bits in the NVMCON register.

Data can be loaded in any order and the holding registers can be written to multiple times before performing a write operation. Subsequent writes, however, will wipe out any previous writes.

**Note:** Writing to a location multiple times without erasing is *not* recommended.

All of the table write operations are single-word writes (2 instruction cycles), because only the buffers are written. A programming cycle is required for programming each row.

### 5.3 JTAG Operation

The PIC24F family supports JTAG boundary scan. Boundary scan can improve the manufacturing process by verifying pin-to-PCB connectivity.

### 5.4 Enhanced In-Circuit Serial Programming

Enhanced In-Circuit Serial Programming uses an on-board bootloader, known as the program executive, to manage the programming process. Using an SPI data frame format, the program executive can erase, program and verify program memory. For more information on Enhanced ICSP, see the device programming specification.

### 5.5 Control Registers

There are two SFRs used to read and write the program Flash memory: NVMCON and NVMKEY.

The NVMCON register (Register 5-1) controls which blocks are to be erased, which memory type is to be programmed and when the programming cycle starts.

NVMKEY is a write-only register that is used for write protection. To start a programming or erase sequence, the user must consecutively write 55h and AAh to the NVMKEY register. Refer to **Section 5.6 "Programming Operations"** for further details.

### 5.6 Programming Operations

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. During a programming or erase operation, the processor stalls (waits) until the operation is finished. Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

### 5.6.2 PROGRAMMING A SINGLE WORD OF FLASH PROGRAM MEMORY

If a Flash location has been erased, it can be programmed using table write instructions to write an instruction word (24-bit) into the write latch. The TBLPAG register is loaded with the 8 Most Significant Bytes of the Flash address. The TBLWTL and TBLWTH instructions write the desired data into the write latches and specify the lower 16 bits of the program memory address to write to. To configure the NVMCON register for a word write, set the NVMOP bits (NVMCON<3:0>) to '0011'. The write is performed by executing the unlock sequence and setting the WR bit, as shown in Example 5-7. An equivalent procedure in C, using the MPLAB C30 compiler and built-in hardware functions, is shown in Example 5-8.

### EXAMPLE 5-7: PROGRAMMING A SINGLE WORD OF FLASH PROGRAM MEMORY (ASSEMBLY LANGUAGE CODE)

| ; Setup a p | pointer to data Program Memory       |                                                        |

|-------------|--------------------------------------|--------------------------------------------------------|

| MOV         | <pre>#tblpage(PROG_ADDR), W0</pre>   | i                                                      |

| MOV         | W0, TBLPAG                           | ;Initialize PM Page Boundary SFR                       |

| MOV         | <pre>#tbloffset(PROG_ADDR), W0</pre> | ;Initialize a register with program memory address     |

| MOV         | #LOW_WORD, W2                        | ;                                                      |

| MOV         | #HIGH_BYTE, W3                       | ;                                                      |

| TBLWTL      | W2, [W0]                             | ; Write PM low word into program latch                 |

| TBLWTH      | W3, [W0++]                           | ; Write PM high byte into program latch                |

| ; Setup NVN | MCON for programming one word t      | to data Program Memory                                 |

| MOV         | #0x4003, W0                          | ;                                                      |

| MOV         | W0, NVMCON                           | ; Set NVMOP bits to 0011                               |

| DISI        | #5                                   | ; Disable interrupts while the KEY sequence is written |

| MOV         | #0x55, W0                            | ; Write the key sequence                               |

| MOV         | W0, NVMKEY                           |                                                        |

| MOV         | #0xAA, W0                            |                                                        |

| MOV         | W0, NVMKEY                           |                                                        |

| BSET        | NVMCON, #WR                          | ; Start the write cycle                                |

| NOP         |                                      | ; Insert two NOPs after the erase                      |

| NOP         |                                      | ; Command is asserted                                  |

### EXAMPLE 5-8: PROGRAMMING A SINGLE WORD OF FLASH PROGRAM MEMORY (C LANGUAGE CODE)

```

// C example using MPLAB C30

unsigned int offset;

unsigned long progAddr = 0xXXXXXX;

// Address of word to program

unsigned int progDataL = 0xXXXX;

// Data to program lower word

unsigned char progDataH = 0xXX;

// Data to program upper byte

//Set up NVMCON for word programming

NVMCON = 0 \times 4003;

// Initialize NVMCON

//Set up pointer to the first memory location to be written

// Initialize PM Page Boundary SFR

TBLPAG = progAddr>>16;

offset = progAddr & 0xFFFF;

// Initialize lower word of address

//Perform TBLWT instructions to write latches

// Write to address low word

__builtin_tblwtl(offset, progDataL);

__builtin_tblwth(offset, progDataH);

// Write to upper byte

asm("DISI #5");

// Block interrupts with priority < 7</pre>

// for next 5 instructions

__builtin_write_NVM();

// C30 function to perform unlock

// sequence and set WR

```

| U-0                | R/W-1                                                                 | R/W-0                                                                                                                    | R/W-0                       | U-0               | R/W-1            | R/W-0           | R/W-0  |

|--------------------|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-----------------------------|-------------------|------------------|-----------------|--------|

| _                  | T2IP2                                                                 | T2IP1                                                                                                                    | T2IP0                       | _                 | OC2IP2           | OC2IP1          | OC2IP0 |

| bit 15             |                                                                       |                                                                                                                          |                             |                   |                  |                 | bit    |

| U-0                | R/W-1                                                                 | R/W-0                                                                                                                    | R/W-0                       | U-0               | U-0              | U-0             | U-0    |

| _                  | IC2IP2                                                                | IC2IP1                                                                                                                   | IC2IP0                      | —                 | _                | _               | _      |

| bit 7              |                                                                       |                                                                                                                          |                             |                   |                  |                 | bit    |

| Legend:            |                                                                       |                                                                                                                          |                             |                   |                  |                 |        |

| R = Readab         | le bit                                                                | W = Writable                                                                                                             | bit                         | U = Unimplei      | mented bit, read | l as '0'        |        |

| -n = Value a       | t POR                                                                 | '1' = Bit is set                                                                                                         |                             | '0' = Bit is cle  | ared             | x = Bit is unkr | nown   |

| bit 11<br>bit 10-8 | •<br>•<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>OC2IP<2:0>: | pt is priority 7 (I<br>pt is priority 1<br>pt source is dis<br>ated: Read as '(<br>c Output Compa<br>pt is priority 7 (I | abled<br>)'<br>re Channel 2 | Interrupt Priorit | ty bits          |                 |        |

| bit 7<br>bit 6-4   | Unimplemen<br>IC2IP<2:0>:                                             | pt source is dis<br>ited: Read as '(<br>Input Capture C<br>pt is priority 7 (I                                           | )'<br>Shannel 2 Inte        |                   | S                |                 |        |

| bit 3-0            | 000 = Interru                                                         | pt is priority i<br>pt source is dis<br>ited: Read as '(                                                                 |                             |                   |                  |                 |        |

### REGISTER 7-18: IPC1: INTERRUPT PRIORITY CONTROL REGISTER 1

### REGISTER 10-21: RPINR29: PERIPHERAL PIN SELECT INPUT REGISTER 29

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   |     | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| —     | —   | SS3R5 | SS3R4 | SS3R3 | SS3R2 | SS3R1 | SS3R0 |

| bit 7 |     |       |       |       |       |       | bit 0 |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-6 Unimplemented: Read as '0'

bit 5-0 SS3R<5:0>: Assign SPI3 Slave Select Input (SS31IN) to Corresponding RPn or RPIn Pin bits

### REGISTER 10-22: RPOR0: PERIPHERAL PIN SELECT OUTPUT REGISTER 0

| U-0                                | U-0   | R/W-0          | R/W-0 | R/W-0                                   | R/W-0            | R/W-0    | R/W-0 |  |

|------------------------------------|-------|----------------|-------|-----------------------------------------|------------------|----------|-------|--|

| _                                  | _     | RP1R5          | RP1R4 | RP1R3                                   | RP1R2            | RP1R1    | RP1R0 |  |

| bit 15                             |       |                |       | ·                                       |                  | •        | bit 8 |  |

|                                    |       |                |       |                                         |                  |          |       |  |

| U-0                                | U-0   | R/W-0          | R/W-0 | R/W-0                                   | R/W-0            | R/W-0    | R/W-0 |  |

| _                                  | _     | RP0R5          | RP0R4 | RP0R3                                   | RP0R2            | RP0R1    | RP0R0 |  |

| bit 7                              |       |                |       | ·                                       |                  | •        | bit 0 |  |

|                                    |       |                |       |                                         |                  |          |       |  |

| Legend:                            |       |                |       |                                         |                  |          |       |  |

| R = Readable                       | e bit | W = Writable I | oit   | U = Unimplem                            | nented bit, read | l as '0' |       |  |

| -n = Value at POR '1' = Bit is set |       |                |       | '0' = Bit is cleared x = Bit is unknown |                  |          |       |  |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP1R<5:0>:** RP1 Output Pin Mapping bits Peripheral output number n is assigned to pin, RP1 (see Table 10-3 for peripheral function numbers)

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **RP0R<5:0>:** RP0 Output Pin Mapping bits Peripheral output number n is assigned to pin, RP0 (see Table 10-3 for peripheral function numbers)

### REGISTER 10-25: RPOR3: PERIPHERAL PIN SELECT OUTPUT REGISTER 3

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|-------|-------|-------|

| —      | —   | RP7R5 | RP7R4 | RP7R3 | RP7R2 | RP7R1 | RP7R0 |

| bit 15 |     |       |       |       |       |       | bit 8 |

|        |     |       |       |       |       |       |       |

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| —      | —   | RP6R5 | RP6R4 | RP6R3 | RP6R2 | RP6R1 | RP6R0 |

| bit 7  |     |       |       |       |       |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                          |

|-----------|-----------------------------------------------------------------------------------------------------|

| bit 13-8  | RP7R<5:0>: RP7 Output Pin Mapping bits                                                              |

|           | Peripheral output number n is assigned to pin, RP7 (see Table 10-3 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                          |

| bit 5-0   | RP6R<5:0>: RP6 Output Pin Mapping bits                                                              |

|           | Peripheral output number n is assigned to pin, RP6 (see Table 10-3 for peripheral function numbers) |

### REGISTER 10-26: RPOR4: PERIPHERAL PIN SELECT OUTPUT REGISTER 4

| U-0             | U-0 | R/W-0            | R/W-0 | R/W-0                                   | R/W-0            | R/W-0  | R/W-0 |

|-----------------|-----|------------------|-------|-----------------------------------------|------------------|--------|-------|

| —               | —   | RP9R5            | RP9R4 | RP9R3                                   | RP9R2            | RP9R1  | RP9R0 |

| bit 15          |     |                  |       |                                         |                  |        | bit 8 |

|                 |     |                  |       |                                         |                  |        |       |

| U-0             | U-0 | R/W-0            | R/W-0 | R/W-0                                   | R/W-0            | R/W-0  | R/W-0 |

| —               | _   | RP8R5            | RP8R4 | RP8R3                                   | RP8R2            | RP8R1  | RP8R0 |

| bit 7           | •   |                  |       |                                         |                  |        | bit 0 |

|                 |     |                  |       |                                         |                  |        |       |

| Legend:         |     |                  |       |                                         |                  |        |       |

| R = Readable    | bit | W = Writable b   | oit   | U = Unimplem                            | nented bit, read | as '0' |       |

| -n = Value at I | POR | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |                  |        | nown  |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP9R<5:0>:** RP9 Output Pin Mapping bits Peripheral output number n is assigned to pin, RP9 (see Table 10-3 for peripheral function numbers)

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **RP8R<5:0>:** RP8 Output Pin Mapping bits Peripheral output number n is assigned to pin, RP8 (see Table 10-3 for peripheral function numbers)

| U-0          | U-0                             | U-0                                    | U-0             | U-0                 | U-0              | U-0                | U-0           |

|--------------|---------------------------------|----------------------------------------|-----------------|---------------------|------------------|--------------------|---------------|

| —            | —                               | —                                      | —               | —                   | —                | —                  |               |

| bit 15       |                                 |                                        |                 |                     |                  |                    | bit           |

| R-x, HSC     | R-x, HSC                        | R/W-0                                  | R/W-0           | R/W-0               | R/W-0            | R/W-0              | R/W-0         |

| JSTATE       | SE0                             | TOKBUSY                                | USBRST          | HOSTEN              | RESUME           | PPBRST             | SOFEN         |

| bit 7        | 3EU                             | TURBUST                                | USDRST          | HUSTEN              | RESUME           | FFDROI             | bit           |

|              |                                 |                                        |                 |                     |                  |                    |               |

| Legend:      |                                 | U = Unimplem                           | ented bit, read | 1 as '0'            |                  |                    |               |

| R = Readab   | le bit                          | W = Writable t                         | bit             | HSC = Hardw         | are Settable/C   | learable bit       |               |

| -n = Value a | t POR                           | '1' = Bit is set                       |                 | '0' = Bit is clea   | ared             | x = Bit is unkn    | iown          |

|              |                                 |                                        |                 |                     |                  |                    |               |

| bit 15-8     | -                               | ited: Read as '0                       |                 |                     |                  |                    |               |

| bit 7        |                                 | e Differential Re                      |                 | •                   |                  |                    | <b>D</b>      |

|              | 1 = J state (0<br>0 = No J stat | differential '0' in te detected        | low speed, dif  | terential '1' in fi | ull speed) dete  | cted on the US     | В             |

| oit 6        | SE0: Live Sir                   | ngle-Ended Zero                        | Flag bit        |                     |                  |                    |               |

|              |                                 | nded zero active                       |                 | ous                 |                  |                    |               |

|              | •                               | e-ended zero de                        |                 |                     |                  |                    |               |

| bit 5        |                                 | oken Busy Statu                        |                 |                     | <b>•</b> • •     |                    |               |

|              |                                 | eing executed by<br>being executed     |                 | dule in On-The-     | Go state         |                    |               |

| bit 4        |                                 | dule Reset bit                         | •               |                     |                  |                    |               |

|              |                                 | set has been ge                        | nerated; for so | oftware Reset,      | application mu   | st set this bit fo | or 50 ms, the |

|              | clear it                        | Ū                                      | ,               | ,                   |                  |                    | ,             |

|              |                                 | set terminated                         |                 |                     |                  |                    |               |

| bit 3        |                                 | st Mode Enable                         |                 |                     |                  | ·                  |               |

|              |                                 | t capability enal<br>t capability disa |                 | is on D+ and D      | - are activated  | in hardware        |               |

| bit 2        |                                 | esume Signaling                        |                 |                     |                  |                    |               |

|              |                                 | signaling activat                      |                 | ust set bit for 10  | ) ms and then cl | ear to enable re   | mote wake-u   |

|              | 0 = Resume                      | signaling disabl                       | ed              |                     |                  |                    |               |

| bit 1        |                                 | ig-Pong Buffers                        |                 |                     |                  |                    |               |

|              |                                 | Il Ping-Pong But<br>ng Buffer Pointe   |                 | the EVEN BD         | banks            |                    |               |

|              |                                 |                                        |                 |                     |                  |                    |               |

| bit 0        |                                 |                                        |                 |                     |                  |                    |               |

| bit 0        | SOFEN: Star                     | t-Of-Frame Ena<br>Frame token se       | ble bit         | millisecond         |                  |                    |               |

### REGISTER 18-11: U1SOF: USB OTG START-OF-TOKEN THRESHOLD REGISTER (HOST MODE ONLY)

| bit 15 |     |     |     |     |     |     | bit 8 |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      |     | _   |     | —   | —   | _   |       |

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|       |      |      |      | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|------|------|------|-------|-------|-------|-------|

| CNT7  | CNT6 | CNT5 | CNT4 | CNT3  | CNT2  | CNT1  | CNT0  |

| bit 7 |      |      |      |       |       |       | bit 0 |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-8 Unimplemented: Read as '0'

bit 7-0

CNT<7:0>: Start-Of-Frame Size bits;

Value represents 10 + (packet size of n bytes). For example:

0100 1010 = 64-byte packet

0010 1010 = **32-byte packet**

0001 0010 = 8-byte packet

### REGISTER 18-12: U1CNFG1: USB CONFIGURATION REGISTER 1

| U-0    | U-0                                                           | U-0 | U-0   | U-0 | U-0 | U-0   | U-0   |

|--------|---------------------------------------------------------------|-----|-------|-----|-----|-------|-------|

| —      | —                                                             | —   | _     | —   | —   | —     | —     |

| bit 15 |                                                               |     |       | •   |     |       | bit 8 |

|        |                                                               |     |       |     |     |       |       |

| R/W-0  | R/W-0                                                         | U-0 | R/W-0 | U-0 | U-0 | R/W-0 | R/W-0 |

|        | $\mu = \mu =$ |     |       |     |     |       |       |

|   | R/W-0 | R/W-0                 | U-0 | R/W-0   | U-0 | U-0 | R/W-0 | R/W-0 |

|---|-------|-----------------------|-----|---------|-----|-----|-------|-------|

|   | UTEYE | UOEMON <sup>(1)</sup> | _   | USBSIDL | —   | _   | PPB1  | PPB0  |

| ł | oit 7 |                       |     |         |     |     |       | bit 0 |

| Logond     |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                 |                    |

|------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|--------------------|

| Legend:    |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                 |                    |

| R = Reada  | ble bit  | W = Writable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | U = Unimplemented bit           | , read as '0'      |

| -n = Value | at POR   | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | '0' = Bit is cleared            | x = Bit is unknown |

|            |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                 |                    |

| bit 15-8   | Unimple  | mented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                 |                    |

| bit 7      | UTEYE:   | USB Eye Pattern Test Enabl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | e bit                           |                    |

|            | •        | pattern test enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                 |                    |

|            |          | pattern test disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                 |                    |

| bit 6      |          | 1: USB OE Monitor Enable t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                 |                    |

|            |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | rvals during which the D+/D- li | nes are driving    |

|            | 0 = OE s | signal inactive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                 |                    |

| bit 5      | Unimple  | mented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                 |                    |

| bit 4      | USBSIDI  | .: USB OTG Stop in Idle Mo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | de bit                          |                    |

|            |          | ontinue module operation whether the second s |                                 |                    |

|            | 0 = Cont | inue module operation in Idl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | e mode                          |                    |

| bit 3-2    | Unimple  | mented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                 |                    |

| bit 1-0    | PPB<1:0  | >: Ping-Pong Buffers Config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | uration bit                     |                    |

|            | 11 = EVE | N/ODD ping-pong buffers e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | nabled for Endpoints 1 to 15    |                    |

|            |          | EN/ODD ping-pong buffers e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | •                               |                    |

|            |          | N/ODD ping-pong buffer en                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                 |                    |

|            | 00 = EVE | EN/ODD ping-pong buffers d                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | isabled                         |                    |

|            |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                 |                    |

Note 1: This bit is only active when the UTRDIS bit (U1CNFG2<0>) is set.

NOTES:

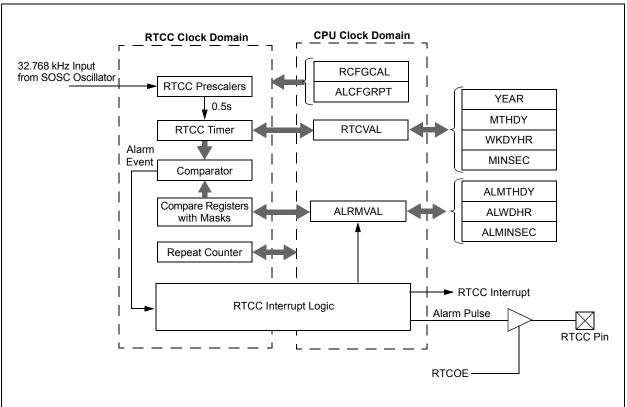

## 20.0 REAL-TIME CLOCK AND CALENDAR (RTCC)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "PIC24F Family Reference Manual", Section 29. "Real-Time Clock and Calendar (RTCC)" (DS39696).

The Real-Time Clock and Calendar (RTCC) provides on-chip, hardware-based clock and calendar functionality with little or no CPU overhead. It is intended for applications where accurate time must be maintained for extended periods with minimal CPU activity and with limited power resources, such as battery-powered applications. Key features include:

- Time data in hours, minutes and seconds, with a granularity of one-half second

- 24-hour format (Military Time) display option

- Calendar data as date, month and year

- Automatic, hardware-based day of the week and leap year calculations for dates from 2000 through 2099

- Time and calendar data in BCD format for \_compact firmware

- Highly configurable alarm function

- External output pin with selectable alarm signal or seconds "tick" signal output

- · User calibration feature with auto-adjust

A simplified block diagram of the module is shown in Figure 20-1. The SOSC and RTCC will both remain running while the device is held in Reset with MCLR and will continue running after MCLR is released.

### FIGURE 20-1: RTCC BLOCK DIAGRAM

#### REGISTER 26-1: CW1: FLASH CONFIGURATION WORD 1 (CONTINUED)

bit 3-0 **WDTPS<3:0>:** Watchdog Timer Postscaler Select bits

1111 = 1:32,768 1110 = 1:16,384 1101 = 1:8,192 1100 = 1:4,096 1011 = 1:2,048 1010 = 1:1,024 1001 = 1:512 1000 = 1:256 0111 = 1:128 0110 = 1:64 0101 = 1:32 0100 = 1:16 0011 = 1:8 0010 = 1:4 0001 = 1:2 0000 = 1:1

**Note 1:** The JTAGEN bit can only be modified using In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>). It cannot be modified while programming the device through the JTAG interface.

| TABLE 28-2: | INSTRUCTION SET OVERVIEW | (CONTINUED) |

|-------------|--------------------------|-------------|

|             |                          |             |

| Assembly<br>Mnemonic |                 | Assembly Syntax   | Description                             | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|----------------------|-----------------|-------------------|-----------------------------------------|---------------|----------------|--------------------------|

| PWRSAV               | PWRSAV          | #lit1             | Go into Sleep or Idle mode              | 1             | 1              | WDTO, Sleep              |

| RCALL                | RCALL           | Expr              | Relative Call                           | 1             | 2              | None                     |

|                      | RCALL           | Wn                | Computed Call                           | 1             | 2              | None                     |

| REPEAT               | REPEAT          | #lit14            | Repeat Next Instruction lit14 + 1 times | 1             | 1              | None                     |

|                      | REPEAT          | Wn                | Repeat Next Instruction (Wn) + 1 times  | 1             | 1              | None                     |

| RESET                | RESET           |                   | Software Device Reset                   | 1             | 1              | None                     |

| RETFIE               | RETFIE          |                   | Return from Interrupt                   | 1             | 3 (2)          | None                     |

| RETLW                | RETLW           | #lit10,Wn         | Return with Literal in Wn               | 1             | 3 (2)          | None                     |

| RETURN               | RETURN          |                   | Return from Subroutine                  | 1             | 3 (2)          | None                     |

| RLC                  | RLC             | f                 | f = Rotate Left through Carry f         | 1             | 1              | C, N, Z                  |

|                      | RLC             | f,WREG            | WREG = Rotate Left through Carry f      | 1             | 1              | C, N, Z                  |

|                      | RLC             | Ws,Wd             | Wd = Rotate Left through Carry Ws       | 1             | 1              | C, N, Z                  |

| RLNC                 | RLNC            | f                 | f = Rotate Left (No Carry) f            | 1             | 1              | N, Z                     |

|                      | RLNC            | f,WREG            | WREG = Rotate Left (No Carry) f         | 1             | 1              | N, Z                     |

|                      | RLNC            | Ws,Wd             | Wd = Rotate Left (No Carry) Ws          | 1             | 1              | N, Z                     |

| RRC                  | RRC             | f                 | f = Rotate Right through Carry f        | 1             | 1              | C, N, Z                  |

|                      | RRC             | f,WREG            | WREG = Rotate Right through Carry f     | 1             | 1              | C, N, Z                  |

|                      | RRC             | Ws,Wd             | Wd = Rotate Right through Carry Ws      | 1             | 1              | C, N, Z                  |

| RRNC                 | RRNC            | f                 | f = Rotate Right (No Carry) f           | 1             | 1              | N, Z                     |

|                      | RRNC            | f,WREG            | WREG = Rotate Right (No Carry) f        | 1             | 1              | N, Z                     |

|                      | RRNC            | Ws,Wd             | Wd = Rotate Right (No Carry) Ws         | 1             | 1              | N, Z                     |

| SE                   | SE              | Ws,Wnd            | Wnd = Sign-Extended Ws                  | 1             | 1              | C, N, Z                  |

| SETM                 | SETM            | f                 | f = FFFFh                               | 1             | 1              | None                     |

| 02111                | SETM            | WREG              | WREG = FFFFh                            | 1             | 1              | None                     |

|                      | SETM            | Ws                | Ws = FFFFh                              | 1             | 1              | None                     |

| SL                   | SL              | f                 | f = Left Shift f                        | 1             | 1              | C, N, OV, Z              |

| 02                   | SL              | f,WREG            | WREG = Left Shift f                     | 1             | 1              | C, N, OV, Z              |

|                      | SL              | Ws,Wd             | Wd = Left Shift Ws                      | 1             | 1              | C, N, OV, Z              |

|                      | SL              | Wb,Wns,Wnd        | Wnd = Left Shift Wb by Wns              | 1             | 1              | N, Z                     |

|                      | SL              | Wb,#lit5,Wnd      | Wnd = Left Shift Wb by lit5             | 1             | 1              | N, Z                     |

| SUB                  | SUB             | f                 | f = f - WREG                            | 1             | 1              | C, DC, N, OV, 2          |

| 000                  | SUB             | f,WREG            | WREG = f – WREG                         | 1             | 1              | C, DC, N, OV, 2          |

|                      | SUB             | #lit10,Wn         | Wn = Wn – lit10                         | 1             | 1              | C, DC, N, OV, 2          |

|                      | SUB             | Wb,Ws,Wd          | Wd = Wb - Ws                            | 1             | 1              | C, DC, N, OV, 2          |

|                      | SUB             | Wb,#lit5,Wd       | Wd = Wb - lit5                          | 1             | 1              | C, DC, N, OV, 2          |

|                      |                 |                   | $f = f - WREG - (\overline{C})$         |               |                |                          |

| SUBB                 | SUBB            | f                 |                                         | 1             | 1              | C, DC, N, OV, 2          |

|                      | SUBB            | f,WREG            | WREG = $f - WREG - (C)$                 | 1             | 1              | C, DC, N, OV, 2          |

|                      | SUBB            | #lit10,Wn         | $Wn = Wn - lit10 - (\overline{C})$      | 1             | 1              | C, DC, N, OV, 2          |

|                      | SUBB            | Wb,Ws,Wd          | $Wd = Wb - Ws - (\overline{C})$         | 1             | 1              | C, DC, N, OV, 2          |

|                      | SUBB            | Wb,#lit5,Wd       | $Wd = Wb - lit5 - (\overline{C})$       | 1             | 1              | C, DC, N, OV, 2          |

| SUBR                 | SUBR            | f                 | f = WREG – f                            | 1             | 1              | C, DC, N, OV, 2          |

|                      | SUBR            | f,WREG            | WREG = WREG – f                         | 1             | 1              | C, DC, N, OV, 2          |

|                      | SUBR            | Wb,Ws,Wd          | Wd = Ws – Wb                            | 1             | 1              | C, DC, N, OV, 2          |

|                      | SUBR            | Wb,#lit5,Wd       | Wd = lit5 – Wb                          | 1             | 1              | C, DC, N, OV, 2          |

| SUBBR                | SUBBR           | f                 | $f = WREG - f - (\overline{C})$         | 1             | 1              | C, DC, N, OV, 2          |

|                      | SUBBR           | f,WREG            | WREG = WREG – f – $(\overline{C})$      | 1             | 1              | C, DC, N, OV, 2          |

|                      | SUBBR           | Wb,Ws,Wd          | $Wd = Ws - Wb - (\overline{C})$         | 1             | 1              | C, DC, N, OV, 2          |

|                      | SUBBR           | Wb,#lit5,Wd       | $Wd = lit5 - Wb - (\overline{C})$       | 1             | 1              | C, DC, N, OV, 2          |

| SWAP                 | SUBBR<br>SWAP.b | WD,#1105,Wd<br>Wn | Wn = Nibble Swap Wn                     | 1             | 1              | None                     |

| our.                 | SWAP.D<br>SWAP  | Wn                | Wn = Byte Swap Wn                       | 1             | 1              | None                     |

NOTES:

| DC CH        | ARACTER        | ISTICS                                                                  | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |      |            |      |                                   |  |

|--------------|----------------|-------------------------------------------------------------------------|------------------------------------------------------|------|------------|------|-----------------------------------|--|

| Param<br>No. | Symbol         | Characteristic                                                          | Min Typ <sup>(1)</sup> Max Units Conc                |      | Conditions |      |                                   |  |

| Operati      | ing Voltage    | 9                                                                       |                                                      |      |            |      |                                   |  |

| DC10         | Supply Voltage |                                                                         |                                                      |      |            |      |                                   |  |

|              | Vdd            |                                                                         | 2.2                                                  | _    | 3.6        | V    | Regulator enabled                 |  |

|              | Vdd            |                                                                         | VDDCORE                                              | _    | 3.6        | V    | Regulator disabled                |  |

|              | VDDCORE        |                                                                         | 2.0                                                  | —    | 2.75       | V    | Regulator disabled                |  |