Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2 0 0 0 0 0                |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB OTG                                     |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                     |

| Number of I/O              | 83                                                                             |

| Program Memory Size        | 192KB (65.5K x 24)                                                             |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16К х 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 100-TQFP                                                                       |

| Supplier Device Package    | 100-TQFP (12x12)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj192gb110-i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|              | Pin Number          |                |                 |     | Input  |                                   |  |  |

|--------------|---------------------|----------------|-----------------|-----|--------|-----------------------------------|--|--|

| Function     | 64-Pin<br>TQFP, QFN | 80-Pin<br>TQFP | 100-Pin<br>TQFP | I/O | Buffer | Description                       |  |  |

| CN0          | 48                  | 60             | 74              | Ι   | ST     | Interrupt-on-Change Inputs.       |  |  |

| CN1          | 47                  | 59             | 73              | I   | ST     |                                   |  |  |

| CN2          | 16                  | 20             | 25              | I   | ST     |                                   |  |  |

| CN3          | 15                  | 19             | 24              | I   | ST     |                                   |  |  |

| CN4          | 14                  | 18             | 23              | I   | ST     |                                   |  |  |

| CN5          | 13                  | 17             | 22              | I   | ST     |                                   |  |  |

| CN6          | 12                  | 16             | 21              | I   | ST     |                                   |  |  |

| CN7          | 11                  | 15             | 20              | I   | ST     |                                   |  |  |

| CN8          | 4                   | 6              | 10              | I   | ST     |                                   |  |  |

| CN9          | 5                   | 7              | 11              | I   | ST     |                                   |  |  |

| CN10         | 6                   | 8              | 12              | I   | ST     |                                   |  |  |

| CN11         | 8                   | 10             | 14              | I   | ST     | 1                                 |  |  |

| CN12         | 30                  | 36             | 44              | I   | ST     | 1                                 |  |  |

| CN13         | 52                  | 66             | 81              | Ι   | ST     | 1                                 |  |  |

| CN14         | 53                  | 67             | 82              | I   | ST     |                                   |  |  |

| CN15         | 54                  | 68             | 83              | I   | ST     |                                   |  |  |

| CN16         | 55                  | 69             | 84              | I   | ST     |                                   |  |  |

| CN17         | 31                  | 39             | 49              | I   | ST     |                                   |  |  |

| CN18         | 32                  | 40             | 50              | 1   | ST     |                                   |  |  |

| CN19         | _                   | 65             | 80              | I   | ST     |                                   |  |  |

| CN20         | _                   | 37             | 47              | I   | ST     |                                   |  |  |

| CN21         | _                   | 38             | 48              | 1   | ST     |                                   |  |  |

| CN22         | 40                  | 50             | 64              | I   | ST     |                                   |  |  |

| CN23         | 39                  | 49             | 63              | 1   | ST     |                                   |  |  |

| CN24         | 17                  | 21             | 26              | 1   | ST     |                                   |  |  |

| CN25         | 18                  | 22             | 27              | 1   | ST     |                                   |  |  |

| CN26         | 21                  | 27             | 32              | 1   | ST     |                                   |  |  |

| CN27         | 22                  | 28             | 33              | 1   | ST     |                                   |  |  |

| CN28         | 23                  | 29             | 34              | 1   | ST     |                                   |  |  |

| CN29         | 24                  | 30             | 35              | 1   | ST     |                                   |  |  |

| CN30         | 27                  | 33             | 41              | 1   | ST     |                                   |  |  |

| CN31         | 28                  | 34             | 42              |     | ST     |                                   |  |  |

| CN32         | 29                  | 35             | 43              |     | ST     |                                   |  |  |

| CN33         |                     |                | 17              |     | ST     | 1                                 |  |  |

| CN34         | _                   | _              | 38              |     | ST     | 1                                 |  |  |

| CN35         | _                   | _              | 58              |     | ST     | 1                                 |  |  |

| CN36         |                     | _              | 59              |     | ST     | 1                                 |  |  |

| CN37         |                     | _              | 60              | 1   | ST     | 1                                 |  |  |

| CN38         |                     | _              | 61              | 1   | ST     | 1                                 |  |  |

| CN39         |                     |                | 91              | 1   | ST     | 4                                 |  |  |

| CN39<br>CN40 |                     |                | 91              | 1   | ST     | 4                                 |  |  |

| CN40<br>CN41 | _                   | 23             | 28              |     | ST     | 4                                 |  |  |

| CN41<br>CN42 |                     | 23             | 20              |     | ST     | 4                                 |  |  |

| Legend:      | TTL = TTL inp       |                | 29              |     |        | L<br>Schmitt Trigger input buffer |  |  |

#### **TABLE 1-4:** PIC24FJ256GB110 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

I I L Input buller ANA = Analog level input/output

SI = Schmitt Trigger input buffer $I^2C^{TM} = I^2C/SMBus input buffer$

|          |                     | Pin Number     |                 | Input |                 |                                      |

|----------|---------------------|----------------|-----------------|-------|-----------------|--------------------------------------|

| Function | 64-Pin<br>TQFP, QFN | 80-Pin<br>TQFP | 100-Pin<br>TQFP | I/O   | Input<br>Buffer | Description                          |

| CN43     | —                   | 52             | 66              | I     | ST              | Interrupt-on-Change Inputs.          |

| CN44     | —                   | 53             | 67              | I     | ST              |                                      |

| CN45     | _                   | 4              | 6               | I     | ST              |                                      |

| CN46     | —                   | _              | 7               | I     | ST              |                                      |

| CN47     | —                   | 5              | 8               | I     | ST              |                                      |

| CN48     | _                   | _              | 9               | I     | ST              |                                      |

| CN49     | 46                  | 58             | 72              | I     | ST              |                                      |

| CN50     | 49                  | 61             | 76              | I     | ST              |                                      |

| CN51     | 50                  | 62             | 77              | I     | ST              |                                      |

| CN52     | 51                  | 63             | 78              | I     | ST              |                                      |

| CN53     | 42                  | 54             | 68              | Ι     | ST              | ]                                    |

| CN54     | 43                  | 55             | 69              | Ι     | ST              |                                      |

| CN55     | 44                  | 56             | 70              | Ι     | ST              | ]                                    |

| CN56     | 45                  | 57             | 71              | I     | ST              |                                      |

| CN57     | —                   | 64             | 79              | I     | ST              |                                      |

| CN58     | 60                  | 76             | 93              | I     | ST              |                                      |

| CN59     | 61                  | 77             | 94              | I     | ST              |                                      |

| CN60     | 62                  | 78             | 98              | I     | ST              |                                      |

| CN61     | 63                  | 79             | 99              | I     | ST              |                                      |

| CN62     | 64                  | 80             | 100             | I     | ST              |                                      |

| CN63     | 1                   | 1              | 3               | I     | ST              |                                      |

| CN64     | 2                   | 2              | 4               | I     | ST              |                                      |

| CN65     | 3                   | 3              | 5               | I     | ST              |                                      |

| CN66     | —                   | 13             | 18              | I     | ST              |                                      |

| CN67     | —                   | 14             | 19              | I     | ST              |                                      |

| CN68     | 58                  | 72             | 87              | I     | ST              |                                      |

| CN69     | 59                  | 73             | 88              | I     | ST              |                                      |

| CN70     | —                   | 42             | 52              | I     | ST              |                                      |

| CN71     | 33                  | 41             | 51              | I     | ST              |                                      |

| CN74     | —                   | 43             | 53              | I     | ST              |                                      |

| CN75     | —                   | _              | 40              | I     | ST              |                                      |

| CN76     | —                   | _              | 39              | I     | ST              |                                      |

| CN77     | —                   | 75             | 90              | Ι     | ST              |                                      |

| CN78     | —                   | 74             | 89              | Ι     | ST              |                                      |

| CN79     | —                   | _              | 96              | Ι     | ST              |                                      |

| CN80     | —                   | _              | 97              | Ι     | ST              |                                      |

| CN81     | —                   | _              | 95              | Ι     | ST              |                                      |

| CN82     | —                   | _              | 1               | Ι     | ST              |                                      |

| CTED1    | 28                  | 34             | 42              | Ι     | ANA             | CTMU External Edge Input 1.          |

| CTED2    | 27                  | 33             | 41              | I     | ANA             | CTMU External Edge Input 2.          |

| CTPLS    | 29                  | 35             | 43              | 0     | —               | CTMU Pulse Output.                   |

| CVREF    | 23                  | 29             | 34              | 0     | _               | Comparator Voltage Reference Output. |

### TABLE 1-4: PIC24FJ256GB110 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

Legend: TT

TTL = TTL input buffer ANA = Analog level input/output ST = Schmitt Trigger input buffer

$I^2C^{TM} = I^2C/SMBus$  input buffer

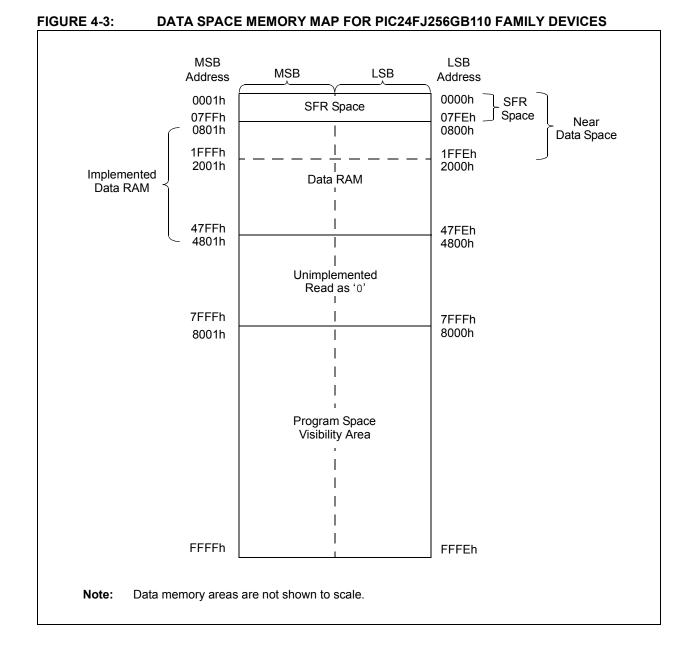

### 4.2 Data Address Space

The PIC24F core has a separate, 16-bit wide data memory space, addressable as a single linear range. The data space is accessed using two Address Generation Units (AGUs), one each for read and write operations. The data space memory map is shown in Figure 4-3.

All Effective Addresses (EAs) in the data memory space are 16 bits wide and point to bytes within the data space. This gives a data space address range of 64 Kbytes or 32K words. The lower half of the data memory space (that is, when EA<15> = 0) is used for implemented memory addresses, while the upper half (EA<15> = 1) is reserved for the program space visibility area (see **Section 4.3.3 "Reading Data from Program Memory Using Program Space Visibility"**). PIC24FJ256GB110 family devices implement a total of 16 Kbytes of data memory. Should an EA point to a location outside of this area, an all zero word or byte will be returned.

### 4.2.1 DATA SPACE WIDTH

The data memory space is organized in byte-addressable, 16-bit wide blocks. Data is aligned in data memory and registers as 16-bit words, but all data space EAs resolve to bytes. The Least Significant Bytes of each word have even addresses, while the Most Significant Bytes have odd addresses.

| Flag Bit          | Setting Event                                     | Clearing Event          |

|-------------------|---------------------------------------------------|-------------------------|

| TRAPR (RCON<15>)  | Trap Conflict Event                               | POR                     |

| IOPUWR (RCON<14>) | Illegal Opcode or Uninitialized W Register Access | POR                     |

| CM (RCON<9>)      | Configuration Mismatch Reset                      | POR                     |

| EXTR (RCON<7>)    | MCLR Reset                                        | POR                     |

| SWR (RCON<6>)     | RESET Instruction                                 | POR                     |

| WDTO (RCON<4>)    | WDT Time-out                                      | PWRSAV Instruction, POR |

| SLEEP (RCON<3>)   | PWRSAV #SLEEP Instruction                         | POR                     |

| IDLE (RCON<2>)    | PWRSAV #IDLE Instruction                          | POR                     |

| BOR (RCON<1>)     | POR, BOR                                          | _                       |

| POR (RCON<0>)     | POR                                               |                         |

### TABLE 6-1: RESET FLAG BIT OPERATION

Note: All Reset flag bits may be set or cleared by the user software.

### 6.1 Clock Source Selection at Reset

If clock switching is enabled, the system clock source at device Reset is chosen as shown in Table 6-2. If clock switching is disabled, the system clock source is always selected according to the oscillator Configuration bits. Refer to **Section 8.0 "Oscillator Configuration"** for further details.

#### TABLE 6-2: OSCILLATOR SELECTION vs. TYPE OF RESET (CLOCK SWITCHING ENABLED)

| Reset Type | Clock Source Determinant |

|------------|--------------------------|

| POR        | FNOSC Configuration bits |

| BOR        | (CW2<10:8>)              |

| MCLR       | COSC Control bits        |

| WDTO       | (OSCCON<14:12>)          |

| SWR        |                          |

### 6.2 Device Reset Times

The Reset times for various types of device Reset are summarized in Table 6-3. Note that the system Reset signal, SYSRST, is released after the POR and PWRT delay times expire.

The time at which the device actually begins to execute code will also depend on the system oscillator delays, which include the Oscillator Start-up Timer (OST) and the PLL lock time. The OST and PLL lock times occur in parallel with the applicable SYSRST delay times.

The FSCM delay determines the time at which the FSCM begins to monitor the system clock source after the SYSRST signal is released.

| REGISTER                     | 7-5: IFS0:      | INTERRUP                         | FLAG STAT        | US REGISTE        | R 0              |                 |        |

|------------------------------|-----------------|----------------------------------|------------------|-------------------|------------------|-----------------|--------|

| U-0                          | U-0             | R/W-0                            | R/W-0            | R/W-0             | R/W-0            | R/W-0           | R/W-0  |

| —                            | —               | AD1IF                            | U1TXIF           | U1RXIF            | SPI1IF           | SPF1IF          | T3IF   |

| bit 15                       |                 |                                  |                  |                   |                  |                 | bit 8  |

| R/W-0                        | R/W-0           | R/W-0                            | U-0              | R/W-0             | R/W-0            | R/W-0           | R/W-0  |

| T2IF                         | OC2IF           | IC2IF                            | _                | T1IF              | OC1IF            | IC1IF           | INTOIF |

| bit 7                        |                 |                                  |                  |                   |                  |                 | bit C  |

| Logondy                      |                 |                                  |                  |                   |                  |                 |        |

| <b>Legend:</b><br>R = Readab | le bit          | W = Writable                     | bit              | U = Unimplem      | nented bit, read | 1 as '0'        |        |

| -n = Value at                |                 | '1' = Bit is se                  |                  | '0' = Bit is clea |                  | x = Bit is unkn | own    |

|                              |                 |                                  |                  |                   |                  |                 |        |

| bit 15-14                    | -               | ted: Read as                     |                  |                   |                  |                 |        |

| bit 13                       |                 |                                  |                  | t Flag Status bit | t                |                 |        |

|                              |                 | request has oc<br>request has no |                  |                   |                  |                 |        |

| bit 12                       | -               | -                                | r Interrupt Flag | Status bit        |                  |                 |        |

|                              |                 | request has oc                   |                  | Status bit        |                  |                 |        |

|                              |                 | request has no                   |                  |                   |                  |                 |        |

| bit 11                       | -               | -                                | nterrupt Flag S  | tatus bit         |                  |                 |        |

|                              | 1 = Interrupt r | request has oc                   | curred           |                   |                  |                 |        |

|                              | 0 = Interrupt r | request has no                   | t occurred       |                   |                  |                 |        |

| bit 10                       |                 |                                  | t Flag Status b  | it                |                  |                 |        |

|                              |                 | request has oc                   |                  |                   |                  |                 |        |

| hit O                        | -               | request has no                   |                  | :4                |                  |                 |        |

| bit 9                        |                 | request has oc                   | t Flag Status b  | IL                |                  |                 |        |

|                              |                 | request has oc                   |                  |                   |                  |                 |        |

| bit 8                        | •               | Interrupt Flag                   |                  |                   |                  |                 |        |

|                              |                 | request has oc                   |                  |                   |                  |                 |        |

|                              | 0 = Interrupt r | request has no                   | t occurred       |                   |                  |                 |        |

| bit 7                        |                 | Interrupt Flag                   |                  |                   |                  |                 |        |

|                              |                 | request has oc                   |                  |                   |                  |                 |        |

|                              | •               | request has no                   |                  |                   |                  |                 |        |

| bit 6                        |                 | •                                |                  | ipt Flag Status b | Dit              |                 |        |

|                              |                 | request has oc<br>request has no |                  |                   |                  |                 |        |

| bit 5                        | -               | -                                | el 2 Interrupt F | lag Status bit    |                  |                 |        |

|                              |                 | request has oc                   | •                |                   |                  |                 |        |

|                              | 0 = Interrupt r | request has no                   | t occurred       |                   |                  |                 |        |

| bit 4                        | Unimplemen      | ted: Read as                     | 0'               |                   |                  |                 |        |

| bit 3                        |                 | Interrupt Flag                   |                  |                   |                  |                 |        |

|                              |                 | request has oc                   |                  |                   |                  |                 |        |

| 1.1.0                        | -               | request has no                   |                  |                   |                  |                 |        |

| bit 2                        | •               | •                                |                  | ipt Flag Status b | DIT              |                 |        |

|                              |                 | request has oc<br>request has no |                  |                   |                  |                 |        |

| bit 1                        | -               | -                                | el 1 Interrupt F | lag Status bit    |                  |                 |        |

|                              |                 | request has oc                   | -                | lag clatac sit    |                  |                 |        |

|                              |                 | request has no                   |                  |                   |                  |                 |        |

| bit 0                        | INT0IF: Exter   | nal Interrupt 0                  | Flag Status bit  |                   |                  |                 |        |

|                              |                 | request has oc                   |                  |                   |                  |                 |        |

|                              | 0 = Interrupt r | request has no                   | t occurred       |                   |                  |                 |        |

### REGISTER 7-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0

| U-0          | U-0                                                                                                | R/W-0                                | U-0            | U-0               | U-0              | U-0             | R/W-0 |

|--------------|----------------------------------------------------------------------------------------------------|--------------------------------------|----------------|-------------------|------------------|-----------------|-------|

|              | <u> </u>                                                                                           | CTMUIF                               |                | <u> </u>          | _                | <u> </u>        | LVDIF |

| bit 15       |                                                                                                    |                                      |                |                   |                  |                 | bit 8 |

|              |                                                                                                    |                                      |                | <b>D</b> 444 0    | <b>D</b> 444 0   | <b>D</b> #44 0  |       |

| U-0          | U-0                                                                                                | U-0                                  | U-0            | R/W-0             | R/W-0            | R/W-0           | U-0   |

|              | —                                                                                                  | —                                    | _              | CRCIF             | U2ERIF           | U1ERIF          |       |

| bit 7        |                                                                                                    |                                      |                |                   |                  |                 | bit ( |

| Legend:      |                                                                                                    |                                      |                |                   |                  |                 |       |

| R = Readab   | ole bit                                                                                            | W = Writable b                       | it             | U = Unimplem      | nented bit, read | d as '0'        |       |

| -n = Value a | at POR                                                                                             | '1' = Bit is set                     |                | '0' = Bit is clea | ared             | x = Bit is unkn | own   |

|              |                                                                                                    |                                      |                |                   |                  |                 |       |

| bit 15-14    | Unimplemer                                                                                         | nted: Read as '0                     | ,              |                   |                  |                 |       |

| bit 13       | CTMUIF: CT                                                                                         | MU Interrupt Fla                     | g Status bit   |                   |                  |                 |       |

|              |                                                                                                    | request has occur<br>request has not |                |                   |                  |                 |       |

| bit 12-9     | Unimplemer                                                                                         | nted: Read as '0                     | ,              |                   |                  |                 |       |

| bit 8        | LVDIF: Low-                                                                                        | Voltage Detect Ir                    | terrupt Flag   | Status bit        |                  |                 |       |

|              |                                                                                                    | request has occurrequest has not     |                |                   |                  |                 |       |

| bit 7-4      | Unimplemer                                                                                         | nted: Read as '0                     | ,              |                   |                  |                 |       |

| bit 3        | CRCIF: CRC                                                                                         | Generator Inter                      | rupt Flag Stat | tus bit           |                  |                 |       |

|              | 1 = Interrupt request has occurred                                                                 |                                      |                |                   |                  |                 |       |

|              | 0 = Interrupt request has not occurred                                                             |                                      |                |                   |                  |                 |       |

| bit 2        | U2ERIF: UART2 Error Interrupt Flag Status bit                                                      |                                      |                |                   |                  |                 |       |

|              | <ol> <li>I = Interrupt request has occurred</li> <li>Interrupt request has not occurred</li> </ol> |                                      |                |                   |                  |                 |       |

| bit 1        | U1ERIF: UART1 Error Interrupt Flag Status bit                                                      |                                      |                |                   |                  |                 |       |

|              |                                                                                                    | request has occi                     |                |                   |                  |                 |       |

|              |                                                                                                    |                                      |                |                   |                  |                 |       |

|              | 0 = Interrupt                                                                                      | request has not                      | occurred       |                   |                  |                 |       |

### REGISTER 7-9: IFS4: INTERRUPT FLAG STATUS REGISTER 4

### REGISTER 7-29: IPC12: INTERRUPT PRIORITY CONTROL REGISTER 12

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-1   | R/W-0   | R/W-0   |

|--------|-----|-----|-----|-----|---------|---------|---------|

| —      | _   |     |     | —   | MI2C2P2 | MI2C2P1 | MI2C2P0 |

| bit 15 |     |     |     |     |         |         | bit 8   |

|        |     |     |     |     |         |         |         |

| U-0       | R/W-1   | R/W-0   | R/W-0   | U-0 | U-0 | U-0 | U-0   |

|-----------|---------|---------|---------|-----|-----|-----|-------|

| —         | SI2C2P2 | SI2C2P1 | SI2C2P0 | —   |     |     | _     |

| bit 7 bit |         |         |         |     |     |     | bit 0 |

| Legend:                                                                       |                                                                                                                                  |                  |                       |                    |  |  |  |

|-------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------|--------------------|--|--|--|

| R = Readable bit                                                              |                                                                                                                                  | W = Writable bit | U = Unimplemented bit | , read as '0'      |  |  |  |

| -n = Value a                                                                  | at POR                                                                                                                           | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |  |  |  |

| bit 15-11                                                                     | 5-11 Unimplemented: Read as '0'                                                                                                  |                  |                       |                    |  |  |  |

| bit 10-8                                                                      | MI2C2P<2:0>: Master I2C2 Event Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt)             |                  |                       |                    |  |  |  |

| •<br>•<br>001 = Interrupt is priority 1<br>000 = Interrupt source is disabled |                                                                                                                                  |                  |                       |                    |  |  |  |

| bit 7                                                                         | Unimplemented: Read as '0'                                                                                                       |                  |                       |                    |  |  |  |

| bit 6-4                                                                       | <b>SI2C2P&lt;2:0&gt;:</b> Slave I2C2 Event Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt) |                  |                       |                    |  |  |  |

- 111 = Interrupt is priority 7 (highest priority interrup

- 001 = Interrupt is priority 1 000 = Interrupt source is disabled

- bit 3-0 Unimplemented: Read as '0'

### 7.4 Interrupt Setup Procedures

### 7.4.1 INITIALIZATION

To configure an interrupt source:

- 1. Set the NSTDIS Control bit (INTCON1<15>) if nested interrupts are not desired.

- Select the user-assigned priority level for the interrupt source by writing the control bits in the appropriate IPCx register. The priority level will depend on the specific application and type of interrupt source. If multiple priority levels are not desired, the IPCx register control bits for all enabled interrupt sources may be programmed to the same non-zero value.

| Note: | At a device Reset, the IPCx registers are |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|

|       | initialized, such that all user interrupt |  |  |  |  |

|       | sources are assigned to priority level 4. |  |  |  |  |

- 3. Clear the interrupt flag status bit associated with the peripheral in the associated IFSx register.

- 4. Enable the interrupt source by setting the interrupt enable control bit associated with the source in the appropriate IECx register.

### 7.4.2 INTERRUPT SERVICE ROUTINE

The method that is used to declare an ISR and initialize the IVT with the correct vector address will depend on the programming language (i.e., 'C' or assembler) and the language development toolsuite that is used to develop the application. In general, the user must clear the interrupt flag in the appropriate IFSx register for the source of the interrupt that the ISR handles. Otherwise, the ISR will be re-entered immediately after exiting the routine. If the ISR is coded in assembly language, it must be terminated using a RETFIE instruction to unstack the saved PC value, SRL value and old CPU priority level.

### 7.4.3 TRAP SERVICE ROUTINE

A Trap Service Routine (TSR) is coded like an ISR, except that the appropriate trap status flag in the INTCON1 register must be cleared to avoid re-entry into the TSR.

### 7.4.4 INTERRUPT DISABLE

All user interrupts can be disabled using the following procedure:

- 1. Push the current SR value onto the software stack using the PUSH instruction.

- 2. Force the CPU to priority level 7 by inclusive ORing the value E0h with SRL.

To enable user interrupts, the POP instruction may be used to restore the previous SR value.

Note that only user interrupts with a priority level of 7 or less can be disabled. Trap sources (level 8-15) cannot be disabled.

The DISI instruction provides a convenient way to disable interrupts of priority levels 1-6 for a fixed period of time. Level 7 interrupt sources are not disabled by the DISI instruction.

### 9.0 POWER-SAVING FEATURES

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "PIC24F Family Reference Manual", Section 10. "Power-Saving Features" (DS39698).

The PIC24FJ256GB110 family of devices provides the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of circuits being clocked constitutes lower consumed power. All PIC24F devices manage power consumption in four different ways:

- Clock frequency

- Instruction-based Sleep and Idle modes

- Software controlled Doze mode

- · Selective peripheral control in software

Combinations of these methods can be used to selectively tailor an application's power consumption, while still maintaining critical application features, such as timing-sensitive communications.

### 9.1 Clock Frequency and Clock Switching

PIC24F devices allow for a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or high-precision oscillators by simply changing the NOSC bits. The process of changing a system clock during operation, as well as limitations to the process, are discussed in more detail in **Section 8.0 "Oscillator Configuration"**.

### 9.2 Instruction-Based Power-Saving Modes

PIC24F devices have two special power-saving modes that are entered through the execution of a special PWRSAV instruction. Sleep mode stops clock operation and halts all code execution; Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation. The assembly syntax of the PWRSAV instruction is shown in Example 9-1. Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to "wake-up".

| Note: | SLEEP_MODE and IDLE_MODE are con-       |

|-------|-----------------------------------------|

|       | stants defined in the assembler include |

|       | file for the selected device.           |

### 9.2.1 SLEEP MODE

Sleep mode has these features:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption will be reduced to a minimum provided that no I/O pin is sourcing current.

- The Fail-Safe Clock Monitor does not operate during Sleep mode since the system clock source is disabled.

- The LPRC clock will continue to run in Sleep mode if the WDT is enabled.

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode.

- Some device features or peripherals may continue to operate in Sleep mode. This includes items such as the input change notification on the I/O ports, or peripherals that use an external clock input. Any peripheral that requires the system clock source for its operation will be disabled in Sleep mode.

The device will wake-up from Sleep mode on any of the these events:

- On any interrupt source that is individually enabled

- On any form of device Reset

- · On a WDT time-out

On wake-up from Sleep, the processor will restart with the same clock source that was active when Sleep mode was entered.

### EXAMPLE 9-1: PWRSAV INSTRUCTION SYNTAX

| PWRSAV | #SLEEP_MODE | ; | Put | the | device | into | SLEEP  | mode |

|--------|-------------|---|-----|-----|--------|------|--------|------|

| PWRSAV | #IDLE_MODE  | ; | Put | the | device | into | IDLE ' | mode |

### REGISTER 10-19: RPINR27: PERIPHERAL PIN SELECT INPUT REGISTER 27

| U-0    | U-0 | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   |

|--------|-----|---------|---------|---------|---------|---------|---------|

| —      | —   | U4CTSR5 | U4CTSR4 | U4CTSR3 | U4CTSR2 | U4CTSR1 | U4CTSR0 |

| bit 15 |     |         |         |         |         |         | bit 8   |

| U-0   | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | U4RXR5 | U4RXR4 | U4RXR3 | U4RXR2 | U4RXR1 | U4RXR0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                            |

|-----------|---------------------------------------------------------------------------------------|

| bit 13-8  | U4CTSR<5:0>: Assign UART4 Clear to Send (U4CTS) to Corresponding RPn or RPIn Pin bits |

| bit 7-6   | Unimplemented: Read as '0'                                                            |

| bit 5-0   | U4RXR<5:0>: Assign UART4 Receive (U4RX) to Corresponding RPn or RPIn Pin bits         |

### REGISTER 10-20: RPINR28: PERIPHERAL PIN SELECT INPUT REGISTER 28

| U-0    | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | SCK3R5 | SCK3R4 | SCK3R3 | SCK3R2 | SCK3R1 | SCK3R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

| U-0   | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | SDI3R5 | SDI3R4 | SDI3R3 | SDI3R2 | SDI3R1 | SDI3R0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 SCK3R<5:0>: Assign SPI3 Clock Input (SCK3IN) to Corresponding RPn or RPIn Pin bits

bit 7-6 Unimplemented: Read as '0'

bit 5-0 SDI3R<5:0>: Assign SPI3 Data Input (SDI3) to Corresponding RPn or RPIn Pin bits

### REGISTER 14-2: OCxCON2: OUTPUT COMPARE x CONTROL REGISTER 2

| R/W-0  | R/W-0  | R/W-0    | R/W-0 | U-0 | U-0 | U-0 | R/W-0 |

|--------|--------|----------|-------|-----|-----|-----|-------|

| FLTMD  | FLTOUT | FLTTRIEN | OCINV | —   | —   |     | OC32  |

| bit 15 |        |          |       |     |     |     | bit 8 |

| R/W-0  | R/W-0 HS | R/W-0  | R/W-0    | R/W-1    | R/W-1    | R/W-0    | R/W-0    |

|--------|----------|--------|----------|----------|----------|----------|----------|

| OCTRIG | TRIGSTAT | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 |

| bit 7  |          |        |          |          |          |          | bit 0    |

| Legend:           | HS = Hardware Settable                                                                             | bit                                                         |

|-------------------|----------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| R = Reada         | ble bit W = Writable bit                                                                           | U = Unimplemented bit, read as '0'                          |

| -n = Value        | at POR '1' = Bit is set                                                                            | '0' = Bit is cleared x = Bit is unknown                     |

|                   |                                                                                                    |                                                             |

| bit 15            | FLTMD: Fault Mode Select bit                                                                       |                                                             |

|                   |                                                                                                    | Fault source is removed and the corresponding OCFLT0 bit i  |

|                   | cleared in software                                                                                | ault source is removed and a new PWM period starts          |

| bit 14            | <b>FLTOUT:</b> Fault Out bit                                                                       |                                                             |

|                   | 1 = PWM output is driven high on a Fau                                                             | ılt                                                         |

|                   | 0 = PWM output is driven low on a Faul                                                             |                                                             |

| bit 13            | FLTTRIEN: Fault Output State Select bit                                                            | t                                                           |

|                   | 1 = Pin is forced to an output on a Fault                                                          |                                                             |

|                   | 0 = Pin I/O condition is unaffected by a                                                           | Fault                                                       |

| bit 12            | OCINV: OCMP Invert bit                                                                             |                                                             |

|                   | 1 = OCx output is inverted                                                                         |                                                             |

| h:+ 11 0          | 0 = OCx output is not inverted                                                                     |                                                             |

| bit 11-9<br>bit 8 | Unimplemented: Read as '0'                                                                         | le hit (20 hit energien)                                    |

| DILO              | <ul> <li>OC32: Cascade Two OC Modules Enab</li> <li>1 = Cascade module operation enable</li> </ul> |                                                             |

|                   | 0 = Cascade module operation disable                                                               |                                                             |

| bit 7             | OCTRIG: OCx Trigger/Sync Select bit                                                                |                                                             |

|                   | 1 = Trigger OCx from source designate                                                              | ed by the SYNCSELx bits                                     |

|                   | 0 = Synchronize OCx with source desi                                                               | gnated by the SYNCSELx bits                                 |

| bit 6             | TRIGSTAT: Timer Trigger Status bit                                                                 |                                                             |

|                   | 1 = Timer source has been triggered a                                                              |                                                             |

|                   | 0 = Timer source has not been triggere                                                             |                                                             |

| bit 5             | OCTRIS: OCx Output Pin Direction Sele                                                              | ect bit                                                     |

|                   | 1 = OCx pin is tristated                                                                           | ated to OCy ain                                             |

|                   | 0 = Output compare peripheral x connect                                                            |                                                             |

|                   |                                                                                                    | source, either by selecting this mode or another equivalent |

|                   | SYNCSEL setting.                                                                                   |                                                             |

| 2:                | Use these inputs as trigger sources only and                                                       | d never as sync sources.                                    |

Г

### 18.1.2 HOST AND OTG MODES

### 18.1.2.1 D+ and D- Pull-down Resistors

PIC24FJ256GB110 family devices have built-in 15 kΩ pull-down resistor on the D+ and D- lines. These are used in tandem to signal to the bus that the microcontroller is operating in Host mode. They are engaged by setting the DPPULDWN and DMPULDWN bits (U10TGCON<5,4>).

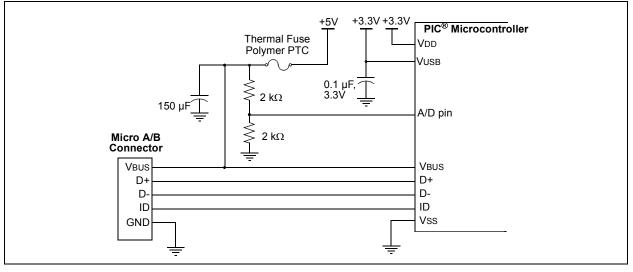

### 18.1.2.2 Power Configurations

In Host mode, as well as Host mode in On-the-Go operation, the USB 2.0 specification requires that the Host application supply power on VBUS. Since the

FIGURE 18-6: HOST INTERFACE EXAMPLE

microcontroller is running below VBUS and is not able to source sufficient current, a separate power supply must be provided.

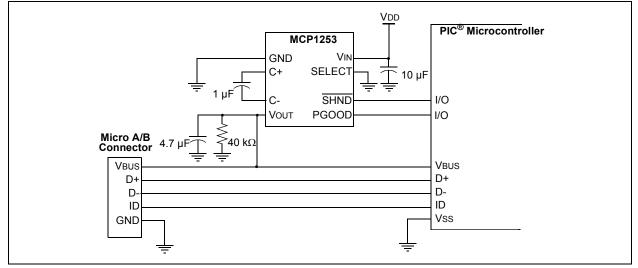

When the application is always operating in Host mode, a simple circuit can be used to supply VBUS and regulate current on the bus (Figure 18-6). For OTG operation, it is necessary to be able to turn VBUS on or off as needed, as the microcontroller switches between Device and Host modes. A typical example using an external charge pump is shown in Figure 18-7.

### FIGURE 18-7: OTG INTERFACE EXAMPLE

### 18.6.2 HOST NEGOTIATION PROTOCOL (HNP)

In USB OTG applications, a Dual Role Device (DRD) is a device that is capable of being either a host or a peripheral. Any OTG DRD must support Host Negotiation Protocol (HNP).

HNP allows an OTG B-device to temporarily become the USB host. The A-device must first enable the B-device to follow HNP. Refer to the "On-The-Go Supplement to the USB 2.0 Specification" for more information regarding HNP. HNP may only be initiated at full speed.

After being enabled for HNP by the A-device, the B-device requests being the host any time that the USB link is in Suspend state, by simply indicating a disconnect. This can be done in software by clearing DPPULUP and DMPULUP. When the A-device detects the disconnect condition (via the URSTIF (U1IR<0>) interrupt), the A-device may allow the B-device to take over as Host. The A-device does this by signaling connect as a full-speed function. Software may accomplish this by setting DPPULUP.

If the A-device responds instead with resume signaling, the A-device remains as host. When the B-device detects the connect condition (via ATTACHIF (U1IR<6>), the B-device becomes host. The B-device drives Reset signaling prior to using the bus.

When the B-device has finished in its role as Host, it stops all bus activity and turns on its D+ pull-up resistor by setting DPPULUP. When the A-device detects a suspend condition (Idle for 3 ms), the A-device turns off its D+ pull-up. The A-device may also power-down VBUS supply to end the session. When the A-device detects the connect condition (via ATTACHIF), the A-device resumes host operation, and drives Reset signaling.

### 18.7 USB OTG Module Registers

There are a total of 37 memory mapped registers associated with the USB OTG module. They can be divided into four general categories:

- USB OTG Module Control (12)

- USB Interrupt (7)

- USB Endpoint Management (16)

- USB VBUS Power Control (2)

This total does not include the (up to) 128 BD registers in the BDT. Their prototypes, described in Register 18-1 and Register 18-2, are shown separately in **Section 18.2 "USB Buffer Descriptors and the BDT"**.

With the exception U1PWMCON and U1PWMRRS, all USB OTG registers are implemented in the Least Significant Byte of the register. Bits in the upper byte are unimplemented, and have no function. Note that some registers are instantiated only in Host mode, while other registers have different bit instantiations and functions in Device and Host modes.

Registers described in the following sections are those that have bits with specific control and configuration features. The following registers are used for data or address values only:

- U1BDTP1: Specifies the 256-word page in data RAM used for the BDT; 8-bit value with bit 0 fixed as '0' for boundary alignment

- U1FRML and U1FRMH: Contains the 11-bit byte counter for the current data frame

- U1PWMRRS: Contains the 8-bit value for PWM duty cycle (bits<15:8>) and PWM period (bits<7:0>) for the VBUS boost assist PWM module.

### REGISTER 19-1: PMCON: PARALLEL PORT CONTROL REGISTER (CONTINUED)

| bit 2 | <b>BEP:</b> Byte Enable Polarity bit<br>1 = Byte enable active-high (PMBE)<br>0 = Byte enable active-low (PMBE)                            |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------|

| bit 1 | WRSP: Write Strobe Polarity bit                                                                                                            |

|       | For Slave modes and Master mode 2 (PMMODE<9:8> = 00,01,10):<br>1 = Write strobe active-high (PMWR)<br>0 = Write strobe active-low (PMWR)   |

|       | <u>For Master mode 1 (PMMODE&lt;9:8&gt; = 11):</u><br>1 = Enable strobe active-high <u>(PMENB)</u><br>0 = Enable strobe active-low (PMENB) |

| bit 0 | RDSP: Read Strobe Polarity bit                                                                                                             |

|       | For Slave modes and Master mode 2 (PMMODE<9:8> = 00,01,10):<br>1 = Read strobe active-high (PMRD)<br>0 = Read strobe active-low (PMRD)     |

|       | For Master mode 1 (PMMODE<9:8> = 11):<br>1 = Read/write strobe active-high (PMRD/PMWR)<br>0 = Read/write strobe active-low (PMRD/PMWR)     |

Note 1: These bits have no effect when their corresponding pins are used as address lines.

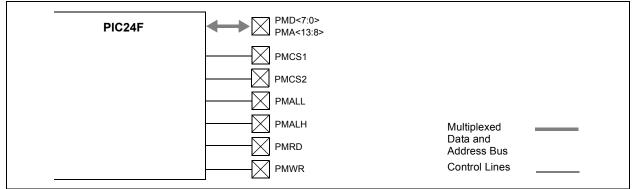

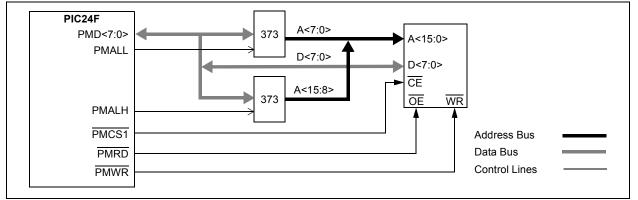

### FIGURE 19-5: MASTER MODE, PARTIALLY MULTIPLEXED ADDRESSING (SEPARATE READ AND WRITE STROBES, TWO CHIP SELECTS)

| PIC24F → PMA<13:8>         |  |

|----------------------------|--|

| PMD<7:0><br>PMA<7:0>       |  |

| PMCS1                      |  |

| PMCS2 Address Bus          |  |

| PMALL Multiplexed Data and |  |

| PMRD Address Bus           |  |

| PMWR Control Lines         |  |

### FIGURE 19-6: MASTER MODE, FULLY MULTIPLEXED ADDRESSING (SEPARATE READ AND WRITE STROBES, TWO CHIP SELECTS)

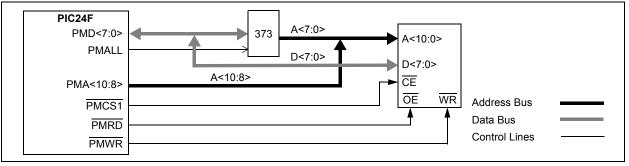

### FIGURE 19-8: EXAMPLE OF A PARTIALLY MULTIPLEXED ADDRESSING APPLICATION

© 2009 Microchip Technology Inc.

### REGISTER 20-1: RCFGCAL: RTCC CALIBRATION AND CONFIGURATION REGISTER<sup>(1)</sup> (CONTINUED)

bit 7-0 CAL<7:0>: RTC Drift Calibration bits

...

01111111 = Maximum positive adjustment; adds 508 RTC clock pulses every one minute

... 00000001 = Minimum positive adjustment; adds 4 RTC clock pulses every one minute 00000000 = No adjustment

111111111 = Minimum negative adjustment; subtracts 4 RTC clock pulses every one minute

10000000 = Maximum negative adjustment; subtracts 512 RTC clock pulses every one minute

- **Note 1:** The RCFGCAL register is only affected by a POR.

- **2:** A write to the RTCEN bit is only allowed when RTCWREN = 1.

- 3: This bit is read-only. It is cleared to '0' on a write to the lower half of the MINSEC register.

### REGISTER 20-2: PADCFG1: PAD CONFIGURATION CONTROL REGISTER

| U-0                                | U-0 | U-0                  | U-0                                | U-0                | U-0 | U-0                     | U-0    |

|------------------------------------|-----|----------------------|------------------------------------|--------------------|-----|-------------------------|--------|

| —                                  | —   | —                    | —                                  | —                  | —   | —                       |        |

| bit 15                             |     |                      |                                    |                    |     |                         | bit 8  |

|                                    |     |                      |                                    |                    |     |                         |        |

| U-0                                | U-0 | U-0                  | U-0                                | U-0                | U-0 | R/W-0                   | R/W-0  |

| —                                  | —   | —                    | —                                  | —                  | —   | RTSECSEL <sup>(1)</sup> | PMPTTL |

| bit 7                              |     |                      |                                    | ·                  |     |                         | bit 0  |

|                                    |     |                      |                                    |                    |     |                         |        |

| Legend:                            |     |                      |                                    |                    |     |                         |        |

| R = Readable bit W = Writable bit  |     | bit                  | U = Unimplemented bit, read as '0' |                    |     |                         |        |

| -n = Value at POR '1' = Bit is set |     | '0' = Bit is cleared |                                    | x = Bit is unknown |     |                         |        |

| L                                  |     |                      |                                    |                    |     |                         |        |

| Unimplemented: Read as '0'                                                                                                                     |

|------------------------------------------------------------------------------------------------------------------------------------------------|

| RTSECSEL: RTCC Seconds Clock Output Select bit <sup>(1)</sup>                                                                                  |

| <ul> <li>1 = RTCC seconds clock is selected for the RTCC pin</li> <li>0 = RTCC alarm pulse is selected for the RTCC pin</li> </ul>             |

| PMPTTL: PMP Module TTL Input Buffer Select bit                                                                                                 |

| <ul> <li>1 = PMP module inputs (PMDx, PMCS1) use TTL input buffers</li> <li>0 = PMP module inputs use Schmitt Trigger input buffers</li> </ul> |

|                                                                                                                                                |

Note 1: To enable the actual RTCC output, the RTCOE (RCFGCAL<10>)) bit must also be set.

|                     |               |                                  |                    |                   |                  |                   | n          |

|---------------------|---------------|----------------------------------|--------------------|-------------------|------------------|-------------------|------------|

| R/W-0               | U-0           | R/W-0                            | U-0                | U-0               | U-0              | R/W-0             | R/W-0      |

| ADON <sup>(1)</sup> | —             | ADSIDL                           | _                  | —                 | —                | FORM1             | FORM0      |

| bit 15              |               |                                  |                    |                   |                  |                   | bit 8      |

|                     |               |                                  |                    |                   |                  |                   |            |

| R/W-0               | R/W-0         | R/W-0                            | U-0                | U-0               | R/W-0            | R/W-0, HCS        | R/W-0, HCS |

| SSRC2               | SSRC1         | SSRC0                            | _                  | —                 | ASAM             | SAMP              | DONE       |

| bit 7               |               |                                  |                    |                   |                  |                   | bit 0      |

|                     |               |                                  |                    |                   |                  |                   |            |

| Legend:             |               | HCS = Hardw                      | are Clearable/     | Settable bit      |                  |                   |            |

| R = Readable        | e bit         | W = Writable                     | bit                | U = Unimplem      | nented bit, read | d as '0'          |            |

| -n = Value at       | POR           | '1' = Bit is set                 |                    | '0' = Bit is clea | ared             | x = Bit is unkn   | iown       |

|                     |               |                                  |                    |                   |                  |                   |            |

| bit 15              | ADON: A/D C   | perating Mode                    | bit <sup>(1)</sup> |                   |                  |                   |            |

|                     |               | verter module is                 | operating          |                   |                  |                   |            |

|                     | 0 = A/D Conv  | erter is off                     |                    |                   |                  |                   |            |

| bit 14              | Unimplemen    | ted: Read as '                   | )'                 |                   |                  |                   |            |

| bit 13              |               | o in Idle Mode I                 |                    |                   |                  |                   |            |

|                     |               |                                  |                    | evice enters Idle | e mode           |                   |            |

| h:: 40.40           |               | module operat                    |                    | le                |                  |                   |            |

| bit 12-10           | -             | ted: Read as '                   |                    |                   |                  |                   |            |

| bit 9-8             |               | Data Output Fo                   |                    |                   |                  |                   |            |

|                     |               | ractional (sddd<br>al (dddd dddd |                    |                   |                  |                   |            |

|                     |               | nteger (ssss                     |                    |                   |                  |                   |            |

|                     |               | b 5500 0000                      |                    | ,                 |                  |                   |            |

| bit 7-5             | SSRC<2:0>:    | Conversion Tri                   | gger Source So     | elect bits        |                  |                   |            |

|                     |               |                                  |                    | starts conversio  | on (auto-conve   | rt)               |            |

|                     |               | event ends sar                   | npling and star    | ts conversion     |                  |                   |            |

|                     | 101 = Reserv  |                                  | sampling and       | starts conversi   | on               |                   |            |

|                     | 011 = Reserv  | -                                | oumphing und       |                   |                  |                   |            |

|                     |               |                                  |                    | starts conversi   |                  |                   |            |

|                     |               |                                  |                    | ampling and sta   |                  |                   |            |

| h:: 4 0             |               | -                                |                    | nd starts conver  | sion             |                   |            |

| bit 4-3             | -             | ted: Read as '                   |                    |                   |                  |                   |            |

| bit 2               |               | ample Auto-Sta                   |                    | conversion co     | moletes SAM      | ⊃ bit is auto-set |            |

|                     |               | begins when S                    |                    |                   |                  |                   |            |

| bit 1               |               | ample Enable                     |                    |                   |                  |                   |            |

|                     | 1 = A/D samp  | le/hold amplifie                 | er is sampling i   | nput              |                  |                   |            |

|                     | 0 = A/D samp  | le/hold amplifie                 | er is holding      |                   |                  |                   |            |

| bit 0               | DONE: A/D C   | conversion Stat                  | us bit             |                   |                  |                   |            |

|                     |               | ersion is done                   |                    |                   |                  |                   |            |

|                     | 0 = A/D conve | ersion is NOT c                  | one                |                   |                  |                   |            |

| Note 1: Va          | lues of ADC1B | UFx registers v                  | vill not retain th | eir values once   | e the ADON bit   | is cleared. Rea   | ad out the |

#### REGISTER 22-1: AD1CON1: A/D CONTROL REGISTER 1

**Note 1:** Values of ADC1BUFx registers will not retain their values once the ADON bit is cleared. Read out the conversion values from the buffer before disabling the module.

### 27.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers and dsPIC<sup>®</sup> digital signal controllers are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Compilers/Assemblers/Linkers

- MPLAB C Compiler for Various Device Families

- HI-TECH C for Various Device Families

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers

- MPLAB ICD 3

- PICkit™ 3 Debug Express

- Device Programmers

- PICkit<sup>™</sup> 2 Programmer

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits, and Starter Kits

### 27.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16/32-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup> operating system-based application that contains:

- A single graphical interface to all debugging tools

- Simulator

- Programmer (sold separately)

- In-Circuit Emulator (sold separately)

- In-Circuit Debugger (sold separately)

- A full-featured editor with color-coded context

- A multiple project manager

- Customizable data windows with direct edit of contents

- High-level source code debugging

- · Mouse over variable inspection

- Drag and drop variables from source to watch windows

- · Extensive on-line help

- Integration of select third party tools, such as IAR C Compilers

The MPLAB IDE allows you to:

- Edit your source files (either C or assembly)

- One-touch compile or assemble, and download to emulator and simulator tools (automatically updates all project information)

- Debug using:

- Source files (C or assembly)

- Mixed C and assembly

- Machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost-effective simulators, through low-cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increased flexibility and power.

100-Lead TQFP (14x14x1 mm)

| Legend | : XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>* | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator (e3)<br>can be found on the outer packaging for this package. |

|--------|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note:  | be carrie                                | nt the full Microchip part number cannot be marked on one line, it will<br>d over to the next line, thus limiting the number of available<br>s for customer-specific information.                                                                                                                                                                                            |

### INDEX

| 4 |   |

|---|---|

|   |   |

|   | 4 |

| A/D Converter                           |     |

|-----------------------------------------|-----|

| Analog Input Model                      |     |

| Transfer Function                       |     |

| AC Characteristics                      |     |

| ADC Conversion Timing                   | 326 |

| CLKO and I/O Timing                     | 324 |

| Alternate Interrupt Vector Table (AIVT) | 77  |

| Assembler                               |     |

| MPASM Assembler                         | 300 |

### В

| Block Diagrams                                                                  |     |

|---------------------------------------------------------------------------------|-----|

| 10-Bit High-Speed A/D Converter                                                 | 268 |

| 16-Bit Asynchronous Timer3 and Timer5                                           |     |

| 16-Bit Synchronous Timer2 and Timer4                                            | 165 |

| 16-Bit Timer1 Module                                                            | 161 |

| 32-Bit Timer2/3 and Timer4/5                                                    |     |

| Accessing Program Space Using Table                                             |     |