Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 32MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB OTG                                      |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                      |

| Number of I/O              | 51                                                                              |

| Program Memory Size        | 256КВ (85.5К х 24)                                                              |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-TQFP                                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj256gb106t-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2.4 Voltage Regulator Pins (ENVREG/DISVREG and VCAP/VDDCORE)

| Note: | This secti | on applies   | only | to | PIC24FJ |

|-------|------------|--------------|------|----|---------|

|       |            | th an on-chi |      |    |         |

The on-chip voltage regulator enable/disable pin (ENVREG or DISVREG, depending on the device family) must always be connected directly to either a supply voltage or to ground. The particular connection is determined by whether or not the regulator is to be used:

- For ENVREG, tie to VDD to enable the regulator, or to ground to disable the regulator

- For DISVREG, tie to ground to enable the regulator or to VDD to disable the regulator

Refer to **Section 26.2** "**On-Chip Voltage Regulator**" for details on connecting and using the on-chip regulator.

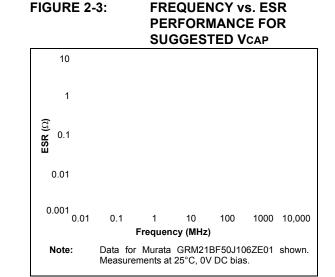

When the regulator is enabled, a low-ESR (<5 $\Omega$ ) capacitor is required on the VCAP/VDDCORE pin to stabilize the voltage regulator output voltage. The VCAP/VDDCORE pin must not be connected to VDD, and must use a capacitor of 10  $\mu$ F connected to ground. The type can be ceramic or tantalum. A suitable example is the Murata GRM21BF50J106ZE01 (10  $\mu$ F, 6.3V) or equivalent. Designers may use Figure 2-3 to evaluate ESR equivalence of candidate devices.

The placement of this capacitor should be close to VCAP/VDDCORE. It is recommended that the trace length not exceed 0.25 inch (6 mm). Refer to **Section 29.0 "Electrical Characteristics"** for additional information.

When the regulator is disabled, the VCAP/VDDCORE pin must be tied to a voltage supply at the VDDCORE level. Refer to **Section 29.0 "Electrical Characteristics"** for information on VDD and VDDCORE.

### 2.5 ICSP Pins

The PGECx and PGEDx pins are used for In-Circuit Serial Programming (ICSP) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of ohms, not to exceed  $100\Omega$ .

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

For device emulation, ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to the Microchip debugger/emulator tool.

For more information on available Microchip development tools connection requirements, refer to **Section 27.0 "Development Support"**.

### 4.0 MEMORY ORGANIZATION

As Harvard architecture devices, PIC24F microcontrollers feature separate program and data memory spaces and busses. This architecture also allows the direct access of program memory from the data space during code execution.

### 4.1 **Program Address Space**

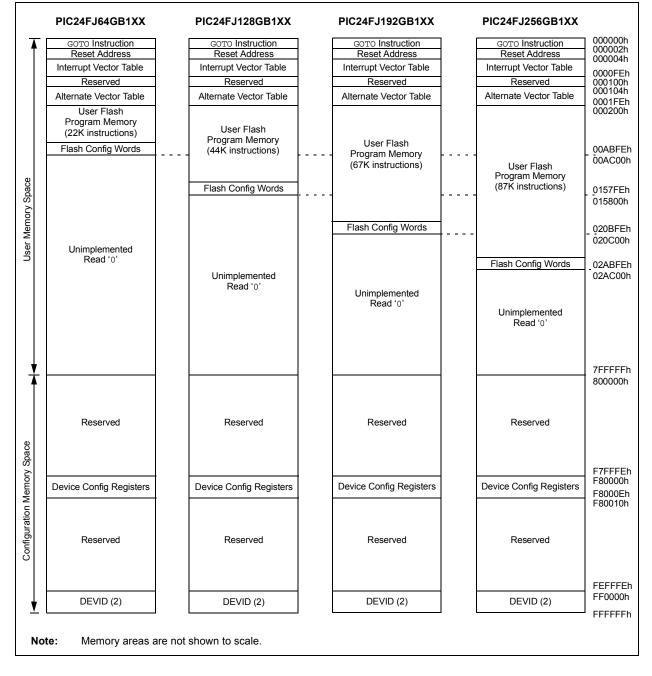

The program address memory space of the PIC24FJ256GB110 family devices is 4M instructions. The space is addressable by a 24-bit value derived

from either the 23-bit Program Counter (PC) during program execution, or from table operation or data space remapping, as described in **Section 4.3 "Interfacing Program and Data Memory Spaces"**.

User access to the program memory space is restricted to the lower half of the address range (000000h to 7FFFFFh). The exception is the use of TBLRD/TBLWT operations which use TBLPAG<7> to permit access to the Configuration bits and Device ID sections of the configuration memory space.

Memory maps for the PIC24FJ256GB110 family of devices are shown in Figure 4-1.

#### 4.3.2 DATA ACCESS FROM PROGRAM MEMORY USING TABLE **INSTRUCTIONS**

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the program space without going through data space. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a program space word as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to data space addresses. Program memory can thus be regarded as two, 16-bit word-wide address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space which contains the least significant data word, and TBLRDH and TBLWTH access the space which contains the upper data byte.

Two table instructions are provided to move byte or word-sized (16-bit) data to and from program space. Both function as either byte or word operations.

TBLRDL (Table Read Low): In Word mode, it 1. maps the lower word of the program space location (P<15:0>) to a data address (D<15:0>). In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when byte select is '1'; the lower byte is selected when it is '0'.

2. TBLRDH (Table Read High): In Word mode, it maps the entire upper word of a program address (P<23:16>) to a data address. Note that D<15:8>, the 'phantom' byte, will always be '0'. In Byte mode, it maps the upper or lower byte of the program word to D<7:0> of the data address, as above. Note that the data will always be '0' when the upper 'phantom' byte is selected (byte select = 1).

In a similar fashion, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a program space address. The details of their operation are explained in Section 5.0 "Flash Program Memory".

For all table operations, the area of program memory space to be accessed is determined by the Table Memory Page Address register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

Note: Only table read operations will execute in the configuration memory space, and only then, in implemented areas such as the Device ID. Table write operations are not allowed.

| FIGURE 4-6:             | ACCESSING PROGRAM MEMORY WITH TABLE INSTRUCTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         | Program Space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 782, <i>894%</i><br>(82 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                         | 23       15       6       6000000       23       16       8       0         0200000       00000000       00000000       00000000       00000000       00000000       00000000         0200000       00000000       00000000       00000000       00000000       00000000         0200000       00000000       00000000       00000000       00000000       00000000         0200000       00000000       00000000       00000000       00000000       00000000         0200000       00000000       00000000       00000000       00000000       00000000         0200000       00000000       00000000       00000000       00000000       0000000         0200000       00000000       00000000       00000000       00000000       0000000         0200000       0000000       0000000       0000000       0000000       0000000         0200000       0000000       0000000       0000000       0000000       0000000         0200000       0000000       00000000       00000000       00000000       0000000         02000000       00000000       000000000       00000000       00000000       00000000         02000000       00000000       00000000 |

© 2009 Microchip Technology Inc.

| R/W-0, H   | S R/W-0, HS                                                 | U-0                                                                  | U-0                                 | U-0                  | U-0               | R/W-0, HS        | R/W-0         |

|------------|-------------------------------------------------------------|----------------------------------------------------------------------|-------------------------------------|----------------------|-------------------|------------------|---------------|

| TRAPR      | IOPUWR                                                      | —                                                                    | _                                   |                      |                   | СМ               | PMSLP         |

| bit 15     |                                                             |                                                                      |                                     |                      |                   |                  | bit 8         |

| R/W-0, H   | S R/W-0, HS                                                 | R/W-0                                                                | R/W-0, HS                           | R/W-0, HS            | R/W-0, HS         | R/W-1, HS        | R/W-1, HS     |

| EXTR       | SWR                                                         | SWDTEN <sup>(2)</sup>                                                | WDTO                                | SLEEP                | IDLE              | BOR              | POR           |

| bit 7      |                                                             |                                                                      |                                     |                      |                   |                  | bit 0         |

| Legend:    |                                                             | HS = Hardwar                                                         | e settable bit                      |                      |                   |                  |               |

| R = Reada  | ble bit                                                     | W = Writable I                                                       |                                     | U = Unimplem         | nented bit, read  | as '0'           |               |

| -n = Value |                                                             | '1' = Bit is set                                                     |                                     | '0' = Bit is clea    |                   | x = Bit is unkn  | iown          |

| bit 15     | 1 = A Trap Co                                               | Reset Flag bit<br>onflict Reset has                                  |                                     |                      |                   |                  |               |

| bit 14     | <b>IOPUWR:</b> Illegal<br>1 = An illegal<br>Pointer ca      | gal Opcode or I<br>opcode detecti<br>aused a Reset<br>opcode or unir | Jninitialized W<br>on, an illegal a | ddress mode o        | r uninitialized V | √ register used  | as an Address |

| bit 13-10  | -                                                           | ted: Read as '0                                                      |                                     |                      |                   |                  |               |

| bit 9      | -                                                           | ation Word Misi                                                      |                                     | lag bit              |                   |                  |               |

|            | 1 = A Configu                                               | ration Word Mis<br>ration Word Mis                                   | smatch Reset I                      | has occurred         | d                 |                  |               |

| bit 8      | 1 = Program r                                               | ram Memory P<br>memory bias vo<br>nemory bias volta                  | ltage remains                       | powered during       |                   | regulator enters | Standby mode. |

| bit 7      | EXTR: Extern<br>1 = A Master                                | al Reset (MCLI<br>Clear (pin) Res<br>Clear (pin) Res                 | R) Pin bit<br>et has occurre        | d                    |                   |                  | 2             |

| bit 6      | <b>SWR:</b> Softwar<br>1 = A RESET i                        | re Reset (Instru<br>instruction has<br>instruction has               | ction) Flag bit<br>been executed    | l                    |                   |                  |               |

| bit 5      | <b>SWDTEN:</b> So<br>1 = WDT is er<br>0 = WDT is di         |                                                                      | Disable of WD                       | T bit <sup>(2)</sup> |                   |                  |               |

| bit 4      | 1 = WDT time                                                | ndog Timer Tim<br>-out has occurr<br>-out has not oc                 | ed                                  |                      |                   |                  |               |

| bit 3      | 1 = Device ha                                               | e From Sleep F<br>Is been in Sleep<br>Is not been in S               | mode                                |                      |                   |                  |               |

| bit 2      | IDLE: Wake-u<br>1 = Device ha                               | up From Idle Fla<br>is been in Idle r<br>is not been in Id           | ag bit<br>node                      |                      |                   |                  |               |

| bit 1      | <b>BOR:</b> Brown-0                                         | out Reset Flag<br>out Reset has o<br>out Reset has n                 | bit<br>ccurred. Note                | that BOR is als      | o set after a Po  | ower-on Reset.   |               |

| bit 0      | <b>POR:</b> Power-u                                         | on Reset Flag b<br>up Reset has or<br>up Reset has no                | bit<br>ccurred                      |                      |                   |                  |               |

|            | All of the Reset st<br>cause a device Re<br>If the FWDTEN C | eset.                                                                |                                     |                      | -                 |                  |               |

### REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup>

| REGISTER     | 7-6: IFS1:                            | INTERRUPT                                                | FLAG STAT                | US REGISTE        | ER 1            |                 |         |

|--------------|---------------------------------------|----------------------------------------------------------|--------------------------|-------------------|-----------------|-----------------|---------|

| R/W-0        | R/W-0                                 | R/W-0                                                    | R/W-0                    | R/W-0             | R/W-0           | R/W-0           | U-0     |

| U2TXIF       | U2RXIF                                | INT2IF                                                   | T5IF                     | T4IF              | OC4IF           | OC3IF           | _       |

| bit 15       |                                       | •                                                        |                          |                   |                 |                 | bit 8   |

| R/W-0        | R/W-0                                 | U-0                                                      | R/W-0                    | R/W-0             | R/W-0           | R/W-0           | R/W-0   |

| IC8IF        | IC7IF                                 | _                                                        | INT1IF                   | CNIF              | CMIF            | MI2C1IF         | SI2C1IF |

| bit 7        |                                       |                                                          |                          |                   |                 |                 | bit 0   |

| Legend:      |                                       |                                                          |                          |                   |                 |                 |         |

| R = Readab   | le bit                                | W = Writable I                                           | oit                      | U = Unimplen      | nented bit, rea | d as '0'        |         |

| -n = Value a | t POR                                 | '1' = Bit is set                                         |                          | '0' = Bit is clea | ared            | x = Bit is unkr | nown    |

| bit 15       | 1 = Interrupt                         | RT2 Transmitter<br>request has occ<br>request has not    | urred                    | Status bit        |                 |                 |         |

| bit 14       | 1 = Interrupt                         | RT2 Receiver In<br>request has occ<br>request has not    | urred                    | tatus bit         |                 |                 |         |

| bit 13       | 1 = Interrupt                         | rnal Interrupt 2 F<br>request has occ<br>request has not | urred                    |                   |                 |                 |         |

| bit 12       | 1 = Interrupt                         | Interrupt Flag S<br>request has occ<br>request has not   | urred                    |                   |                 |                 |         |

| bit 11       | 1 = Interrupt                         | Interrupt Flag S<br>request has occ<br>request has not   | urred                    |                   |                 |                 |         |

| bit 10       | 1 = Interrupt                         | ut Compare Cha<br>request has occ<br>request has not     | urred                    | pt Flag Status I  | bit             |                 |         |

| bit 9        | 1 = Interrupt                         | ut Compare Cha<br>request has occ<br>request has not     | urred                    | pt Flag Status I  | bit             |                 |         |

| bit 8        | Unimplemen                            | ted: Read as 'o                                          | )'                       |                   |                 |                 |         |

| bit 7        | 1 = Interrupt                         | Capture Channe<br>request has occ<br>request has not     | urred                    | lag Status bit    |                 |                 |         |

| bit 6        | 1 = Interrupt                         | Capture Channe<br>request has occ<br>request has not     | urred                    | lag Status bit    |                 |                 |         |

| bit 5        | Unimplemen                            | ted: Read as 'o                                          | )'                       |                   |                 |                 |         |

| bit 4        | 1 = Interrupt                         | nal Interrupt 1 F<br>request has occ<br>request has not  | urred                    |                   |                 |                 |         |

| bit 3        | <b>CNIF:</b> Input C<br>1 = Interrupt | Change Notificat<br>request has occ<br>request has not   | ion Interrupt F<br>urred | lag Status bit    |                 |                 |         |

| bit 2        | 1 = Interrupt                         | arator Interrupt<br>request has occ<br>request has not   | urred                    |                   |                 |                 |         |

| bit 1        | 1 = Interrupt                         | ster I2C1 Event<br>request has occ<br>request has not    | urred                    | Status bit        |                 |                 |         |

| bit 0        | 1 = Interrupt                         | ve I2C1 Event In<br>request has occ<br>request has not   | urred                    | Status bit        |                 |                 |         |

| U-0          | R/W-0         | U-0                                    | U-0            | U-0              | U-0             | U-0              | U-0   |

|--------------|---------------|----------------------------------------|----------------|------------------|-----------------|------------------|-------|

| —            | RTCIF         | —                                      | _              | —                |                 | _                | _     |

| bit 15       |               |                                        |                |                  |                 |                  | bit 8 |

|              |               |                                        |                |                  |                 |                  |       |

| U-0          | R/W-0         | R/W-0                                  | U-0            | U-0              | R/W-0           | R/W-0            | U-0   |

| —            | INT4IF        | INT3IF                                 | —              | _                | MI2C2IF         | SI2C2IF          | —     |

| bit 7        |               |                                        |                |                  |                 |                  | bit 0 |

|              |               |                                        |                |                  |                 |                  |       |

| Legend:      |               |                                        |                |                  |                 |                  |       |

| R = Readab   | ole bit       | W = Writable b                         | it             | U = Unimpler     | mented bit, rea | d as '0'         |       |

| -n = Value a | at POR        | '1' = Bit is set                       |                | '0' = Bit is cle | ared            | x = Bit is unkno | own   |

|              |               |                                        |                |                  |                 |                  |       |

| pit 15       | -             | nted: Read as '0                       |                |                  |                 |                  |       |

| bit 14       |               | -Time Clock/Cale                       | •              | ot Flag Status b | it              |                  |       |

|              |               | request has occu                       |                |                  |                 |                  |       |

|              | -             | request has not                        |                |                  |                 |                  |       |

| oit 13-7     | •             | nted: Read as '0                       |                |                  |                 |                  |       |

| oit 6        |               | rnal Interrupt 4 F<br>request has occu |                |                  |                 |                  |       |

|              |               | request has occur                      |                |                  |                 |                  |       |

| oit 5        | •             | rnal Interrupt 3 F                     |                |                  |                 |                  |       |

|              |               | request has occu                       | 0              |                  |                 |                  |       |

|              |               | request has not                        |                |                  |                 |                  |       |

| oit 4-3      | Unimplemer    | ted: Read as '0                        | ,              |                  |                 |                  |       |

| bit 2        | MI2C2IF: Ma   | ster I2C2 Event                        | Interrupt Flag | Status bit       |                 |                  |       |

|              | 1 = Interrupt | request has occu                       | urred          |                  |                 |                  |       |

|              | 0 = Interrupt | request has not                        | occurred       |                  |                 |                  |       |

| pit 1        | SI2C2IF: Sla  | ve I2C2 Event In                       | terrupt Flag S | Status bit       |                 |                  |       |

|              |               | request has occu                       |                |                  |                 |                  |       |

|              | •             | request has not                        |                |                  |                 |                  |       |

| oit 0        | Unimplemer    | nted: Read as '0                       | ,              |                  |                 |                  |       |

### REGISTER 7-8: IFS3: INTERRUPT FLAG STATUS REGISTER 3

| U-0           | R/W-1                                                                                                                     | R/W-0                                   | R/W-0            | U-0                 | R/W-1            | R/W-0           | R/W-0  |  |  |  |  |

|---------------|---------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|------------------|---------------------|------------------|-----------------|--------|--|--|--|--|

| —             | OC7IP2                                                                                                                    | OC7IP1                                  | OC7IP0           |                     | OC6IP2           | OC6IP1          | OC6IP0 |  |  |  |  |

| bit 15        |                                                                                                                           |                                         |                  |                     |                  | 1               | bit    |  |  |  |  |

|               |                                                                                                                           |                                         |                  |                     |                  |                 |        |  |  |  |  |

| U-0           | R/W-1                                                                                                                     | R/W-0                                   | R/W-0            | U-0                 | R/W-1            | R/W-0           | R/W-0  |  |  |  |  |

| —             | OC5IP2                                                                                                                    | OC5IP1                                  | OC5IP0           | —                   | IC6IP2           | IC6IP1          | IC6IP0 |  |  |  |  |

| bit 7         |                                                                                                                           |                                         |                  |                     |                  |                 | bit    |  |  |  |  |

| Legend:       |                                                                                                                           |                                         |                  |                     |                  |                 |        |  |  |  |  |

| R = Readable  | e hit                                                                                                                     | W = Writable I                          | nit              | U = Unimpler        | mented bit, read | d as '0'        |        |  |  |  |  |

| -n = Value at |                                                                                                                           | '1' = Bit is set                        |                  | '0' = Bit is cle    |                  | x = Bit is unkr | own    |  |  |  |  |

|               |                                                                                                                           |                                         |                  |                     |                  |                 | 101111 |  |  |  |  |

| bit 15        | Unimplemer                                                                                                                | nted: Read as '0                        | )'               |                     |                  |                 |        |  |  |  |  |

| bit 14-12     | OC7IP<2:0>                                                                                                                | : Output Compa                          | re Channel 7     | Interrupt Priorit   | y bits           |                 |        |  |  |  |  |

|               | 111 = Interru                                                                                                             | pt is priority 7 (h                     | nighest priority | interrupt)          |                  |                 |        |  |  |  |  |

|               | •                                                                                                                         |                                         |                  |                     |                  |                 |        |  |  |  |  |

|               |                                                                                                                           |                                         |                  |                     |                  |                 |        |  |  |  |  |

|               | 001 = Interrupt is priority 1                                                                                             |                                         |                  |                     |                  |                 |        |  |  |  |  |

|               |                                                                                                                           | pt source is disa                       | abled            |                     |                  |                 |        |  |  |  |  |

| bit 11        | Unimplemer                                                                                                                | nted: Read as 'o                        | )'               |                     |                  |                 |        |  |  |  |  |

| bit 10-8      | OC6IP<2:0>: Output Compare Channel 6 Interrupt Priority bits                                                              |                                         |                  |                     |                  |                 |        |  |  |  |  |

|               | 111 = Interrupt is priority 7 (highest priority interrupt)                                                                |                                         |                  |                     |                  |                 |        |  |  |  |  |

|               | •                                                                                                                         |                                         |                  |                     |                  |                 |        |  |  |  |  |

|               | •                                                                                                                         |                                         |                  |                     |                  |                 |        |  |  |  |  |

|               | 001 = Interrupt is priority 1                                                                                             |                                         |                  |                     |                  |                 |        |  |  |  |  |

|               |                                                                                                                           | pt source is disa                       |                  |                     |                  |                 |        |  |  |  |  |

| bit 7         | -                                                                                                                         | nted: Read as '0                        |                  |                     |                  |                 |        |  |  |  |  |

| bit 6-4       | OC5IP<2:0>: Output Compare Channel 5 Interrupt Priority bits                                                              |                                         |                  |                     |                  |                 |        |  |  |  |  |

|               | 111 = Interrupt is priority 7 (highest priority interrupt)                                                                |                                         |                  |                     |                  |                 |        |  |  |  |  |

|               | •                                                                                                                         |                                         |                  |                     |                  |                 |        |  |  |  |  |

|               | •                                                                                                                         |                                         |                  |                     |                  |                 |        |  |  |  |  |

|               | 001 = Interrupt is priority 1<br>000 = Interrupt source is disabled                                                       |                                         |                  |                     |                  |                 |        |  |  |  |  |

| bit 3         |                                                                                                                           | -                                       |                  |                     |                  |                 |        |  |  |  |  |

| 011.5         | -                                                                                                                         | nted: Read as '0                        |                  | www.et Deieniterbit | -                |                 |        |  |  |  |  |

|               | IC6IP<2:0>: Input Capture Channel 6 Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt) |                                         |                  |                     |                  |                 |        |  |  |  |  |

| bit 2-0       | 111 – Intorru                                                                                                             | int is priority 7 (k                    | naboet priority  |                     |                  |                 |        |  |  |  |  |

|               | 111 = Interru<br>•                                                                                                        | pt is priority 7 (h                     | nighest priority | (interrupt)         |                  |                 |        |  |  |  |  |

|               | 111 = Interru<br>•                                                                                                        | ıpt is priority 7 (ł                    | nighest priority | (interrupt)         |                  |                 |        |  |  |  |  |

|               | •<br>•<br>•                                                                                                               | pt is priority 7 (h<br>pt is priority 1 | nighest priority | (interrupt)         |                  |                 |        |  |  |  |  |

### © 2009 Microchip Technology Inc.

### REGISTER 10-21: RPINR29: PERIPHERAL PIN SELECT INPUT REGISTER 29

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   |     | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| —     | —   | SS3R5 | SS3R4 | SS3R3 | SS3R2 | SS3R1 | SS3R0 |

| bit 7 |     |       |       |       |       |       | bit 0 |

| Legend:           |                  |                                               |                    |  |  |

|-------------------|------------------|-----------------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | itable bit U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                          | x = Bit is unknown |  |  |

bit 15-6 Unimplemented: Read as '0'

bit 5-0 SS3R<5:0>: Assign SPI3 Slave Select Input (SS31IN) to Corresponding RPn or RPIn Pin bits

### REGISTER 10-22: RPOR0: PERIPHERAL PIN SELECT OUTPUT REGISTER 0

| U-0           | U-0   | R/W-0            | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

|---------------|-------|------------------|-------|-----------------------------------------|-------|-------|-------|

| _             | _     | RP1R5            | RP1R4 | RP1R3                                   | RP1R2 | RP1R1 | RP1R0 |

| bit 15        |       |                  |       | ·                                       |       | •     | bit 8 |

|               |       |                  |       |                                         |       |       |       |

| U-0           | U-0   | R/W-0            | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

| _             | _     | RP0R5            | RP0R4 | RP0R3                                   | RP0R2 | RP0R1 | RP0R0 |

| bit 7         |       |                  |       | ·                                       |       | •     | bit 0 |

|               |       |                  |       |                                         |       |       |       |

| Legend:       |       |                  |       |                                         |       |       |       |

| R = Readable  | e bit | W = Writable I   | oit   | U = Unimplemented bit, read as '0'      |       |       |       |

| -n = Value at | POR   | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |       |       | nown  |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP1R<5:0>:** RP1 Output Pin Mapping bits Peripheral output number n is assigned to pin, RP1 (see Table 10-3 for peripheral function numbers)

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **RP0R<5:0>:** RP0 Output Pin Mapping bits Peripheral output number n is assigned to pin, RP0 (see Table 10-3 for peripheral function numbers)

| U-0                               | U-0 | R/W-0            | R/W-0                              | R/W-0  | R/W-0                | R/W-0  | R/W-0              |  |

|-----------------------------------|-----|------------------|------------------------------------|--------|----------------------|--------|--------------------|--|

| —                                 |     | RP27R5           | RP27R4                             | RP27R3 | RP27R2               | RP27R1 | RP27R0             |  |

| bit 15                            |     |                  |                                    |        |                      |        | bit 8              |  |

|                                   |     |                  |                                    |        |                      |        |                    |  |

| U-0                               | U-0 | R/W-0            | R/W-0                              | R/W-0  | R/W-0                | R/W-0  | R/W-0              |  |

| —                                 | —   | RP26R5           | RP26R4                             | RP26R3 | RP26R2               | RP26R1 | RP26R0             |  |

| bit 7                             |     |                  |                                    |        |                      |        | bit 0              |  |

|                                   |     |                  |                                    |        |                      |        |                    |  |

| Legend:                           |     |                  |                                    |        |                      |        |                    |  |

| R = Readable bit W = Writable bit |     | oit              | U = Unimplemented bit, read as '0' |        |                      |        |                    |  |

| -n = Value at POR                 |     | '1' = Bit is set | '1' = Bit is set                   |        | '0' = Bit is cleared |        | x = Bit is unknown |  |

### REGISTER 10-35: RPOR13: PERIPHERAL PIN SELECT OUTPUT REGISTER 13

bit 15-14 Unimplemented: Read as '0'

- bit 13-8

RP27R<5:0>: RP27 Output Pin Mapping bits

Peripheral output number n is assigned to pin, RP27 (see Table 10-3 for peripheral function numbers)

bit 7-6

Unimplemented: Read as '0'

- bit 5-0 **RP26R<5:0>:** RP26 Output Pin Mapping bits Peripheral output number n is assigned to pin, RP26 (see Table 10-3 for peripheral function numbers)

### REGISTER 10-36: RPOR14: PERIPHERAL PIN SELECT OUTPUT REGISTER 14

| U-0                        | U-0 | R/W-0        | R/W-0                                  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|----------------------------|-----|--------------|----------------------------------------|--------|--------|--------|--------|

| _                          | _   | RP29R5       | RP29R4                                 | RP29R3 | RP29R2 | RP29R1 | RP29R0 |

| bit 15                     |     |              |                                        |        |        |        | bit 8  |

|                            |     |              |                                        |        |        |        |        |

| U-0                        | U-0 | R/W-0        | R/W-0                                  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

| —                          | _   | RP28R5       | RP28R4                                 | RP28R3 | RP28R2 | RP28R1 | RP28R0 |

| bit 7                      |     |              |                                        |        |        |        | bit 0  |

|                            |     |              |                                        |        |        |        |        |

| Legend:                    |     |              |                                        |        |        |        |        |

| R = Readable bit W = Writa |     | W = Writable | bit U = Unimplemented bit, read as '0' |        |        |        |        |

|                            |     |              |                                        |        |        |        |        |

'0' = Bit is cleared

bit 15-14 Unimplemented: Read as '0'

'1' = Bit is set

bit 13-8 **RP29R<5:0>:** RP29 Output Pin Mapping bits Peripheral output number n is assigned to pin, RP29 (see Table 10-3 for peripheral function numbers)

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **RP28R<5:0>:** RP28 Output Pin Mapping bits Peripheral output number n is assigned to pin, RP28 (see Table 10-3 for peripheral function numbers)

-n = Value at POR

x = Bit is unknown

| R/W-0        | U-0                                                                                   | R/W-0                              | U-0             | U-0              | U-0              | U-0              | U-0 |  |  |  |  |

|--------------|---------------------------------------------------------------------------------------|------------------------------------|-----------------|------------------|------------------|------------------|-----|--|--|--|--|

| TON          |                                                                                       | TSIDL                              |                 |                  |                  |                  | —   |  |  |  |  |

| bit 15       |                                                                                       |                                    |                 |                  |                  |                  | bit |  |  |  |  |

|              |                                                                                       |                                    |                 |                  |                  |                  |     |  |  |  |  |

| U-0          | R/W-0                                                                                 | R/W-0                              | R/W-0           | U-0              | R/W-0            | R/W-0            | U-0 |  |  |  |  |

| _            | TGATE                                                                                 | TCKPS1                             | TCKPS0          | —                | TSYNC            | TCS              |     |  |  |  |  |

| bit 7        |                                                                                       |                                    |                 |                  |                  |                  | bit |  |  |  |  |

| Legend:      |                                                                                       |                                    |                 |                  |                  |                  |     |  |  |  |  |

| R = Readab   | le bit                                                                                | W = Writable                       | bit             | U = Unimpler     | mented bit, read | l as '0'         |     |  |  |  |  |

| -n = Value a | t POR                                                                                 | '1' = Bit is set                   |                 | '0' = Bit is cle |                  | x = Bit is unkno | own |  |  |  |  |

|              |                                                                                       |                                    |                 |                  |                  |                  |     |  |  |  |  |

| bit 15       | TON: Timer1                                                                           |                                    |                 |                  |                  |                  |     |  |  |  |  |

|              | 1 = Starts 16<br>0 = Stops 16                                                         |                                    |                 |                  |                  |                  |     |  |  |  |  |

| bit 14       | -                                                                                     | ted: Read as '                     | o'              |                  |                  |                  |     |  |  |  |  |

| bit 13       | -                                                                                     | in Idle Mode bit                   |                 |                  |                  |                  |     |  |  |  |  |

|              | 1 = Discontinue module operation when device enters Idle mode                         |                                    |                 |                  |                  |                  |     |  |  |  |  |

|              | 0 = Continue                                                                          | module operat                      | ion in Idle mod | le               |                  |                  |     |  |  |  |  |

| bit 12-7     | Unimplemer                                                                            | nted: Read as '                    | o'              |                  |                  |                  |     |  |  |  |  |

| bit 6        | TGATE: Time                                                                           | er1 Gated Time                     | Accumulation    | Enable bit       |                  |                  |     |  |  |  |  |

|              | When TCS = 1:<br>This hit is imported                                                 |                                    |                 |                  |                  |                  |     |  |  |  |  |

|              | This bit is ignored.<br><u>When TCS = 0:</u>                                          |                                    |                 |                  |                  |                  |     |  |  |  |  |

|              | 1 = Gated time accumulation enabled                                                   |                                    |                 |                  |                  |                  |     |  |  |  |  |

|              |                                                                                       | me accumulatio                     |                 |                  |                  |                  |     |  |  |  |  |

| bit 5-4      | TCKPS<1:0>                                                                            | : Timer1 Input                     | Clock Prescale  | e Select bits    |                  |                  |     |  |  |  |  |

|              | 11 = 1:256                                                                            |                                    |                 |                  |                  |                  |     |  |  |  |  |

|              | 10 = 1:64<br>01 = 1:8                                                                 |                                    |                 |                  |                  |                  |     |  |  |  |  |

|              | 01 - 1.0<br>00 = 1.1                                                                  |                                    |                 |                  |                  |                  |     |  |  |  |  |

| bit 3        | Unimplemer                                                                            | nted: Read as '                    | o'              |                  |                  |                  |     |  |  |  |  |

| bit 2        | -                                                                                     |                                    |                 | hronization Sel  | lect bit         |                  |     |  |  |  |  |

|              | <b>TSYNC:</b> Timer1 External Clock Input Synchronization Select bit<br>When TCS = 1: |                                    |                 |                  |                  |                  |     |  |  |  |  |

|              | 1 = Synchronize external clock input                                                  |                                    |                 |                  |                  |                  |     |  |  |  |  |

|              | 0 = Do not synchronize external clock input                                           |                                    |                 |                  |                  |                  |     |  |  |  |  |

|              | When TCS =                                                                            |                                    |                 |                  |                  |                  |     |  |  |  |  |

| L:1 4        | This bit is ign                                                                       |                                    | Calaat hit      |                  |                  |                  |     |  |  |  |  |

| bit 1        |                                                                                       | Clock Source S<br>I clock from T10 |                 | riging odgo)     |                  |                  |     |  |  |  |  |

|              |                                                                                       | clock (Fosc/2)                     |                 | rising edge)     |                  |                  |     |  |  |  |  |

|              | Unimplemented: Read as '0'                                                            |                                    |                 |                  |                  |                  |     |  |  |  |  |

## REGISTER 11-1: T1CON: TIMER1 CONTROL REGISTER<sup>(1)</sup>

**Note 1:** Changing the value of TxCON while the timer is running (TON = 1) causes the timer prescale counter reset and is not recommended.

| U-0                | U-0                                  | U-0                              | R/W-0                                 | R/W-0                 | R/W-0                  | R/W-0              | R/W-0              |

|--------------------|--------------------------------------|----------------------------------|---------------------------------------|-----------------------|------------------------|--------------------|--------------------|

|                    | _                                    | _                                | DISSCK <sup>(1)</sup>                 | DISSDO <sup>(2)</sup> | MODE16                 | SMP                | CKE <sup>(3)</sup> |

| bit 15             |                                      |                                  |                                       |                       |                        |                    | bit                |

| R/W-0              | R/W-0                                | R/W-0                            | R/W-0                                 | R/W-0                 | R/W-0                  | R/W-0              | R/W-0              |

| SSEN <sup>(4</sup> | -                                    | MSTEN                            | SPRE2                                 | SPRE1                 | SPRE0                  | PPRE1              | PPRE0              |

| bit 7              |                                      |                                  |                                       |                       |                        |                    | bit                |

| Legend:            |                                      |                                  |                                       |                       |                        |                    |                    |

| R = Reada          | able bit                             | W = Writable                     | bit                                   | U = Unimplem          | nented bit, read       | as '0'             |                    |

| -n = Value         | at POR                               | '1' = Bit is set                 |                                       | '0' = Bit is clea     | ared                   | x = Bit is unkn    | own                |

| bit 15-13          | Unimplemen                           | ted: Read as '                   | ٥'                                    |                       |                        |                    |                    |

| bit 12             | •                                    |                                  | o<br>bit (SPI Master                  | modes only)(1)        | )                      |                    |                    |

|                    | 1 = Internal S                       |                                  | abled; pin funct                      |                       |                        |                    |                    |

| bit 11             |                                      | able SDOx pin                    |                                       |                       |                        |                    |                    |

|                    | 1 = SDOx pir                         | •                                | y module; pin fu                      | unctions as I/O       |                        |                    |                    |

| bit 10             | -                                    |                                  | nunication Sele                       | ct bit                |                        |                    |                    |

|                    |                                      |                                  | -wide (16 bits)                       |                       |                        |                    |                    |

|                    | 0 = Commun                           | ication is byte-                 | wide (8 bits)                         |                       |                        |                    |                    |

| bit 9              | SMP: SPIx D                          | ata Input Sam                    | ole Phase bit                         |                       |                        |                    |                    |

|                    |                                      | a sampled at e                   | nd of data outp                       |                       |                        |                    |                    |

|                    | 0 = Input data<br>Slave mode:        | a sampled at n                   | niddle of data o                      | utput time            |                        |                    |                    |

|                    |                                      | cleared when                     | SPIx is used in                       | Slave mode.           |                        |                    |                    |

| bit 8              | CKE: SPIx C                          | lock Edge Sele                   | ect bit <sup>(3)</sup>                |                       |                        |                    |                    |

|                    |                                      |                                  | ges on transitio<br>ges on transitio  |                       |                        |                    |                    |

| bit 7              | SSEN: Slave                          | Select Enable                    | (Slave mode) b                        | oit <sup>(4)</sup>    |                        |                    |                    |

|                    |                                      | used for Slave<br>not used by mo | mode<br>dule; pin contro              | olled by port fur     | nction                 |                    |                    |

| bit 6              | CKP: Clock F                         | Polarity Select I                | oit                                   |                       |                        |                    |                    |

|                    |                                      |                                  | nigh level; activ<br>ow level; active |                       |                        |                    |                    |

| bit 5              | MSTEN: Mas                           | ter Mode Enat                    | ole bit                               |                       |                        |                    |                    |

|                    | 1 = Master m<br>0 = Slave mo         |                                  |                                       |                       |                        |                    |                    |

| Note 1:            | If DISSCK = 0, S<br>Select" for more |                                  | onfigured to an                       | available RPn         | pin. See <b>Sectio</b> | on 10.4 "Perip     | heral Pin          |

| 2:                 | If DISSDO = 0, S<br>Select" for more | DOx must be o                    | configured to ar                      | ı available RPn       | pin. See <b>Secti</b>  | on 10.4 "Perip     | oheral Pin         |

| 3:                 | The CKE bit is no<br>SPI modes (FRM  | ot used in the F                 | ramed SPI mod                         | des. The user s       | hould program          | this bit to '0' fo | or the Frame       |

| 4:                 | If SSEN = 1, $\overline{SSx}$        | ,                                | jured to an avai                      | ilable RPn pin.       | See Section 10         | ).4 "Periphera     | I Pin Select       |

### REGISTER 15-2: SPIxCON1: SPIx CONTROL REGISTER 1

NOTES:

### 18.7.4 USB VBUS POWER CONTROL REGISTER

### REGISTER 18-22: U1PWMCON: USB VBUS PWM GENERATOR CONTROL REGISTER

| R/W-0         | U-0                                     | U-0                | U-0             | U-0                                | U-0             | R/W-0           | R/W-0 |  |  |

|---------------|-----------------------------------------|--------------------|-----------------|------------------------------------|-----------------|-----------------|-------|--|--|

| PWMEN         | _                                       | _                  | _               |                                    | —               | PWMPOL          | CNTEN |  |  |

| bit 15        |                                         |                    |                 |                                    |                 |                 | bit 8 |  |  |

|               |                                         |                    |                 |                                    |                 |                 |       |  |  |

| U-0           | U-0                                     | U-0                | U-0             | U-0                                | U-0             | U-0             | U-0   |  |  |

| —             | _                                       | _                  | _               | _                                  | —               | —               | —     |  |  |

| bit 7         |                                         |                    |                 |                                    |                 |                 | bit 0 |  |  |

|               |                                         |                    |                 |                                    |                 |                 |       |  |  |

| Legend:       |                                         |                    |                 |                                    |                 |                 |       |  |  |

| R = Readabl   | e bit                                   | W = Writable b     | it              | U = Unimplemented bit, read as '0' |                 |                 |       |  |  |

| -n = Value at | POR                                     | '1' = Bit is set   |                 | '0' = Bit is clea                  | ared            | x = Bit is unkn | own   |  |  |

|               |                                         |                    |                 |                                    |                 |                 |       |  |  |

| bit 15        | PWMEN: PW                               | M Enable bit       |                 |                                    |                 |                 |       |  |  |

|               |                                         | nerator is enable  |                 |                                    |                 |                 |       |  |  |

|               | 0 = PWM ger                             | nerator is disable | ed; output is h | neld in Reset sta                  | ate specified b | y PWMPOL        |       |  |  |

| bit 14-10     | Unimplemen                              | ted: Read as '0    | ,               |                                    |                 |                 |       |  |  |

| bit 9         | PWMPOL: P                               | NM Polarity bit    |                 |                                    |                 |                 |       |  |  |

|               | 1 = PWM out                             | put is active-low  | and resets h    | ligh                               |                 |                 |       |  |  |

|               | DIA/AA subsub is a stick and as a talen |                    |                 |                                    |                 |                 |       |  |  |

- 0 = PWM output is active-high and resets low

- bit 8 CNTEN: PWM Counter Enable bit

- 1 = Counter is enabled

- 0 = Counter is disabled

- bit 7-0 Unimplemented: Read as '0'

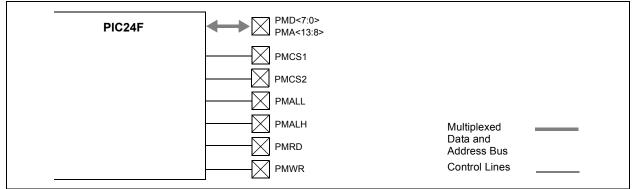

## FIGURE 19-5: MASTER MODE, PARTIALLY MULTIPLEXED ADDRESSING (SEPARATE READ AND WRITE STROBES, TWO CHIP SELECTS)

| PIC24F → PMA<13:8>         |  |

|----------------------------|--|

| PMD<7:0><br>PMA<7:0>       |  |

| PMCS1                      |  |

| PMCS2 Address Bus          |  |

| PMALL Multiplexed Data and |  |

| PMRD Address Bus           |  |

| PMWR Control Lines         |  |

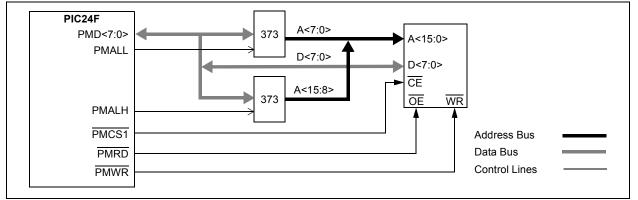

## FIGURE 19-6: MASTER MODE, FULLY MULTIPLEXED ADDRESSING (SEPARATE READ AND WRITE STROBES, TWO CHIP SELECTS)

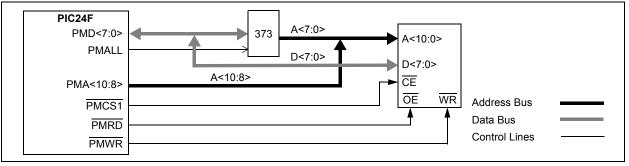

#### FIGURE 19-8: EXAMPLE OF A PARTIALLY MULTIPLEXED ADDRESSING APPLICATION

© 2009 Microchip Technology Inc.

| R/W-0        | U-0                                                                                  | U-0                | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |  |  |  |

|--------------|--------------------------------------------------------------------------------------|--------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|--|--|--|

| CH0NB        |                                                                                      | _                  | CH0SB4 <sup>(1)</sup> | CH0SB3 <sup>(1)</sup> | CH0SB2 <sup>(1)</sup> | CH0SB1 <sup>(1)</sup> | CH0SB0 <sup>(1)</sup> |  |  |  |

| bit 15       |                                                                                      |                    |                       | •                     |                       |                       | bit                   |  |  |  |

| R/W-0        | U-0                                                                                  | U-0                | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |  |  |  |

| CHONA        |                                                                                      |                    | CH0SA4                | CH0SA3                | CH0SA2                | CH0SA1                | CH0SA0                |  |  |  |

| bit 7        |                                                                                      |                    | 01100/11              | oniconic              | 01100/12              | onicorti              | bit                   |  |  |  |

| Legend:      |                                                                                      |                    |                       |                       |                       |                       |                       |  |  |  |

| R = Readab   | le hit                                                                               | W = Writable       | bit                   | U = Unimplem          | nented bit, read      | 1 as '0'              |                       |  |  |  |

| -n = Value a |                                                                                      | '1' = Bit is se    |                       | '0' = Bit is clea     |                       | x = Bit is unkr       | nown                  |  |  |  |

|              |                                                                                      |                    |                       |                       |                       |                       |                       |  |  |  |

| oit 15       | CHONB: CI                                                                            | hannel 0 Negativ   | e Input Select f      | or MUX B Multi        | plexer Setting        | bit                   |                       |  |  |  |

|              | 1 = Channe                                                                           | el 0 negative inpu | ut is AN1             |                       |                       |                       |                       |  |  |  |

|              |                                                                                      | el 0 negative inpu |                       |                       |                       |                       |                       |  |  |  |

| bit 14-13    | -                                                                                    | ented: Read as     |                       |                       |                       |                       |                       |  |  |  |

| oit 12-8     |                                                                                      | 0>: Channel 0 P    |                       |                       |                       |                       |                       |  |  |  |

|              | 10001 = Channel 0 positive input is internal band gap reference (VBG) <sup>(2)</sup> |                    |                       |                       |                       |                       |                       |  |  |  |

|              | 10000 = Channel 0 positive input is VBG/2 <sup>(2)</sup>                             |                    |                       |                       |                       |                       |                       |  |  |  |

|              | 01111 = Channel 0 positive input is AN15                                             |                    |                       |                       |                       |                       |                       |  |  |  |