Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 32MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB OTG                                      |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                      |

| Number of I/O              | 65                                                                              |

| Program Memory Size        | 256КВ (85.5К х 24)                                                              |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 80-TQFP                                                                         |

| Supplier Device Package    | 80-TQFP (12x12)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj256gb108t-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.2 USB On-The-Go

With the PIC24FJ256GB110 family of devices, Microchip introduces USB On-The-Go functionality on a single chip to its product line. This new module provides on-chip functionality as a target device compatible with the USB 2.0 standard, as well as limited stand-alone functionality as a USB embedded host. By implementing USB Host Negotiation Protocol (HNP), the module can also dynamically switch between device and host operation, allowing for a much wider range of versatile USB-enabled applications on a microcontroller platform.

In addition to USB host functionality, PIC24FJ256GB110 family devices provide a true single-chip USB solution, including an on-chip transceiver and voltage regulator, and a voltage boost generator for sourcing bus power during host operations.

# 1.3 Other Special Features

- Peripheral Pin Select: The Peripheral Pin Select (PPS) feature allows most digital peripherals to be mapped over a fixed set of digital I/O pins. Users may independently map the input and/or output of any one of the many digital peripherals to any one of the I/O pins.

- **Communications:** The PIC24FJ256GB110 family incorporates a range of serial communication peripherals to handle a range of application requirements. There are three independent I<sup>2</sup>C modules that support both Master and Slave modes of operation. Devices also have, through the Peripheral Pin Select feature, four independent UARTs with built-in IrDA encoder/decoders and three SPI modules.

- Analog Features: All members of the PIC24FJ256GB110 family include a 10-bit A/D Converter module and a triple comparator module. The A/D module incorporates programmable acquisition time, allowing for a channel to be selected and a conversion to be initiated without waiting for a sampling period, as well as faster sampling speeds. The comparator module includes three analog comparators that are configurable for a wide range of operations.

- **CTMU Interface:** In addition to their other analog features, members of the PIC24FJ256GB110 family include the brand new CTMU interface module. This provides a convenient method for precision time measurement and pulse generation, and can serve as an interface for capacitive sensors.

- Parallel Master/Enhanced Parallel Slave Port: One of the general purpose I/O ports can be reconfigured for enhanced parallel data communications. In this mode, the port can be configured for both master and slave operations, and supports 8-bit and 16-bit data transfers with up to 16 external address lines in Master modes.

- Real-Time Clock/Calendar: This module implements a full-featured clock and calendar with alarm functions in hardware, freeing up timer resources and program memory space for use of the core application.

### 1.4 Details on Individual Family Members

Devices in the PIC24FJ256GB110 family are available in 64-pin, 80-pin and 100-pin packages. The general block diagram for all devices is shown in Figure 1-1.

The devices are differentiated from each other in four ways:

- Flash program memory (64 Kbytes for PIC24FJ64GB1 devices, 128 Kbytes for PIC24FJ128GB1 devices, 192 Kbytes for PIC24FJ192GB1 devices and 256 Kbytes for PIC24FJ256GB1 devices).

- Available I/O pins and ports (51 pins on 6 ports for 64-pin devices, 65 pins on 7 ports for 80-pin devices and 83 pins on 7 ports for 100-pin devices).

- 3. Available Interrupt-on-Change Notification (ICN) inputs (49 on 64-pin devices, 63 on 80-pin devices and 81 on 100-pin devices).

- 4. Available remappable pins (29 pins on 64-pin devices, 40 pins on 80-pin devices and 44 pins on 100-pin devices)

All other features for devices in this family are identical. These are summarized in Table 1-1.

A list of the pin features available on the PIC24FJ256GB110 family devices, sorted by function, is shown in Table 1-4. Note that this table shows the pin location of individual peripheral features and not how they are multiplexed on the same pin. This information is provided in the pinout diagrams in the beginning of the data sheet. Multiplexed features are sorted by the priority given to a feature, with the highest priority peripheral being listed first.

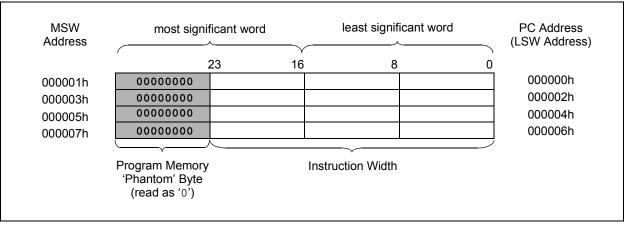

### 4.1.1 PROGRAM MEMORY ORGANIZATION

The program memory space is organized in word-addressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address (Figure 4-2).

Program memory addresses are always word-aligned on the lower word and addresses are incremented or decremented by two during code execution. This arrangement also provides compatibility with data memory space addressing and makes it possible to access data in the program memory space.

### 4.1.2 HARD MEMORY VECTORS

All PIC24F devices reserve the addresses between 00000h and 000200h for hard coded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user at 000000h, with the actual address for the start of code at 000002h.

PIC24F devices also have two interrupt vector tables, located from 000004h to 0000FFh and 000100h to 0001FFh. These vector tables allow each of the many device interrupt sources to be handled by separate ISRs. A more detailed discussion of the interrupt vector tables is provided in **Section 7.1 "Interrupt Vector Table"**.

### 4.1.3 FLASH CONFIGURATION WORDS

In PIC24FJ256GB110 family devices, the top three words of on-chip program memory are reserved for configuration information. On device Reset, the configuration information is copied into the appropriate Configuration registers. The addresses of the Flash Configuration Word for devices in the PIC24FJ256GB110 family are shown in Table 4-1. Their location in the memory map is shown with the other memory vectors in Figure 4-1.

The Configuration Words in program memory are a compact format. The actual Configuration bits are mapped in several different registers in the configuration memory space. Their order in the Flash Configuration Words does not reflect a corresponding arrangement in the configuration space. Additional details on the device Configuration Words are provided in **Section 26.1** "Configuration Bits".

| TABLE 4-1: | FLASH CONFIGURATION    |

|------------|------------------------|

|            | WORDS FOR              |

|            | PIC24FJ256GB110 FAMILY |

|            | DEVICES                |

| Device       | Program<br>Memory<br>(Words) | Configuration<br>Word<br>Addresses |

|--------------|------------------------------|------------------------------------|

| PIC24FJ64GB  | 22,016                       | 00ABFAh:<br>00ABFEh                |

| PIC24FJ128GB | 44,032                       | 0157FAh:<br>0157FEh                |

| PIC24FJ192GB | 67,072                       | 020BFAh:<br>020BFEh                |

| PIC24FJ256GB | 87,552                       | 02ABFAh:<br>02ABFEh                |

### FIGURE 4-2: PROGRAM MEMORY ORGANIZATION

### TABLE 4-28: SYSTEM REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7   | Bit 6  | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|--------|--------|---------|--------|--------|-------|-------|--------|--------|-------|---------------|

| RCON      | 0740 | TRAPR  | IOPUWR | _      | _      | _      | _      | СМ     | PMSLP  | EXTR    | SWR    | SWDTEN | WDTO  | SLEEP | IDLE   | BOR    | POR   | Note 1        |

| OSCCON    | 0742 | _      | COSC2  | COSC1  | COSC0  | _      | NOSC2  | NOSC1  | NOSC0  | CLKLOCK | IOLOCK | LOCK   | _     | CF    | POSCEN | SOSCEN | OSWEN | Note 2        |

| CLKDIV    | 0744 | ROI    | DOZE2  | DOZE1  | DOZE0  | DOZEN  | RCDIV2 | RCDIV1 | RCDIV0 | CPDIV1  | CPDIV0 | _      | _     | _     | _      | —      | _     | 0100          |

| OSCTUN    | 0748 | _      | _      | _      | _      |        | _      | _      | _      | _       |        | TUN5   | TUN4  | TUN3  | TUN2   | TUN1   | TUN0  | 0000          |

| REFOCON   | 074E | ROEN   | —      | ROSSLP | ROSEL  | RODIV3 | RODIV2 | RODIV1 | RODIV0 | -       |        | _      | —     | _     | _      |        |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: The Reset value of the RCON register is dependent on the type of Reset event. See Section 6.0 "Resets" for more information.

2: The Reset value of the OSCCON register is dependent on both the type of Reset event and the device configuration. See Section 8.0 "Oscillator Configuration" for more information.

#### TABLE 4-29: NVM REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7                | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets   |

|-----------|------|--------|--------|--------|--------|--------|--------|-------|-------|----------------------|-------|-------|-------|--------|--------|--------|--------|-----------------|

| NVMCON    | 0760 | WR     | WREN   | WRERR  | —      | _      | _      | _     | _     | -                    | ERASE | _     | —     | NVMOP3 | NVMOP2 | NVMOP1 | NVMOP0 | 0000 <b>(1)</b> |

| NVMKEY    | 0766 | _      | _      | —      | —      | _      | _      | _     | _     | NVMKEY Register<7:0> |       |       |       |        |        | 0000   |        |                 |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Reset value shown is for POR only. Value on other Reset states is dependent on the state of memory write or erase operations at the time of Reset.

#### TABLE 4-30: PMD REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8 | Bit 7  | Bit 6  | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|--------|-------|--------|--------|-------|--------|--------|--------|--------|--------|---------------|

| PMD1      | 0770 | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | -      | —      | _     | I2C1MD | U2MD   | U1MD  | SPI2MD | SPI1MD | —      | _      | ADC1MD | 0000          |

| PMD2      | 0772 | IC8MD  | IC7MD  | IC6MD  | IC5MD  | IC4MD  | IC3MD  | IC2MD  | IC1MD | OC8MD  | OC7MD  | OC6MD | OC5MD  | OC4MD  | OC3MD  | OC2MD  | OC1MD  | 0000          |

| PMD3      | 0774 | _      | _      | _      | _      | —      | CMPMD  | RTCCMD | PMPMD | CRCMD  | _      | _     | _      | U3MD   | I2C3MD | I2C2MD | _      | 0000          |

| PMD4      | 0776 | _      | _      | _      | _      | _      | _      | _      |       | _      | UPWMMD | U4MD  | _      | REFOMD | CTMUMD | LVDMD  | USB1MD | 0000          |

| PMD5      | 0778 | —      | _      | —      | —      | _      | —      | —      | IC9MD | _      | —      | —     | —      | —      | _      | _      | OC9MD  | 0000          |

| PMD6      | 077A | _      |        | _      | _      |        |        | _      | _     |        | _      | _     |        |        | —      | _      | SPI3MD | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| U-0                           | U-0          | R/W-0                                                     | R/W-0            | R/W-0             | R/W-0            | R/W-0           | R/W-0  |  |  |  |  |

|-------------------------------|--------------|-----------------------------------------------------------|------------------|-------------------|------------------|-----------------|--------|--|--|--|--|

|                               | _            | PMPIF                                                     | OC8IF            | OC7IF             | OC6IF            | OC5IF           | IC6IF  |  |  |  |  |

| oit 15                        |              |                                                           |                  |                   |                  |                 | bit    |  |  |  |  |

| R/W-0                         | R/W-0        | R/W-0                                                     | U-0              | U-0               | U-0              | R/W-0           | R/W-0  |  |  |  |  |

| IC5IF                         | IC4IF        | IC3IF                                                     | _                |                   | <u> </u>         | SPI2IF          | SPF2IF |  |  |  |  |

| pit 7                         | 10 11        | loon                                                      |                  |                   |                  | 01 1211         | bit    |  |  |  |  |

|                               |              |                                                           |                  |                   |                  |                 |        |  |  |  |  |

| L <b>egend:</b><br>R = Readat | le hit       | W = Writable                                              | hit              | II = I Inimplem   | nented bit, read | 1 as '0'        |        |  |  |  |  |

| n = Value a                   |              | '1' = Bit is set                                          |                  | '0' = Bit is clea |                  | x = Bit is unkr | iown   |  |  |  |  |

|                               |              |                                                           |                  |                   |                  |                 |        |  |  |  |  |

| oit 15-14                     | •            | nted: Read as '                                           |                  |                   |                  |                 |        |  |  |  |  |

| oit 13                        |              | Illel Master Port                                         |                  | Status bit        |                  |                 |        |  |  |  |  |

|                               |              | request has oc<br>request has no                          |                  |                   |                  |                 |        |  |  |  |  |

| oit 12                        |              |                                                           |                  | pt Flag Status b  | bit              |                 |        |  |  |  |  |

|                               |              | request has oc                                            |                  |                   |                  |                 |        |  |  |  |  |

| pit 11                        | -            | request has no                                            |                  | unt Elon Statua k | .i+              |                 |        |  |  |  |  |

|                               | •            | request has oc                                            |                  | pt Flag Status b  | л                |                 |        |  |  |  |  |

|                               |              | request has no                                            |                  |                   |                  |                 |        |  |  |  |  |

| oit 10                        | -            | OC6IF: Output Compare Channel 6 Interrupt Flag Status bit |                  |                   |                  |                 |        |  |  |  |  |

|                               |              | request has oc<br>request has no                          |                  |                   |                  |                 |        |  |  |  |  |

| oit 9                         | -            | -                                                         |                  | pt Flag Status b  | bit              |                 |        |  |  |  |  |

|                               | -            | request has oc                                            |                  |                   |                  |                 |        |  |  |  |  |

|                               | -            | request has no                                            |                  |                   |                  |                 |        |  |  |  |  |

| oit 8                         |              | Capture Chann                                             | -                | lag Status bit    |                  |                 |        |  |  |  |  |

|                               |              | request has oc<br>request has no                          |                  |                   |                  |                 |        |  |  |  |  |

| oit 7                         | •            | Capture Chann                                             |                  | lag Status bit    |                  |                 |        |  |  |  |  |

|                               |              | request has oc                                            |                  |                   |                  |                 |        |  |  |  |  |

|                               | -            | request has no                                            |                  |                   |                  |                 |        |  |  |  |  |

| oit 6                         |              | Capture Chann<br>request has oc                           | -                | lag Status bit    |                  |                 |        |  |  |  |  |

|                               |              | request has no                                            |                  |                   |                  |                 |        |  |  |  |  |

| oit 5                         | IC3IF: Input | Capture Chann                                             | el 3 Interrupt F | lag Status bit    |                  |                 |        |  |  |  |  |

|                               |              | request has oc<br>request has no                          |                  |                   |                  |                 |        |  |  |  |  |

| oit 4-2                       |              | nted: Read as '                                           |                  |                   |                  |                 |        |  |  |  |  |

| bit 4-2<br>bit 1              | -            | 2 Event Interrup                                          |                  | it                |                  |                 |        |  |  |  |  |

|                               |              | request has oc                                            | -                |                   |                  |                 |        |  |  |  |  |

|                               | -            | request has no                                            |                  |                   |                  |                 |        |  |  |  |  |

|                               | OBEALE OD    |                                                           |                  |                   |                  |                 |        |  |  |  |  |

| oit 0                         |              | 2 Fault Interrup<br>request has oc                        | -                | it                |                  |                 |        |  |  |  |  |

### REGISTER 7-23: IPC6: INTERRUPT PRIORITY CONTROL REGISTER 6

| U-0              | R/W-1                                                                                 | R/W-0                                                                                  | R/W-0                                              | U-0               | R/W-1            | R/W-0                              | R/W-0  |  |  |  |  |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------|-------------------|------------------|------------------------------------|--------|--|--|--|--|--|--|--|--|--|

| _                | T4IP2                                                                                 | T4IP1                                                                                  | T4IP0                                              |                   | OC4IP2           | OC4IP1                             | OC4IP0 |  |  |  |  |  |  |  |  |  |

| bit 15           |                                                                                       | •                                                                                      |                                                    | ·                 |                  | •                                  | bit 8  |  |  |  |  |  |  |  |  |  |

| U-0              | R/W-1                                                                                 | R/W-0                                                                                  | R/W-0                                              | U-0               | U-0              | U-0                                | U-0    |  |  |  |  |  |  |  |  |  |

| —                | OC3IP2                                                                                | OC3IP1                                                                                 | OC3IP0                                             | —                 | _                | —                                  | —      |  |  |  |  |  |  |  |  |  |

| bit 7            |                                                                                       |                                                                                        |                                                    |                   |                  |                                    | bit    |  |  |  |  |  |  |  |  |  |

| Legend:          |                                                                                       |                                                                                        |                                                    |                   |                  |                                    |        |  |  |  |  |  |  |  |  |  |

| R = Readab       | ole bit                                                                               | W = Writable                                                                           | bit                                                | U = Unimpler      | nented bit, read | l as '0'                           |        |  |  |  |  |  |  |  |  |  |

| -n = Value a     | t POR                                                                                 | '1' = Bit is set                                                                       |                                                    | '0' = Bit is cle  | ared             | x = Bit is unkr                    | nown   |  |  |  |  |  |  |  |  |  |

|                  |                                                                                       |                                                                                        |                                                    |                   |                  |                                    |        |  |  |  |  |  |  |  |  |  |

| bit 15           | Unimplemer                                                                            | nted: Read as 'o                                                                       | )'                                                 |                   |                  |                                    |        |  |  |  |  |  |  |  |  |  |

| bit 14-12        | T4IP<2:0>: Timer4 Interrupt Priority bits                                             |                                                                                        |                                                    |                   |                  |                                    |        |  |  |  |  |  |  |  |  |  |

|                  | 111 = Interru                                                                         | pt is priority 7 (ł                                                                    | nighest priority                                   | interrupt)        |                  |                                    |        |  |  |  |  |  |  |  |  |  |

|                  | •                                                                                     |                                                                                        |                                                    |                   |                  |                                    |        |  |  |  |  |  |  |  |  |  |

|                  | •                                                                                     |                                                                                        |                                                    |                   |                  |                                    |        |  |  |  |  |  |  |  |  |  |

|                  | 001 = Interru                                                                         | pt is priority 1                                                                       |                                                    |                   |                  |                                    |        |  |  |  |  |  |  |  |  |  |

|                  |                                                                                       | pt source is dis                                                                       | abled                                              |                   |                  |                                    |        |  |  |  |  |  |  |  |  |  |

| bit 11           | Unimplemer                                                                            | nted: Read as 'd                                                                       | )'                                                 |                   |                  |                                    |        |  |  |  |  |  |  |  |  |  |

| bit 10-8         | OC4IP<2:0>: Output Compare Channel 4 Interrupt Priority bits                          |                                                                                        |                                                    |                   |                  |                                    |        |  |  |  |  |  |  |  |  |  |

|                  | 111 = Interru                                                                         | pt is priority 7 (ł                                                                    | nighest priority                                   | interrupt)        |                  |                                    |        |  |  |  |  |  |  |  |  |  |

|                  | •                                                                                     |                                                                                        |                                                    |                   |                  |                                    |        |  |  |  |  |  |  |  |  |  |

|                  | •                                                                                     |                                                                                        |                                                    |                   |                  |                                    |        |  |  |  |  |  |  |  |  |  |

|                  |                                                                                       | int is priority 1                                                                      |                                                    |                   |                  |                                    |        |  |  |  |  |  |  |  |  |  |

|                  | 001 = Interru                                                                         |                                                                                        |                                                    |                   |                  |                                    |        |  |  |  |  |  |  |  |  |  |

|                  | 001 = Interru<br>000 = Interru                                                        |                                                                                        | abled                                              |                   |                  | 000 = Interrupt source is disabled |        |  |  |  |  |  |  |  |  |  |

| bit 7            | 000 = Interru                                                                         |                                                                                        |                                                    |                   |                  |                                    |        |  |  |  |  |  |  |  |  |  |

| bit 7<br>bit 6-4 | 000 = Interru<br>Unimplemer                                                           | pt source is dis                                                                       | )'                                                 | Interrupt Priorit | y bits           |                                    |        |  |  |  |  |  |  |  |  |  |

|                  | 000 = Interru<br>Unimplemer<br>OC3IP<2:0>                                             | ipt source is dis<br>ited: Read as '(                                                  | )'<br>re Channel 3                                 | •                 | y bits           |                                    |        |  |  |  |  |  |  |  |  |  |

|                  | 000 = Interru<br>Unimplemer<br>OC3IP<2:0>                                             | ipt source is dis<br>ited: Read as '(<br>: Output Compa                                | )'<br>re Channel 3                                 | •                 | y bits           |                                    |        |  |  |  |  |  |  |  |  |  |

|                  | 000 = Interru<br>Unimplemer<br>OC3IP<2:0>                                             | ipt source is dis<br>ited: Read as '(<br>: Output Compa                                | )'<br>re Channel 3                                 | •                 | y bits           |                                    |        |  |  |  |  |  |  |  |  |  |

|                  | 000 = Interru<br>Unimplemer<br>OC3IP<2:0><br>111 = Interru<br>•<br>•                  | ipt source is dis<br>ited: Read as '(<br>: Output Compa                                | )'<br>re Channel 3                                 | •                 | y bits           |                                    |        |  |  |  |  |  |  |  |  |  |

|                  | 000 = Interru<br>Unimplemen<br>OC3IP<2:0><br>111 = Interru<br>•<br>•<br>001 = Interru | ipt source is dis<br><b>ited:</b> Read as '(<br>: Output Compa<br>ipt is priority 7 (H | <sub>)</sub> ,<br>re Channel 3<br>highest priority | •                 | y bits           |                                    |        |  |  |  |  |  |  |  |  |  |

### REGISTER 7-31: IPC15: INTERRUPT PRIORITY CONTROL REGISTER 15

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-1  | R/W-0  | R/W-0  |

|--------|-----|-----|-----|-----|--------|--------|--------|

| —      |     |     | —   | —   | RTCIP2 | RTCIP1 | RTCIP0 |

| bit 15 |     |     |     |     |        |        | bit 8  |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| —     | —   | —   | —   | —   | —   | —   | —     |

| bit 7 |     |     |     |     |     |     | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-11 Unimplemented: Read as '0'

- bit 10-8 **RTCIP<2:0>:** Real-Time Clock/Calendar Interrupt Priority bits 111 = Interrupt is priority 7 (highest priority interrupt)

- •

- 001 = Interrupt is priority 1

- 000 = Interrupt source is disabled

- bit 7-0 Unimplemented: Read as '0'

| U-0          | R/W-1              | R/W-0                                | R/W-0            | U-0               | R/W-1            | R/W-0           | R/W-0   |

|--------------|--------------------|--------------------------------------|------------------|-------------------|------------------|-----------------|---------|

| _            | CRCIP2             | CRCIP1                               | CRCIP0           | —                 | U2ERIP2          | U2ERIP1         | U2ERIP0 |

| bit 15       |                    |                                      |                  |                   |                  |                 | bit 8   |

|              |                    |                                      |                  |                   |                  |                 |         |

| U-0          | R/W-1              | R/W-0                                | R/W-0            | U-0               | U-0              | U-0             | U-0     |

|              | U1ERIP2            | U1ERIP1                              | U1ERIP0          |                   |                  |                 |         |

| bit 7        |                    |                                      |                  |                   |                  |                 | bit 0   |

| [            |                    |                                      |                  |                   |                  |                 |         |

| Legend:      |                    |                                      |                  |                   |                  |                 |         |

| R = Readab   |                    | W = Writable                         |                  | -                 | nented bit, read |                 |         |

| -n = Value a | at POR             | '1' = Bit is set                     |                  | '0' = Bit is cle  | ared             | x = Bit is unkr | nown    |

|              |                    |                                      |                  |                   |                  |                 |         |

| bit 15       | -                  | ted: Read as '                       |                  |                   |                  |                 |         |

| bit 14-12    | CRCIP<2:0>:        | CRC Generate                         | or Error Interru | upt Priority bits |                  |                 |         |

|              | 111 = Interru      | pt is priority 7 (I                  | highest priority | / interrupt)      |                  |                 |         |

|              | •                  |                                      |                  |                   |                  |                 |         |

|              | •                  |                                      |                  |                   |                  |                 |         |

|              | 001 = Interru      | pt is priority 1                     |                  |                   |                  |                 |         |

|              |                    | pt source is dis                     | abled            |                   |                  |                 |         |

| bit 11       | Unimplemen         | ted: Read as '                       | D'               |                   |                  |                 |         |

| bit 10-8     | U2ERIP<2:0>        | : UART2 Error                        | Interrupt Prio   | rity bits         |                  |                 |         |

|              | 111 = Interru      | pt is priority 7 (I                  | highest priority | / interrupt)      |                  |                 |         |

|              | •                  |                                      |                  |                   |                  |                 |         |

|              | •                  |                                      |                  |                   |                  |                 |         |

|              | 001 = Interru      | pt is priority 1                     |                  |                   |                  |                 |         |

|              |                    | pt source is dis                     | abled            |                   |                  |                 |         |

| bit 7        | Unimplemen         | ted: Read as '                       | o'               |                   |                  |                 |         |

| bit 6-4      | U1ERIP<2:0>        | -: UART1 Error                       | Interrupt Prio   | rity bits         |                  |                 |         |

|              | 111 = Interru      | pt is priority 7 (l                  | highest priority | / interrupt)      |                  |                 |         |

|              | •                  |                                      |                  |                   |                  |                 |         |

|              | •                  |                                      |                  |                   |                  |                 |         |

|              | •<br>001 = Interru | nt is priority 1                     |                  |                   |                  |                 |         |

|              |                    | pt is priority i<br>pt source is dis | abled            |                   |                  |                 |         |

| bit 3-0      | -                  | ted: Read as '                       |                  |                   |                  |                 |         |

|              | •                  |                                      |                  |                   |                  |                 |         |

### REGISTER 7-32: IPC16: INTERRUPT PRIORITY CONTROL REGISTER 16

| U-0    | R/W-1   | R/W-0   | R/W-0   | U-0 | R/W-1   | R/W-0   | R/W-0   |

|--------|---------|---------|---------|-----|---------|---------|---------|

| _      | U4ERIP2 | U4ERIP1 | U4ERIP0 | —   | USB1IP2 | USB1IP1 | USB1IP0 |

| bit 15 |         |         |         |     |         |         | bit 8   |

### REGISTER 7-36: IPC21: INTERRUPT PRIORITY CONTROL REGISTER 21

| U-0   | R/W-1   | R/W-0   | R/W-0   | U-0 | R/W-1   | R/W-0   | R/W-0   |

|-------|---------|---------|---------|-----|---------|---------|---------|

| —     | MI2C3P2 | MI2C3P1 | MI2C3P0 | —   | SI2C3P2 | SI2C3P1 | SI2C3P0 |

| bit 7 |         |         |         |     |         |         | bit 0   |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | 1 as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15    | Unimplemented: Read as '0'                                                     |

|-----------|--------------------------------------------------------------------------------|

| bit 14-12 | U4ERIP<2:0>: UART4 Error Interrupt Priority bits                               |

|           | 111 = Interrupt is priority 7 (highest priority interrupt)                     |

|           | •                                                                              |

|           | •                                                                              |

|           | •<br>001 = Interrupt is priority 1                                             |

|           | 000 = Interrupt source is disabled                                             |

| bit 11    | Unimplemented: Read as '0'                                                     |

| bit 10-8  | USB1IP<2:0>: USB1 (USB OTG) Interrupt Priority bits                            |

|           | 111 = Interrupt is priority 7 (highest priority interrupt)                     |

|           | •                                                                              |

|           | •                                                                              |

|           | •                                                                              |

|           | 001 = Interrupt is priority 1                                                  |

|           | 000 = Interrupt source is disabled                                             |

| bit 7     | Unimplemented: Read as '0'                                                     |

| bit 6-4   | MI2C3P<2:0>: Master I2C3 Event Interrupt Priority bits                         |

|           | <ul> <li>111 = Interrupt is priority 7 (highest priority interrupt)</li> </ul> |

|           |                                                                                |

|           | •                                                                              |

|           | 001 = Interrupt is priority 1                                                  |

|           | 000 = Interrupt source is disabled                                             |

| bit 3     | Unimplemented: Read as '0'                                                     |

| bit 2-0   | SI2C3P<2:0>: Slave I2C3 Event Interrupt Priority bits                          |

|           | 111 = Interrupt is priority 7 (highest priority interrupt)                     |

|           | •                                                                              |

|           | •                                                                              |

|           | •<br>001 = Interrupt is priority 1                                             |

|           | 000 = Interrupt source is disabled                                             |

|           |                                                                                |

### REGISTER 15-1: SPIx STATUS AND CONTROL REGISTER (CONTINUED)

- bit 1 SPITBF: SPIx Transmit Buffer Full Status bit 1 = Transmit not yet started, SPIxTXB is full 0 = Transmit started, SPIxTXB is empty In Standard Buffer mode: Automatically set in hardware when CPU writes SPIxBUF location, loading SPIxTXB. Automatically cleared in hardware when SPIx module transfers data from SPIxTXB to SPIxSR. In Enhanced Buffer mode: Automatically set in hardware when CPU writes SPIxBUF location, loading the last available buffer location. Automatically cleared in hardware when a buffer location is available for a CPU write. bit 0 SPIRBF: SPIx Receive Buffer Full Status bit 1 = Receive complete, SPIxRXB is full 0 = Receive is not complete, SPIxRXB is empty In Standard Buffer mode: Automatically set in hardware when SPIx transfers data from SPIxSR to SPIxRXB. Automatically cleared in hardware when core reads SPIxBUF location, reading SPIxRXB. In Enhanced Buffer mode: Automatically set in hardware when SPIx transfers data from SPIxSR to buffer, filling the last unread buffer location. Automatically cleared in hardware when a buffer location is available for a transfer from SPIxSR.

- **Note 1:** If SPIEN = 1, these functions must be assigned to available RPn pins before use. See **Section 10.4** "**Peripheral Pin Select**" for more information.

# 18.1 Hardware Configuration

### 18.1.1 DEVICE MODE

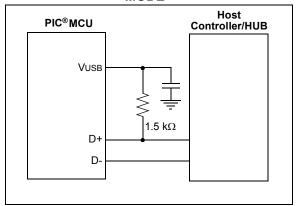

### 18.1.1.1 D+ Pull-up Resistor

PIC24FJ256GB110 family devices have a built-in 1.5 kΩ resistor on the D+ line that is available when the microcontroller in operating in device mode. This is used to signal an external Host that the device is operating in Full Speed Device mode. It is engaged by setting the DPPULUP bit (U10TGCON<7>).

Alternatively, an external resistor may be used on D+, as shown in Figure 18-2.

#### FIGURE 18-2: EXTERNAL PULL-UP FOR FULL-SPEED DEVICE MODE

### 18.1.1.2 Power Modes

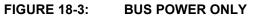

Many USB applications will likely have several different sets of power requirements and configuration. The most common power modes encountered are:

- Bus Power Only,

- · Self-Power Only and

- Dual Power with Self-Power Dominance.

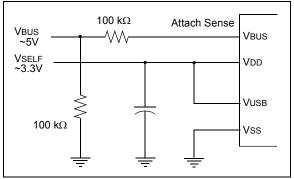

Bus Power Only mode (Figure 18-3) is effectively the simplest method. All power for the application is drawn from the USB.

To meet the inrush current requirements of the USB 2.0 Specification, the total effective capacitance appearing across VBUs and ground must be no more than 10  $\mu$ F.

In the USB Suspend mode, devices must consume no more than 2.5 mA from the 5V VBUS line of the USB cable. During the USB Suspend mode, the D+ or D-pull-up resistor must remain active, which will consume some of the allowed suspend current.

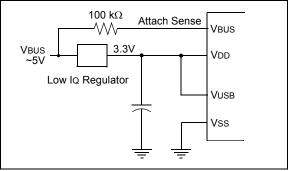

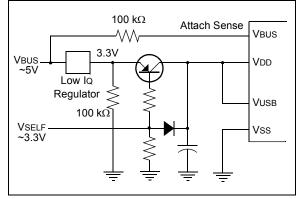

In Self-Power Only mode (Figure 18-4), the USB application provides its own power, with very little power being pulled from the USB. Note that an attach indication is added to indicate when the USB has been connected and the host is actively powering VBUS.

To meet compliance specifications, the USB module (and the D+ or D- pull-up resistor) should not be enabled until the host actively drives VBUS high. One of the 5.5V tolerant I/O pins may be used for this purpose.

The application should never source any current onto the 5V VBUS pin of the USB cable.

The Dual-power option with Self-Power Dominance (Figure 18-5) allows the application to use internal power primarily, but switch to power from the USB when no internal power is available. Dual-power devices must also meet all of the special requirements for inrush current and Suspend mode current previously described, and must not enable the USB module until VBUS is driven high.

FIGURE 18-4: SELF-POWER ONLY

FIGURE 18-5:

DUAL POWER EXAMPLE

### 18.7.1 USB OTG MODULE CONTROL REGISTERS

### REGISTER 18-3: U1OTGSTAT: USB OTG STATUS REGISTER (HOST MODE ONLY)

| U-0                     | U-0                                                                   | U-0                                                                                             | U-0                                         | U-0               | U-0                    | U-0            | U-0            |

|-------------------------|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|---------------------------------------------|-------------------|------------------------|----------------|----------------|

| —                       | —                                                                     | —                                                                                               | —                                           | —                 | —                      | —              | —              |

| bit 15                  |                                                                       |                                                                                                 |                                             |                   |                        |                | bit            |

| R-0, HSC                | U-0                                                                   | R-0, HSC                                                                                        | U-0                                         | R-0, HSC          | R-0, HSC               | U-0            | R-0, HSC       |

| ID                      | —                                                                     | LSTATE                                                                                          | _                                           | SESVD             | SESEND                 | _              | VBUSVD         |

| bit 7                   |                                                                       |                                                                                                 |                                             |                   |                        |                | bit            |

| Legend:                 |                                                                       |                                                                                                 |                                             | U = Unimplem      | ented bit, read        | l as '0'       |                |

| R = Readab              | ole bit                                                               | W = Writable b                                                                                  | pit                                         | HSC = Hardw       | are Settable/C         | learable bit   |                |

| -n = Value a            | at POR                                                                | '1' = Bit is set                                                                                |                                             | '0' = Bit is clea | ared                   | x = Bit is unk | nown           |

| bit 7<br>bit 6<br>bit 5 | 0 = A type A<br>Unimplement<br>LSTATE: Line<br>1 = The USB            | s attached, or a<br>plug has been p<br>ted: Read as '0<br>e State Stable In<br>line state (as d | dicator bit<br>efined by SE0                | and JSTATE) I     | cle<br>nas been stable |                | ous 1 ms       |

| bit 4                   |                                                                       | line state has N<br>ted: Read as '0                                                             |                                             | ole for the previ | ous 1 ms               |                |                |

| bit 3                   | SESVD: Sess<br>1 = The VBUS<br>B-device                               | sion Valid Indica<br>S voltage is abo                                                           | tor bit<br>ve VA_SESS_V                     |                   |                        | ΓG Specificati | on) on the A o |

|                         |                                                                       | s voltage is belo                                                                               | W VA_SESS_VI                                | _D on the A or E  |                        |                |                |

| bit 2                   | SESEND: B-S<br>1 = The VBU:<br>B-device                               | S voltage is beic<br>Session End Inc<br>S voltage is be                                         | licator bit<br>low VB_SESS_                 | _END (as define   | ed in the USE          | 3 OTG Specif   | ïcation) on th |

|                         | SESEND: B-S<br>1 = The VBU<br>B-device<br>0 = The VBUS                | Session End Inc<br>s voltage is be                                                              | licator bit<br>low VB_SESS_<br>ve VB_SESS_E | _END (as define   | ed in the USE          | 3 OTG Specif   | ïcation) on th |

| bit 2<br>bit 1<br>bit 0 | SESEND: B-S<br>1 = The VBU:<br>B-device<br>0 = The VBUS<br>Unimplemen | Session End Inc<br>s voltage is be<br>s voltage is abo                                          | licator bit<br>low VB_sess_<br>ve VB_sess_e | _END (as define   | ed in the USE          | 3 OTG Specif   | ïcation) on th |

### REGISTER 18-5: U1PWRC: USB POWER CONTROL REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0, HS   | U-0 | U-0 | R/W-0   | U-0 | U-0 | R/W-0, HC | R/W-0  |

|-------------|-----|-----|---------|-----|-----|-----------|--------|

| UACTPND     | —   | —   | USLPGRD | —   | —   | USUSPND   | USBPWR |

| bit 7 bit 0 |     |     |         |     |     |           |        |

| Legend:           | HS = Hardware Settable bit | HC = Hardware Clearable bit        |                    |  |

|-------------------|----------------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared               | x = Bit is unknown |  |

| bit 15-8 | Unimplemented: Read as '0'                                                                                                                                 |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7    | UACTPND: USB Activity Pending bit                                                                                                                          |

|          | <ul> <li>1 = Module should not be suspended at the moment (requires USLPGRD bit to be set)</li> <li>0 = Module may be suspended or powered down</li> </ul> |

| bit 6-5  | Unimplemented: Read as '0'                                                                                                                                 |

| bit 4    | USLPGRD: Sleep/Suspend Guard bit                                                                                                                           |

|          | <ul> <li>1 = Indicate to the USB module that it is about to be suspended or powered down</li> <li>0 = No suspend</li> </ul>                                |

| bit 3-2  | Unimplemented: Read as '0'                                                                                                                                 |

| bit 1    | USUSPND: USB Suspend Mode Enable bit                                                                                                                       |

|          | <ul> <li>1 = USB OTG module is in Suspend mode; USB clock is gated and the transceiver is placed in a<br/>low-power state</li> </ul>                       |

|          | 0 = Normal USB OTG operation                                                                                                                               |

| bit 0    | USBPWR: USB Operation Enable bit                                                                                                                           |

|          | 1 = USB OTG module is enabled (1)                                                                                                                          |

|          | $0 = \text{USB OTG module is disabled}^{(1)}$                                                                                                              |

| Nata A.  |                                                                                                                                                            |

Note 1: Do not clear this bit unless the HOSTEN, USBEN and OTGEN bits (U1CON<3,0> and U1OTGCON<2>) are all cleared.

| <b>REGISTER 18-7:</b> | U1CON: USB CONTROL REGISTER (DEVICE MODE) |  |

|-----------------------|-------------------------------------------|--|

|-----------------------|-------------------------------------------|--|

|        |          |        |     |        | ,      |        |       |

|--------|----------|--------|-----|--------|--------|--------|-------|

| U-0    | U-0      | U-0    | U-0 | U-0    | U-0    | U-0    | U-0   |

| —      | —        | —      | —   | —      | —      | —      | —     |

| bit 15 |          | •      |     |        |        |        | bit 8 |

|        |          |        |     |        |        |        |       |

| U-0    | R-x, HSC | R/W-0  | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0 |

| —      | SE0      | PKTDIS | —   | HOSTEN | RESUME | PPBRST | USBEN |

| bit 7  |          | •      |     |        |        |        | bit 0 |

|        |          |        |     |        |        |        |       |

| Legend:           | U = Unimplemented bit, read as '0' |                                       |                    |  |  |

|-------------------|------------------------------------|---------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                   | HSC = Hardware Settable/Clearable bit |                    |  |  |

| -n = Value at POR | '1' = Bit is set                   | '0' = Bit is cleared                  | x = Bit is unknown |  |  |

| bit 15-7 | Unimplemented: Read as '0'                                                                                                                                                                             |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6    | SE0: Live Single-Ended Zero Flag bit                                                                                                                                                                   |

|          | <ul><li>1 = Single-ended zero active on the USB bus</li><li>0 = No single-ended zero detected</li></ul>                                                                                                |

| bit 5    | PKTDIS: Packet Transfer Disable bit                                                                                                                                                                    |

|          | <ul> <li>1 = SIE token and packet processing disabled; automatically set when a SETUP token is received</li> <li>0 = SIE token and packet processing enabled</li> </ul>                                |

| bit 4    | Unimplemented: Read as '0'                                                                                                                                                                             |

| bit 3    | HOSTEN: Host Mode Enable bit                                                                                                                                                                           |

|          | <ul> <li>1 = USB host capability enabled; pull-downs on D+ and D- are activated in hardware</li> <li>0 = USB host capability disabled</li> </ul>                                                       |

| bit 2    | RESUME: Resume Signaling Enable bit                                                                                                                                                                    |

|          | <ul><li>1 = Resume signaling activated</li><li>0 = Resume signaling disabled</li></ul>                                                                                                                 |

| bit 1    | PPBRST: Ping-Pong Buffers Reset bit                                                                                                                                                                    |

|          | <ol> <li>Reset all Ping-Pong Buffer Pointers to the EVEN BD banks</li> <li>Ping-Pong Buffer Pointers not reset</li> </ol>                                                                              |

| bit 0    | USBEN: USB Module Enable bit                                                                                                                                                                           |

|          | <ul> <li>1 = USB module and supporting circuitry enabled (device attached); D+ pull-up is activated in hardware</li> <li>0 = USB module and supporting circuitry disabled (device detached)</li> </ul> |

|          |                                                                                                                                                                                                        |

# 21.3 Registers

There are four registers used to control programmable CRC operation:

- CRCCON

- CRCXOR

- CRCDAT

- CRCWDAT

### REGISTER 21-1: CRCCON: CRC CONTROL REGISTER

| U-0    | U-0 | R/W-0 | R-0    | R-0    | R-0    | R-0    | R-0    |

|--------|-----|-------|--------|--------|--------|--------|--------|

| —      | —   | CSIDL | VWORD4 | VWORD3 | VWORD2 | VWORD1 | VWORD0 |

| bit 15 |     |       |        |        |        |        | bit 8  |

| R-0    | R-1    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|--------|-----|-------|-------|-------|-------|-------|

| CRCFUL | CRCMPT | —   | CRCGO | PLEN3 | PLEN2 | PLEN1 | PLEN0 |

| bit 7  |        |     |       |       |       |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                         |

|-----------|------------------------------------------------------------------------------------------------------------------------------------|

| bit 13    | CSIDL: CRC Stop in Idle Mode bit                                                                                                   |

|           | <ul><li>1 = Discontinue module operation when device enters Idle mode</li><li>0 = Continue module operation in Idle mode</li></ul> |

| bit 12-8  | VWORD<4:0>: Pointer Value bits                                                                                                     |

|           | Indicates the number of valid words in the FIFO. Has a maximum value of 8 when PLEN<3:0> > 7, or 16 when PLEN<3:0> $\leq$ 7.       |

| bit 7     | CRCFUL: FIFO Full bit                                                                                                              |

|           | 1 = FIFO is full                                                                                                                   |

|           | 0 = FIFO is not full                                                                                                               |

| bit 6     | CRCMPT: FIFO Empty Bit                                                                                                             |

|           | 1 = FIFO is empty                                                                                                                  |

|           | 0 = FIFO is not empty                                                                                                              |

| bit 5     | Unimplemented: Read as '0'                                                                                                         |

| bit 4     | CRCGO: Start CRC bit                                                                                                               |

|           | 1 = Start CRC serial shifter                                                                                                       |

|           | 0 = CRC serial shifter turned off                                                                                                  |

| bit 3-0   | PLEN<3:0>: Polynomial Length bits                                                                                                  |

|           | Denotes the length of the polynomial to be generated minus 1.                                                                      |

|           |                                                                                                                                    |

| U-0                                                                                                                                      | U-0                                                                                                                                                                         | U-0              | U-0   | U-0               | U-0            | U-0             | U-0   |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------|-------------------|----------------|-----------------|-------|--|--|--|--|

| _                                                                                                                                        | —                                                                                                                                                                           | _                | —     | —                 | _              | —               | —     |  |  |  |  |

| bit 15                                                                                                                                   |                                                                                                                                                                             |                  |       |                   |                |                 | bit 8 |  |  |  |  |

|                                                                                                                                          |                                                                                                                                                                             |                  |       |                   |                |                 |       |  |  |  |  |

| R/W-0                                                                                                                                    | R/W-0                                                                                                                                                                       | R/W-0            | R/W-0 | R/W-0             | R/W-0          | R/W-0           | R/W-0 |  |  |  |  |

| CVREN                                                                                                                                    | CVROE                                                                                                                                                                       | CVRR             | CVRSS | CVR3              | CVR2           | CVR1            | CVR0  |  |  |  |  |

| bit 7                                                                                                                                    |                                                                                                                                                                             |                  |       |                   |                |                 | bit ( |  |  |  |  |

|                                                                                                                                          |                                                                                                                                                                             |                  |       |                   |                |                 |       |  |  |  |  |

| Legend:<br>R = Readab                                                                                                                    | lo hit                                                                                                                                                                      | W = Writable     | hit   | II – Unimplom     | onted hit read | d ac 'O'        |       |  |  |  |  |

|                                                                                                                                          |                                                                                                                                                                             |                  |       | U = Unimplem      |                |                 |       |  |  |  |  |

| -n = Value a                                                                                                                             | IT POR                                                                                                                                                                      | '1' = Bit is set |       | '0' = Bit is clea | ared           | x = Bit is unkn | IOWN  |  |  |  |  |

| bit 15-8                                                                                                                                 | Unimplemen                                                                                                                                                                  | ted: Read as '   | 0'    |                   |                |                 |       |  |  |  |  |

| bit 7                                                                                                                                    | CVREN: Comparator Voltage Reference Enable bit                                                                                                                              |                  |       |                   |                |                 |       |  |  |  |  |

|                                                                                                                                          | 1 = CVREF circuit powered on                                                                                                                                                |                  |       |                   |                |                 |       |  |  |  |  |

|                                                                                                                                          | 0 = CVREF circuit powered down                                                                                                                                              |                  |       |                   |                |                 |       |  |  |  |  |

| bit 6                                                                                                                                    | CVROE: Comparator VREF Output Enable bit                                                                                                                                    |                  |       |                   |                |                 |       |  |  |  |  |

|                                                                                                                                          | 1 = CVREF voltage level is output on CVREF pin                                                                                                                              |                  |       |                   |                |                 |       |  |  |  |  |

|                                                                                                                                          | 0 = CVREF voltage level is disconnected from CVREF pin                                                                                                                      |                  |       |                   |                |                 |       |  |  |  |  |

| bit 5                                                                                                                                    | CVRR: Comparator VREF Range Selection bit                                                                                                                                   |                  |       |                   |                |                 |       |  |  |  |  |

|                                                                                                                                          | <ul> <li>1 = CVRSRC range should be 0 to 0.625 CVRSRC with CVRSRC/24 step size</li> <li>0 = CVRSRC range should be 0.25 to 0.719 CVRSRC with CVRSRC/32 step size</li> </ul> |                  |       |                   |                |                 |       |  |  |  |  |

|                                                                                                                                          |                                                                                                                                                                             | •                |       |                   | JVRSRC/32 ste  | p size          |       |  |  |  |  |

| bit 4                                                                                                                                    | CVRSS: Comparator VREF Source Selection bit                                                                                                                                 |                  |       |                   |                |                 |       |  |  |  |  |