Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 32MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB OTG                                      |

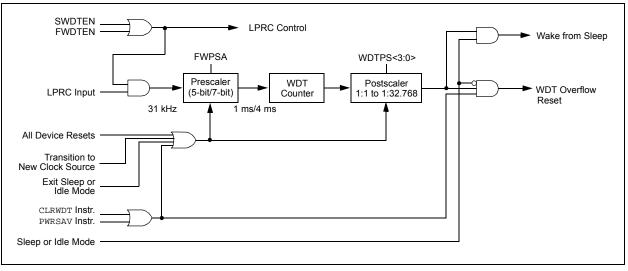

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                      |

| Number of I/O              | 83                                                                              |

| Program Memory Size        | 256КВ (85.5К х 24)                                                              |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

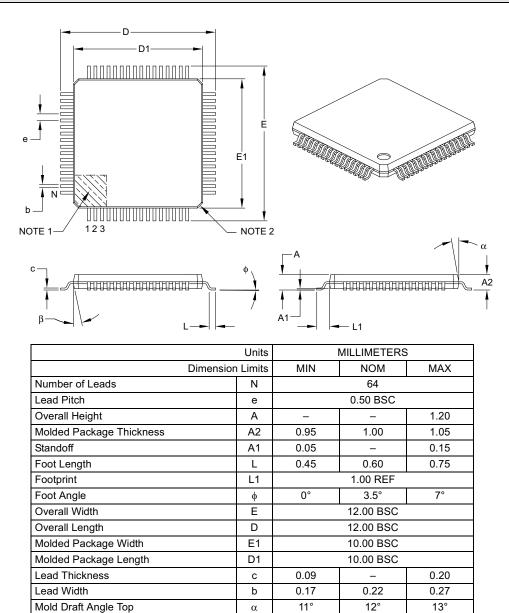

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (14x14)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj256gb110t-i-pf |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

MCI R

Vss

Vdd

C1

C6<sup>(2)</sup>-

Ī

### 2.0 **GUIDELINES FOR GETTING STARTED WITH 16-BIT** MICROCONTROLLERS

#### 2.1 **Basic Connection Requirements**

Getting started with the PIC24FJ256GB110 family of 16-bit microcontrollers requires attention to a minimal set of device pin connections before proceeding with development.

The following pins must always be connected:

- All VDD and Vss pins (see Section 2.2 "Power Supply Pins")

- All AVDD and AVSS pins, regardless of whether or not the analog device features are used (see Section 2.2 "Power Supply Pins")

- MCLR pin (see Section 2.3 "Master Clear (MCLR) Pin")

- ENVREG/DISVREG and VCAP/VDDCORE pins (PIC24FJ devices only) (see Section 2.4 "Voltage Regulator Pins (ENVREG/DISVREG and VCAP/VDDCORE)")

These pins must also be connected if they are being used in the end application:

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see Section 2.5 "ICSP Pins")

- · OSCI and OSCO pins when an external oscillator source is used

(see Section 2.6 "External Oscillator Pins")

Additionally, the following pins may be required:

VREF+/VREF- pins used when external voltage reference for analog modules is implemented

The AVDD and AVSS pins must always be Note: connected, regardless of whether any of the analog modules are being used.

The minimum mandatory connections are shown in Figure 2-1.

### RECOMMENDED FIGURE 2-1: MINIMUM CONNECTIONS C2<sup>(2)</sup> Vdd ŹR1 20 /ss (1) (1) R2 (EN/DIS)VREG

PIC24FXXXX

VCAP/VDDCORE

20/

C4<sup>(2)</sup>

VDD

Vss

/SS

C7

C3(2)

### Key (all values are recommendations):

AVDD

AVSS

C1 through C6: 0.1 µF, 20V ceramic

C7: 10  $\mu\text{F},\,6.3\text{V}$  or greater, tantalum or ceramic

C5<sup>(2)</sup>

R1: 10 kΩ

- R2: 100Ω to 470Ω

- Note 1: See Section 2.4 "Voltage Regulator Pins (ENVREG/DISVREG and VCAP/VDDCORE)" for explanation of ENVREG/DISVREG pin connections.

- 2: The example shown is for a PIC24F device with five VDD/VSS and AVDD/AVSS pairs. Other devices may have more or less pairs; adjust the number of decoupling capacitors appropriately.

### TABLE 4-10: UART REGISTER MAPS

| File Name      | Addr | Bit 15                         | Bit 14     | Bit 13           | Bit 12     | Bit 11      | Bit 10  | Bit 9   | Bit 8      | Bit 7         | Bit 6    | Bit 5 | Bit 4       | Bit 3 | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|----------------|------|--------------------------------|------------|------------------|------------|-------------|---------|---------|------------|---------------|----------|-------|-------------|-------|--------|--------|-------|---------------|

| U1MODE         | 0220 | UARTEN                         | _          | USIDL            | IREN       | RTSMD       | —       | UEN1    | UEN0       | WAKE          | LPBACK   | ABAUD | RXINV       | BRGH  | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U1STA          | 0222 | UTXISEL1                       | UTXINV     | UTXISEL0         | _          | UTXBRK      | UTXEN   | UTXBF   | TRMT       | URXISEL1      | URXISEL0 | ADDEN | RIDLE       | PERR  | FERR   | OERR   | URXDA | 0110          |

| U1TXREG        | 0224 | —                              |            | —                | —          | —           | —       |         |            |               |          | Trar  | smit Regist | er    |        |        |       | xxxx          |

| U1RXREG        | 0226 | _                              |            | _                | —          | _           | —       |         |            |               |          | Rec   | eive Regist | er    |        |        |       | 0000          |

| U1BRG          | 0228 |                                |            |                  |            |             |         | Baud Ra | ate Genera | tor Prescaler | Register |       |             |       |        |        |       | 0000          |

| U2MODE         | 0230 | UARTEN                         | _          | USIDL            | IREN       | RTSMD       | —       | UEN1    | UEN0       | WAKE          | LPBACK   | ABAUD | RXINV       | BRGH  | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U2STA          | 0232 | UTXISEL1                       | UTXINV     | UTXISEL0         | —          | UTXBRK      | UTXEN   | UTXBF   | TRMT       | URXISEL1      | URXISEL0 | ADDEN | RIDLE       | PERR  | FERR   | OERR   | URXDA | 0110          |

| U2TXREG        | 0234 | —                              |            | —                | —          | —           | —       |         |            |               |          | Trar  | smit Regist | er    |        |        |       | xxxx          |

| U2RXREG        | 0236 | —                              | _          | Receive Register |            |             |         |         |            |               | 0000     |       |             |       |        |        |       |               |

| U2BRG          | 0238 |                                |            |                  |            |             |         | Baud Ra | ate Genera | tor Prescaler | Register |       |             |       |        |        |       | 0000          |

| U3MODE         | 0250 | UARTEN                         |            | USIDL            | IREN       | RTSMD       | —       | UEN1    | UEN0       | WAKE          | LPBACK   | ABAUD | RXINV       | BRGH  | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U3STA          | 0252 | UTXISEL1                       | UTXINV     | UTXISEL0         | —          | UTXBRK      | UTXEN   | UTXBF   | TRMT       | URXISEL1      | URXISEL0 | ADDEN | RIDLE       | PERR  | FERR   | OERR   | URXDA | 0110          |

| <b>U3TXREG</b> | 0254 | _                              |            | _                | —          | _           | —       |         |            |               |          | Trar  | smit Regist | ter   |        |        |       | xxxx          |

| <b>U3RXREG</b> | 0256 | —                              |            | —                | —          | —           | —       |         |            |               |          | Rec   | eive Regist | er    |        |        |       | 0000          |

| U3BRG          | 0258 |                                |            |                  |            |             |         | Baud Ra | ate Genera | tor Prescaler | Register |       |             |       |        |        |       | 0000          |

| U4MODE         | 02B0 | UARTEN                         |            | USIDL            | IREN       | RTSMD       | —       | UEN1    | UEN0       | WAKE          | LPBACK   | ABAUD | RXINV       | BRGH  | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U4STA          | 02B2 | UTXISEL1                       | UTXINV     | UTXISEL0         | —          | UTXBRK      | UTXEN   | UTXBF   | TRMT       | URXISEL1      | URXISEL0 | ADDEN | RIDLE       | PERR  | FERR   | OERR   | URXDA | 0110          |

| U4TXREG        | 02B4 | —                              |            | —                | —          | —           | —       |         |            |               |          | Trar  | smit Regist | er    |        |        |       | xxxx          |

| U4RXREG        | 02B6 | — — — — — — — Receive Register |            |                  |            |             |         |         |            | 0000          |          |       |             |       |        |        |       |               |

| U4BRG          | 02B8 |                                |            |                  |            |             |         | Baud Ra | ate Genera | tor Prescaler | Register |       |             |       |        |        |       | 0000          |

| Legend:        | = un | implementer                    | read as 'n | . Reset valu     | les are sh | own in hey: | decimal |         |            |               |          |       |             |       |        |        |       |               |

d. read as 0. Reset values are snown in nexadecimal

### TABLE 4-11: SPI REGISTER MAPS

| File Name | Addr | Bit 15 | Bit 14                        | Bit 13  | Bit 12 | Bit 11 | Bit 10  | Bit 9   | Bit 8        | Bit 7      | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|--------|-------------------------------|---------|--------|--------|---------|---------|--------------|------------|--------|--------|--------|--------|--------|--------|--------|---------------|

| SPI1STAT  | 0240 | SPIEN  | _                             | SPISIDL | _      | -      | SPIBEC2 | SPIBEC1 | SPIBEC0      | SRMPT      | SPIROV | SRXMPT | SISEL2 | SISEL1 | SISEL0 | SPITBF | SPIRBF | 0000          |

| SPI1CON1  | 0242 | _      | _                             | _       | DISSCK | DISSDO | MODE16  | SMP     | CKE          | SSEN       | CKP    | MSTEN  | SPRE2  | SPRE1  | SPRE0  | PPRE1  | PPRE0  | 0000          |

| SPI1CON2  | 0244 | FRMEN  | SPIFSD                        | SPIFPOL | _      | _      | _       | _       | _            | _          | _      | _      | _      | _      | _      | SPIFE  | SPIBEN | 0000          |

| SPI1BUF   | 0248 |        | Transmit and Receive Buffer   |         |        |        |         |         |              |            |        |        | 0000   |        |        |        |        |               |

| SPI2STAT  | 0260 | SPIEN  | _                             | SPISIDL | _      | _      | SPIBEC2 | SPIBEC1 | SPIBEC0      | SRMPT      | SPIROV | SRXMPT | SISEL2 | SISEL1 | SISEL0 | SPITBF | SPIRBF | 0000          |

| SPI2CON1  | 0262 | _      | _                             | _       | DISSCK | DISSDO | MODE16  | SMP     | CKE          | SSEN       | CKP    | MSTEN  | SPRE2  | SPRE1  | SPRE0  | PPRE1  | PPRE0  | 0000          |

| SPI2CON2  | 0264 | FRMEN  | SPIFSD                        | SPIFPOL | _      | _      | —       | —       | _            | _          | _      | _      | _      | _      | _      | SPIFE  | SPIBEN | 0000          |

| SPI2BUF   | 0268 |        |                               |         |        |        |         | Tra     | ansmit and I | Receive Bu | ffer   |        |        |        |        |        |        | 0000          |

| SPI3STAT  | 0280 | SPIEN  | _                             | SPISIDL | _      | _      | SPIBEC2 | SPIBEC1 | SPIBEC0      | SRMPT      | SPIROV | SRXMPT | SISEL2 | SISEL1 | SISEL0 | SPITBF | SPIRBF | 0000          |

| SPI3CON1  | 0282 | _      |                               | _       | DISSCK | DISSDO | MODE16  | SMP     | CKE          | SSEN       | CKP    | MSTEN  | SPRE2  | SPRE1  | SPRE0  | PPRE1  | PPRE0  | 0000          |

| SPI3CON2  | 0284 | FRMEN  | SPIFSD                        | SPIFPOL | _      | _      | —       | —       | _            | _          | _      | _      | —      | —      | —      | SPIFE  | SPIBEN | 0000          |

| SPI3BUF   | 0288 |        | Transmit and Receive Buffer 0 |         |        |        |         |         |              |            |        | 0000   |        |        |        |        |        |               |

| Legend:   |      |        |                               |         |        |        |         |         |              |            |        |        |        |        |        |        |        |               |

© 2009 Microchip Technology Inc.

### 4.3.2 DATA ACCESS FROM PROGRAM MEMORY USING TABLE **INSTRUCTIONS**

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the program space without going through data space. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a program space word as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to data space addresses. Program memory can thus be regarded as two, 16-bit word-wide address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space which contains the least significant data word, and TBLRDH and TBLWTH access the space which contains the upper data byte.

Two table instructions are provided to move byte or word-sized (16-bit) data to and from program space. Both function as either byte or word operations.

TBLRDL (Table Read Low): In Word mode, it 1. maps the lower word of the program space location (P<15:0>) to a data address (D<15:0>). In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when byte select is '1'; the lower byte is selected when it is '0'.

2. TBLRDH (Table Read High): In Word mode, it maps the entire upper word of a program address (P<23:16>) to a data address. Note that D<15:8>, the 'phantom' byte, will always be '0'. In Byte mode, it maps the upper or lower byte of the program word to D<7:0> of the data address, as above. Note that the data will always be '0' when the upper 'phantom' byte is selected (byte select = 1).

In a similar fashion, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a program space address. The details of their operation are explained in Section 5.0 "Flash Program Memory".

For all table operations, the area of program memory space to be accessed is determined by the Table Memory Page Address register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

Note: Only table read operations will execute in the configuration memory space, and only then, in implemented areas such as the Device ID. Table write operations are not allowed.

| FIGURE 4-6:             | ACCESSING PROGRAM MEMORY WITH TABLE INSTRUCTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         | Program Space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 782, <i>894%</i><br>(82 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                         | 23       15       6       6000000       23       16       8       0         0200000       00000000       00000000       00000000       00000000       00000000       00000000         0200000       00000000       00000000       00000000       00000000       00000000         0200000       00000000       00000000       00000000       00000000       00000000         0200000       00000000       00000000       00000000       00000000       00000000         0200000       00000000       00000000       00000000       00000000       00000000         0200000       00000000       00000000       00000000       00000000       0000000         0200000       00000000       00000000       00000000       00000000       0000000         0200000       0000000       0000000       0000000       0000000       0000000         0200000       0000000       0000000       0000000       0000000       0000000         0200000       0000000       00000000       00000000       0000000       0000000         02000000       00000000       000000000       00000000       00000000       0000000         02000000       0000000       000000000 </th |

© 2009 Microchip Technology Inc.

| U-0          | R/W-1         | R/W-0                                | R/W-0             | U-0                | R/W-1            | R/W-0            | R/W-0            |

|--------------|---------------|--------------------------------------|-------------------|--------------------|------------------|------------------|------------------|

| _            | IC8IP2        | IC8IP1                               | IC8IP0            | _                  | IC7IP2           | IC7IP1           | IC7IP0           |

| oit 15       |               |                                      |                   |                    |                  |                  | bit              |

|              |               |                                      |                   |                    |                  | DAVO             |                  |

| U-0          | U-0           | U-0                                  | U-0               | U-0                | R/W-1<br>INT1IP2 | R/W-0<br>INT1IP1 | R/W-0<br>INT1IP0 |

| <br>bit 7    |               | _                                    |                   | _                  | INT IF2          |                  | bit              |

|              |               |                                      |                   |                    |                  |                  |                  |

| Legend:      |               |                                      |                   |                    |                  |                  |                  |

| R = Readat   |               | W = Writable                         |                   | •                  | nented bit, read |                  |                  |

| -n = Value a | at POR        | '1' = Bit is set                     | i .               | '0' = Bit is clea  | ared             | x = Bit is unkr  | iown             |

| bit 15       | Unimplemen    | ted: Read as '                       | 0'                |                    |                  |                  |                  |

| bit 14-12    | -             |                                      |                   | rupt Priority bits | s                |                  |                  |

| 510 TT 12    |               | pt is priority 7 (                   |                   |                    |                  |                  |                  |

|              | •             |                                      | ingricer priority | interrupt)         |                  |                  |                  |

|              | •             |                                      |                   |                    |                  |                  |                  |

|              | •             |                                      |                   |                    |                  |                  |                  |

|              | 001 = Interru |                                      |                   |                    |                  |                  |                  |

|              | -             | pt source is dis                     |                   |                    |                  |                  |                  |

| bit 11       | -             | ted: Read as '                       |                   |                    |                  |                  |                  |

| bit 10-8     |               |                                      |                   | rupt Priority bits | S                |                  |                  |

|              | 111 = Interru | pt is priority 7 (                   | highest priority  | interrupt)         |                  |                  |                  |

|              | •             |                                      |                   |                    |                  |                  |                  |

|              | •             |                                      |                   |                    |                  |                  |                  |

|              | 001 = Interru | pt is priority 1                     |                   |                    |                  |                  |                  |

|              |               | pt source is dis                     | abled             |                    |                  |                  |                  |

| bit 7-3      |               | ted: Read as '                       |                   |                    |                  |                  |                  |

| bit 2-0      | -             | External Inter                       |                   | oits               |                  |                  |                  |

|              |               | pt is priority 7 (                   |                   |                    |                  |                  |                  |

|              | •             |                                      |                   |                    |                  |                  |                  |

|              | •             |                                      |                   |                    |                  |                  |                  |

|              | •             |                                      |                   |                    |                  |                  |                  |

|              |               |                                      |                   |                    |                  |                  |                  |

|              | 001 = Interru | pt is priority 1<br>pt source is dis |                   |                    |                  |                  |                  |

### REGISTER 7-22: IPC5: INTERRUPT PRIORITY CONTROL REGISTER 5

| U-0          | R/W-1              | R/W-0                                | R/W-0            | U-0               | R/W-1            | R/W-0           | R/W-0   |

|--------------|--------------------|--------------------------------------|------------------|-------------------|------------------|-----------------|---------|

| _            | CRCIP2             | CRCIP1                               | CRCIP0           | —                 | U2ERIP2          | U2ERIP1         | U2ERIP0 |

| bit 15       |                    |                                      |                  |                   |                  |                 | bit 8   |

|              |                    |                                      |                  |                   |                  |                 |         |

| U-0          | R/W-1              | R/W-0                                | R/W-0            | U-0               | U-0              | U-0             | U-0     |

|              | U1ERIP2            | U1ERIP1                              | U1ERIP0          |                   |                  |                 |         |

| bit 7        |                    |                                      |                  |                   |                  |                 | bit 0   |

| [            |                    |                                      |                  |                   |                  |                 |         |

| Legend:      |                    |                                      |                  |                   |                  |                 |         |

| R = Readab   |                    | W = Writable                         |                  | -                 | nented bit, read |                 |         |

| -n = Value a | at POR             | '1' = Bit is set                     |                  | '0' = Bit is cle  | ared             | x = Bit is unkr | nown    |

|              |                    |                                      |                  |                   |                  |                 |         |

| bit 15       | -                  | ted: Read as '                       |                  |                   |                  |                 |         |

| bit 14-12    | CRCIP<2:0>:        | CRC Generate                         | or Error Interru | upt Priority bits |                  |                 |         |

|              | 111 = Interru      | pt is priority 7 (I                  | highest priority | / interrupt)      |                  |                 |         |

|              | •                  |                                      |                  |                   |                  |                 |         |

|              | •                  |                                      |                  |                   |                  |                 |         |

|              | 001 = Interru      | pt is priority 1                     |                  |                   |                  |                 |         |

|              |                    | pt source is dis                     | abled            |                   |                  |                 |         |

| bit 11       | Unimplemen         | ted: Read as '                       | o'               |                   |                  |                 |         |

| bit 10-8     | U2ERIP<2:0>        | : UART2 Error                        | Interrupt Prio   | rity bits         |                  |                 |         |

|              | 111 = Interru      | pt is priority 7 (I                  | highest priority | / interrupt)      |                  |                 |         |

|              | •                  |                                      |                  |                   |                  |                 |         |

|              | •                  |                                      |                  |                   |                  |                 |         |

|              | 001 = Interru      | pt is priority 1                     |                  |                   |                  |                 |         |

|              |                    | pt source is dis                     | abled            |                   |                  |                 |         |

| bit 7        | Unimplemen         | ted: Read as '                       | o'               |                   |                  |                 |         |

| bit 6-4      | U1ERIP<2:0>        | -: UART1 Error                       | Interrupt Prio   | rity bits         |                  |                 |         |

|              | 111 = Interru      | pt is priority 7 (l                  | highest priority | / interrupt)      |                  |                 |         |

|              | •                  |                                      |                  |                   |                  |                 |         |

|              | •                  |                                      |                  |                   |                  |                 |         |

|              | •<br>001 = Interru | nt is priority 1                     |                  |                   |                  |                 |         |

|              |                    | pt is priority i<br>pt source is dis | abled            |                   |                  |                 |         |

| bit 3-0      | -                  | ted: Read as '                       |                  |                   |                  |                 |         |

|              | •                  |                                      |                  |                   |                  |                 |         |

### REGISTER 7-32: IPC16: INTERRUPT PRIORITY CONTROL REGISTER 16

| R-0           | U-0                                                                                                                                                                                                                                                                                                       | R/W-0                                | U-0              | R-0                                                  | R-0              | R-0               | R-0             |  |  |  |  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|------------------|------------------------------------------------------|------------------|-------------------|-----------------|--|--|--|--|

| CPUIRQ        | _                                                                                                                                                                                                                                                                                                         | VHOLD                                | _                | ILR3                                                 | ILR2             | ILR1              | ILR0            |  |  |  |  |

| bit 15        |                                                                                                                                                                                                                                                                                                           |                                      |                  |                                                      |                  |                   | bit 8           |  |  |  |  |

|               |                                                                                                                                                                                                                                                                                                           |                                      |                  |                                                      |                  |                   |                 |  |  |  |  |

| U-0           | R-0                                                                                                                                                                                                                                                                                                       | R-0                                  | R-0              | R-0                                                  | R-0              | R-0               | R-0             |  |  |  |  |

|               | VECNUM6                                                                                                                                                                                                                                                                                                   | VECNUM5                              | VECNUM4          | VECNUM3                                              | VECNUM2          | VECNUM1           | VECNUM0         |  |  |  |  |

| bit 7         |                                                                                                                                                                                                                                                                                                           |                                      |                  |                                                      |                  |                   | bit 0           |  |  |  |  |

|               |                                                                                                                                                                                                                                                                                                           |                                      |                  |                                                      |                  |                   |                 |  |  |  |  |

| Legend:       |                                                                                                                                                                                                                                                                                                           |                                      |                  |                                                      |                  |                   |                 |  |  |  |  |

| R = Readable  |                                                                                                                                                                                                                                                                                                           | W = Writable                         | DIt              | •                                                    | nented bit, read |                   |                 |  |  |  |  |

| -n = Value at | POR                                                                                                                                                                                                                                                                                                       | '1' = Bit is set                     |                  | '0' = Bit is clea                                    | ared             | x = Bit is unkr   | iown            |  |  |  |  |

| bit 15        | <ul> <li>CPUIRQ: Interrupt Request from Interrupt Controller CPU bit</li> <li>1 = An interrupt request has occurred but has not yet been Acknowledged by the CPU; this happens when the CPU priority is higher than the interrupt priority</li> <li>0 = No interrupt request is unacknowledged</li> </ul> |                                      |                  |                                                      |                  |                   |                 |  |  |  |  |

| bit 14        | Unimplemente                                                                                                                                                                                                                                                                                              | ed: Read as '0'                      |                  |                                                      |                  |                   |                 |  |  |  |  |

| bit 13        | VHOLD: Vect                                                                                                                                                                                                                                                                                               | or Number Cap                        | oture Configura  | ation bit                                            |                  |                   |                 |  |  |  |  |

|               | 0 = VECNUM                                                                                                                                                                                                                                                                                                | 1 contains the                       | value of the la  | hest priority pe<br>st Acknowledg<br>PU, even if oth | ed interrupt (i. | e., the last inte | errupt that has |  |  |  |  |

| bit 12        | Unimplemente                                                                                                                                                                                                                                                                                              | ed: Read as '0'                      | -                |                                                      | ·                |                   |                 |  |  |  |  |

| bit 11-8      | ILR<3:0>: Ne                                                                                                                                                                                                                                                                                              | w CPU Interrup                       | ot Priority Leve | l bits                                               |                  |                   |                 |  |  |  |  |

|               | 1111 = CPU  <br>•                                                                                                                                                                                                                                                                                         | Interrupt Priorit                    | y Level is 15    |                                                      |                  |                   |                 |  |  |  |  |

|               | •                                                                                                                                                                                                                                                                                                         |                                      |                  |                                                      |                  |                   |                 |  |  |  |  |

|               |                                                                                                                                                                                                                                                                                                           | Interrupt Priorit                    |                  |                                                      |                  |                   |                 |  |  |  |  |

| bit 7         | Unimplemente                                                                                                                                                                                                                                                                                              | ed: Read as '0'                      |                  |                                                      |                  |                   |                 |  |  |  |  |

| bit 6-0       |                                                                                                                                                                                                                                                                                                           | D>: Pending Int<br>terrupt vector p  |                  | D bits (pending<br>ber 135                           | vector number    | r is VECNUM +     | - 8)            |  |  |  |  |

|               |                                                                                                                                                                                                                                                                                                           | terrupt vector p<br>terrupt vector p |                  |                                                      |                  |                   |                 |  |  |  |  |

### REGISTER 7-39: INTTREG: INTERRUPT CONTROL AND STATUS REGISTER

| U-0    | U-0 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|--------|-----|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| —      | —   | RP31R5 <sup>(1)</sup> | RP31R4 <sup>(1)</sup> | RP31R3 <sup>(1)</sup> | RP31R2 <sup>(1)</sup> | RP31R1 <sup>(1)</sup> | RP31R0 <sup>(1)</sup> |

| bit 15 |     |                       |                       |                       |                       |                       | bit 8                 |

| U-0   | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | RP30R5 | RP30R4 | RP30R3 | RP30R2 | RP30R1 | RP30R0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP31R<5:0>:** RP31 Output Pin Mapping bits<sup>(1)</sup>

Peripheral output number n is assigned to pin, RP31 (see Table 10-3 for peripheral function numbers)bit 7-6 Unimplemented: Read as '0'

Dil 7-6 Unimplemented: Read as 0

bit 5-0 RP30R<5:0>: RP30 Output Pin Mapping bits<sup>(2)</sup>

Peripheral output number n is assigned to pin, RP30 (see Table 10-3 for peripheral function numbers)

Note 1: Unimplemented on 64-pin and 80-pin devices; read as '0'.

2: Unimplemented on 64-pin devices; read as '0'.

### REGISTER 16-2: I2CxSTAT: I2Cx STATUS REGISTER

| R-0, HSC            | R-0, HSC                                                                                                                                                                                                                                                                                                                                                                                                                                                           | U-0                                             | U-0                                                | U-0                                                            | R/C-0, HS        | R-0, HSC              | R-0, HSC              |  |  |  |  |  |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|----------------------------------------------------|----------------------------------------------------------------|------------------|-----------------------|-----------------------|--|--|--|--|--|

| ACKSTAT             | TRSTAT                                                                                                                                                                                                                                                                                                                                                                                                                                                             | _                                               | _                                                  | _                                                              | BCL              | GCSTAT                | ADD10                 |  |  |  |  |  |

| bit 15              | 11.01/1                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                 |                                                    |                                                                | DOL              | 0001/11               | bit 8                 |  |  |  |  |  |

|                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                 |                                                    |                                                                |                  |                       | bit o                 |  |  |  |  |  |

| R/C-0, HS           | R/C-0, HS                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R-0, HSC                                        | R/C-0, HSC                                         | R/C-0, HSC                                                     | R-0, HSC         | R-0, HSC              | R-0, HSC              |  |  |  |  |  |

| IWCOL               | I2COV                                                                                                                                                                                                                                                                                                                                                                                                                                                              | D/A                                             | Р                                                  | S                                                              | R/W              | RBF                   | TBF                   |  |  |  |  |  |

| bit 7               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                 |                                                    |                                                                | I                | I                     | bit 0                 |  |  |  |  |  |

|                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                 |                                                    |                                                                |                  |                       |                       |  |  |  |  |  |

| Legend:             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | C = Clearal                                     | ole bit                                            | HS = Hardwar                                                   | e Settable bit   | HSC = Hardware S      | ettable/Clearable bit |  |  |  |  |  |

| R = Reada           | ble bit                                                                                                                                                                                                                                                                                                                                                                                                                                                            | W = Writab                                      | le bit                                             | U = Unimplen                                                   | nented bit, read | l as '0'              |                       |  |  |  |  |  |

| -n = Value          | at POR                                                                                                                                                                                                                                                                                                                                                                                                                                                             | '1' = Bit is s                                  | set                                                | '0' = Bit is clea                                              | ared             | x = Bit is unknown    |                       |  |  |  |  |  |

| bit 15<br>bit 14    | ACKSTAT: Acknowledge Status bit<br>1 = NACK was detected last<br>0 = ACK was detected last<br>Hardware set or clear at end of Acknowledge.<br>TRSTAT: Transmit Status bit<br>(When operating as I <sup>2</sup> C master. Applicable to master transmit operation.)<br>1 = Master transmit is in progress (8 bits + ACK)<br>0 = Master transmit is not in progress<br>Hardware set at beginning of master transmission. Hardware clear at end of slave Acknowledge. |                                                 |                                                    |                                                                |                  |                       |                       |  |  |  |  |  |

|                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -                                               | -                                                  | r transmission.                                                | Hardware clea    | ar at end of slave Ac | knowledge.            |  |  |  |  |  |

| bit 13-11<br>bit 10 | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ented: Rea                                      | a as <sup>r</sup> 0 <sup>r</sup><br>sion Detect bi | :4                                                             |                  |                       |                       |  |  |  |  |  |

|                     | 1 = A bus o<br>0 = No coll<br>Hardware s                                                                                                                                                                                                                                                                                                                                                                                                                           | collision has<br>ision<br>set at detect         | been detecte                                       | ed during a ma                                                 | ster operation   |                       |                       |  |  |  |  |  |

| bit 9               | 1 = Genera<br>0 = Genera                                                                                                                                                                                                                                                                                                                                                                                                                                           | al call addres                                  | ss was receiv<br>ss was not re                     | ceived                                                         | address. Hardv   | vare clear at Stop de | etection.             |  |  |  |  |  |

| bit 8               | 1 = 10-bit a<br>0 = 10-bit a                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                 | matched<br>not matched                             |                                                                | bit address. Ha  | irdware clear at Stop | o detection.          |  |  |  |  |  |

| bit 7               | <ul> <li>Hardware set at match of 2nd byte of matched 10-bit address. Hardware clear at Stop detection.</li> <li>IWCOL: Write Collision Detect bit</li> <li>1 = An attempt to write the I2CxTRN register failed because the I<sup>2</sup>C module is busy</li> <li>0 = No collision</li> <li>Hardware set at occurrence of write to I2CxTRN while busy (cleared by software).</li> </ul>                                                                           |                                                 |                                                    |                                                                |                  |                       |                       |  |  |  |  |  |

| bit 6               | I2COV: Receive Overflow Flag bit<br>1 = A byte was received while the I2CxRCV register is still holding the previous byte<br>0 = No overflow<br>Hardware set at attempt to transfer I2CxRSR to I2CxRCV (cleared by software).                                                                                                                                                                                                                                      |                                                 |                                                    |                                                                |                  |                       |                       |  |  |  |  |  |

| bit 5               | D/A: Data/<br>1 = Indicate<br>0 = Indicate                                                                                                                                                                                                                                                                                                                                                                                                                         | Address bit<br>es that the la<br>es that the la | (when operat<br>ast byte recei<br>ast byte recei   | ing as I <sup>2</sup> C slav<br>ved was data<br>ved was device | e)<br>e address  |                       | s, or by reception of |  |  |  |  |  |

### 18.1.2.3 VBUS Voltage Generation with External Devices

When operating as a USB host, either as an A-device in an OTG configuration or as an embedded host, VBUS must be supplied to the attached device. PIC24FJ256GB110 family devices have an internal VBUS boost assist to help generate the required 5V VBUS from the available voltages on the board. This is comprised of a simple PWM output to control a Switch mode power supply, and built-in comparators to monitor output voltage and limit current.

To enable voltage generation:

- Verify that the USB module is powered (U1PWRC<0> = 1) and that the VBUS discharge is disabled (U1OTGCON<0> = 0).

- 2. Set the PWM period (U1PWMRRS<7:0>) and duty cycle (U1PWMRRS<15:8>) as required.

- 3. Select the required polarity of the output signal based on the configuration of the external circuit with the PWMPOL bit (U1PWMCON<9>).

- 4. Select the desired target voltage using the VBUSCHG bit (U1OTGCON<1>).

- 5. Enable the PWM counter by setting the CNTEN bit to '1' (U1PWMCON<8>).

- 6. Enable the PWM module by setting the PWMEN bit to '1' (U1PWMCON<15>).

- 7. Enable the VBUS generation circuit (U10TGCON<3> = 1).

- Note: This section describes the general process for VBUS voltage generation and control. Please refer to the "*PIC24F Family Reference Manual*" for additional examples.

### 18.1.3 USING AN EXTERNAL INTERFACE

Some applications may require the USB interface to be isolated from the rest of the system. PIC24FJ256GB110 family devices include a complete interface to communicate with and control an external USB transceiver, including the control of data line pull-ups and pull-downs. The VBUS voltage generation control circuit can also be configured for different VBUS generation topologies.

Please refer to the *"PIC24F Family Reference Manual"*, **Section 27. "USB On-The-Go (OTG)**" for information on using the external interface.

### 18.1.4 CALCULATING TRANSCEIVER POWER REQUIREMENTS

The USB transceiver consumes a variable amount of current depending on the characteristic impedance of the USB cable, the length of the cable, the VUSB supply voltage and the actual data patterns moving across the USB cable. Longer cables have larger capacitances and consume more total energy when switching output states. The total transceiver current consumption will be application-specific. Equation 18-1 can help estimate how much current actually may be required in full-speed applications.

Please refer to the *"PIC24F Family Reference Manual"*, **Section 27. "USB On-The-Go (OTG)"** for a complete discussion on transceiver power consumption.

### EQUATION 18-1: ESTIMATING USB TRANSCEIVER CURRENT CONSUMPTION

$Ixcvr = \frac{(40 \text{ mA} \cdot \text{VUSB} \cdot \text{PZERO} \cdot \text{PIN} \cdot \text{LCABLE})}{(3.3V \cdot 5m)} + IPULLUP$

Legend: VUSB – Voltage applied to the VUSB pin in volts (3.0V to 3.6V).

PZERO - Percentage (in decimal) of the IN traffic bits sent by the  $PIC^{\$}$  microcontroller that are a value of '0'.

PIN – Percentage (in decimal) of total bus bandwidth that is used for IN traffic.

LCABLE – Length (in meters) of the USB cable. The USB 2.0 Specification requires that full-speed applications use cables no longer than 5m.

IPULLUP – Current which the nominal, 1.5 k $\Omega$  pull-up resistor (when enabled) must supply to the USB cable.

| U-0          | U-0                             | U-0                                    | U-0             | U-0                 | U-0              | U-0                | U-0           |

|--------------|---------------------------------|----------------------------------------|-----------------|---------------------|------------------|--------------------|---------------|

| —            | —                               | —                                      | —               | —                   | —                | —                  |               |

| bit 15       |                                 |                                        |                 |                     |                  |                    | bit           |

| R-x, HSC     | R-x, HSC                        | R/W-0                                  | R/W-0           | R/W-0               | R/W-0            | R/W-0              | R/W-0         |

| JSTATE       | SE0                             | TOKBUSY                                | USBRST          | HOSTEN              | RESUME           | PPBRST             | SOFEN         |

| bit 7        | 3EU                             | TURBUST                                | USDRST          | HUSTEN              | RESUME           | FFDROI             | bit           |

|              |                                 |                                        |                 |                     |                  |                    |               |

| Legend:      |                                 | U = Unimplem                           | ented bit, read | 1 as '0'            |                  |                    |               |

| R = Readab   | le bit                          | W = Writable t                         | bit             | HSC = Hardw         | are Settable/C   | learable bit       |               |

| -n = Value a | t POR                           | '1' = Bit is set                       |                 | '0' = Bit is clea   | ared             | x = Bit is unkn    | iown          |

|              |                                 |                                        |                 |                     |                  |                    |               |

| bit 15-8     | -                               | ited: Read as '0                       |                 |                     |                  |                    |               |

| bit 7        |                                 | e Differential Re                      |                 | •                   |                  |                    | <b>D</b>      |

|              | 1 = J state (0<br>0 = No J stat | differential '0' in te detected        | low speed, dif  | terential '1' in fi | ull speed) dete  | cted on the US     | В             |

| oit 6        | SE0: Live Sir                   | ngle-Ended Zero                        | Flag bit        |                     |                  |                    |               |

|              |                                 | nded zero active                       |                 | ous                 |                  |                    |               |

|              | •                               | e-ended zero de                        |                 |                     |                  |                    |               |

| bit 5        |                                 | oken Busy Statu                        |                 |                     | <b>•</b> • •     |                    |               |

|              |                                 | eing executed by<br>being executed     |                 | dule in On-The-     | Go state         |                    |               |

| bit 4        |                                 | dule Reset bit                         | •               |                     |                  |                    |               |

|              |                                 | set has been ge                        | nerated; for so | oftware Reset,      | application mu   | st set this bit fo | or 50 ms, the |

|              | clear it                        | Ū                                      | ,               | ,                   |                  |                    | ,             |

|              |                                 | set terminated                         |                 |                     |                  |                    |               |

| bit 3        |                                 | st Mode Enable                         |                 |                     |                  | ·                  |               |

|              |                                 | t capability enal<br>t capability disa |                 | is on D+ and D      | - are activated  | in hardware        |               |

| bit 2        |                                 | esume Signaling                        |                 |                     |                  |                    |               |

|              |                                 | signaling activat                      |                 | ust set bit for 10  | ) ms and then cl | ear to enable re   | mote wake-u   |

|              | 0 = Resume                      | signaling disabl                       | ed              |                     |                  |                    |               |

| bit 1        |                                 | ig-Pong Buffers                        |                 |                     |                  |                    |               |

|              |                                 | Il Ping-Pong But<br>ng Buffer Pointe   |                 | the EVEN BD         | banks            |                    |               |

|              |                                 |                                        |                 |                     |                  |                    |               |

| bit 0        |                                 |                                        |                 |                     |                  |                    |               |

| bit 0        | SOFEN: Star                     | t-Of-Frame Ena<br>Frame token se       | ble bit         | millisecond         |                  |                    |               |

| U-0          | U-0                                                                                 | U-0                                                   | U-0                          | U-0               | U-0                     | U-0                     | U-0                   |  |  |  |

|--------------|-------------------------------------------------------------------------------------|-------------------------------------------------------|------------------------------|-------------------|-------------------------|-------------------------|-----------------------|--|--|--|

|              | —                                                                                   | —                                                     | —                            | —                 | —                       | —                       |                       |  |  |  |

| pit 15       |                                                                                     | •<br>•                                                |                              |                   |                         |                         | bit 8                 |  |  |  |

|              |                                                                                     |                                                       |                              |                   |                         |                         |                       |  |  |  |

| U-0          | U-0                                                                                 | U-0                                                   | R/W-0                        | R/W-0             | R/W-0                   | R/W-0                   | R/W-0                 |  |  |  |

| —            |                                                                                     |                                                       | PUVBUS                       | EXTI2CEN          | UVBUSDIS <sup>(1)</sup> | UVCMPDIS <sup>(1)</sup> | UTRDIS <sup>(1)</sup> |  |  |  |

| oit 7        |                                                                                     |                                                       |                              |                   |                         |                         | bit (                 |  |  |  |

|              |                                                                                     |                                                       |                              |                   |                         |                         |                       |  |  |  |

| _egend:      |                                                                                     |                                                       |                              |                   |                         |                         |                       |  |  |  |

| R = Readab   |                                                                                     | W = Writable                                          |                              | •                 | nented bit, read        |                         |                       |  |  |  |

| -n = Value a | it POR                                                                              | '1' = Bit is set                                      |                              | '0' = Bit is clea | ared                    | x = Bit is unkn         | own                   |  |  |  |

|              |                                                                                     |                                                       |                              |                   |                         |                         |                       |  |  |  |

| oit 15-5     | -                                                                                   | nted: Read as '                                       |                              |                   |                         |                         |                       |  |  |  |

| oit 4        |                                                                                     | BUS Pull-up Ena                                       |                              |                   |                         |                         |                       |  |  |  |