Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB OTG                                     |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                     |

| Number of I/O              | 51                                                                             |

| Program Memory Size        | 64KB (22K x 24)                                                                |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-TQFP                                                                        |

| Supplier Device Package    | 64-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj64gb106t-i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Features                                            | 64GB106                                                                                                                                             | 128GB106             | 192GB106         | 256GB106      |  |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------------------|---------------|--|

| Operating Frequency                                 |                                                                                                                                                     | DC – 3               | 32 MHz           | -             |  |

| Program Memory (bytes)                              | 64K                                                                                                                                                 | 128K                 | 192K             | 256K          |  |

| Program Memory (instructions)                       | 22,016                                                                                                                                              | 44,032               | 67,072           | 87,552        |  |

| Data Memory (bytes)                                 |                                                                                                                                                     | 16,                  | 384              | •             |  |

| Interrupt Sources (soft vectors/NMI traps)          |                                                                                                                                                     | 66 (                 | 62/4)            |               |  |

| I/O Ports                                           |                                                                                                                                                     | Ports B, C           | , D, E, F, G     |               |  |

| Total I/O Pins                                      |                                                                                                                                                     | 5                    | 51               |               |  |

| Remappable Pins                                     |                                                                                                                                                     | 29 (28 I/O,          | 1 Input only)    |               |  |

| Timers:                                             |                                                                                                                                                     |                      |                  |               |  |

| Total Number (16-bit)                               |                                                                                                                                                     | 5                    | (1)              |               |  |

| 32-Bit (from paired 16-bit timers)                  |                                                                                                                                                     | :                    | 2                |               |  |

| Input Capture Channels                              |                                                                                                                                                     | 9                    | (1)              |               |  |

| Output Compare/PWM Channels                         | 9 <sup>(1)</sup>                                                                                                                                    |                      |                  |               |  |

| Input Change Notification Interrupt                 | 49                                                                                                                                                  |                      |                  |               |  |

| Serial Communications:                              |                                                                                                                                                     |                      |                  |               |  |

| UART                                                |                                                                                                                                                     | 4                    | (1)              |               |  |

| SPI (3-wire/4-wire)                                 |                                                                                                                                                     | 3                    | (1)              |               |  |

| I <sup>2</sup> C™                                   | 3                                                                                                                                                   |                      |                  |               |  |

| Parallel Communications (PMP/PSP)                   | Yes                                                                                                                                                 |                      |                  |               |  |

| JTAG Boundary Scan/Programming                      | Yes                                                                                                                                                 |                      |                  |               |  |

| 10-Bit Analog-to-Digital Module<br>(input channels) |                                                                                                                                                     | 1                    | 6                |               |  |

| Analog Comparators                                  |                                                                                                                                                     | :                    | 3                |               |  |

| CTMU Interface                                      | Yes                                                                                                                                                 |                      |                  |               |  |

| Resets (and delays)                                 | POR, BOR, RESET Instruction, MCLR, WDT; Illegal Opcode,<br>REPEAT Instruction, Hardware Traps, Configuration Word Mismatcl<br>(PWRT, OST, PLL Lock) |                      |                  |               |  |

| Instruction Set                                     | 76 Base In                                                                                                                                          | structions, Multiple | e Addressing Mod | le Variations |  |

| Packages                                            |                                                                                                                                                     | 64-Pin               | TQFP             |               |  |

#### TABLE 1-1:DEVICE FEATURES FOR THE PIC24FJ256GB110 FAMILY: 64-PIN DEVICES

**Note 1:** Peripherals are accessible through remappable pins.

|                   | Vector | IVT Address | AIVT    | Interrupt Bit Locations |          |              |

|-------------------|--------|-------------|---------|-------------------------|----------|--------------|

| Interrupt Source  | Number |             | Address | Flag                    | Enable   | Priority     |

| Timer1            | 3      | 00001Ah     | 00011Ah | IFS0<3>                 | IEC0<3>  | IPC0<14:12>  |

| Timer2            | 7      | 000022h     | 000122h | IFS0<7>                 | IEC0<7>  | IPC1<14:12>  |

| Timer3            | 8      | 000024h     | 000124h | IFS0<8>                 | IEC0<8>  | IPC2<2:0>    |

| Timer4            | 27     | 00004Ah     | 00014Ah | IFS1<11>                | IEC1<11> | IPC6<14:12>  |

| Timer5            | 28     | 00004Ch     | 00014Ch | IFS1<12>                | IEC1<12> | IPC7<2:0>    |

| UART1 Error       | 65     | 000096h     | 000196h | IFS4<1>                 | IEC4<1>  | IPC16<6:4>   |

| UART1 Receiver    | 11     | 00002Ah     | 00012Ah | IFS0<11>                | IEC0<11> | IPC2<14:12>  |

| UART1 Transmitter | 12     | 00002Ch     | 00012Ch | IFS0<12>                | IEC0<12> | IPC3<2:0>    |

| UART2 Error       | 66     | 000098h     | 000198h | IFS4<2>                 | IEC4<2>  | IPC16<10:8>  |

| UART2 Receiver    | 30     | 000050h     | 000150h | IFS1<14>                | IEC1<14> | IPC7<10:8>   |

| UART2 Transmitter | 31     | 000052h     | 000152h | IFS1<15>                | IEC1<15> | IPC7<14:12>  |

| UART3 Error       | 81     | 0000B6h     | 0001B6h | IFS5<1>                 | IEC5<1>  | IPC20<6:4>   |

| UART3 Receiver    | 82     | 0000B8h     | 0001B8h | IFS5<2>                 | IEC5<2>  | IPC20<10:8>  |

| UART3 Transmitter | 83     | 0000BAh     | 0001BAh | IFS5<3>                 | IEC5<3>  | IPC20<14:12> |

| UART4 Error       | 87     | 0000C2h     | 0001C2h | IFS5<7>                 | IEC5<7>  | IPC21<14:12> |

| UART4 Receiver    | 88     | 0000C4h     | 0001C4h | IFS5<8>                 | IEC5<8>  | IPC22<2:0>   |

| UART4 Transmitter | 89     | 0000C6h     | 0001C6h | IFS5<9>                 | IEC5<9>  | IPC22<6:4>   |

| USB Interrupt     | 86     | 0000C0h     | 0001C0h | IFS5<6>                 | IEC5<6>  | IPC21<10:8>  |

## TABLE 7-2: IMPLEMENTED INTERRUPT VECTORS (CONTINUED)

## 7.3 Interrupt Control and Status Registers

The PIC24FJ256GB110 family of devices implements a total of 37 registers for the interrupt controller:

- INTCON1

- INTCON2

- IFS0 through IFS5

- IEC0 through IEC5

- IPC0 through IPC23 (except IPC14 and IPC17)

- INTTREG

Global interrupt control functions are controlled from INTCON1 and INTCON2. INTCON1 contains the Interrupt Nesting Disable (NSTDIS) bit, as well as the control and status flags for the processor trap sources. The INTCON2 register controls the external interrupt request signal behavior and the use of the Alternate Interrupt Vector Table.

The IFSx registers maintain all of the interrupt request flags. Each source of interrupt has a status bit which is set by the respective peripherals, or an external signal, and is cleared via software.

The IECx registers maintain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals.

The IPCx registers are used to set the interrupt priority level for each source of interrupt. Each user interrupt source can be assigned to one of eight priority levels. The INTTREG register contains the associated interrupt vector number and the new CPU interrupt priority level, which are latched into the Vector Number (VECNUM<6:0>) and the Interrupt Level (ILR<3:0>) bit fields in the INTTREG register. The new interrupt priority level is the priority of the pending interrupt.

The interrupt sources are assigned to the IFSx, IECx and IPCx registers in the order of their vector numbers, as shown in Table 7-2. For example, the INT0 (External Interrupt 0) is shown as having a vector number and a natural order priority of 0. Thus, the INT0IF status bit is found in IFS0<0>, the INT0IE enable bit in IEC0<0> and the INT0IP<2:0> priority bits in the first position of IPC0 (IPC0<2:0>).

Although they are not specifically part of the interrupt control hardware, two of the CPU Control registers contain bits that control interrupt functionality. The ALU STATUS register (SR) contains the IPL<2:0> bits (SR<7:5>). These indicate the current CPU interrupt priority level. The user may change the current CPU priority level by writing to the IPL bits.

The CORCON register contains the IPL3 bit, which together with IPL<2:0>, indicates the current CPU priority level. IPL3 is a read-only bit so that trap events cannot be masked by the user software.

All interrupt registers are described in Register 7-1 through Register 7-39, in the following pages.

## REGISTER 7-23: IPC6: INTERRUPT PRIORITY CONTROL REGISTER 6

| U-0              | R/W-1                                                                                 | R/W-0                                                                                  | R/W-0                                              | U-0               | R/W-1            | R/W-0           | R/W-0  |

|------------------|---------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------|-------------------|------------------|-----------------|--------|

| _                | T4IP2                                                                                 | T4IP1                                                                                  | T4IP0                                              |                   | OC4IP2           | OC4IP1          | OC4IP0 |

| bit 15           |                                                                                       | •                                                                                      |                                                    | ·                 |                  | •               | bit 8  |

| U-0              | R/W-1                                                                                 | R/W-0                                                                                  | R/W-0                                              | U-0               | U-0              | U-0             | U-0    |

| —                | OC3IP2                                                                                | OC3IP1                                                                                 | OC3IP0                                             | —                 | _                | —               | —      |

| bit 7            |                                                                                       |                                                                                        |                                                    |                   |                  |                 | bit    |

| Legend:          |                                                                                       |                                                                                        |                                                    |                   |                  |                 |        |

| R = Readab       | ole bit                                                                               | W = Writable                                                                           | bit                                                | U = Unimpler      | nented bit, read | l as '0'        |        |

| -n = Value a     | t POR                                                                                 | '1' = Bit is set                                                                       |                                                    | '0' = Bit is cle  | ared             | x = Bit is unkr | nown   |

|                  |                                                                                       |                                                                                        |                                                    |                   |                  |                 |        |

| bit 15           | Unimplemer                                                                            | nted: Read as 'o                                                                       | )'                                                 |                   |                  |                 |        |

| bit 14-12        | <b>T4IP&lt;2:0&gt;:</b> ⊺                                                             | Timer4 Interrupt                                                                       | Priority bits                                      |                   |                  |                 |        |

|                  | 111 = Interru                                                                         | pt is priority 7 (ł                                                                    | nighest priority                                   | interrupt)        |                  |                 |        |

|                  | •                                                                                     |                                                                                        |                                                    |                   |                  |                 |        |

|                  | •                                                                                     |                                                                                        |                                                    |                   |                  |                 |        |

|                  | 001 = Interru                                                                         | pt is priority 1                                                                       |                                                    |                   |                  |                 |        |

|                  |                                                                                       | pt source is dis                                                                       | abled                                              |                   |                  |                 |        |

| bit 11           | Unimplemer                                                                            | nted: Read as 'd                                                                       | )'                                                 |                   |                  |                 |        |

| bit 10-8         | OC4IP<2:0>                                                                            | : Output Compa                                                                         | re Channel 4                                       | Interrupt Priorit | y bits           |                 |        |

|                  | 111 = Interru                                                                         | pt is priority 7 (ł                                                                    | nighest priority                                   | interrupt)        |                  |                 |        |

|                  | •                                                                                     |                                                                                        |                                                    |                   |                  |                 |        |

|                  | •                                                                                     |                                                                                        |                                                    |                   |                  |                 |        |

|                  |                                                                                       | int is priority 1                                                                      |                                                    |                   |                  |                 |        |

|                  | 001 = Interru                                                                         |                                                                                        |                                                    |                   |                  |                 |        |

|                  | 001 = Interru<br>000 = Interru                                                        | ipt is priority i<br>ipt source is dis                                                 | abled                                              |                   |                  |                 |        |

| bit 7            | 000 = Interru                                                                         |                                                                                        |                                                    |                   |                  |                 |        |

| bit 7<br>bit 6-4 | 000 = Interru<br>Unimplemer                                                           | pt source is dis                                                                       | )'                                                 | Interrupt Priorit | y bits           |                 |        |

|                  | 000 = Interru<br>Unimplemer<br>OC3IP<2:0>                                             | ipt source is dis<br>ited: Read as '(                                                  | )'<br>re Channel 3                                 | •                 | y bits           |                 |        |

|                  | 000 = Interru<br>Unimplemer<br>OC3IP<2:0>                                             | ipt source is dis<br>ited: Read as '(<br>: Output Compa                                | )'<br>re Channel 3                                 | •                 | y bits           |                 |        |

|                  | 000 = Interru<br>Unimplemer<br>OC3IP<2:0>                                             | ipt source is dis<br>ited: Read as '(<br>: Output Compa                                | )'<br>re Channel 3                                 | •                 | y bits           |                 |        |

|                  | 000 = Interru<br>Unimplemer<br>OC3IP<2:0><br>111 = Interru<br>•<br>•                  | ipt source is dis<br>ited: Read as '(<br>: Output Compa                                | )'<br>re Channel 3                                 | •                 | y bits           |                 |        |

|                  | 000 = Interru<br>Unimplemen<br>OC3IP<2:0><br>111 = Interru<br>•<br>•<br>001 = Interru | ipt source is dis<br><b>ited:</b> Read as '(<br>: Output Compa<br>ipt is priority 7 (H | <sub>)</sub> ,<br>re Channel 3<br>highest priority | •                 | y bits           |                 |        |

| <b></b>      |                    |                                      |                  |                   |                  |                 |         |

|--------------|--------------------|--------------------------------------|------------------|-------------------|------------------|-----------------|---------|

| U-0          | R/W-1              | R/W-0                                | R/W-0            | U-0               | R/W-1            | R/W-0           | R/W-0   |

|              | U3TXIP2            | U3TXIP1                              | U3TXIP0          | <u> </u>          | U3RXIP2          | U3RXIP1         | U3RXIP0 |

| bit 15       |                    |                                      |                  |                   |                  |                 | bit 8   |

|              |                    |                                      |                  |                   |                  |                 |         |

| U-0          | R/W-1              | R/W-0                                | R/W-0            | U-0               | U-0              | U-0             | U-0     |

|              | U3ERIP2            | U3ERIP1                              | U3ERIP0          | <u> </u>          |                  |                 |         |

| bit 7        |                    |                                      |                  |                   |                  |                 | bit 0   |

|              |                    |                                      |                  |                   |                  |                 |         |

| Legend:      |                    |                                      |                  |                   |                  |                 |         |

| R = Readab   | ole bit            | W = Writable                         | bit              | U = Unimplen      | nented bit, read | d as '0'        |         |

| -n = Value a | at POR             | '1' = Bit is set                     |                  | '0' = Bit is clea | ared             | x = Bit is unkr | nown    |

|              |                    |                                      |                  |                   |                  |                 |         |

| bit 15       | Unimplemen         | ted: Read as '                       | 0'               |                   |                  |                 |         |

| bit 14-12    | U3TXIP<2:0>        | : UART3 Trans                        | smitter Interrup | ot Priority bits  |                  |                 |         |

|              | 111 = Interru      | pt is priority 7 (                   | highest priority | / interrupt)      |                  |                 |         |

|              | •                  |                                      |                  |                   |                  |                 |         |

|              | •                  |                                      |                  |                   |                  |                 |         |

|              | 001 = Interru      | pt is priority 1                     |                  |                   |                  |                 |         |

|              |                    | pt source is dis                     | abled            |                   |                  |                 |         |

| bit 11       | Unimplemen         | ted: Read as '                       | 0'               |                   |                  |                 |         |

| bit 10-8     | U3RXIP<2:0>        | -: UART3 Rece                        | eiver Interrupt  | Priority bits     |                  |                 |         |

|              | 111 = Interru      | pt is priority 7 (                   | highest priority | / interrupt)      |                  |                 |         |

|              | •                  |                                      |                  |                   |                  |                 |         |

|              | •                  |                                      |                  |                   |                  |                 |         |

|              | •<br>001 = Interru | nt is priority 1                     |                  |                   |                  |                 |         |

|              |                    | pt source is dis                     | abled            |                   |                  |                 |         |

| bit 7        | Unimplemen         | ted: Read as '                       | 0'               |                   |                  |                 |         |

| bit 6-4      | U3ERIP<2:0>        | -: UART3 Error                       | Interrupt Prio   | rity bits         |                  |                 |         |

|              |                    | pt is priority 7 (                   | •                | •                 |                  |                 |         |

|              | •                  |                                      |                  |                   |                  |                 |         |

|              | •                  |                                      |                  |                   |                  |                 |         |

|              | •<br>001 = Interru | nt is priority 1                     |                  |                   |                  |                 |         |

|              |                    | pt is priority i<br>pt source is dis | abled            |                   |                  |                 |         |

| bit 3-0      |                    | ted: Read as '                       |                  |                   |                  |                 |         |

| ···· •       |                    |                                      | -                |                   |                  |                 |         |

#### REGISTER 7-35: IPC20: INTERRUPT PRIORITY CONTROL REGISTER 20

## 8.5 Oscillator Modes and USB Operation

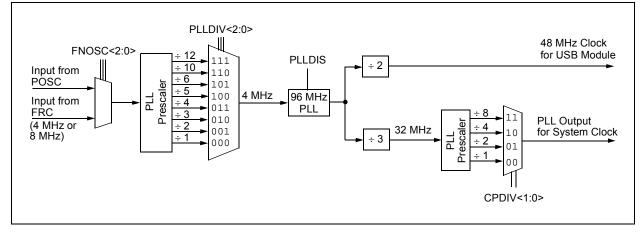

Because of the timing requirements imposed by USB, an internal clock of 48 MHz is required at all times while the USB module is enabled. Since this is well beyond the maximum CPU clock speed, a method is provided to internally generate both the USB and system clocks from a single oscillator source. PIC24FJ256GB110 family devices use the same clock structure as other PIC24FJ devices, but include a two-branch PLL system to generate the two clock signals.

The USB PLL block is shown in Figure 8-2. In this system, the input from the Primary Oscillator is divided down by a PLL prescaler to generate a 4 MHz output. This is used to drive an on-chip 96 MHz PLL frequency multiplier to drive the two clock branches. One branch uses a fixed divide-by-2 frequency divider to generate the 48 MHz USB clock. The other branch uses a fixed divide-by-3 frequency divider and configurable PLL prescaler/divider to generate a range of system clock frequencies. The CPDIV bits select the system clock speed; available clock options are listed in Table 8-2.

The USB PLL prescaler does not automatically sense the incoming oscillator frequency. The user must manually configure the PLL divider to generate the required 4 MHz output, using the PLLDIV<2:0> Configuration bits. This limits the choices for Primary Oscillator frequency to a total of 8 possibilities, shown in Table 8-3.

## FIGURE 8-2: USB PLL BLOCK

## TABLE 8-2:SYSTEM CLOCK OPTIONSDURING USB OPERATION

| MCU Clock Division<br>(CPDIV<1:0>) | Microcontroller<br>Clock Frequency |

|------------------------------------|------------------------------------|

| None (00)                          | 32 MHz                             |

| ÷2(01)                             | 16 MHz                             |

| ÷4 (10)                            | 8 MHz                              |

| ÷8 (11)                            | 4 MHz                              |

| <b>TABLE 8-3</b> : | VALID PRIMARY OSCILLATOR |

|--------------------|--------------------------|

|                    | CONFIGURATIONS FOR USB   |

|                    | OPERATIONS               |

| Input Oscillator<br>Frequency | Clock Mode   | PLL Division<br>(PLLDIV<2:0>) |

|-------------------------------|--------------|-------------------------------|

| 48 MHz                        | ECPLL        | ÷ <b>12 (</b> 111)            |

| 40 MHz                        | ECPLL        | ÷ <b>10 (</b> 110)            |

| 24 MHz                        | HSPLL, ECPLL | ÷6 (101)                      |

| 20 MHz                        | HSPLL, ECPLL | ÷5 (100)                      |

| 16 MHz                        | HSPLL, ECPLL | ÷4(011)                       |

| 12 MHz                        | HSPLL, ECPLL | ÷3(010)                       |

| 8 MHz                         | ECPLL, XTPLL | ÷2(001)                       |

| 4 MHz                         | ECPLL, XTPLL | ÷1 (000)                      |

#### 10.4.6 PERIPHERAL PIN SELECT REGISTERS

The PIC24FJ256GB110 family of devices implements a total of 37 registers for remappable peripheral configuration:

- Input Remappable Peripheral Registers (21)

- Output Remappable Peripheral Registers (16)

Note: Input and output register values can only be changed if IOLOCK (OSCCON<6>) = 0. See Section 10.4.4.1 "Control Register Lock" for a specific command sequence.

### REGISTER 10-1: RPINR0: PERIPHERAL PIN SELECT INPUT REGISTER 0

| U-0           | U-0   | R/W-1            | R/W-1  | R/W-1             | R/W-1            | R/W-1           | R/W-1  |

|---------------|-------|------------------|--------|-------------------|------------------|-----------------|--------|

| —             | _     | INT1R5           | INT1R4 | INT1R3            | INT1R2           | INT1R1          | INT1R0 |

| bit 15        |       |                  |        |                   |                  |                 | bit 8  |

|               |       |                  |        |                   |                  |                 |        |

| U-0           | U-0   | U-0              | U-0    | U-0               | U-0              | U-0             | U-0    |

| —             |       | —                |        | —                 | —                |                 | —      |

| bit 7         |       |                  |        |                   |                  |                 | bit 0  |

|               |       |                  |        |                   |                  |                 |        |

| Legend:       |       |                  |        |                   |                  |                 |        |

| R = Readable  | e bit | W = Writable I   | oit    | U = Unimplem      | nented bit, read | l as '0'        |        |

| -n = Value at | POR   | '1' = Bit is set |        | '0' = Bit is clea | ared             | x = Bit is unki | nown   |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 INT1R<5:0>: Assign External Interrupt 1 (INT1) to Corresponding RPn or RPIn Pin bits

bit 7-0 Unimplemented: Read as '0'

#### REGISTER 10-2: RPINR1: PERIPHERAL PIN SELECT INPUT REGISTER 1

| U-0    | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      |     | INT3R5 | INT3R4 | INT3R3 | INT3R2 | INT3R1 | INT3R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

|        |     |        |        |        |        |        |        |

| U-0    | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

| —      | —   | INT2R5 | INT2R4 | INT2R3 | INT2R2 | INT2R1 | INT2R0 |

| bit 7  |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                           |

|-----------|--------------------------------------------------------------------------------------|

| bit 13-8  | INT3R<5:0>: Assign External Interrupt 3 (INT3) to Corresponding RPn or RPIn Pin bits |

| bit 7-6   | Unimplemented: Read as '0'                                                           |

| bit 5-0   | INT2R<5:0>: Assign External Interrupt 2 (INT2) to Corresponding RPn or RPIn Pin bits |

|        |   |                       | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|--------|---|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| —      | _ | RP15R5 <sup>(1)</sup> | RP15R4 <sup>(1)</sup> | RP15R3 <sup>(1)</sup> | RP15R2 <sup>(1)</sup> | RP15R1 <sup>(1)</sup> | RP15R0 <sup>(1)</sup> |

| bit 15 |   |                       |                       |                       |                       |                       | bit 8                 |

| U-0   | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | RP14R5 | RP14R4 | RP14R3 | RP14R2 | RP14R1 | RP14R0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                                    |  |  |  |

|-------------------|------------------|-----------------------|------------------------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | U = Unimplemented bit, read as '0' |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown                 |  |  |  |

| bit 15-14 | Unimplemented: Read as '0'                                                                           |

|-----------|------------------------------------------------------------------------------------------------------|

| bit 13-8  | RP15R<5:0>: RP15 Output Pin Mapping bits <sup>(1)</sup>                                              |

|           | Peripheral output number n is assigned to pin, RP0 (see Table 10-3 for peripheral function numbers)  |

| bit 7-6   | Unimplemented: Read as '0'                                                                           |

| bit 5-0   | RP14R<5:0>: RP14 Output Pin Mapping bits                                                             |

|           | Peripheral output number n is assigned to pin, RP14 (see Table 10-3 for peripheral function numbers) |

Note 1: Unimplemented on 64-pin devices; read as '0'.

#### REGISTER 10-30: RPOR8: PERIPHERAL PIN SELECT OUTPUT REGISTER 8

| 1      |     |        |        |        |        |        |        |

|--------|-----|--------|--------|--------|--------|--------|--------|

| bit 15 |     |        |        |        |        |        | bit 8  |

|        | —   | RP17R5 | RP17R4 | RP17R3 | RP17R2 | RP17R1 | RP17R0 |

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

| U-0   | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | RP16R5 | RP16R4 | RP16R3 | RP16R2 | RP16R1 | RP16R0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 15-14

Unimplemented: Read as '0'

bit 13-8

RP17R<5:0>: RP17 Output Pin Mapping bits Peripheral output number n is assigned to pin, RP17 (see Table 10-3 for peripheral function numbers)

bit 7-6

Unimplemented: Read as '0'

bit 5-0

RP16R<5:0>: RP16 Output Pin Mapping bits Peripheral output number n is assigned to pin, RP16 (see Table 10-3 for peripheral function numbers)

© 2009 Microchip Technology Inc.

## 16.0 INTER-INTEGRATED CIRCUIT (I<sup>2</sup>C™)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "PIC24F Family Reference Manual", Section 24. "Inter-Integrated Circuit (I<sup>2</sup>C™)" (DS39702).

The Inter-Integrated Circuit  $(l^2C)$  module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, display drivers, A/D Converters, etc.

The I<sup>2</sup>C module supports these features:

- Independent master and slave logic

- 7-bit and 10-bit device addresses

- General call address, as defined in the I<sup>2</sup>C protocol

- Clock stretching to provide delays for the processor to respond to a slave data request

- Both 100 kHz and 400 kHz bus specifications.

- Configurable address masking

- Multi-Master modes to prevent loss of messages in arbitration

- Bus Repeater mode, allowing the acceptance of all messages as a slave regardless of the address

- Automatic SCL

- A block diagram of the module is shown in Figure 16-1.

## 16.1 Communicating as a Master in a Single Master Environment

The details of sending a message in Master mode depends on the communications protocol for the device being communicated with. Typically, the sequence of events is as follows:

- 1. Assert a Start condition on SDAx and SCLx.

- Send the I<sup>2</sup>C device address byte to the slave with a write indication.

- 3. Wait for and verify an Acknowledge from the slave.

- 4. Send the first data byte (sometimes known as the command) to the slave.

- 5. Wait for and verify an Acknowledge from the slave.

- 6. Send the serial memory address low byte to the slave.

- 7. Repeat steps 4 and 5 until all data bytes are sent.

- 8. Assert a Repeated Start condition on SDAx and SCLx.

- 9. Send the device address byte to the slave with a read indication.

- 10. Wait for and verify an Acknowledge from the slave.

- 11. Enable master reception to receive serial memory data.

- 12. Generate an ACK or NACK condition at the end of a received byte of data.

- 13. Generate a Stop condition on SDAx and SCLx.

### REGISTER 16-2: I2CxSTAT: I2Cx STATUS REGISTER

| R-0, HSC            | R-0, HSC                                                                                           | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | U-0                                                                                  | U-0                                   | R/C-0, HS        | R-0, HSC                                           | R-0, HSC              |  |  |  |  |  |

|---------------------|----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|---------------------------------------|------------------|----------------------------------------------------|-----------------------|--|--|--|--|--|

| ACKSTAT             | TRSTAT                                                                                             | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | _                                                                                    | _                                     | BCL              | GCSTAT                                             | ADD10                 |  |  |  |  |  |

| bit 15              | 11.01/1                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                      |                                       | DOL              | 0001/11                                            | bit 8                 |  |  |  |  |  |

|                     |                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                      |                                       |                  |                                                    | bit o                 |  |  |  |  |  |

| R/C-0, HS           | R/C-0, HS                                                                                          | R-0, HSC                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R/C-0, HSC                                                                           | R/C-0, HSC                            | R-0, HSC         | R-0, HSC                                           | R-0, HSC              |  |  |  |  |  |

| IWCOL               | I2COV                                                                                              | D/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Р                                                                                    | S                                     | R/W              | RBF                                                | TBF                   |  |  |  |  |  |

| bit 7               | bit 0                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                      |                                       |                  |                                                    |                       |  |  |  |  |  |

|                     |                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                      |                                       |                  |                                                    |                       |  |  |  |  |  |

| Legend:             |                                                                                                    | C = Clearal                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ole bit                                                                              | HS = Hardwar                          | e Settable bit   | HSC = Hardware S                                   | ettable/Clearable bit |  |  |  |  |  |

| R = Reada           | ble bit                                                                                            | W = Writab                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | le bit                                                                               | U = Unimplen                          | nented bit, read | l as '0'                                           |                       |  |  |  |  |  |

| -n = Value          | at POR                                                                                             | '1' = Bit is s                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | set                                                                                  | '0' = Bit is clea                     | ared             | x = Bit is unknown                                 |                       |  |  |  |  |  |

| bit 15<br>bit 14    | 1 = NACK w<br>0 = ACK w<br>Hardware s<br><b>TRSTAT:</b> T<br>(When ope<br>1 = Master<br>0 = Master | was detected<br>as detected<br>set or clear a<br>ransmit Stat<br>rating as I <sup>2</sup> (<br>transmit is i<br>transmit is i                                                                                                                                                                                                                                                                                                                                                         | last<br>at end of Ackr<br>us bit<br>C master. App<br>n progress (8<br>not in progres | blicable to mass<br>bits + ACK)<br>ss | ter transmit ope |                                                    |                       |  |  |  |  |  |

|                     |                                                                                                    | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -                                                                                    | r transmission.                       | Hardware clea    | ar at end of slave Ac                              | knowledge.            |  |  |  |  |  |

| bit 13-11<br>bit 10 | -                                                                                                  | ented: Rea                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | a as <sup>r</sup> 0 <sup>r</sup><br>sion Detect bi                                   | :4                                    |                  |                                                    |                       |  |  |  |  |  |

|                     | 1 = A bus o<br>0 = No coll<br>Hardware s                                                           | collision has<br>ision<br>set at detect                                                                                                                                                                                                                                                                                                                                                                                                                                               | been detecte                                                                         | ed during a ma                        | ster operation   |                                                    |                       |  |  |  |  |  |

| bit 9               | 1 = Genera<br>0 = Genera                                                                           | al call addres                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ss was receiv<br>ss was not re                                                       | ceived                                | address. Hardv   | vare clear at Stop de                              | etection.             |  |  |  |  |  |

| bit 8               | 1 = 10-bit a<br>0 = 10-bit a                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | matched<br>not matched                                                               |                                       | bit address. Ha  | irdware clear at Stop                              | o detection.          |  |  |  |  |  |

| bit 7               | 1 = An atte<br>0 = No coll                                                                         | ision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | the I2CxTRN                                                                          |                                       |                  | <sup>2</sup> C module is busy<br>red by software). |                       |  |  |  |  |  |

| bit 6               | <b>12COV:</b> Re<br>1 = A byte<br>0 = No ove                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                      |                                       |                  |                                                    |                       |  |  |  |  |  |

| bit 5               | D/A: Data/<br>1 = Indicate<br>0 = Indicate                                                         | <ul> <li>a) = No overflow</li> <li>b) = No overflow</li> <li>b) Hardware set at attempt to transfer I2CxRSR to I2CxRCV (cleared by software).</li> <li>b) A Diversion of the last byte received was data</li> <li>b) = Indicates that the last byte received was device address</li> <li>b) = Indicates that the last byte received was device address</li> <li>c) Hardware clear at device address match. Hardware set by after transmission finishes, or by reception of</li> </ul> |                                                                                      |                                       |                  |                                                    |                       |  |  |  |  |  |

## 17.1 UART Baud Rate Generator (BRG)

The UART module includes a dedicated 16-bit Baud Rate Generator. The UxBRG register controls the period of a free-running, 16-bit timer. Equation 17-1 shows the formula for computation of the baud rate with BRGH = 0.

## EQUATION 17-1: UART BAUD RATE WITH BRGH = $0^{(1,2)}$

Baud Rate =  $\frac{FCY}{16 \cdot (UxBRG + 1)}$ UxBRG =  $\frac{FCY}{16 \cdot Baud Rate} - 1$

**Note 1:** FCY denotes the instruction cycle clock

- frequency (Fosc/2).

- **2:** Based on FCY = FOSC/2, Doze mode and PLL are disabled.

Example 17-1 shows the calculation of the baud rate error for the following conditions:

- Fcy = 4 MHz

- Desired Baud Rate = 9600

The maximum baud rate (BRGH = 0) possible is FCY/16 (for UxBRG = 0) and the minimum baud rate possible is FCY/(16 \* 65536).

Equation 17-2 shows the formula for computation of the baud rate with BRGH = 1.

#### EQUATION 17-2: UART BAUD RATE WITH BRGH = $1^{(1,2)}$

|      |    | Baud Rate = $\frac{FCY}{4 \cdot (UxBRG + 1)}$         |

|------|----|-------------------------------------------------------|

|      |    | $UxBRG = \frac{FCY}{4 \cdot Baud Rate} - 1$           |

| Note | 1: | Fcy denotes the instruction cycle clock<br>frequency. |

|      | э. | Deced on Fox - Foco/2 Deza made                       |

2: Based on FCY = FOSC/2, Doze mode and PLL are disabled.

The maximum baud rate (BRGH = 1) possible is FcY/4 (for UxBRG = 0) and the minimum baud rate possible is FcY/(4 \* 65536).

Writing a new value to the UxBRG register causes the BRG timer to be reset (cleared). This ensures the BRG does not wait for a timer overflow before generating the new baud rate.

## EXAMPLE 17-1: BAUD RATE ERROR CALCULATION (BRGH = 0)<sup>(1)</sup>

Desired Baud Rate = FCY/(16 (UxBRG + 1))Solving for UxBRG value: UxBRG = ((FCY/Desired Baud Rate)/16) - 1UxBRG = ((400000/9600)/16) - 1UxBRG = 2.5 Calculated Baud Rate= 4000000/(16 (25 + 1)) 9615 = Error (Calculated Baud Rate - Desired Baud Rate) = Desired Baud Rate = (9615 - 9600)/9600= 0.16%**Note 1:** Based on FCY = FOSC/2, Doze mode and PLL are disabled.

## 18.3.1 CLEARING USB OTG INTERRUPTS

Unlike device level interrupts, the USB OTG interrupt status flags are not freely writable in software. All USB OTG flag bits are implemented as hardware set only bits. Additionally, these bits can only be cleared in

software by writing a '1' to their locations (i.e., performing a MOV type instruction). Writing a '0' to a flag bit (i.e., a BCLR instruction) has no effect.

Note: Throughout this data sheet, a bit that can only be cleared by writing a '1' to its location is referred to as "Write '1' to clear". In register descriptions, this function is indicated by the descriptor "K".

## 18.4 Device Mode Operation

The following section describes how to perform a common Device mode task. In Device mode, USB transfers are performed at the transfer level. The USB module automatically performs the status phase of the transfer.

18.4.1 ENABLING DEVICE MODE

- Reset the Ping-Pong Buffer Pointers by setting, then clearing, the Ping-Pong Buffer Reset bit PPBRST (U1CON<1>).

- 2. Disable all interrupts (U1IE and U1EIE = 00h).

- 3. Clear any existing interrupt flags by writing FFh to U1IR and U1EIR.

- 4. Verify that VBUS is present (non OTG devices only).

- 5. Enable the USB module by setting the USBEN bit (U1CON<0>).

- Set the OTGEN bit (U1OTGCON<2>) to enable OTG operation.

- Enable the endpoint zero buffer to receive the first setup packet by setting the EPRXEN and EPHSHK bits for Endpoint 0 (U1EP0<3,0> = 1).

- 8. Power up the USB module by setting the USBPWR bit (U1PWRC<0>).

- 9. Enable the D+ pull-up resistor to signal an attach by setting DPPULUP (U10TGCON<7>).

## REGISTER 18-15: U1OTGIE: USB OTG INTERRUPT ENABLE REGISTER (HOST MODE ONLY)

| U-0          | U-0                                                                                                       | U-0                 | U-0             | U-0               | U-0              | U-0            | U-0      |  |  |

|--------------|-----------------------------------------------------------------------------------------------------------|---------------------|-----------------|-------------------|------------------|----------------|----------|--|--|

| _            |                                                                                                           |                     |                 |                   |                  |                |          |  |  |

| pit 15       |                                                                                                           |                     |                 |                   |                  |                | bit 8    |  |  |

| R/W-0        | R/W-0                                                                                                     | R/W-0               | R/W-0           | R/W-0             | R/W-0            | U-0            | R/W-0    |  |  |

| IDIE         | T1MSECIE                                                                                                  | LSTATEIE            | ACTVIE          | SESVDIE           | SESENDIE         | _              | VBUSVDIE |  |  |

| pit 7        |                                                                                                           |                     |                 |                   | 0_0_0_0          |                | bit      |  |  |

| Legend:      |                                                                                                           |                     |                 |                   |                  |                |          |  |  |

| R = Readable | e bit                                                                                                     | W = Writable b      | bit             | U = Unimplen      | nented bit, read | as '0'         |          |  |  |

| n = Value at | POR                                                                                                       | '1' = Bit is set    |                 | '0' = Bit is clea | ared             | x = Bit is unl | known    |  |  |

| bit 7        | IDIE: ID Interrupt Enable bit<br>1 = Interrupt enabled<br>0 = Interrupt disabled                          |                     |                 |                   |                  |                |          |  |  |

| oit 6        | 1 = Interrupt<br>0 = Interrupt                                                                            | enabled             | mor Interrunt [ | -nabla bit        |                  |                |          |  |  |

|              | 1 = Interrupt<br>0 = Interrupt                                                                            | enabled<br>disabled |                 |                   |                  |                |          |  |  |

| bit 5        | LSTATEIE: Li<br>1 = Interrupt<br>0 = Interrupt                                                            |                     | Interrupt Ena   | ble bit           |                  |                |          |  |  |

| bit 4        |                                                                                                           | Activity Interru    | ot Enable bit   |                   |                  |                |          |  |  |

| bit 3        | SESVDIE: Session Valid Interrupt Enable bit<br>1 = Interrupt enabled<br>0 = Interrupt disabled            |                     |                 |                   |                  |                |          |  |  |

| bit 2        | SESENDIE: E<br>1 = Interrupt<br>0 = Interrupt                                                             |                     | on End Interru  | pt Enable bit     |                  |                |          |  |  |

| bit 1        | -                                                                                                         |                     | ,               |                   |                  |                |          |  |  |

| bit 0        | Unimplemented: Read as '0'<br>VBUSVDIE: A-Device VBUS Valid Interrupt Enable bit<br>1 = Interrupt enabled |                     |                 |                   |                  |                |          |  |  |

0 = Interrupt disabled

## REGISTER 18-18: U1IE: USB INTERRUPT ENABLE REGISTER (ALL USB MODES)

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0   | R/W-0                   | R/W-0    | R/W-0  | R/W-0 | R/W-0 | R/W-0  | R/W-0    |

|---------|-------------------------|----------|--------|-------|-------|--------|----------|

| STALLIE | ATTACHIE <sup>(1)</sup> | RESUMEIE | IDLEIE | TRNIE | SOFIE | UERRIE | URSTIE   |

|         |                         |          |        |       |       |        | DETACHIE |

| bit 7   |                         |          |        |       |       |        | bit 0    |

| Legend:                                         |                            |                               |                                    |                                |  |  |  |

|-------------------------------------------------|----------------------------|-------------------------------|------------------------------------|--------------------------------|--|--|--|

| R = Readab                                      | le bit                     | W = Writable bit              | U = Unimplemented bit, read as '0' |                                |  |  |  |

| -n = Value a                                    | t POR                      | '1' = Bit is set              | '0' = Bit is cleared               | x = Bit is unknown             |  |  |  |

|                                                 |                            |                               |                                    |                                |  |  |  |

| bit 15-8                                        | -                          | mented: Read as '0'           |                                    |                                |  |  |  |

| bit 7                                           |                            | : STALL Handshake Interrup    | t Enable bit                       |                                |  |  |  |

|                                                 |                            | rupt enabled                  |                                    |                                |  |  |  |

| L:1 0                                           |                            | rupt disabled                 | + h :+ (1   + + + - )(1)           |                                |  |  |  |

| bit 6                                           |                            | E: Peripheral Attach Interrup | of bit (Host mode only)            |                                |  |  |  |

| 1 = Interrupt enabled<br>0 = Interrupt disabled |                            |                               |                                    |                                |  |  |  |

| bit 5                                           |                            | IE: Resume Interrupt bit      |                                    |                                |  |  |  |

|                                                 |                            | rupt enabled                  |                                    |                                |  |  |  |

|                                                 |                            | rupt disabled                 |                                    |                                |  |  |  |

| bit 4                                           | IDLEIE: I                  | dle Detect Interrupt bit      |                                    |                                |  |  |  |

|                                                 |                            | rupt enabled                  |                                    |                                |  |  |  |

|                                                 | 0 = Inter                  | rupt disabled                 |                                    |                                |  |  |  |

| bit 3                                           | TRNIE: T                   | oken Processing Complete I    | nterrupt bit                       |                                |  |  |  |

|                                                 |                            | rupt enabled                  |                                    |                                |  |  |  |

|                                                 |                            | rupt disabled                 | ( ) · · ·                          |                                |  |  |  |

| bit 2                                           |                            | tart-of-Frame Token Interrup  | t bit                              |                                |  |  |  |

|                                                 |                            | rupt enabled<br>rupt disabled |                                    |                                |  |  |  |

| bit 1                                           |                            | USB Error Condition Interru   | nt hit                             |                                |  |  |  |

|                                                 |                            | rupt enabled                  |                                    |                                |  |  |  |

|                                                 |                            | rupt disabled                 |                                    |                                |  |  |  |

| bit 0                                           | <b>URSTIE</b><br>Enable bi |                               | Interrupt (Device mode) or U       | SB Detach Interrupt (Host mode |  |  |  |

|                                                 |                            | rupt enabled                  |                                    |                                |  |  |  |

|                                                 | 0 = Inter                  | rupt disabled                 |                                    |                                |  |  |  |

| Note 1: U                                       | Inimplement                | ed in Device mode, read as '  | 'n.'                               |                                |  |  |  |