Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB OTG                                    |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 83                                                                            |

| Program Memory Size        | 64KB (22K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 16K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                     |

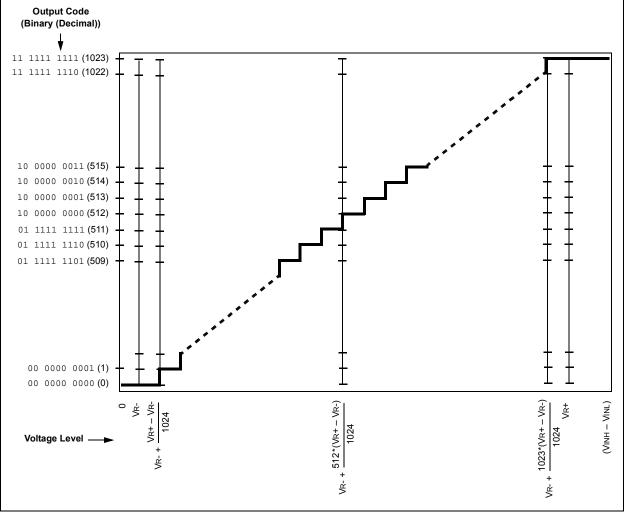

| Data Converters            | A/D 16x10b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

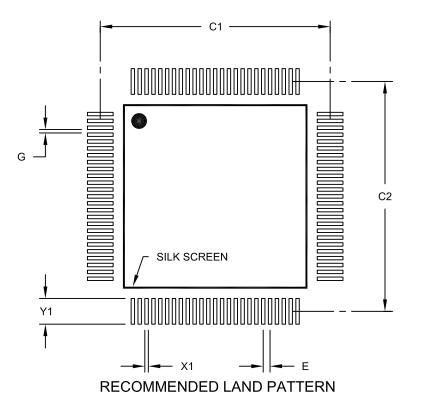

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 100-TQFP                                                                      |

| Supplier Device Package    | 100-TQFP (14x14)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj64gb110-i-pf |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.4 Voltage Regulator Pins (ENVREG/DISVREG and VCAP/VDDCORE)

| Note: | This secti | on applies   | only | to | PIC24FJ |

|-------|------------|--------------|------|----|---------|

|       |            | th an on-chi |      |    |         |

The on-chip voltage regulator enable/disable pin (ENVREG or DISVREG, depending on the device family) must always be connected directly to either a supply voltage or to ground. The particular connection is determined by whether or not the regulator is to be used:

- For ENVREG, tie to VDD to enable the regulator, or to ground to disable the regulator

- For DISVREG, tie to ground to enable the regulator or to VDD to disable the regulator

Refer to **Section 26.2** "**On-Chip Voltage Regulator**" for details on connecting and using the on-chip regulator.

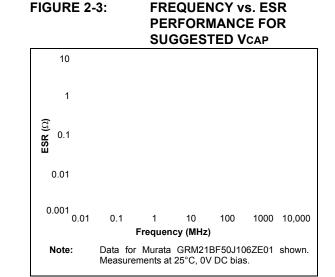

When the regulator is enabled, a low-ESR (<5 $\Omega$ ) capacitor is required on the VCAP/VDDCORE pin to stabilize the voltage regulator output voltage. The VCAP/VDDCORE pin must not be connected to VDD, and must use a capacitor of 10  $\mu$ F connected to ground. The type can be ceramic or tantalum. A suitable example is the Murata GRM21BF50J106ZE01 (10  $\mu$ F, 6.3V) or equivalent. Designers may use Figure 2-3 to evaluate ESR equivalence of candidate devices.

The placement of this capacitor should be close to VCAP/VDDCORE. It is recommended that the trace length not exceed 0.25 inch (6 mm). Refer to **Section 29.0 "Electrical Characteristics"** for additional information.

When the regulator is disabled, the VCAP/VDDCORE pin must be tied to a voltage supply at the VDDCORE level. Refer to **Section 29.0 "Electrical Characteristics"** for information on VDD and VDDCORE.

## 2.5 ICSP Pins

The PGECx and PGEDx pins are used for In-Circuit Serial Programming (ICSP) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of ohms, not to exceed  $100\Omega$ .

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

For device emulation, ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to the Microchip debugger/emulator tool.

For more information on available Microchip development tools connection requirements, refer to **Section 27.0 "Development Support"**.

| REGISTER 3-2. CORCON. OF CONTROL REGISTER | REGISTER 3-2: | CORCON: CPU CONTROL REGISTER |

|-------------------------------------------|---------------|------------------------------|

|-------------------------------------------|---------------|------------------------------|

| U-0     | U-0 | U-0           | U-0 | U-0                 | U-0   | U-0 | U-0   |

|---------|-----|---------------|-----|---------------------|-------|-----|-------|

| _       | —   | _             | _   | —                   | —     | —   |       |

| bit 15  | -   |               |     |                     | •     | •   | bit 8 |

|         |     |               |     |                     |       |     |       |

| U-0     | U-0 | U-0           | U-0 | R/C-0               | R/W-0 | U-0 | U-0   |

| _       | —   | _             | _   | IPL3 <sup>(1)</sup> | PSV   | —   |       |

| bit 7   | -   |               |     |                     | •     | •   | bit 0 |

|         |     |               |     |                     |       |     |       |

| Legend: |     | C = Clearable | hit |                     |       |     |       |

| Legend:           | C = Clearable bit |                             |                    |

|-------------------|-------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-4 | Unimplemented: Read as '0'                                                                                                    |

|----------|-------------------------------------------------------------------------------------------------------------------------------|

| bit 3    | IPL3: CPU Interrupt Priority Level Status bit <sup>(1)</sup>                                                                  |

|          | <ul> <li>1 = CPU interrupt priority level is greater than 7</li> <li>0 = CPU interrupt priority level is 7 or less</li> </ul> |

| bit 2    | <b>PSV:</b> Program Space Visibility in Data Space Enable bit                                                                 |

|          | 1 = Program space visible in data space                                                                                       |

|          | 0 = Program space not visible in data space                                                                                   |

| bit 1-0  | Unimplemented: Read as '0'                                                                                                    |

**Note 1:** User interrupts are disabled when IPL3 = 1.

## 3.3 Arithmetic Logic Unit (ALU)

The PIC24F ALU is 16 bits wide and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are 2's complement in nature. Depending on the operation, the ALU may affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the SR register. The C and DC Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array, or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

The PIC24F CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware for 16-bit divisor division.

## 3.3.1 MULTIPLIER

The ALU contains a high-speed, 17-bit x 17-bit multiplier. It supports unsigned, signed or mixed sign operation in several multiplication modes:

- 1. 16-bit x 16-bit signed

- 2. 16-bit x 16-bit unsigned

- 3. 16-bit signed x 5-bit (literal) unsigned

- 4. 16-bit unsigned x 16-bit unsigned

- 5. 16-bit unsigned x 5-bit (literal) unsigned

- 6. 16-bit unsigned x 16-bit signed

- 7. 8-bit unsigned x 8-bit unsigned

## TABLE 4-22: USB OTG REGISTER MAP (CONTINUED)

| File Name | Addr | Bit 15 | Bit 14 | Bit 13    | Bit 12    | Bit 11    | Bit 10   | Bit 9  | Bit 8 | Bit 7               | Bit 6                   | Bit 5  | Bit 4          | Bit 3        | Bit 2   | Bit 1   | Bit 0  | All<br>Resets |

|-----------|------|--------|--------|-----------|-----------|-----------|----------|--------|-------|---------------------|-------------------------|--------|----------------|--------------|---------|---------|--------|---------------|

| U1EP0     | 04AA | —      | —      | _         | —         | —         | _        | -      | _     | LSPD <sup>(1)</sup> | RETRYDIS <sup>(1)</sup> | _      | EPCONDIS       | EPRXEN       | EPTXEN  | EPSTALL | EPHSHK | 0000          |

| U1EP1     | 04AC | —      |        | _         | _         | _         | _        | _      | _     | _                   | _                       | _      | EPCONDIS       | EPRXEN       | EPTXEN  | EPSTALL | EPHSHK | 0000          |

| U1EP2     | 04AE | _      |        | _         | _         | _         | _        | _      | _     | _                   | —                       | _      | EPCONDIS       | EPRXEN       | EPTXEN  | EPSTALL | EPHSHK | 0000          |

| U1EP3     | 04B0 | _      | _      | _         | -         | _         |          | _      | _     |                     | _                       |        | EPCONDIS       | EPRXEN       | EPTXEN  | EPSTALL | EPHSHK | 0000          |

| U1EP4     | 04B2 | —      |        | _         | _         | _         | _        | _      | _     | _                   | _                       | _      | EPCONDIS       | EPRXEN       | EPTXEN  | EPSTALL | EPHSHK | 0000          |

| U1EP5     | 04B4 | _      | _      | _         | _         | _         | _        | _      | _     | _                   | _                       | _      | EPCONDIS       | EPRXEN       | EPTXEN  | EPSTALL | EPHSHK | 0000          |

| U1EP6     | 04B6 | _      | _      | _         | _         | _         | _        | _      | _     | _                   | _                       | _      | EPCONDIS       | EPRXEN       | EPTXEN  | EPSTALL | EPHSHK | 0000          |

| U1EP7     | 04B8 | _      |        | _         | _         | _         | _        | _      | _     | _                   | —                       | _      | EPCONDIS       | EPRXEN       | EPTXEN  | EPSTALL | EPHSHK | 0000          |

| U1EP8     | 04BA | _      | _      | _         | _         | _         |          | _      |       | _                   | _                       | _      | EPCONDIS       | EPRXEN       | EPTXEN  | EPSTALL | EPHSHK | 0000          |

| U1EP9     | 04BC | _      | _      | _         | _         | _         |          | _      |       | _                   | _                       | _      | EPCONDIS       | EPRXEN       | EPTXEN  | EPSTALL | EPHSHK | 0000          |

| U1EP10    | 04BE | _      | _      | _         | _         | _         |          | _      |       | _                   | _                       | _      | EPCONDIS       | EPRXEN       | EPTXEN  | EPSTALL | EPHSHK | 0000          |

| U1EP11    | 04C0 | _      | _      | _         | _         | _         | _        | _      |       | _                   | _                       | -      | EPCONDIS       | EPRXEN       | EPTXEN  | EPSTALL | EPHSHK | 0000          |

| U1EP12    | 04C2 | _      | _      | _         | _         | _         | _        | _      |       | _                   | _                       | -      | EPCONDIS       | EPRXEN       | EPTXEN  | EPSTALL | EPHSHK | 0000          |

| U1EP13    | 04C4 | _      | _      | _         | _         | _         |          | _      |       | _                   | _                       | _      | EPCONDIS       | EPRXEN       | EPTXEN  | EPSTALL | EPHSHK | 0000          |

| U1EP14    | 04C6 | _      | _      | _         | _         | _         |          | _      |       | _                   | _                       | -      | EPCONDIS       | EPRXEN       | EPTXEN  | EPSTALL | EPHSHK | 0000          |

| U1EP15    | 04C8 | _      | _      | _         | _         | _         |          | _      |       | _                   | _                       | -      | EPCONDIS       | EPRXEN       | EPTXEN  | EPSTALL | EPHSHK | 0000          |

| U1PWMRRS  | 04CC |        | US     | B Power S | Supply PV | /M Duty C | ycle Reg | ister  |       |                     |                         | USB Po | ower Supply P\ | WM Period Re | egister |         |        | 0000          |

| U1PWMCON  | 04CE | PWMEN  | _      | _         | _         | _         |          | PWMPOL | CNTEN | _                   | _                       | _      | _              | —            | —       | _       |        | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

**Note** 1: Alternate register or bit definitions when the module is operating in Host mode.

2: This register is available in Host mode only.

#### TABLE 4-23: PARALLEL MASTER/SLAVE PORT REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14                                                                                                | Bit 13 | Bit 12  | Bit 11  | Bit 10 | Bit 9          | Bit 8        | Bit 7          | Bit 6        | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|--------|-------------------------------------------------------------------------------------------------------|--------|---------|---------|--------|----------------|--------------|----------------|--------------|--------|--------|--------|--------|--------|--------|---------------|

| PMCON     | 0600 | PMPEN  |                                                                                                       | PSIDL  | ADRMUX1 | ADRMUX0 | PTBEEN | PTWREN         | PTRDEN       | CSF1           | CSF0         | ALP    | CS2P   | CS1P   | BEP    | WRSP   | RDSP   | 0000          |

| PMMODE    | 0602 | BUSY   | IRQM1                                                                                                 | IRQM0  | INCM1   | INCM0   | MODE16 | MODE1          | MODE0        | WAITB1         | WAITB0       | WAITM3 | WAITM2 | WAITM1 | WAITM0 | WAITE1 | WAITE0 | 0000          |

| PMADDR    | 0604 | CS2    | CS1                                                                                                   | ADDR13 | ADDR12  | ADDR11  | ADDR10 | ADDR9          | ADDR8        | ADDR7          | ADDR6        | ADDR5  | ADDR4  | ADDR3  | ADDR2  | ADDR1  | ADDR0  | 0000          |

| PMDOUT1   |      |        | Parallel Port Data Out Register 1 (Buffers 0 and 1) 000                                               |        |         |         |        |                |              |                |              | 0000   |        |        |        |        |        |               |

| PMDOUT2   | 0606 |        |                                                                                                       |        |         |         | Pa     | rallel Port D  | ata Out Reg  | gister 2 (Buff | fers 2 and 3 | )      |        |        |        |        |        | 0000          |

| PMDIN1    | 0608 |        |                                                                                                       |        |         |         | Pa     | arallel Port [ | Data In Regi | ster 1 (Buffe  | ers 0 and 1) |        |        |        |        |        |        | 0000          |

| PMDIN2    | 060A |        |                                                                                                       |        |         |         | Pa     | arallel Port [ | Data In Regi | ster 2 (Buffe  | ers 2 and 3) |        |        |        |        |        |        | 0000          |

| PMAEN     | 060C | PTEN15 | 5 PTEN14 PTEN13 PTEN12 PTEN11 PTEN10 PTEN9 PTEN8 PTEN7 PTEN6 PTEN5 PTEN4 PTEN3 PTEN2 PTEN1 PTEN0 0000 |        |         |         |        |                |              |                |              |        | 0000   |        |        |        |        |               |

| PMSTAT    | 060E | IBF    | IBOV                                                                                                  | _      |         | IB3F    | IB2F   | IB1F           | IB0F         | OBE            | OBUF         | _      | _      | OB3E   | OB2E   | OB1E   | OB0E   | 0000          |

|           |      |        |                                                                                                       |        |         |         |        |                |              |                |              |        |        |        |        |        |        |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-27: PERIPHERAL PIN SELECT REGISTER MAP

| IADLE        | 4-27. |        |        |                       | ELECT                 |                       |                       |                       |                       |       |       |        |        |        |        |        |        |               |

|--------------|-------|--------|--------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-------|-------|--------|--------|--------|--------|--------|--------|---------------|

| File<br>Name | Addr  | Bit 15 | Bit 14 | Bit 13                | Bit 12                | Bit 11                | Bit 10                | Bit 9                 | Bit 8                 | Bit 7 | Bit 6 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

| RPINR0       | 0680  | —      | —      | INT1R5                | INT1R4                | INT1R3                | INT1R2                | INT1R1                | INT1R0                | _     | _     | _      | -      | _      | —      | -      | —      | 3F00          |

| RPINR1       | 0682  | _      | _      | INT3R5                | INT3R4                | INT3R3                | INT3R2                | INT3R1                | INT3R0                | _     | _     | INT2R5 | INT2R4 | INT2R3 | INT2R2 | INT2R1 | INT2R0 | 3F3F          |

| RPINR2       | 0684  | —      | _      | —                     | _                     | _                     | _                     | _                     | —                     | —     | _     | INT4R5 | INT4R4 | INT4R3 | INT4R2 | INT4R1 | INT4R0 | 003F          |

| RPINR3       | 0686  | _      | —      | T3CKR5                | T3CKR4                | T3CKR3                | T3CKR2                | T3CKR1                | T3CKR0                | _     |       | T2CKR5 | T2CKR4 | T2CKR3 | T2CKR2 | T2CKR1 | T2CKR0 | 3F3F          |

| RPINR4       | 0688  | _      | _      | T5CKR5                | T5CKR4                | T5CKR3                | T5CKR2                | T5CKR1                | T5CKR0                | _     | _     | T4CKR5 | T4CKR4 | T4CKR3 | T4CKR2 | T4CKR1 | T4CKR0 | 3F3F          |

| RPINR7       | 068E  | _      | _      | IC2R5                 | IC2R4                 | IC2R3                 | IC2R2                 | IC2R1                 | IC2R0                 | _     | _     | IC1R5  | IC1R4  | IC1R3  | IC1R2  | IC1R1  | IC1R0  | 3F3F          |

| RPINR8       | 0690  | _      | —      | IC4R5                 | IC4R4                 | IC4R3                 | IC4R2                 | IC4R1                 | IC4R0                 | _     |       | IC3R5  | IC3R4  | IC3R3  | IC3R2  | IC3R1  | IC3R0  | 3F3F          |

| RPINR9       | 0692  |        | —      | IC6R5                 | IC6R4                 | IC6R3                 | IC6R2                 | IC6R1                 | IC6R0                 | _     |       | IC5R5  | IC5R4  | IC5R3  | IC5R2  | IC5R1  | IC5R0  | 3F3F          |

| RPINR10      | 0694  | _      | —      | IC8R5                 | IC8R4                 | IC8R3                 | IC8R2                 | IC8R1                 | IC8R0                 | _     |       | IC7R5  | IC7R4  | IC7R3  | IC7R2  | IC7R1  | IC7R0  | 3F3F          |

| RPINR11      | 0696  |        | —      | OCFBR5                | OCFBR4                | OCFBR3                | OCFBR2                | OCFBR1                | OCFBR0                | _     |       | OCFAR5 | OCFAR4 | OCFAR3 | OCFAR2 | OCFAR1 | OCFAR0 | 3F3F          |

| RPINR15      | 069E  |        | —      | IC9R5                 | IC9R4                 | IC9R3                 | IC9R2                 | IC9R1                 | IC9R0                 | _     |       | _      |        |        | —      |        | —      | 3F00          |

| RPINR17      | 06A2  |        | —      | U3RXR5                | U3RXR4                | U3RXR3                | U3RXR2                | U3RXR1                | U3RXR0                | _     |       | _      |        |        | _      |        | _      | 3F00          |

| RPINR18      | 06A4  |        | —      | U1CTSR5               | U1CTSR4               | U1CTSR3               | U1CTSR2               | U1CTSR1               | U1CTSR0               | _     |       | U1RXR5 | U1RXR4 | U1RXR3 | U1RXR2 | U1RXR1 | U1RXR0 | 3F3F          |

| RPINR19      | 06A6  | —      | —      | U2CTSR5               | U2CTSR4               | U2CTSR3               | U2CTSR2               | U2CTSR1               | U2CTSR0               | _     | _     | U2RXR5 | U2RXR4 | U2RXR3 | U2RXR2 | U2RXR1 | U2RXR0 | 3F3F          |

| RPINR20      | 06A8  |        | —      | SCK1R5                | SCK1R4                | SCK1R3                | SCK1R2                | SCK1R1                | SCK1R0                | _     |       | SDI1R5 | SDI1R4 | SDI1R3 | SDI1R2 | SDI1R1 | SDI1R0 | 3F3F          |

| RPINR21      | 06AA  |        | —      | U3CTSR5               | U3CTSR4               | U3CTSR3               | U3CTSR2               | U3CTSR1               | U3CTSR0               | _     |       | SS1R5  | SS1R4  | SS1R3  | SS1R2  | SS1R1  | SS1R0  | 3F3F          |

| RPINR22      | 06AC  | _      | —      | SCK2R5                | SCK2R4                | SCK2R3                | SCK2R2                | SCK2R1                | SCK2R0                |       |       | SDI2R5 | SDI2R4 | SDI2R3 | SDI2R2 | SDI2R1 | SDI2R0 | 3F3F          |

| RPINR23      | 06AE  | _      | —      | —                     | —                     | _                     | —                     | —                     | —                     | —     |       | SS2R5  | SS2R4  | SS2R3  | SS2R2  | SS2R1  | SS2R0  | 003F          |

| RPINR27      | 06B6  |        | —      | U4CTSR5               | U4CTSR4               | U4CTSR3               | U4CTSR2               | U4CTSR1               | U4CTSR0               | _     |       | U4RXR5 | U4RXR4 | U4RXR3 | U4RXR2 | U4RXR1 | U4RXR0 | 3F3F          |

| RPINR28      | 06B8  |        | —      | SCK3R5                | SCK3R4                | SCK3R3                | SCK3R2                | SCK3R1                | SCK3R0                | _     |       | SDI3R5 | SDI3R4 | SDI3R3 | SDI3R2 | SDI3R1 | SDI3R0 | 3F3F          |

| RPINR29      | 06BA  | _      | —      | —                     | —                     | _                     | —                     | —                     | —                     | —     |       | SS3R5  | SS3R4  | SS3R3  | SS3R2  | SS3R1  | SS3R0  | 003F          |

| RPOR0        | 06C0  |        | —      | RP1R5                 | RP1R4                 | RP1R3                 | RP1R2                 | RP1R1                 | RP1R0                 | _     |       | RP0R5  | RP0R4  | RP0R3  | RP0R2  | RP0R1  | RP0R0  | 0000          |

| RPOR1        | 06C2  |        | —      | RP3R5                 | RP3R4                 | RP3R3                 | RP3R2                 | RP3R1                 | RP3R0                 | _     |       | RP2R5  | RP2R4  | RP2R3  | RP2R2  | RP2R1  | RP2R0  | 0000          |

| RPOR2        | 06C4  |        | —      | RP5R5 <sup>(1)</sup>  | RP5R4 <sup>(1)</sup>  | RP5R3 <sup>(1)</sup>  | RP5R2 <sup>(1)</sup>  | RP5R1 <sup>(1)</sup>  | RP5R0 <sup>(1)</sup>  | _     |       | RP4R5  | RP4R4  | RP4R3  | RP4R2  | RP4R1  | RP4R0  | 0000          |

| RPOR3        | 06C6  |        | —      | RP7R5                 | RP7R4                 | RP7R3                 | RP7R2                 | RP7R1                 | RP7R0                 | _     |       | RP6R5  | RP6R4  | RP6R3  | RP6R2  | RP6R1  | RP6R0  | 0000          |

| RPOR4        | 06C8  | —      | —      | RP9R5                 | RP9R4                 | RP9R3                 | RP9R2                 | RP9R1                 | RP9R0                 | _     | _     | RP8R5  | RP8R4  | RP8R3  | RP8R2  | RP8R1  | RP8R0  | 0000          |

| RPOR5        | 06CA  |        | —      | RP11R5                | RP11R4                | RP11R3                | RP11R2                | RP11R1                | RP11R0                | _     |       | RP10R5 | RP10R4 | RP10R3 | RP10R2 | RP10R1 | RP10R0 | 0000          |

| RPOR6        | 06CC  |        | —      | RP13R5                | RP13R4                | RP13R3                | RP13R2                | RP13R1                | RP13R0                | _     |       | RP12R5 | RP12R4 | RP12R3 | RP12R2 | RP12R1 | RP12R0 | 0000          |

| RPOR7        | 06CE  | _      | —      | RP15R5 <sup>(1)</sup> | RP15R4 <sup>(1)</sup> | RP15R3 <sup>(1)</sup> | RP15R2 <sup>(1)</sup> | RP15R1 <sup>(1)</sup> | RP15R0 <sup>(1)</sup> |       |       | RP14R5 | RP14R4 | RP14R3 | RP14R2 | RP14R1 | RP14R0 | 0000          |

| RPOR8        | 06D0  | _      | _      | RP17R5                | RP17R4                | RP17R3                | RP17R2                | RP17R1                | RP17R0                | _     | _     | RP16R5 | RP16R4 | RP16R3 | RP16R2 | RP16R1 | RP16R0 | 0000          |

| RPOR9        | 06D2  | _      | _      | RP19R5                | RP19R4                | RP19R3                | RP19R2                | RP19R1                | RP19R0                | _     | _     | RP18R5 | RP18R4 | RP18R3 | RP18R2 | RP18R1 | RP18R0 | 0000          |

| RPOR10       | 06D4  | _      | _      | RP21R5                | RP21R4                | RP21R3                | RP21R2                | RP21R1                | RP21R0                | _     | _     | RP20R5 | RP20R4 | RP20R3 | RP20R2 | RP20R1 | RP20R0 | 0000          |

| RPOR11       | 06D6  | —      | _      | RP23R5                | RP23R4                | RP23R3                | RP23R2                | RP23R1                | RP23R0                | —     |       | RP22R5 | RP22R4 | RP22R3 | RP22R2 | RP22R1 | RP22R0 | 0000          |

| RPOR12       | 06D8  | —      | _      | RP25R5                | RP25R4                | RP25R3                | RP25R2                | RP25R1                | RP25R0                | —     |       | RP24R5 | RP24R4 | RP24R3 | RP24R2 | RP24R1 | RP24R0 | 0000          |

| RPOR13       | 06DA  | —      | _      | RP27R5                | RP27R4                | RP27R3                | RP27R2                | RP27R1                | RP27R0                | —     | _     | RP26R5 | RP26R4 | RP26R3 | RP26R2 | RP26R1 | RP26R0 | 0000          |

| RPOR14       | 06DC  | —      | _      | RP29R5                | RP29R4                | RP29R3                | RP29R2                | RP29R1                | RP29R0                | —     | _     | RP28R5 | RP28R4 | RP28R3 | RP28R2 | RP28R1 | RP28R0 | 0000          |

| RPOR15       | 06DE  | —      | _      | RP31R5 <sup>(2)</sup> | RP31R4 <sup>(2)</sup> | RP31R3 <sup>(2)</sup> | RP31R2 <sup>(2)</sup> | RP31R1 <sup>(2)</sup> | RP31R0 <sup>(2)</sup> | _     | _     | RP30R5 | RP30R4 | RP30R3 | RP30R2 | RP30R1 | RP30R0 | 0000          |

| r            |       |        |        |                       |                       |                       |                       |                       |                       |       |       |        |        |        |        |        |        |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Bits are unimplemented on 64-pin devices; read as '0'.

2: Bits are unimplemented on 64-pin and 80-pin devices; read as '0'.

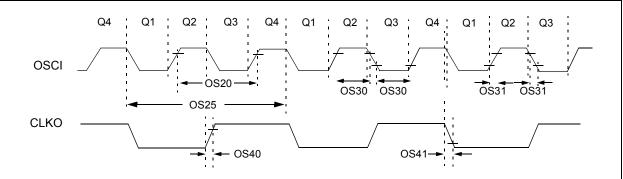

## 8.1 CPU Clocking Scheme

The system clock source can be provided by one of four sources:

- Primary Oscillator (POSC) on the OSCI and OSCO pins

- Secondary Oscillator (SOSC) on the SOSCI and SOSCO pins

- · Fast Internal RC (FRC) Oscillator

- · Low-Power Internal RC (LPRC) Oscillator

The Primary Oscillator and FRC sources have the option of using the internal USB PLL block, which generates both the USB module clock and a separate system clock from the 96 MHZ PLL. Refer to **Section 8.5 "Oscillator Modes and USB Operation"** for additional information.

The Fast Internal FRC provides an 8 MHz clock source. It can optionally be reduced by the programmable clock divider to provide a range of system clock frequencies.

The selected clock source generates the processor and peripheral clock sources. The processor clock source is divided by two to produce the internal instruction cycle clock, FCY. In this document, the instruction cycle clock is also denoted by FOSC/2. The internal instruction cycle clock, FOSC/2, can be provided on the OSCO I/O pin for some operating modes of the Primary Oscillator.

## 8.2 Initial Configuration on POR

The oscillator source (and operating mode) that is used at a device Power-on Reset event is selected using Configuration bit settings. The oscillator Configuration bit settings are located in the Configuration registers in the program memory (refer to **Section 26.1 "Configuration Bits"** for further details). The Primary Oscillator Configuration bits, POSCMD<1:0> (Configuration Word 2<1:0>), and the Initial Oscillator Select Configuration bits, FNOSC<2:0> (Configuration Word 2<10:8>), select the oscillator source that is used at a Power-on Reset. The FRC Primary Oscillator with Postscaler (FRCDIV) is the default (unprogrammed) selection. The Secondary Oscillator, or one of the internal oscillators, may be chosen by programming these bit locations.

The Configuration bits allow users to choose between the various clock modes, shown in Table 8-1.

#### 8.2.1 CLOCK SWITCHING MODE CONFIGURATION BITS

The FCKSM Configuration bits (Configuration Word 2<7:6>) are used to jointly configure device clock switching and the Fail-Safe Clock Monitor (FSCM). Clock switching is enabled only when FCKSM1 is programmed ('0'). The FSCM is enabled only when FCKSM<1:0> are both programmed ('00').

| Oscillator Mode                                    | Oscillator Source | POSCMD<1:0> | FNOSC<2:0> | Note |

|----------------------------------------------------|-------------------|-------------|------------|------|

| Fast RC Oscillator with Postscaler (FRCDIV)        | Internal          | 11          | 111        | 1, 2 |

| (Reserved)                                         | Internal          | XX          | 110        | 1    |

| Low-Power RC Oscillator (LPRC)                     | Internal          | 11          | 101        | 1    |

| Secondary (Timer1) Oscillator<br>(SOSC)            | Secondary         | 11          | 100        | 1    |

| Primary Oscillator (XT) with PLL<br>Module (XTPLL) | Primary           | 01          | 011        |      |

| Primary Oscillator (EC) with PLL<br>Module (ECPLL) | Primary           | 00          | 011        |      |

| Primary Oscillator (HS)                            | Primary           | 10          | 010        |      |

| Primary Oscillator (XT)                            | Primary           | 01          | 010        |      |

| Primary Oscillator (EC)                            | Primary           | 00          | 010        |      |

| Fast RC Oscillator with PLL Module (FRCPLL)        | Internal          | 11          | 001        | 1    |

| Fast RC Oscillator (FRC)                           | Internal          | 11          | 000        | 1    |

## TABLE 8-1: CONFIGURATION BIT VALUES FOR CLOCK SELECTION

**Note 1:** OSCO pin function is determined by the OSCIOFCN Configuration bit.

2: This is the default oscillator mode for an unprogrammed (erased) device.

### 10.4.3.3 Mapping Limitations

The control schema of the Peripheral Pin Select is extremely flexible. Other than systematic blocks that prevent signal contention caused by two physical pins being configured as the same functional input, or two functional outputs configured as the same pin, there are no hardware enforced lockouts. The flexibility extends to the point of allowing a single input to drive multiple peripherals or a single functional output to drive multiple output pins.

#### 10.4.3.4 Mapping Exceptions for PIC24FJ256GB110 Family Devices

Although the PPS registers theoretically allow for up to 64 remappable I/O pins, not all of these are implemented in all devices. For PIC24FJ256GB110 family devices, the maximum number of remappable pins available are 44, which includes 12 input only pins. In addition, some pins in the RP and RPI sequences are unimplemented in lower pin count devices. The differences in available remappable pins are summarized in Table 10-4.

When developing applications that use remappable pins, users should also keep these things in mind:

- For the RPINRx registers, bit combinations corresponding to an unimplemented pin for a particular device are treated as invalid; the corresponding module will not have an input mapped to it. For all PIC24FJ256GB110 family devices, this includes all values greater than 43 ('101011').

- For RPORx registers, the bit fields corresponding to an unimplemented pin will also be unimplemented. Writing to these fields will have no effect.

#### 10.4.4 CONTROLLING CONFIGURATION CHANGES

Because peripheral remapping can be changed during run time, some restrictions on peripheral remapping are needed to prevent accidental configuration changes. PIC24F devices include three features to prevent alterations to the peripheral map:

- Control register lock sequence

- Continuous state monitoring

- Configuration bit remapping lock

## 10.4.4.1 Control Register Lock

Under normal operation, writes to the RPINRx and RPORx registers are not allowed. Attempted writes will appear to execute normally, but the contents of the registers will remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the IOLOCK bit (OSCCON<6>). Setting IOLOCK prevents writes to the control registers; clearing IOLOCK allows writes.

To set or clear IOLOCK, a specific command sequence must be executed:

- 1. Write 46h to OSCCON<7:0>.

- 2. Write 57h to OSCCON<7:0>.

- 3. Clear (or set) IOLOCK as a single operation.

Unlike the similar sequence with the oscillator's LOCK bit, IOLOCK remains in one state until changed. This allows all of the Peripheral Pin Selects to be configured with a single unlock sequence, followed by an update to all control registers, then locked with a second lock sequence.

### 10.4.4.2 Continuous State Monitoring

In addition to being protected from direct writes, the contents of the RPINRx and RPORx registers are constantly monitored in hardware by shadow registers. If an unexpected change in any of the registers occurs (such as cell disturbances caused by ESD or other external events), a Configuration Mismatch Reset will be triggered.

#### 10.4.4.3 Configuration Bit Pin Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the RPINRx and RPORx registers. The IOL1WAY (CW2<4>) Configuration bit blocks the IOLOCK bit from being cleared after it has been set once. If IOLOCK remains set, the register unlock procedure will not execute and the Peripheral Pin Select Control registers cannot be written to. The only way to clear the bit and re-enable peripheral remapping is to perform a device Reset.

In the default (unprogrammed) state, IOL1WAY is set, restricting users to one write session. Programming IOL1WAY allows users unlimited access (with the proper use of the unlock sequence) to the Peripheral Pin Select registers.

| Device Din Count |       | RP Pins (I/O)         | RPI Pins |                     |  |  |  |  |

|------------------|-------|-----------------------|----------|---------------------|--|--|--|--|

| Device Pin Count | Total | Unimplemented         | Total    | Unimplemented       |  |  |  |  |

| 64-pin           | 28    | RP5, RP15, RP30, RP31 | 1        | RPI32-36, RPI38-43  |  |  |  |  |

| 80-pin           | 31    | RP31                  | 9        | RPI32, RPI39, RPI41 |  |  |  |  |

| 100-pin          | 32    | _                     | 12       | _                   |  |  |  |  |

#### TABLE 10-4: REMAPPABLE PIN EXCEPTIONS FOR PIC24FJ256GB110 FAMILY DEVICES

## REGISTER 10-25: RPOR3: PERIPHERAL PIN SELECT OUTPUT REGISTER 3

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|-------|-------|-------|

| —      | —   | RP7R5 | RP7R4 | RP7R3 | RP7R2 | RP7R1 | RP7R0 |

| bit 15 |     |       |       |       |       |       | bit 8 |

|        |     |       |       |       |       |       |       |

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| —      | —   | RP6R5 | RP6R4 | RP6R3 | RP6R2 | RP6R1 | RP6R0 |

| bit 7  |     |       |       |       |       |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                          |

|-----------|-----------------------------------------------------------------------------------------------------|

| bit 13-8  | RP7R<5:0>: RP7 Output Pin Mapping bits                                                              |

|           | Peripheral output number n is assigned to pin, RP7 (see Table 10-3 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                          |

| bit 5-0   | RP6R<5:0>: RP6 Output Pin Mapping bits                                                              |

|           | Peripheral output number n is assigned to pin, RP6 (see Table 10-3 for peripheral function numbers) |

#### REGISTER 10-26: RPOR4: PERIPHERAL PIN SELECT OUTPUT REGISTER 4

| U-0                | U-0 | R/W-0            | R/W-0 | R/W-0                       | R/W-0 | R/W-0              | R/W-0 |

|--------------------|-----|------------------|-------|-----------------------------|-------|--------------------|-------|

| —                  | —   | RP9R5            | RP9R4 | RP9R3                       | RP9R2 | RP9R1              | RP9R0 |

| bit 15             |     |                  |       |                             |       |                    | bit 8 |

|                    |     |                  |       |                             |       |                    |       |

| U-0                | U-0 | R/W-0            | R/W-0 | R/W-0                       | R/W-0 | R/W-0              | R/W-0 |

| —                  | _   | RP8R5            | RP8R4 | RP8R3                       | RP8R2 | RP8R1              | RP8R0 |

| bit 7              | •   |                  |       |                             |       |                    | bit 0 |

|                    |     |                  |       |                             |       |                    |       |

| Legend:            |     |                  |       |                             |       |                    |       |

| R = Readable bit W |     | W = Writable b   | oit   | U = Unimplemented bit, read |       | as '0'             |       |

| -n = Value at I    | POR | '1' = Bit is set |       | '0' = Bit is cleared        |       | x = Bit is unknown |       |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP9R<5:0>:** RP9 Output Pin Mapping bits Peripheral output number n is assigned to pin, RP9 (see Table 10-3 for peripheral function numbers)

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **RP8R<5:0>:** RP8 Output Pin Mapping bits Peripheral output number n is assigned to pin, RP8 (see Table 10-3 for peripheral function numbers)

|        |   |                       | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|--------|---|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| —      | _ | RP15R5 <sup>(1)</sup> | RP15R4 <sup>(1)</sup> | RP15R3 <sup>(1)</sup> | RP15R2 <sup>(1)</sup> | RP15R1 <sup>(1)</sup> | RP15R0 <sup>(1)</sup> |

| bit 15 |   |                       |                       |                       |                       |                       | bit 8                 |

| U-0   | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | RP14R5 | RP14R4 | RP14R3 | RP14R2 | RP14R1 | RP14R0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                           |

|-----------|------------------------------------------------------------------------------------------------------|

| bit 13-8  | RP15R<5:0>: RP15 Output Pin Mapping bits <sup>(1)</sup>                                              |

|           | Peripheral output number n is assigned to pin, RP0 (see Table 10-3 for peripheral function numbers)  |

| bit 7-6   | Unimplemented: Read as '0'                                                                           |

| bit 5-0   | RP14R<5:0>: RP14 Output Pin Mapping bits                                                             |

|           | Peripheral output number n is assigned to pin, RP14 (see Table 10-3 for peripheral function numbers) |

Note 1: Unimplemented on 64-pin devices; read as '0'.

### REGISTER 10-30: RPOR8: PERIPHERAL PIN SELECT OUTPUT REGISTER 8

| 1      |     |        |        |        |        |        |        |

|--------|-----|--------|--------|--------|--------|--------|--------|

| bit 15 |     |        |        |        |        |        | bit 8  |

|        | —   | RP17R5 | RP17R4 | RP17R3 | RP17R2 | RP17R1 | RP17R0 |

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

| U-0   | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | RP16R5 | RP16R4 | RP16R3 | RP16R2 | RP16R1 | RP16R0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | 1 as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-14

Unimplemented: Read as '0'

bit 13-8

RP17R<5:0>: RP17 Output Pin Mapping bits Peripheral output number n is assigned to pin, RP17 (see Table 10-3 for peripheral function numbers)

bit 7-6

Unimplemented: Read as '0'

bit 5-0

RP16R<5:0>: RP16 Output Pin Mapping bits Peripheral output number n is assigned to pin, RP16 (see Table 10-3 for peripheral function numbers)

© 2009 Microchip Technology Inc.

## 12.0 TIMER2/3 AND TIMER4/5

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "PIC24F Family Reference Manual", Section 14. "Timers" (DS39704).

The Timer2/3 and Timer4/5 modules are 32-bit timers, which can also be configured as four independent, 16-bit timers with selectable operating modes.

As 32-bit timers, Timer2/3 and Timer4/5 can each operate in three modes:

- Two independent 16-bit timers with all 16-bit operating modes (except Asynchronous Counter mode)

- Single 32-bit timer

- · Single 32-bit synchronous counter

They also support these features:

- Timer Gate Operation

- Selectable Prescaler Settings

- Timer Operation during Idle and Sleep modes

- · Interrupt on a 32-Bit Period Register Match

- ADC Event Trigger (Timer4/5 only)

Individually, all four of the 16-bit timers can function as synchronous timers or counters. They also offer the features listed above, except for the ADC Event Trigger; this is implemented only with Timer3. The operating modes and enabled features are determined by setting the appropriate bit(s) in the T2CON, T3CON, T4CON and T5CON registers. T2CON and T4CON are shown in generic form in Register 12-1; T3CON and T5CON are shown in Register 12-2.

For 32-bit timer/counter operation, Timer2 and Timer4 are the least significant word; Timer3 and Timer4 are the most significant word of the 32-bit timers.

| Note: | For 32-bit operation, T3CON and T5CON       |

|-------|---------------------------------------------|

|       | control bits are ignored. Only T2CON and    |

|       | T4CON control bits are used for setup and   |

|       | control. Timer2 and Timer4 clock and gate   |

|       | inputs are utilized for the 32-bit timer    |

|       | modules, but an interrupt is generated with |

|       | the Timer3 or Timer5 interrupt flags.       |

To configure Timer2/3 or Timer4/5 for 32-bit operation:

- 1. Set the T32 bit (T2CON<3> or T4CON<3> = 1).

- 2. Select the prescaler ratio for Timer2 or Timer4 using the TCKPS<1:0> bits.

- Set the Clock and Gating modes using the TCS and TGATE bits. If TCS is set to external clock, RPINRx (TxCK) must be configured to an available RPn pin. See Section 10.4 "Peripheral Pin Select" for more information.

- 4. Load the timer period value. PR3 (or PR5) will contain the most significant word of the value while PR2 (or PR4) contains the least significant word.

- 5. If interrupts are required, set the interrupt enable bit, T3IE or T5IE; use the priority bits, T3IP<2:0> or T5IP<2:0>, to set the interrupt priority. Note that while Timer2 or Timer4 controls the timer, the interrupt appears as a Timer3 or Timer5 interrupt.

- 6. Set the TON bit (= 1).

The timer value, at any point, is stored in the register pair, TMR3:TMR2 (or TMR5:TMR4). TMR3 (TMR5) always contains the most significant word of the count, while TMR2 (TMR4) contains the least significant word.

To configure any of the timers for individual 16-bit operation:

- Clear the T32 bit corresponding to that timer (T2CON<3> for Timer2 and Timer3 or T4CON<3> for Timer4 and Timer5).

- 2. Select the timer prescaler ratio using the TCKPS<1:0> bits.

- 3. Set the Clock and Gating modes using the TCS and TGATE bits. See Section 10.4 "Peripheral Pin Select" for more information.

- 4. Load the timer period value into the PRx register.

- 5. If interrupts are required, set the interrupt enable bit, TxIE; use the priority bits, TxIP<2:0>, to set the interrupt priority.

- 6. Set the TON bit (TxCON<15> = 1).

## 13.1.2 CASCADED (32-BIT) MODE

By default, each module operates independently with its own 16-bit timer. To increase resolution, adjacent even and odd modules can be configured to function as a single 32-bit module. (For example, modules 1 and 2 are paired, as are modules 3 and 4, and so on.) The odd numbered module (ICx) provides the Least Significant 16 bits of the 32-bit register pairs, and the even module (ICy) provides the Most Significant 16 bits. Wraparounds of the ICx registers cause an increment of their corresponding ICy registers.

Cascaded operation is configured in hardware by setting the IC32 bits (ICxCON2<8>) for both modules.

## 13.2 Capture Operations

The input capture module can be configured to capture timer values and generate interrupts on rising edges on ICx, or all transitions on ICx. Captures can be configured to occur on all rising edges, or just some (every 4th or 16th). Interrupts can be independently configured to generate on each event, or a subset of events.

To set up the module for capture operations:

- 1. Configure the ICx input for one of the available Peripheral Pin Select pins.

- 2. If Synchronous mode is to be used, disable the sync source before proceeding.

- 3. Make sure that any previous data has been removed from the FIFO by reading ICxBUF until the ICBNE bit (ICxCON1<3>) is cleared.

- 4. Set the SYNCSEL bits (ICxCON2<4:0>) to the desired sync/trigger source.

- 5. Set the ICTSEL bits (ICxCON1<12:10>) for the desired clock source.

- 6. Set the ICI bits (ICxCON1<6:5>) to the desired interrupt frequency

- 7. Select Synchronous or Trigger mode operation:

- a) Check that the SYNCSEL bits are not set to '00000'.

- b) For Synchronous mode, clear the ICTRIG bit (ICxCON2<7>).

- c) For Trigger mode, set ICTRIG, and clear the TRIGSTAT bit (ICxCON2<6>).

- 8. Set the ICM bits (ICxCON1<2:0>) to the desired operational mode.

- 9. Enable the selected trigger/sync source.

For 32-bit cascaded operations, the setup procedure is slightly different:

- 1. Set the IC32 bits for both modules (ICyCON2<8> and (ICxCON2<8>), enabling the even numbered module first. This ensures the modules will start functioning in unison.

- 2. Set the ICTSEL and SYNCSEL bits for both modules to select the same sync/trigger and time base source. Set the even module first, then the odd module. Both modules must use the same ICTSEL and SYNCSEL settings.

- Clear the ICTRIG bit of the even module (ICyCON2<7>); this forces the module to run in Synchronous mode with the odd module, regardless of its trigger setting.

- 4. Use the odd module's ICI bits (ICxCON1<6:5>) to the desired interrupt frequency.

- Use the ICTRIG bit of the odd module (ICxCON2<7>) to configure Trigger or Synchronous mode operation.

- Note: For Synchronous mode operation, enable the sync source as the last step. Both input capture modules are held in Reset until the sync source is enabled.

- Use the ICM bits of the odd module (ICxCON1<2:0>) to set the desired capture mode.

The module is ready to capture events when the time base and the trigger/sync source are enabled. When the ICBNE bit (ICxCON1<3>) becomes set, at least one capture value is available in the FIFO. Read input capture values from the FIFO until the ICBNE clears to '0'.

For 32-bit operation, read both the ICxBUF and ICyBUF for the full 32-bit timer value (ICxBUF for the lsw, ICyBUF for the msw). At least one capture value is available in the FIFO buffer when the odd module's ICBNE bit (ICxCON1<3>) becomes set. Continue to read the buffer registers until ICBNE is cleared (perform automatically by hardware).

## 18.1 Hardware Configuration

## 18.1.1 DEVICE MODE

## 18.1.1.1 D+ Pull-up Resistor

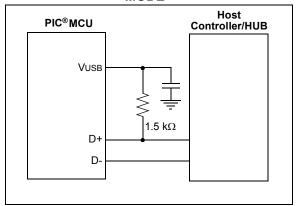

PIC24FJ256GB110 family devices have a built-in 1.5 kΩ resistor on the D+ line that is available when the microcontroller in operating in device mode. This is used to signal an external Host that the device is operating in Full Speed Device mode. It is engaged by setting the DPPULUP bit (U10TGCON<7>).

Alternatively, an external resistor may be used on D+, as shown in Figure 18-2.

#### FIGURE 18-2: EXTERNAL PULL-UP FOR FULL-SPEED DEVICE MODE

## 18.1.1.2 Power Modes

Many USB applications will likely have several different sets of power requirements and configuration. The most common power modes encountered are:

- Bus Power Only,

- · Self-Power Only and

- Dual Power with Self-Power Dominance.

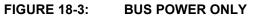

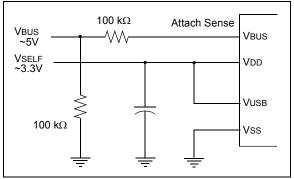

Bus Power Only mode (Figure 18-3) is effectively the simplest method. All power for the application is drawn from the USB.

To meet the inrush current requirements of the USB 2.0 Specification, the total effective capacitance appearing across VBUs and ground must be no more than 10  $\mu$ F.

In the USB Suspend mode, devices must consume no more than 2.5 mA from the 5V VBUS line of the USB cable. During the USB Suspend mode, the D+ or D-pull-up resistor must remain active, which will consume some of the allowed suspend current.

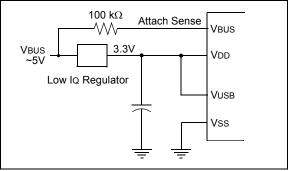

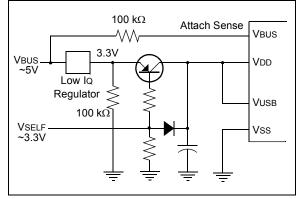

In Self-Power Only mode (Figure 18-4), the USB application provides its own power, with very little power being pulled from the USB. Note that an attach indication is added to indicate when the USB has been connected and the host is actively powering VBUS.

To meet compliance specifications, the USB module (and the D+ or D- pull-up resistor) should not be enabled until the host actively drives VBUS high. One of the 5.5V tolerant I/O pins may be used for this purpose.

The application should never source any current onto the 5V VBUS pin of the USB cable.

The Dual-power option with Self-Power Dominance (Figure 18-5) allows the application to use internal power primarily, but switch to power from the USB when no internal power is available. Dual-power devices must also meet all of the special requirements for inrush current and Suspend mode current previously described, and must not enable the USB module until VBUS is driven high.

FIGURE 18-4: SELF-POWER ONLY

FIGURE 18-5:

DUAL POWER EXAMPLE

### 18.6.2 HOST NEGOTIATION PROTOCOL (HNP)

In USB OTG applications, a Dual Role Device (DRD) is a device that is capable of being either a host or a peripheral. Any OTG DRD must support Host Negotiation Protocol (HNP).

HNP allows an OTG B-device to temporarily become the USB host. The A-device must first enable the B-device to follow HNP. Refer to the "On-The-Go Supplement to the USB 2.0 Specification" for more information regarding HNP. HNP may only be initiated at full speed.

After being enabled for HNP by the A-device, the B-device requests being the host any time that the USB link is in Suspend state, by simply indicating a disconnect. This can be done in software by clearing DPPULUP and DMPULUP. When the A-device detects the disconnect condition (via the URSTIF (U1IR<0>) interrupt), the A-device may allow the B-device to take over as Host. The A-device does this by signaling connect as a full-speed function. Software may accomplish this by setting DPPULUP.

If the A-device responds instead with resume signaling, the A-device remains as host. When the B-device detects the connect condition (via ATTACHIF (U1IR<6>), the B-device becomes host. The B-device drives Reset signaling prior to using the bus.

When the B-device has finished in its role as Host, it stops all bus activity and turns on its D+ pull-up resistor by setting DPPULUP. When the A-device detects a suspend condition (Idle for 3 ms), the A-device turns off its D+ pull-up. The A-device may also power-down VBUS supply to end the session. When the A-device detects the connect condition (via ATTACHIF), the A-device resumes host operation, and drives Reset signaling.

## 18.7 USB OTG Module Registers

There are a total of 37 memory mapped registers associated with the USB OTG module. They can be divided into four general categories:

- USB OTG Module Control (12)

- USB Interrupt (7)

- USB Endpoint Management (16)

- USB VBUS Power Control (2)

This total does not include the (up to) 128 BD registers in the BDT. Their prototypes, described in Register 18-1 and Register 18-2, are shown separately in **Section 18.2 "USB Buffer Descriptors and the BDT"**.

With the exception U1PWMCON and U1PWMRRS, all USB OTG registers are implemented in the Least Significant Byte of the register. Bits in the upper byte are unimplemented, and have no function. Note that some registers are instantiated only in Host mode, while other registers have different bit instantiations and functions in Device and Host modes.

Registers described in the following sections are those that have bits with specific control and configuration features. The following registers are used for data or address values only:

- U1BDTP1: Specifies the 256-word page in data RAM used for the BDT; 8-bit value with bit 0 fixed as '0' for boundary alignment

- U1FRML and U1FRMH: Contains the 11-bit byte counter for the current data frame

- U1PWMRRS: Contains the 8-bit value for PWM duty cycle (bits<15:8>) and PWM period (bits<7:0>) for the VBUS boost assist PWM module.

## REGISTER 18-5: U1PWRC: USB POWER CONTROL REGISTER

| U-0          | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 |  |

|--------------|-----|-----|-----|-----|-----|-----|-----|--|

| —            | —   | —   | —   | —   | —   | —   | —   |  |

| bit 15 bit 8 |     |     |     |     |     |     |     |  |

| R/W-0, HS   | U-0 | U-0 | R/W-0   | U-0 | U-0 | R/W-0, HC | R/W-0  |  |

|-------------|-----|-----|---------|-----|-----|-----------|--------|--|

| UACTPND     | —   | —   | USLPGRD | —   | —   | USUSPND   | USBPWR |  |

| bit 7 bit 0 |     |     |         |     |     |           |        |  |

| Legend:           | HS = Hardware Settable bit | HC = Hardware Clearable bit        |                    |  |

|-------------------|----------------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared               | x = Bit is unknown |  |

| bit 15-8 | Unimplemented: Read as '0'                                                                                                                                 |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7    | UACTPND: USB Activity Pending bit                                                                                                                          |

|          | <ul> <li>1 = Module should not be suspended at the moment (requires USLPGRD bit to be set)</li> <li>0 = Module may be suspended or powered down</li> </ul> |

| bit 6-5  | Unimplemented: Read as '0'                                                                                                                                 |

| bit 4    | USLPGRD: Sleep/Suspend Guard bit                                                                                                                           |

|          | <ul> <li>1 = Indicate to the USB module that it is about to be suspended or powered down</li> <li>0 = No suspend</li> </ul>                                |

| bit 3-2  | Unimplemented: Read as '0'                                                                                                                                 |

| bit 1    | USUSPND: USB Suspend Mode Enable bit                                                                                                                       |

|          | <ul> <li>1 = USB OTG module is in Suspend mode; USB clock is gated and the transceiver is placed in a<br/>low-power state</li> </ul>                       |

|          | 0 = Normal USB OTG operation                                                                                                                               |

| bit 0    | USBPWR: USB Operation Enable bit                                                                                                                           |

|          | 1 = USB OTG module is enabled                                                                                                                              |

|          | $0 = \text{USB OTG module is disabled}^{(1)}$                                                                                                              |

| Nata A.  |                                                                                                                                                            |

Note 1: Do not clear this bit unless the HOSTEN, USBEN and OTGEN bits (U1CON<3,0> and U1OTGCON<2>) are all cleared.

| R-0                   | R/W-0                                                                                                                                                                                 | R/W-0                                                                                                                                                     | R/W-0          | R/W-0             | R/W-0                     | R/W-0                              | R/W-0                 |  |  |  |  |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------------|---------------------------|------------------------------------|-----------------------|--|--|--|--|

| BUSY                  | IRQM1                                                                                                                                                                                 | IRQM0                                                                                                                                                     | INCM1          | INCM0             | MODE16                    | MODE1                              | MODE0                 |  |  |  |  |

| bit 15                |                                                                                                                                                                                       |                                                                                                                                                           |                |                   |                           |                                    | bit 8                 |  |  |  |  |

| R/W-0                 | R/W-0                                                                                                                                                                                 | R/W-0                                                                                                                                                     | R/W-0          | R/W-0             | R/W-0                     | R/W-0                              | R/W-0                 |  |  |  |  |

| WAITB1 <sup>(1)</sup> | WAITB0 <sup>(1)</sup>                                                                                                                                                                 | WAITM3                                                                                                                                                    | WAITM2         | WAITM1            | WAITM0                    | WAITE1 <sup>(1)</sup>              | WAITE0 <sup>(1)</sup> |  |  |  |  |

| bit 7                 |                                                                                                                                                                                       |                                                                                                                                                           |                |                   | •                         | •                                  | bit (                 |  |  |  |  |

| Legend:               |                                                                                                                                                                                       |                                                                                                                                                           |                |                   |                           |                                    |                       |  |  |  |  |

| R = Readabl           | le bit                                                                                                                                                                                | W = Writable                                                                                                                                              | bit            | U = Unimplen      | nented bit, read          | d as '0'                           |                       |  |  |  |  |

| -n = Value at         | POR                                                                                                                                                                                   | '1' = Bit is set                                                                                                                                          |                | '0' = Bit is cle  | ared                      | x = Bit is unkr                    | nown                  |  |  |  |  |

| bit 15                | BUSY: Busy I                                                                                                                                                                          | bit (Master mo                                                                                                                                            | de onlv)       |                   |                           |                                    |                       |  |  |  |  |

|                       | -                                                                                                                                                                                     | usy (not useful                                                                                                                                           |                | essor stall is ac | tive)                     |                                    |                       |  |  |  |  |

| bit 14-13             |                                                                                                                                                                                       | Interrupt Requ                                                                                                                                            | et Mode hite   |                   |                           |                                    |                       |  |  |  |  |

| 51(14-15              |                                                                                                                                                                                       |                                                                                                                                                           |                | er 3 is read or V | Vrite Buffer 3 is         | written (Buffere                   | ed PSP mode           |  |  |  |  |

|                       | 11 = Interrupt generated when Read Buffer 3 is read or Write Buffer 3 is written (Buffered PSP mode<br>or on a read or write operation when PMA<1:0> = 11 (Addressable PSP mode only) |                                                                                                                                                           |                |                   |                           |                                    |                       |  |  |  |  |

|                       |                                                                                                                                                                                       | <ul> <li>10 = No interrupt generated, processor stall activated</li> <li>01 = Interrupt generated at the end of the read/write cycle</li> </ul>           |                |                   |                           |                                    |                       |  |  |  |  |

|                       | 00 = No interrupt generated                                                                                                                                                           |                                                                                                                                                           |                |                   |                           |                                    |                       |  |  |  |  |

| bit 12-11             | INCM<1:0>: Increment Mode bits                                                                                                                                                        |                                                                                                                                                           |                |                   |                           |                                    |                       |  |  |  |  |

|                       | 11 = PSP read and write buffers auto-increment (Legacy PSP mode only)                                                                                                                 |                                                                                                                                                           |                |                   |                           |                                    |                       |  |  |  |  |

|                       | <ul> <li>10 = Decrement ADDR&lt;10:0&gt; by 1 every read/write cycle</li> <li>01 = Increment ADDR&lt;10:0&gt; by 1 every read/write cycle</li> </ul>                                  |                                                                                                                                                           |                |                   |                           |                                    |                       |  |  |  |  |

|                       | 00 = No increment or decrement of address                                                                                                                                             |                                                                                                                                                           |                |                   |                           |                                    |                       |  |  |  |  |

| bit 10                | MODE16: 8/1                                                                                                                                                                           | MODE16: 8/16-Bit Mode bit                                                                                                                                 |                |                   |                           |                                    |                       |  |  |  |  |

|                       |                                                                                                                                                                                       |                                                                                                                                                           |                |                   |                           | ter invokes two<br>r invokes one 8 |                       |  |  |  |  |

| bit 9-8               |                                                                                                                                                                                       | 8-bit mode: Data register is 8 bits, a read or write to the Data register invokes one 8-bit transfer <b>DE&lt;1:0&gt;:</b> Parallel Port Mode Select bits |                |                   |                           |                                    |                       |  |  |  |  |

|                       |                                                                                                                                                                                       | 11 = Master mode 1 (PMCS1, PMRD/PMWR, PMENB, PMBE, PMA <x:0> and PMD&lt;7:0&gt;)</x:0>                                                                    |                |                   |                           |                                    |                       |  |  |  |  |

|                       | 10 = Master mode 2 (PMCS1, PMRD, PMWR, PMBE, PMA <x:0> and PMD&lt;7:0&gt;)</x:0>                                                                                                      |                                                                                                                                                           |                |                   |                           |                                    |                       |  |  |  |  |

|                       | 01 = Enhanced PSP, control signals (PMRD, PMWR, PMCS1, PMD<7:0> and PMA<1:0>)<br>00 = Legacy Parallel Slave Port, control signals (PMRD, PMWR, PMCS1 and PMD<7:0>)                    |                                                                                                                                                           |                |                   |                           |                                    |                       |  |  |  |  |

| bit 7-6               |                                                                                                                                                                                       |                                                                                                                                                           |                |                   |                           |                                    | ,                     |  |  |  |  |