Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detuns                     |                                                                    |

|----------------------------|--------------------------------------------------------------------|

| Product Status             | Active                                                             |

| Core Processor             | 8052                                                               |

| Core Size                  | 8-Bit                                                              |

| Speed                      | 16.78MHz                                                           |

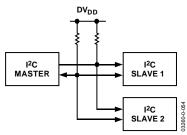

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                  |

| Peripherals                | DMA, PSM, PWM, Temp Sensor, WDT                                    |

| Number of I/O              | 32                                                                 |

| Program Memory Size        | 62KB (62K x 8)                                                     |

| Program Memory Type        | FLASH                                                              |

| EEPROM Size                | -                                                                  |

| RAM Size                   | 2.25K x 8                                                          |

| Voltage - Supply (Vcc/Vdd) | 4.75V ~ 5.25V                                                      |

| Data Converters            | A/D 8x12b                                                          |

| Oscillator Type            | Internal                                                           |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                  |

| Mounting Type              | Surface Mount                                                      |

| Package / Case             | 52-QFP                                                             |

| Supplier Device Package    | 80-PQFP (14x14)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/analog-devices/aduc843bsz62-5 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| arameter                                                                                                                                                                                                           | $V_{DD} = 5 V$                                | $V_{DD} = 3 V$                                | Unit                                                               | Test Conditions/Comments                                                                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-----------------------------------------------|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AC AC CHARACTERISTICS                                                                                                                                                                                              |                                               |                                               |                                                                    |                                                                                                                                                                     |

| Voltage Output Settling Time                                                                                                                                                                                       | 15                                            | 15                                            | μs typ                                                             | Full-scale settling time to within<br>1/2 LSB of final value                                                                                                        |

| Digital-to-Analog Glitch Energy                                                                                                                                                                                    | 10                                            | 10                                            | nV-sec typ                                                         | 1 LSB change at major carry                                                                                                                                         |

| PAC CHANNEL SPECIFICATIONS <sup>12, 13</sup>                                                                                                                                                                       |                                               |                                               |                                                                    |                                                                                                                                                                     |

| nternal Buffer Disabled ADuC841/ADuC842 Only                                                                                                                                                                       |                                               |                                               |                                                                    |                                                                                                                                                                     |

| C ACCURACY <sup>10</sup>                                                                                                                                                                                           |                                               |                                               |                                                                    |                                                                                                                                                                     |

| Resolution                                                                                                                                                                                                         | 12                                            | 12                                            | Bits                                                               |                                                                                                                                                                     |

| Relative Accuracy                                                                                                                                                                                                  | ±3                                            | ±3                                            | LSB typ                                                            |                                                                                                                                                                     |

| Differential Nonlinearity <sup>11</sup>                                                                                                                                                                            | -1                                            | -1                                            | LSB max                                                            | Guaranteed 12-bit monotonic                                                                                                                                         |

|                                                                                                                                                                                                                    | ±1/2                                          | ±1/2                                          | LSB typ                                                            |                                                                                                                                                                     |

| Offset Error                                                                                                                                                                                                       | ±5                                            | ±5                                            | mV max                                                             | V <sub>REF</sub> range                                                                                                                                              |

| Gain Error                                                                                                                                                                                                         | ±0.5                                          | ±0.5                                          | % typ                                                              | V <sub>REF</sub> range                                                                                                                                              |

| Gain Error Mismatch⁴                                                                                                                                                                                               | 0.5                                           | 0.5                                           | % typ                                                              | % of full-scale on DAC1                                                                                                                                             |

| NALOG OUTPUTS                                                                                                                                                                                                      |                                               |                                               | 1                                                                  |                                                                                                                                                                     |

| Voltage Range_0                                                                                                                                                                                                    | $0$ to $V_{\text{REF}}$                       | $0$ to $V_{\text{REF}}$                       | V typ                                                              | $DACV_{REF} = 2.5V$                                                                                                                                                 |

| EFERENCE INPUT/OUTPUT REFERENCE OUTPUT <sup>14</sup>                                                                                                                                                               |                                               |                                               | 1                                                                  |                                                                                                                                                                     |

| Output Voltage (V <sub>REF</sub> )                                                                                                                                                                                 | 2.5                                           | 2.5                                           | v                                                                  |                                                                                                                                                                     |

| Accuracy                                                                                                                                                                                                           | ±10                                           | ±10                                           | mV Max                                                             | Of $V_{REF}$ measured at the $C_{REF}$ pin $T_A = 25^{\circ}C$                                                                                                      |

| Power Supply Rejection                                                                                                                                                                                             | 65                                            | 67                                            | dB typ                                                             |                                                                                                                                                                     |

| Reference Temperature Coefficient                                                                                                                                                                                  | ±15                                           | ±15                                           | ppm/°C typ                                                         |                                                                                                                                                                     |

| Internal $V_{\text{REF}}$ Power-On Time                                                                                                                                                                            | 2                                             | 2                                             | ms typ                                                             |                                                                                                                                                                     |

| XTERNAL REFERENCE INPUT <sup>15</sup>                                                                                                                                                                              |                                               | -                                             |                                                                    |                                                                                                                                                                     |

| Voltage Range ( $V_{ReF}$ ) <sup>4</sup>                                                                                                                                                                           | 1                                             | 1                                             | V min                                                              |                                                                                                                                                                     |

|                                                                                                                                                                                                                    |                                               | V <sub>DD</sub>                               | V max                                                              |                                                                                                                                                                     |

| Input Impedance                                                                                                                                                                                                    | 20                                            | 20                                            | kΩ typ                                                             |                                                                                                                                                                     |

| Input Leakage                                                                                                                                                                                                      | 1                                             | 1                                             | μA max                                                             | Internal band gap deselected via                                                                                                                                    |

|                                                                                                                                                                                                                    |                                               |                                               | por tribust                                                        | ADCCON1.6                                                                                                                                                           |

| OWER SUPPLY MONITOR (PSM)                                                                                                                                                                                          |                                               |                                               |                                                                    |                                                                                                                                                                     |

| DV <sub>DD</sub> Trip Point Selection Range                                                                                                                                                                        |                                               | 2.93                                          | V min                                                              | Two trip points selectable in this                                                                                                                                  |

|                                                                                                                                                                                                                    |                                               | 3.08                                          | V max                                                              | range programmed via TPD1–0 in PSMCON, 3 V part only                                                                                                                |

| DV <sub>DD</sub> Power Supply Trip Point Accuracy                                                                                                                                                                  |                                               | ±2.5                                          | % max                                                              |                                                                                                                                                                     |

| VATCHDOG TIMER (WDT) <sup>4</sup>                                                                                                                                                                                  |                                               |                                               |                                                                    |                                                                                                                                                                     |

| Timeout Period                                                                                                                                                                                                     | 0                                             | 0                                             | ms min                                                             | Nine timeout periods selectable in                                                                                                                                  |

|                                                                                                                                                                                                                    | 2000                                          | 2000                                          | ms max                                                             | this range                                                                                                                                                          |

| LASH/EE MEMORY RELIABILITY CHARACTERISTICS <sup>16</sup>                                                                                                                                                           |                                               |                                               |                                                                    |                                                                                                                                                                     |

| Endurance <sup>17</sup>                                                                                                                                                                                            | 100,000                                       | 100,000                                       | Cycles min                                                         |                                                                                                                                                                     |

| Data Retention <sup>18</sup>                                                                                                                                                                                       | 100                                           | 100                                           | Years min                                                          |                                                                                                                                                                     |

|                                                                                                                                                                                                                    | - 1                                           | 1                                             | 1                                                                  |                                                                                                                                                                     |

| DIGITAL INPUTS                                                                                                                                                                                                     |                                               |                                               |                                                                    |                                                                                                                                                                     |

|                                                                                                                                                                                                                    | ±10                                           | ±10                                           | μA max                                                             | $V_{IN} = 0 V \text{ or } V_{DD}$                                                                                                                                   |

| NGITAL INPUTS<br>Input Leakage Current (Port 0, EA)                                                                                                                                                                | ±10<br>±1                                     | ±10<br>±1                                     | •                                                                  |                                                                                                                                                                     |

| Input Leakage Current (Port 0, EA)                                                                                                                                                                                 |                                               |                                               | μA max<br>μA typ                                                   | $\label{eq:VIN} \begin{split} V_{IN} &= 0 \; V \; or \; V_{DD} \\ V_{IN} &= 0 \; V \; or \; V_{DD} \end{split}$                                                     |

| Input Leakage Current (Port 0, EA)<br>Logic 1 Input Current                                                                                                                                                        | ±1                                            | ±1                                            | μA typ                                                             | $V_{\text{IN}}=0 \; V \; \text{or} \; V_{\text{DD}}$                                                                                                                |

| Input Leakage Current (Port 0, EA)                                                                                                                                                                                 | ±1<br>±10                                     | ±1<br>±10                                     | μA typ<br>μA max                                                   | $V_{IN} = 0 V \text{ or } V_{DD}$<br>$V_{IN} = V_{DD}$                                                                                                              |

| Input Leakage Current (Port 0, EA)<br>Logic 1 Input Current<br>(All Digital Inputs), SDATA, SCLOCK                                                                                                                 | ±1<br>±10<br>±1                               | ±1<br>±10<br>±1                               | μA typ<br>μA max<br>μA typ                                         | $V_{\text{IN}}=0 \; V \; \text{or} \; V_{\text{DD}}$                                                                                                                |

| Input Leakage Current (Port 0, EA)<br>Logic 1 Input Current                                                                                                                                                        | ±1<br>±10<br>±1<br>-75                        | ±1<br>±10<br>±1<br>-25                        | μA typ<br>μA max<br>μA typ<br>μA max                               | $\label{eq:VIN} \begin{split} V_{IN} &= 0 \; V \; or \; V_{DD} \\ V_{IN} &= V_{DD} \\ V_{IN} &= V_{DD} \end{split}$                                                 |

| Input Leakage Current (Port 0, EA)<br>Logic 1 Input Current<br>(All Digital Inputs), SDATA, SCLOCK<br>Logic 0 Input Current (Ports 1, 2, 3) SDATA, SCLOCK                                                          | ±1<br>±10<br>±1<br>-75<br>-40                 | ±1<br>±10<br>±1<br>-25<br>-15                 | μA typ<br>μA max<br>μA typ<br>μA max<br>μA typ                     | $V_{IN} = 0 V \text{ or } V_{DD}$ $V_{IN} = V_{DD}$ $V_{IN} = V_{DD}$ $V_{IL} = 450 \text{ mV}$                                                                     |

| Input Leakage Current (Port 0, EA)<br>Logic 1 Input Current<br>(All Digital Inputs), SDATA, SCLOCK                                                                                                                 | ±1<br>±10<br>±1<br>-75<br>-40<br>-660         | ±1<br>±10<br>±1<br>-25<br>-15<br>-250         | μA typ<br>μA max<br>μA typ<br>μA max<br>μA typ<br>μA max           | $V_{IN} = 0 V \text{ or } V_{DD}$ $V_{IN} = V_{DD}$ $V_{IN} = V_{DD}$ $V_{IL} = 450 \text{ mV}$ $V_{IL} = 2 V$                                                      |

| Input Leakage Current (Port 0, EA)<br>Logic 1 Input Current<br>(All Digital Inputs), SDATA, SCLOCK<br>Logic 0 Input Current (Ports 1, 2, 3) SDATA, SCLOCK<br>Logic 1 to Logic 0 Transition Current (Ports 2 and 3) | ±1<br>±10<br>±1<br>-75<br>-40<br>-660<br>-400 | ±1<br>±10<br>±1<br>-25<br>-15<br>-250<br>-140 | μA typ<br>μA max<br>μA typ<br>μA max<br>μA typ<br>μA max<br>μA typ | $\begin{split} V_{IN} &= 0 \ V \ or \ V_{DD} \\ \\ V_{IN} &= V_{DD} \\ V_{IN} &= V_{DD} \\ \\ V_{IL} &= 450 \ mV \\ V_{IL} &= 2 \ V \\ V_{IL} &= 2 \ V \end{split}$ |

| Input Leakage Current (Port 0, EA)<br>Logic 1 Input Current<br>(All Digital Inputs), SDATA, SCLOCK<br>Logic 0 Input Current (Ports 1, 2, 3) SDATA, SCLOCK                                                          | ±1<br>±10<br>±1<br>-75<br>-40<br>-660         | ±1<br>±10<br>±1<br>-25<br>-15<br>-250         | μA typ<br>μA max<br>μA typ<br>μA max<br>μA typ<br>μA max           | $V_{IN} = 0 V \text{ or } V_{DD}$ $V_{IN} = V_{DD}$ $V_{IN} = V_{DD}$ $V_{IL} = 450 \text{ mV}$ $V_{IL} = 2 V$                                                      |

Data Sheet

<sup>1</sup> Temperature Range –40°C to +85°C.

- <sup>2</sup> ADC linearity is guaranteed during normal MicroConverter core operation.

- <sup>3</sup> ADC LSB size =  $V_{REF}/2^{12}$ , that is, for internal  $V_{REF} = 2.5$  V, 1 LSB = 610  $\mu$ V, and for external  $V_{REF} = 1$  V, 1 LSB = 244  $\mu$ V.

- <sup>4</sup> These numbers are not production tested but are supported by design and/or characterization data on production release.

- <sup>5</sup> Offset and gain error and offset and gain error match are measured after factory calibration.

- <sup>6</sup> Based on external ADC system components, the user may need to execute a system calibration to remove additional external channel errors to achieve these

- specifications.

- <sup>7</sup> SNR calculation includes distortion and noise components.

- <sup>8</sup> Channel-to-channel crosstalk is measured on adjacent channels.

- <sup>9</sup> The temperature monitor gives a measure of the die temperature directly; air temperature can be inferred from this result.

- <sup>10</sup> DAC linearity is calculated using:

- Reduced code range of 100 to 4095, 0 V to V<sub>REF</sub> range.

- Reduced code range of 100 to 3945, 0 V to  $V_{DD}$  range.

- DAC output load =  $10 \text{ k}\Omega$  and 100 pF.

- <sup>11</sup> DAC differential nonlinearity specified on 0 V to V<sub>REF</sub> and 0 V to V<sub>DD</sub> ranges.

- <sup>12</sup> DAC specification for output impedance in the unbuffered case depends on DAC code.

- <sup>13</sup> DAC specifications for I<sub>SINK</sub>, voltage output settling time, and digital-to-analog glitch energy depend on external buffer implementation in unbuffered mode. DAC in unbuffered mode tested with OP270 external buffer, which has a low input leakage current.

- <sup>14</sup> Measured with C<sub>REF</sub> pin decoupled with 0.47 μF capacitor to ground. Power-up time for the internal reference is determined by the value of the decoupling capacitor chosen for the C<sub>REF</sub> pin.

- <sup>15</sup> When using an external reference device, the internal band gap reference input can be bypassed by setting the ADCCON1.6 bit.

- <sup>16</sup> Flash/EE memory reliability characteristics apply to both the Flash/EE program memory and the Flash/EE data memory.

- <sup>17</sup> Endurance is qualified to 100,000 cycles as per JEDEC Std. 22 method A117 and measured at -40°C, +25°C, and +85°C. Typical endurance at 25°C is 700,000 cycles.

<sup>18</sup> Retention lifetime equivalent at junction temperature (T<sub>j</sub>) = 55°C as per JEDEC Std. 22 method A117. Retention lifetime based on an activation energy of 0.6 eV derates with junction temperature as shown in Figure 38 in the Flash/EE Memory Reliability section.

- <sup>19</sup> Power supply current consumption is measured in normal, idle, and power-down modes under the following conditions:

- Normal Mode: Reset = 0.4 V, digital I/O pins = open circuit, Core Clk changed via CD bits in PLLCON (ADuC842/ADuC843), core executing internal software loop.

- Idle Mode: Reset = 0.4 V, digital I/O pins = open circuit, Core Clk changed via CD bits in PLLCON (ADuC842/ADuC843), PCON.0 = 1, core execution suspended in idle mode.

- Power-Down Mode: Reset = 0.4 V, all Port 0 pins = 0.4 V, All other digital I/O and Port 1 pins are open circuit, Core Clk changed via CD bits in PLLCON (ADuC842/ADuC843), PCON.0 = 1, core execution suspended in power-down mode, OSC turned on or off via OSC\_PD bit (PLLCON.7) in PLLCON SFR (ADuC842/ADuC843).

- <sup>20</sup> DV<sub>DD</sub> power supply current increases typically by 3 mA (3 V operation) and 10 mA (5 V operation) during a Flash/EE memory program or erase cycle.

- <sup>21</sup> Power supply currents are production tested at 5.25 V and 3.3 V for a 5 V and 3 V part, respectively.

Data Sheet

| Pin No.    | Mnemonic            | Type <sup>1</sup> | Description                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------|---------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11         | P1.4/ADC4           |                   | Input Port 1 (P1.4). Port 1 is an 8-bit input port only. Unlike the other ports, Port 1 defaults to analog input mode. To configure this port pin as a digital input, write a 0 to the port bit.                                                                                                                                                                                                                                  |

| 12         | P1.5/ADC5/SS        | I                 | Single-Ended Analog Input 4 (ADC4). Channel selection is via ADCCON2 SFR.<br>Input Port 1 (P1.5). Port 1 is an 8-bit input port only. Unlike the other ports, Port 1<br>defaults to analog input mode. To configure this port pin as a digital input, write a<br>0 to the port bit.                                                                                                                                               |

|            |                     |                   | Single-Ended Analog Input 5 (ADC5). Channel selection is via ADCCON2 SFR.<br>Slave Select Input for the SPI Interface (SS).                                                                                                                                                                                                                                                                                                       |

| 13         | P1.6/ADC6           | I                 | Input Port 1 (P1.6). Port 1 is an 8-bit input port only. Unlike the other ports, Port 1 defaults to analog input mode. To configure this port pin as a digital input, write a 0 to the port bit.                                                                                                                                                                                                                                  |

| 14         | P1.7/ADC7           | I                 | Single-Ended Analog Input 6 (ADC6). Channel selection is via ADCCON2 SFR.<br>Input Port 1(P1.7). Port 1 is an 8-bit input port only. Unlike the other ports, Port 1<br>defaults to analog input mode. To configure this port pin as a digital input, write a<br>0 to the port bit.                                                                                                                                                |

|            |                     |                   | Single-Ended Analog Input 7 (ADC7). Channel selection is via ADCCON2 SFR.                                                                                                                                                                                                                                                                                                                                                         |

| 15         | RESET               | I                 | Reset. Digital Input. A high level on this pin for 24 master clock cycles while the oscillator is running resets the device.                                                                                                                                                                                                                                                                                                      |

| 16         | P3.0/RxD            | I/O               | Input/Output Port 3 (P3.0). Port 3 is a bidirectional port with internal pull-up resistors. Port 3 pins that have 1s written to them are pulled high by the internal pull-up resistors, and in that state can be used as inputs. As inputs, Port 3 pins being pulled externally low source current because of the internal pull-up resistors.                                                                                     |

|            |                     |                   | Receiver Data Input (Asynchronous) or Data Input/Output (Synchronous) of the Serial (UART) Port (RxD).                                                                                                                                                                                                                                                                                                                            |

| 17         | P3.1/TxD            | I/O               | Input/Output Port 3 (P3.1). Port 3 is a bidirectional port with internal pull-up resistors. Port 3 pins that have 1s written to them are pulled high by the internal pull-up resistors, and in that state can be used as inputs. As inputs, Port 3 pins being pulled externally low source current because of the internal pull-up resistors.                                                                                     |

|            |                     |                   | Transmitter Data Output (Asynchronous) or Clock Output (Synchronous) of the Serial (UART) Port (TxD).                                                                                                                                                                                                                                                                                                                             |

| 18         | P3.2/INTO           | I/O               | Input/Output Port 3 (P3.2). Port 3 is a bidirectional port with internal pull-up resistors. Port 3 pins that have 1s written to them are pulled high by the internal pull-up resistors, and in that state can be used as inputs. As inputs, Port 3 pins being pulled externally low source current because of the internal pull-up resistors.                                                                                     |

|            |                     |                   | Interrupt 0 (INTO). Programmable edge or level triggered interrupt input; can be programmed to one of two priority levels. This pin can also be used as a gate control input to Timer 0.                                                                                                                                                                                                                                          |

| 19         | P3.3/INT1/MISO/PWM1 | I/O               | Input/Output Port 3 (P3.3). Port 3 is a bidirectional port with internal pull-up resistors. Port 3 pins that have 1s written to them are pulled high by the internal pull-up resistors, and in that state can be used as inputs. As inputs, Port 3 pins being pulled externally low source current because of the internal pull-up resistors.<br>Interrupt 1 (INT1). Programmable edge or level triggered interrupt input; can be |

|            |                     |                   | programmed to one of two priority levels. This pin can also be used as a gate control input to Timer 1.                                                                                                                                                                                                                                                                                                                           |

|            |                     |                   | SPI Master Input/Slave Output Data I/O Pin for SPI Serial Interface (MISO).<br>PWM 1 Voltage Output (PWM1). See the CFG841/CFG842 register for further<br>information.                                                                                                                                                                                                                                                            |

| 20, 34, 48 | DV <sub>DD</sub>    | Р                 | Digital Positive Supply Voltage. 3 V or 5 V nominal.                                                                                                                                                                                                                                                                                                                                                                              |

| 21, 35, 47 | DGND                | G                 | Digital Ground. DGND is the ground reference point for the digital circuitry.                                                                                                                                                                                                                                                                                                                                                     |

## TERMINOLOGY ADC SPECIFICATIONS

#### **Integral Nonlinearity**

The maximum deviation of any code from a straight line passing through the endpoints of the ADC transfer function. The endpoints of the transfer function are zero scale, a point ½ LSB below the first code transition, and full scale, a point ½ LSB above the last code transition.

### **Differential Nonlinearity**

The difference between the measured and the ideal 1 LSB change between any two adjacent codes in the ADC.

#### **Offset Error**

The deviation of the first code transition (0000 . . . 000) to (0000 . . . 001) from the ideal, that is,  $+\frac{1}{2}$  LSB.

#### **Gain Error**

The deviation of the last code transition from the ideal AIN voltage (Full Scale –  $\frac{1}{2}$  LSB) after the offset error has been adjusted out.

#### Signal-to-(Noise + Distortion) Ratio

The measured ratio of signal to (noise + distortion) at the output of the ADC. The signal is the rms amplitude of the fundamental. Noise is the rms sum of all nonfundamental signals up to half the sampling frequency ( $f_s/2$ ), excluding dc. The ratio depends on the number of quantization levels in the digitization process; the more levels, the smaller the quantization noise. The theoretical signal-to-(noise + distortion) ratio for an ideal N-bit converter with a sine wave input is given by

Signal-to-(Noise + Distortion) = (6.02N + 1.76) dB

Thus for a 12-bit converter, this is 74 dB.

### **Total Harmonic Distortion (THD)**

The ratio of the rms sum of the harmonics to the fundamental.

### DAC SPECIFICATIONS

#### **Relative Accuracy**

Relative accuracy or endpoint linearity is a measure of the maximum deviation from a straight line passing through the endpoints of the DAC transfer function. It is measured after adjusting for zero error and full-scale error.

#### Voltage Output Settling Time

The amount of time it takes for the output to settle to a specified level for a full-scale input change.

#### Digital-to-Analog Glitch Impulse

The amount of charge injected into the analog output when the inputs change state. It is specified as the area of the glitch in nV-sec.

Figure 24. Extended Stack Pointer Operation

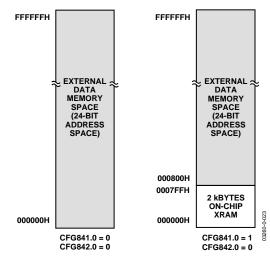

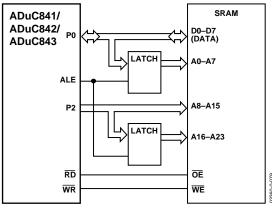

### External Data Memory (External XRAM)

Just like a standard 8051 compatible core, the ADuC841/ ADuC842/ADuC843 can access external data memory by using a MOVX instruction. The MOVX instruction automatically outputs the various control strobes required to access the data memory.

The parts, however, can access up to 16 MBytes of external data memory. This is an enhancement of the 64 kBytes of external data memory space available on a standard 8051 compatible core. The external data memory is discussed in more detail in the Hardware Design Considerations section.

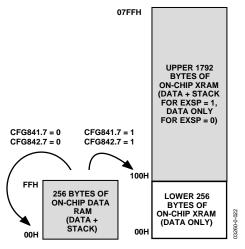

### Internal XRAM

The parts contain 2 kBytes of on-chip data memory. This memory, although on-chip, is also accessed via the MOVX instruction. The 2 kBytes of internal XRAM are mapped into the bottom 2 kBytes of the external address space if the CFG841/CFG842 bit is set. Otherwise, access to the external data memory occurs just like a standard 8051. When using the internal XRAM, Ports 0 and 2 are free to be used as generalpurpose I/O.

Figure 25. Internal and External XRAM

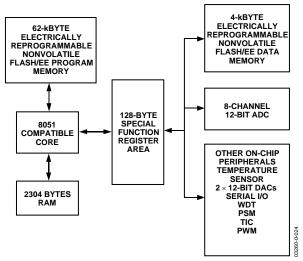

### **SPECIAL FUNCTION REGISTERS (SFRS)**

The SFR space is mapped into the upper 128 bytes of internal data memory space and is accessed by direct addressing only. It provides an interface between the CPU and all on-chip peripherals. A block diagram showing the programming model of the parts via the SFR area is shown in Figure 26.

All registers, except the program counter (PC) and the four general-purpose register banks, reside in the SFR area. The SFR registers include control, configuration, and data registers, which provide an interface between the CPU and all on-chip peripherals.

Figure 26. Programming Model

## **Data Sheet**

### ADCCON1—(ADC Control SFR 1)

The ADCCON1 register controls conversion and acquisition times, hardware conversion modes, and power-down modes as detailed below.

| SFR Address          | EFH |

|----------------------|-----|

| SFR Power-On Default | 40H |

| Bit Addressable      | No  |

### Table 8. ADCCON1 SFR Bit Designations

| Bit No. | Name       | Description                                                |                                                                                                                                                                                                                                                                |                                                                                                                                                                                                     |  |  |  |  |

|---------|------------|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7       | MD1        | The mode bit selects the active operating mode of the ADC. |                                                                                                                                                                                                                                                                |                                                                                                                                                                                                     |  |  |  |  |

|         |            | Set by the us                                              | et by the user to power up the ADC.                                                                                                                                                                                                                            |                                                                                                                                                                                                     |  |  |  |  |

|         |            | Cleared by the                                             | Cleared by the user to power down the ADC.                                                                                                                                                                                                                     |                                                                                                                                                                                                     |  |  |  |  |

| 6       | EXT_REF    | Set by the us                                              | et by the user to select an external reference.                                                                                                                                                                                                                |                                                                                                                                                                                                     |  |  |  |  |

|         |            | Cleared by th                                              | eared by the user to use the internal reference.                                                                                                                                                                                                               |                                                                                                                                                                                                     |  |  |  |  |

| 5       | CK1        |                                                            |                                                                                                                                                                                                                                                                | (CK1, CK0) select the divide ratio for the PLL master clock (ADuC842/ADuC843) or the                                                                                                                |  |  |  |  |

| 4       | CK0        | must be cho<br>plus the sele                               | external crystal (ADuC841) used to generate the ADC clock. To ensure correct ADC operation, the divider ratio must be chosen to reduce the ADC clock to 8.38 MHz or lower. A typical ADC conversion requires 16 ADC clocks blus the selected acquisition time. |                                                                                                                                                                                                     |  |  |  |  |

|         |            | The divider r                                              | atio is selecte                                                                                                                                                                                                                                                | ed as follows:                                                                                                                                                                                      |  |  |  |  |

|         |            | CK1                                                        | CK0                                                                                                                                                                                                                                                            | MCLK Divider                                                                                                                                                                                        |  |  |  |  |

|         |            | 0                                                          | 0                                                                                                                                                                                                                                                              | 32                                                                                                                                                                                                  |  |  |  |  |

|         |            | 0                                                          | 1                                                                                                                                                                                                                                                              | 4 (Do not use with a CD setting of 0)                                                                                                                                                               |  |  |  |  |

|         |            | 1                                                          | 0                                                                                                                                                                                                                                                              | 8                                                                                                                                                                                                   |  |  |  |  |

|         |            | 1                                                          | 1                                                                                                                                                                                                                                                              | 2                                                                                                                                                                                                   |  |  |  |  |

| 3<br>2  | AQ1<br>AQ0 |                                                            | The ADC acquisition select bits (AQ1, AQ0) select the time provided for the input track-and-hold amplifier to acquire the input signal. An acquisition of three or more ADC clocks is recommended; clocks are as follows:                                      |                                                                                                                                                                                                     |  |  |  |  |

|         |            | AQ1                                                        | AQ0                                                                                                                                                                                                                                                            | No. ADC Clks                                                                                                                                                                                        |  |  |  |  |

|         |            | 0                                                          | 0                                                                                                                                                                                                                                                              | 1                                                                                                                                                                                                   |  |  |  |  |

|         |            | 0                                                          | 1                                                                                                                                                                                                                                                              | 2                                                                                                                                                                                                   |  |  |  |  |

|         |            | 1                                                          | 0                                                                                                                                                                                                                                                              | 3                                                                                                                                                                                                   |  |  |  |  |

|         |            | 1                                                          | 1                                                                                                                                                                                                                                                              | 4                                                                                                                                                                                                   |  |  |  |  |

| 1       | T2C        | conversion s                                               | tart trigger ir                                                                                                                                                                                                                                                | 1                                                                                                                                                                                                   |  |  |  |  |

| 0       | EXC        | The external<br>active low co<br>required sam              | onvert start ir                                                                                                                                                                                                                                                | le bit (EXC) is set by the user to allow the external Pin P3.5 ( $\overline{\text{CONVST}}$ ) to be used as the pput. This input should be an active low pulse (minimum pulse width >100 ns) at the |  |  |  |  |

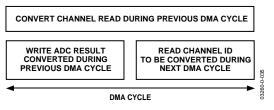

The DMA logic operates from the ADC clock and uses pipelining to perform the ADC conversions and to access the external memory at the same time. The time it takes to perform one ADC conversion is called a DMA cycle. The actions performed by the logic during a typical DMA cycle are shown in Figure 36.

Figure 36. DMA Cycle

Figure 36 shows that during one DMA cycle, the following actions are performed by the DMA logic:

- 1. An ADC conversion is performed on the channel whose ID was read during the previous cycle.

- 2. The 12-bit result and the channel ID of the conversion performed in the previous cycle is written to the external memory.

- 3. The ID of the next channel to be converted is read from external memory.

For the previous example, the complete flow of events is shown in Figure 36. Because the DMA logic uses pipelining, it takes three cycles before the first correct result is written out.

### Micro Operation during ADC DMA Mode

During ADC DMA mode, the MicroConverter core is free to continue code execution, including general housekeeping and communication tasks. However, note that MCU core accesses to Ports 0 and 2 (which of course are being used by the DMA controller) are gated off during the ADC DMA mode of operation. This means that even though the instruction that accesses the external Ports 0 or 2 appears to execute, no data is seen at these external ports as a result. Note that during DMA to the internally contained XRAM, Ports 0 and 2 are available for use.

The only case in which the MCU can access XRAM during DMA is when the internal XRAM is enabled and the section of RAM to which the DMA ADC results are being written to lies in an external XRAM. Then the MCU can access the internal XRAM only. This is also the case for use of the extended stack pointer.

The MicroConverter core can be configured with an interrupt to be triggered by the DMA controller when it has finished filling the requested block of RAM with ADC results, allowing the service routine for this interrupt to postprocess data without any real-time timing constraints.

### ADC Offset and Gain Calibration Coefficients

The ADuC841/ADuC842/ADuC843 have two ADC calibration coefficients, one for offset calibration and one for gain calibration. Both the offset and gain calibration coefficients are 14-bit words, and are each stored in two registers located in the special function register (SFR) area. The offset calibration coefficient is divided into ADCOFSH (six bits) and ADCOFSL (8 bits), and the gain calibration coefficient is divided into ADCGAINH (6 bits) and ADCGAINL (8 bits).

The offset calibration coefficient compensates for dc offset errors in both the ADC and the input signal. Increasing the offset coefficient compensates for positive offset, and effectively pushes the ADC transfer function down. Decreasing the offset coefficient compensates for negative offset, and effectively pushes the ADC transfer function up. The maximum offset that can be compensated is typically  $\pm 5\%$  of V<sub>REF</sub>, which equates to typically  $\pm 125$  mV with a 2.5 V reference.

Similarly, the gain calibration coefficient compensates for dc gain errors in both the ADC and the input signal. Increasing the gain coefficient compensates for a smaller analog input signal range and scales the ADC transfer function up, effectively increasing the slope of the transfer function. Decreasing the gain coefficient compensates for a larger analog input signal range and scales the ADC transfer function down, effectively decreasing the slope of the transfer function. The maximum analog input signal range for which the gain coefficient can compensate is  $1.025 \times V_{\text{REF}}$ , and the minimum input range is  $0.975 \times V_{\text{REF}}$ , which equates to typically  $\pm 2.5\%$  of the reference voltage.

### **CALIBRATING THE ADC**

Two hardware calibration modes are provided, which can be easily initiated by user software. The ADCCON3 SFR is used to calibrate the ADC. Bit 1 (typical) and CS3 to CS0 (ADCCON2) set up the calibration modes.

Device calibration can be initiated to compensate for significant changes in operating condition frequency, analog input range, reference voltage, and supply voltages. In this calibration mode, offset calibration uses internal AGND selected via ADCCON2 register Bits CS3 to CS0 (1011), and gain calibration uses internal  $V_{\text{REF}}$  selected by Bits CS3 to CS0 (1100). Offset calibration should be executed first, followed by gain calibration. System calibration can be initiated to compensate for both internal and external system errors. To perform system calibration by using an external reference, tie the system ground and reference to any two of the six selectable inputs. Enable external reference mode (ADCCON1.6). Select the channel connected to AGND via Bits CS3 to CS0 and perform system offset calibration. Select the channel connected to V<sub>REF</sub> via Bits CS3 to CS0 and perform system gain calibration.

### User Download Mode (ULOAD)

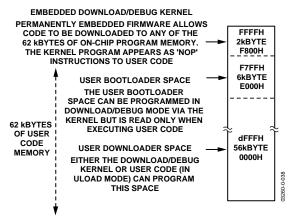

Figure 39 shows that it is possible to use the 62 kBytes of Flash/EE program memory available to the user as a single block of memory. In this mode, all of the Flash/EE memory is read-only to user code.

However, the Flash/EE program memory can also be written to during runtime simply by entering ULOAD mode. In ULOAD mode, the lower 56 kBytes of program memory can be erased and reprogrammed by user software as shown in Figure 39. ULOAD mode can be used to upgrade your code in the field via any user defined download protocol. By configuring the SPI port on the part as a slave, it is possible to completely reprogram the 56 kBytes of Flash/EE program memory in only 5 seconds (refer to Application Note uC007).

Alternatively, ULOAD mode can be used to save data to the 56 kBytes of Flash/EE memory. This can be extremely useful in data logging applications where the part can provide up to 60 kBytes of NV data memory on chip (4 kBytes of dedicated Flash/EE data memory also exist).

The upper 6 kBytes of the 62 kBytes of Flash/EE program memory are programmable only via serial download or parallel programming. This means that this space appears as read-only to user code. Therefore, it cannot be accidentally erased or reprogrammed by erroneous code execution, which makes it very suitable to use the 6 kBytes as a bootloader.

A bootload enable option exists in the serial downloader to "always run from E000H after reset." If using a bootloader, this option is recommended to ensure that the bootloader always executes correct code after reset. Programming the Flash/EE program memory via ULOAD mode is described in more detail in the description of ECON and in Application Note uC007.

Figure 39. Flash/EE Program Memory Map in ULOAD Mode (62 kByte Part)

# ADuC841/ADuC842/ADuC843

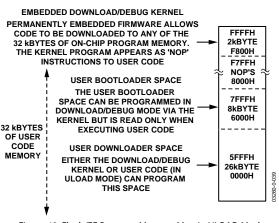

Figure 40. Flash/EE Program Memory Map in ULOAD Mode (32 kByte Part)

### Flash/EE Program Memory Security

The ADuC841/ADuC842/ADuC843 facilitate three modes of Flash/EE program memory security. These modes can be independently activated, restricting access to the internal code space. These security modes can be enabled as part of serial download protocol as described in Application Note uC004 or via parallel programming. The security modes available on the parts are as follows:

### Lock Mode

This mode locks the code memory, disabling parallel programming of the program memory. However, reading the memory in parallel mode and reading the memory via a MOVC command from external memory is still allowed. This mode is deactivated by initiating a code-erase command in serial download or parallel programming modes.

### Secure Mode

This mode locks code in memory, disabling parallel programming (program and verify/read commands) as well as disabling the execution of a MOVC instruction from external memory, which is attempting to read the op codes from internal memory. Read/write of internal data Flash/EE from external memory is also disabled. This mode is deactivated by initiating a code-erase command in serial download or parallel programming modes.

### Serial Safe Mode

This mode disables serial download capability on the device. If serial safe mode is activated and an attempt is made to reset the part into serial download mode, that is, RESET asserted and deasserted with PSEN low, the part interprets the serial download reset as a normal reset only. It therefore cannot enter serial download mode but can only execute as a normal reset sequence. Serial safe mode can be disabled only by initiating a code-erase command in parallel programming mode.

# **Data Sheet**

# ADuC841/ADuC842/ADuC843

| CFG841           | ADuC841 Config SFR |

|------------------|--------------------|

| SFR Address      | AFH                |

| Power-On Default | $10H^1$            |

| Bit Addressable  | No                 |

### Table 15. CFG841 SFR Bit Designations

| Bit No. | Name                                                                                         | Descri                                                                                                              | ption                                                                         |             |                                                                                  |  |  |  |  |

|---------|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------|----------------------------------------------------------------------------------|--|--|--|--|

| 7       | EXSP                                                                                         | Extended SP Enable.                                                                                                 |                                                                               |             |                                                                                  |  |  |  |  |

|         |                                                                                              | When s                                                                                                              | When set to 1 by the user, the stack rolls over from SPH/SP = 00FFH to 0100H. |             |                                                                                  |  |  |  |  |

|         |                                                                                              | When s                                                                                                              | et to 0 by                                                                    | the user,   | the stack rolls over from SP = FFH to SP = 00H.                                  |  |  |  |  |

| 6       | PWPO                                                                                         | PWM Pin Out Selection.                                                                                              |                                                                               |             |                                                                                  |  |  |  |  |

|         |                                                                                              | Set to 1                                                                                                            | by the u                                                                      | ser to sele | ct P3.4 and P3.3 as the PWM output pins.                                         |  |  |  |  |

|         |                                                                                              | Set to 0                                                                                                            | ) by the u                                                                    | ser to sele | ct P2.6 and P2.7 as the PWM output pins.                                         |  |  |  |  |

| 5       | DBUF                                                                                         | DAC O                                                                                                               | utput Buff                                                                    | er.         |                                                                                  |  |  |  |  |

|         |                                                                                              | Set to 1                                                                                                            | by the us                                                                     | ser to bypa | ass the DAC output buffer.                                                       |  |  |  |  |

|         |                                                                                              | Set to 0                                                                                                            | ) by the u                                                                    | ser to enal | ble the DAC output buffer.                                                       |  |  |  |  |

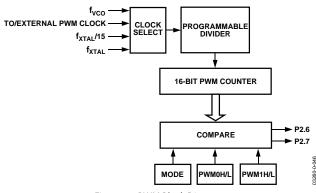

| 4       | EPM2                                                                                         |                                                                                                                     |                                                                               |             | /M Clock Frequency Configuration Bits.                                           |  |  |  |  |

|         |                                                                                              | Freque                                                                                                              | ncy shoul                                                                     | d be confi  | gured such that $F_{osc}$ /Divide Factor = 32 kHz + 50%.                         |  |  |  |  |

| 3       | EPM1                                                                                         | EPM2                                                                                                                | EPM1                                                                          | EPM0        | Divide Factor                                                                    |  |  |  |  |

| 2       | EPM0                                                                                         | 0                                                                                                                   | 0                                                                             | 0           | 32                                                                               |  |  |  |  |

|         |                                                                                              | 0                                                                                                                   | 0                                                                             | 1           | 64                                                                               |  |  |  |  |

|         |                                                                                              | 0                                                                                                                   | 1                                                                             | 0           | 128                                                                              |  |  |  |  |

|         |                                                                                              | 0                                                                                                                   | 1                                                                             | 1           | 256                                                                              |  |  |  |  |

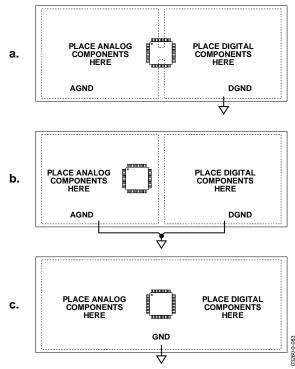

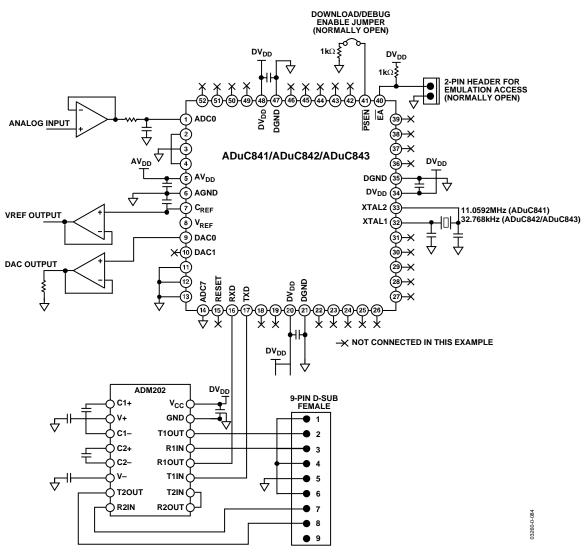

|         |                                                                                              | 1                                                                                                                   | 0                                                                             | 0           | 512                                                                              |  |  |  |  |