Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                        |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | XC800                                                                           |

| Core Size                  | 8-Bit                                                                           |

| Speed                      | 86MHz                                                                           |

| Connectivity               | SSI, UART/USART                                                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 19                                                                              |

| Program Memory Size        | 16KB (16K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 768 x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 8x10b                                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 38-TFSOP (0.173", 4.40mm Width)                                                 |

| Supplier Device Package    | PG-TSSOP-38                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/saf-xc866-4fri-3v-be |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## infineon

#### **Summary of Features**

#### Table 2Device Summary

|     | -                  |     |    |   |    |            |

|-----|--------------------|-----|----|---|----|------------|

|     | SAK-XC866*-1FRI 3V | 3.3 | -  | 4 | -  | Industrial |

|     | SAF-XC866*-4FRA 3V | 3.3 | 12 | 4 | _  | Automotive |

|     | SAF-XC866*-4FRI 3V | 3.3 | 12 | 4 | _  | Industrial |

|     | SAF-XC866*-2FRA 3V | 3.3 | 4  | 4 | _  | Automotive |

|     | SAF-XC866*-2FRI 3V | 3.3 | 4  | 4 | -  | Industrial |

|     | SAF-XC866*-1FRA 3V | 3.3 | -  | 4 | -  | Automotive |

|     | SAF-XC866*-1FRI 3V | 3.3 | -  | 4 | -  | Industrial |

| ROM | SAK-XC866*-4RRA    | 5.0 | -  | 4 | 16 | Automotive |

|     | SAK-XC866*-4RRI    | 5.0 | -  | 4 | 16 | Industrial |

|     | SAK-XC866*-2RRA    | 5.0 | -  | 4 | 8  | Automotive |

|     | SAK-XC866*-2RRI    | 5.0 | -  | 4 | 8  | Industrial |

|     | SAF-XC866*-4RRA    | 5.0 | -  | 4 | 16 | Automotive |

|     | SAF-XC866*-4RRI    | 5.0 | -  | 4 | 16 | Industrial |

|     | SAF-XC866*-2RRA    | 5.0 | _  | 4 | 8  | Automotive |

|     | SAF-XC866*-2RRI    | 5.0 | -  | 4 | 8  | Industrial |

|     | SAK-XC866*-4RRA 3V | 3.3 | -  | 4 | 16 | Automotive |

|     | SAK-XC866*-4RRI 3V | 3.3 | -  | 4 | 16 | Industrial |

|     | SAK-XC866*-2RRA 3V | 3.3 | -  | 4 | 8  | Automotive |

|     | SAK-XC866*-2RRI 3V | 3.3 | _  | 4 | 8  | Industrial |

|     | SAF-XC866*-4RRA 3V | 3.3 | -  | 4 | 16 | Automotive |

|     | SAF-XC866*-4RRI 3V | 3.3 | -  | 4 | 16 | Industrial |

|     | SAF-XC866*-2RRA 3V | 3.3 | -  | 4 | 8  | Automotive |

|     | SAF-XC866*-2RRI 3V | 3.3 | -  | 4 | 8  | Industrial |

1) Industrial is not for Automotive usage

<sup>2)</sup> The flash memory (P-Flash and D-Flash) can be used for code or data.

Note: The asterisk (\*) above denotes the device configuration letters from Table 1.

#### **Summary of Features**

#### **Ordering Information**

The ordering code for Infineon Technologies microcontrollers provides an exact reference to the required product. This ordering code identifies:

- The derivative itself, i.e. its function set, the temperature range, and the supply voltage

- the package and the type of delivery

For the available ordering codes for the XC866, please refer to your responsible sales representative or your local distributor.

As this document refers to all the derivatives, some descriptions may not apply to a specific product. For simplicity all versions are referred to by the term XC866 throughout this document.

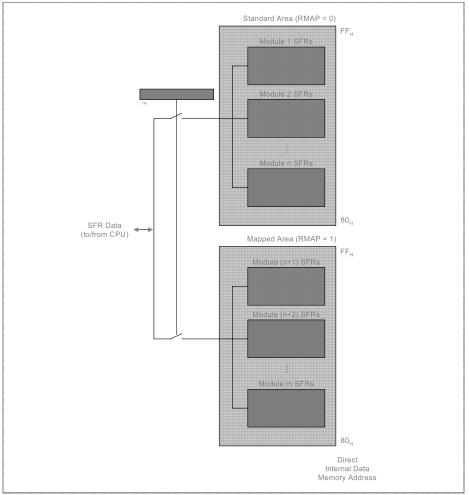

## Note: The RMAP bit must be cleared/set by ANL or ORL instructions. The rest bits of SYSCON0 should not be modified.

As long as bit RMAP is set, the mapped SFR area can be accessed. This bit is not cleared automatically by hardware. Thus, before standard/mapped registers are accessed, bit RMAP must be cleared/set, respectively, by software.

Figure 8 Address Extension by Mapping

#### Table 13 CCU6 Register Overview (cont'd)

| Addr            | Register Name                                                                                   | Bit                       | 7                | 6    | 5     | 4    | 3          | 2    | 1      | 0    |

|-----------------|-------------------------------------------------------------------------------------------------|---------------------------|------------------|------|-------|------|------------|------|--------|------|

| FB <sub>H</sub> | CCU6_CC60SRH Reset: 00 <sub>H</sub><br>Capture/Compare Shadow Register for                      | Bit Field CC60SH          |                  |      |       |      |            |      |        |      |

|                 | Channel CC60 High                                                                               | Type rwh                  |                  |      |       |      |            |      |        |      |

| FC <sub>H</sub> | CCU6_CC61SRL Reset: 00 <sub>H</sub><br>Capture/Compare Shadow Register for                      | Bit Field                 |                  |      |       |      |            |      |        |      |

|                 | Channel CC61 Low                                                                                | Туре                      | Type rwh         |      |       |      |            |      |        |      |

| FD <sub>H</sub> | CCU6_CC61SRH Reset: 00 <sub>H</sub><br>Capture/Compare Shadow Register for                      | Bit Field                 |                  |      |       | CC6  | 1SH        |      |        |      |

|                 | Channel CC61 High                                                                               | Туре                      |                  |      |       |      | vh         |      |        |      |

| FE <sub>H</sub> | CCU6_CC62SRL Reset: 00 <sub>H</sub><br>Capture/Compare Shadow Register for<br>Channel CC62 Low  | Bit Field                 |                  |      |       |      | 2SL        |      |        |      |

|                 |                                                                                                 | Type<br>Bit Field         |                  |      |       |      | vh<br>2SH  |      |        |      |

| FF <sub>H</sub> | CCU6_CC62SRH Reset: 00 <sub>H</sub><br>Capture/Compare Shadow Register for<br>Channel CC62 High |                           |                  |      |       |      |            |      |        |      |

| DMAD -          | 0, Page 1                                                                                       | Туре                      |                  |      |       | rv   | vh         |      |        |      |

| 9A <sub>H</sub> | CCU6_CC63RL Reset: 00 <sub>H</sub><br>Capture/Compare Register for Channel                      | Bit Field                 |                  |      |       | CC6  | 3VL        |      |        |      |

|                 | CC63 Low                                                                                        | Туре                      |                  |      |       | r    | h          |      |        |      |

| 9B <sub>H</sub> | CCU6_CC63RH Reset: 00 <sub>H</sub><br>Capture/Compare Register for Channel                      | Bit Field CC63VH          |                  |      |       |      |            |      |        |      |

|                 | CC63 High                                                                                       | Туре                      | •                |      |       |      |            |      |        |      |

| 9C <sub>H</sub> | CCU6_T12PRL Reset: 00 <sub>H</sub><br>Timer T12 Period Register Low                             |                           | Bit Field T12PVL |      |       |      |            |      |        |      |

| 00              | CCU6 T12PRH Reset: 00 <sub>H</sub>                                                              | 51                        | Type rwh         |      |       |      |            |      |        |      |

| 9D <sub>H</sub> | Timer T12 Period Register High                                                                  | Bit Field T12PVH Type rwh |                  |      |       |      |            |      |        |      |

| 9E <sub>H</sub> | CCU6_T13PRL Reset: 00 <sub>H</sub>                                                              | Bit Field T13PVL          |                  |      |       |      |            |      |        |      |

| 0-A             | Timer T13 Period Register Low                                                                   | Type rwh                  |                  |      |       |      |            |      |        |      |

| 9F <sub>H</sub> | CCU6_T13PRH Reset: 00 <sub>H</sub>                                                              | Bit Field T13PVH          |                  |      |       |      |            |      |        |      |

|                 | Timer T13 Period Register High                                                                  | Туре                      |                  |      |       | rv   | vh         |      |        |      |

| A4 <sub>H</sub> | CCU6_T12DTCL Reset: 00 <sub>H</sub>                                                             | Bit Field                 |                  |      |       |      |            |      |        |      |

|                 | Dead-Time Control Register for Timer<br>T12 Low                                                 | Туре                      |                  |      |       |      |            |      |        |      |

| A5 <sub>H</sub> | CCU6_T12DTCH Reset: 00 <sub>H</sub><br>Dead-Time Control Register for Timer                     | Bit Field                 | 0                | DTR2 | DTR1  | DTR0 | 0          | DTE2 | DTE1   | DTE0 |

|                 | T12 High                                                                                        | Туре                      | r                | rh   | rh    | rh   | r          | rw   | rw     | rw   |

| A6 <sub>H</sub> | CCU6_TCTR0L Reset: 00 <sub>H</sub><br>Timer Control Register 0 Low                              | Bit Field                 | СТМ              | CDIR | STE12 | T12R | T12<br>PRE |      | T12CLK |      |

|                 |                                                                                                 | Туре                      | rw               | rh   | rh    | rh   | rw         |      | rw     |      |

| A7 <sub>H</sub> | CCU6_TCTR0H Reset: 00 <sub>H</sub><br>Timer Control Register 0 High                             | Bit Field                 | (                |      | STE13 | T13R | T13<br>PRE |      | T13CLK |      |

|                 |                                                                                                 | Туре                      | 1                | r    | rh    | rh   | rw         |      | rw     |      |

| FA <sub>H</sub> | CCU6_CC60RL Reset: 00 <sub>H</sub><br>Capture/Compare Register for Channel<br>CC60 Low          |                           | Bit Field CC60VL |      |       |      |            |      |        |      |

| 50              |                                                                                                 | Type                      |                  |      |       |      | h          |      |        |      |

| FB <sub>H</sub> | CCU6_CC60RH Reset: 00 <sub>H</sub><br>Capture/Compare Register for Channel<br>CC60 High         | Bit Field                 |                  |      |       |      | 0VH        |      |        |      |

| 50              | •                                                                                               | Type<br>Bit Field         |                  |      |       |      | h          |      |        |      |

| FC <sub>H</sub> | CCU6_CC61RL Reset: 00 <sub>H</sub><br>Capture/Compare Register for Channel<br>CC61 Low          | Bit Field                 |                  |      |       |      | 51VL       |      |        |      |

|                 |                                                                                                 | Туре                      |                  |      |       | r    | h          |      |        |      |

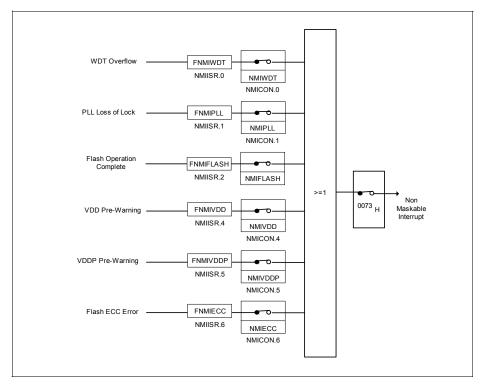

#### 3.4 Interrupt System

The XC800 Core supports one non-maskable interrupt (NMI) and 14 maskable interrupt requests. In addition to the standard interrupt functions supported by the core, e.g., configurable interrupt priority and interrupt masking, the XC866 interrupt system provides extended interrupt support capabilities such as the mapping of each interrupt vector to several interrupt sources to increase the number of interrupt sources supported, and additional status registers for detecting and determining the interrupt source.

#### 3.4.1 Interrupt Source

Figure 13 to Figure 17 give a general overview of the interrupt sources and illustrates the request and control flags.

#### Figure 13 Non-Maskable Interrupt Request Sources

| XINTR6  | 0033 <sub>H</sub> | ADC                  | EADC   | IEN1 |

|---------|-------------------|----------------------|--------|------|

| XINTR7  | 003B <sub>H</sub> | SSC                  | ESSC   |      |

| XINTR8  | 0043 <sub>H</sub> | External Interrupt 2 | EX2    |      |

| XINTR9  | 004B <sub>H</sub> | External Interrupt 3 | EXM    |      |

|         |                   | External Interrupt 4 |        |      |

|         |                   | External Interrupt 5 |        |      |

|         |                   | External Interrupt 6 |        |      |

| XINTR10 | 0053 <sub>H</sub> | CCU6 INP0            | ECCIP0 |      |

| XINTR11 | 005B <sub>H</sub> | CCU6 INP1            | ECCIP1 |      |

| XINTR12 | 0063 <sub>H</sub> | CCU6 INP2            | ECCIP2 |      |

| XINTR13 | 006B <sub>H</sub> | CCU6 INP3            | ECCIP3 |      |

#### Table 17 Interrupt Vector Addresses (cont'd)

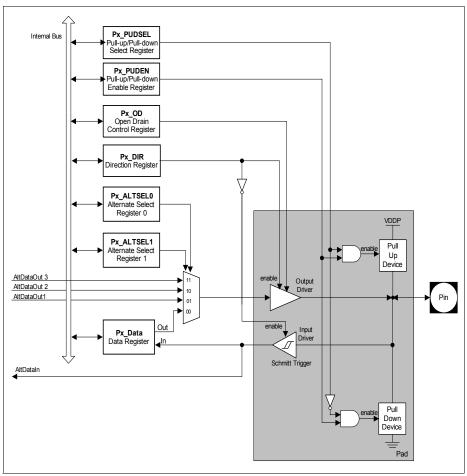

Figure 18 General Structure of Bidirectional Port

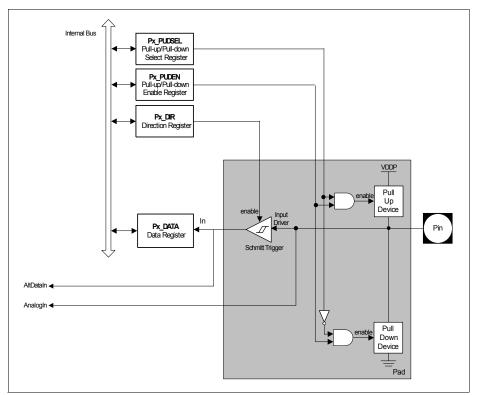

Figure 19 General Structure of Input Port

#### 3.7 Reset Control

The XC866 has five types of reset: power-on reset, hardware reset, watchdog timer reset, power-down wake-up reset, and brownout reset.

When the XC866 is first powered up, the status of certain pins (see **Table 20**) must be defined to ensure proper start operation of the device. At the end of a reset sequence, the sampled values are latched to select the desired boot option, which cannot be modified until the next power-on reset or hardware reset. This guarantees stable conditions during the normal operation of the device.

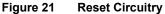

In order to power up the system properly, the external reset pin  $\overrightarrow{\text{RESET}}$  must be asserted until  $V_{\text{DDC}}$  reaches  $0.9^* V_{\text{DDC}}$ . The delay of external reset can be realized by an external capacitor at  $\overrightarrow{\text{RESET}}$  pin. This capacitor value must be selected so that  $V_{\text{RESET}}$  reaches 0.4 V, but not before  $V_{\text{DDC}}$  reaches 0.9\*  $V_{\text{DDC}}$ .

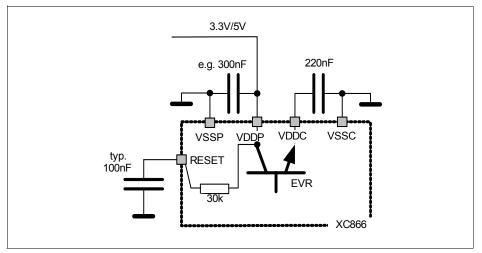

A typical application example is shown in **Figure 21**.  $V_{DDP}$  capacitor value is 300 nF.  $V_{DDC}$  capacitor value is 220 nF. The capacitor connected to RESET pin is 100 nF.

Typically, the time taken for  $V_{DDC}$  to reach  $0.9^*V_{DDC}$  is less than 50 µs once  $V_{DDP}$  reaches 2.3V. Hence, based on the condition that 10% to 90%  $V_{DDP}$  (slew rate) is less than 500 µs, the RESET pin should be held low for 500 µs typically. See **Figure 22**.

# infineon

#### **Functional Description**

#### Figure 22 V<sub>DDP</sub>, V<sub>DDC</sub> and V<sub>RESET</sub> during Power-on Reset

The second type of reset in XC866 is the hardware reset. This reset function can be used <u>during</u> normal operation or when the chip is in power-down mode. A reset input pin RESET is provided for the hardware reset. To ensure the recognition of the hardware reset, pin RESET must be held low for at least 100 ns.

The Watchdog Timer (WDT) module is also capable of resetting the device if it detects a malfunction in the system.

Another type of reset that needs to be detected is a reset while the device is in power-down mode (wake-up reset). While the contents of the static RAM are undefined after a power-on reset, they are well defined after a wake-up reset from power-down mode.

#### 3.8 Clock Generation Unit

The Clock Generation Unit (CGU) allows great flexibility in the clock generation for the XC866. The power consumption is indirectly proportional to the frequency, whereas the performance of the microcontroller is directly proportional to the frequency. During user program execution, the frequency can be programmed for an optimal ratio between performance and power consumption. Therefore the power consumption can be adapted to the actual application state.

#### Features:

- · Phase-Locked Loop (PLL) for multiplying clock source by different factors

- PLL Base Mode

- Prescaler Mode

- PLL Mode

- Power-down mode support

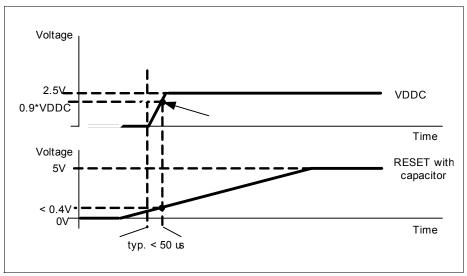

The CGU consists of an oscillator circuit and a PLL.In the XC866, the oscillator can be from either of these two sources: the on-chip oscillator (10 MHz) or the external oscillator (4 MHz to 12 MHz). The term "oscillator" is used to refer to both on-chip oscillator and external oscillator, unless otherwise stated. After the reset, the on-chip oscillator will be used by default. The external oscillator can be selected via software. In addition, the PLL provides a fail-safe logic to perform oscillator run and loss-of-lock detection. This allows emergency routines to be executed for system recovery or to perform system shut down.

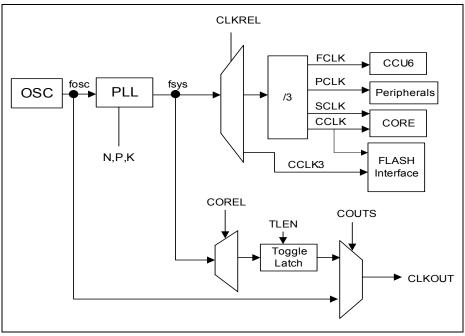

Figure 23 CGU Block Diagram

#### 3.8.2 Clock Management

The CGU generates all clock signals required within the microcontroller from a single clock,  $f_{sys}$ . During normal system operation, the typical frequencies of the different modules are as follow:

- CPU clock: CCLK, SCLK = 26.7 MHz

- CCU6 clock: FCLK = 26.7 MHz

- Other peripherals: PCLK = 26.7 MHz

- Flash Interface clock: CCLK3 = 80 MHz and CCLK = 26.7 MHz

In addition, different clock frequency can output to pin CLKOUT(P0.0). The clock output frequency can further be divided by 2 using toggle latch (bit TLEN is set to 1), the resulting output frequency has 50% duty cycle. **Figure 25** shows the clock distribution of the XC866.

Figure 25 Clock Generation from f<sub>svs</sub>

XC866

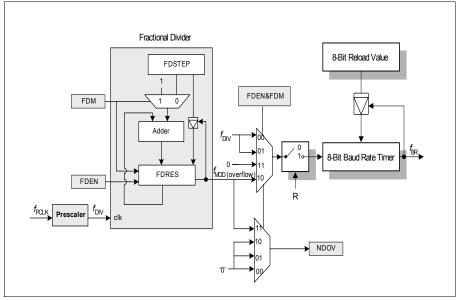

#### 3.11.1 Baud-Rate Generator

The baud-rate generator is based on a programmable 8-bit reload value, and includes divider stages (i.e., prescaler and fractional divider) for generating a wide range of baud rates based on its input clock  $f_{PCLK}$ , see **Figure 29**.

#### Figure 29 Baud-rate Generator Circuitry

The baud rate timer is a count-down timer and is clocked by either the output of the fractional divider ( $f_{MOD}$ ) if the fractional divider is enabled (FDCON.FDEN = 1), or the output of the prescaler ( $f_{DIV}$ ) if the fractional divider is disabled (FDEN = 0). For baud rate generation, the fractional divider must be configured to fractional divider mode (FDCON.FDM = 0). This allows the baud rate control run bit BCON.R to be used to start or stop the baud rate timer. At each timer underflow, the timer is reloaded with the 8-bit reload value in register BG and one clock pulse is generated for the serial channel.

Enabling the fractional divider in normal divider mode (FDEN = 1 and FDM = 1) stops the baud rate timer and nullifies the effect of bit BCON.R. See **Section 3.12**.

The baud rate  $(f_{BR})$  value is dependent on the following parameters:

- Input clock f<sub>PCLK</sub>

- Prescaling factor (2<sup>BRPRE</sup>) defined by bit field BRPRE in register BCON

- Fractional divider (STEP/256) defined by register FDSTEP (to be considered only if fractional divider is enabled and operating in fractional divider mode)

#### 3.14 High-Speed Synchronous Serial Interface

The High-Speed Synchronous Serial Interface (SSC) supports full-duplex and half-duplex synchronous communication. The serial clock signal can be generated by the SSC internally (master mode), using its own 16-bit baud-rate generator, or can be received from an external master (slave mode). Data width, shift direction, clock polarity and phase are programmable. This allows communication with SPI-compatible devices or devices using other synchronous serial interfaces.

#### Features:

- · Master and slave mode operation

- Full-duplex or half-duplex operation

- Transmit and receive buffered

- Flexible data format

- Programmable number of data bits: 2 to 8 bits

- Programmable shift direction: LSB or MSB shift first

- Programmable clock polarity: idle low or high state for the shift clock

- Programmable clock/data phase: data shift with leading or trailing edge of the shift clock

- · Variable baud rate

- · Compatible with Serial Peripheral Interface (SPI)

- Interrupt generation

- On a transmitter empty condition

- On a receiver full condition

- On an error condition (receive, phase, baud rate, transmit error)

#### 3.16 Timer 2

Timer 2 Modes

Table 29

Timer 2 is a 16-bit general purpose timer (THL2) that has two modes of operation, a 16-bit auto-reload mode and a 16-bit one channel capture mode. If the prescalar is disabled, Timer 2 counts with an input clock of PCLK/12. Timer 2 continues counting as long as it is enabled.

| Table 29           | Timer 2 wodes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mode               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Auto-reload        | <ul> <li>Up/Down Count Disabled</li> <li>Count up only</li> <li>Start counting from 16-bit reload value, overflow at FFFF<sub>H</sub></li> <li>Reload event configurable for trigger by overflow condition only, or by negative/positive edge at input pin T2EX as well</li> <li>Programmble reload value in register RC2</li> <li>Interrupt is generated with reload event</li> </ul>                                                                                                                                                                                                                                       |

|                    | <ul> <li>Up/Down Count Enabled</li> <li>Count up or down, direction determined by level at input pin T2EX</li> <li>No interrupt is generated</li> <li>Count up <ul> <li>Start counting from 16-bit reload value, overflow at FFF<sub>H</sub></li> <li>Reload event triggered by overflow condition</li> <li>Programmble reload value in register RC2</li> </ul> </li> <li>Count down <ul> <li>Start counting from FFF<sub>H</sub>, underflow at value defined in register RC2</li> <li>Reload event triggered by underflow condition <ul> <li>Reload event triggered by underflow condition</li> </ul> </li> </ul></li></ul> |

| Channel<br>capture | <ul> <li>Count up only</li> <li>Start counting from 0000<sub>H</sub>, overflow at FFFF<sub>H</sub></li> <li>Reload event triggered by overflow condition</li> <li>Reload value fixed at 0000<sub>H</sub></li> <li>Capture event triggered by falling/rising edge at pin T2EX</li> <li>Captured timer value stored in register RC2</li> <li>Interrupt is generated with reload or capture event</li> </ul>                                                                                                                                                                                                                    |

For module clock  $f_{ADC}$  = 26.7 MHz, the analog clock  $f_{ADCI}$  frequency can be selected as shown in **Table 30**.

| Module Clock f <sub>ADC</sub> | СТС                       | Prescaling Ratio | Analog Clock f <sub>ADCI</sub> |  |

|-------------------------------|---------------------------|------------------|--------------------------------|--|

| 26.7 MHz                      | 00 <sub>B</sub>           | ÷ 2              | 13.3 MHz (N.A)                 |  |

|                               | 01 <sub>B</sub>           | ÷ 3              | 8.9 MHz                        |  |

|                               | 10 <sub>B</sub>           | ÷ 4              | 6.7 MHz                        |  |

|                               | 11 <sub>B</sub> (default) | ÷ 32             | 833.3 kHz                      |  |

#### Table 30f\_ADCI Frequency Selection

As  $f_{ADCI}$  cannot exceed 10 MHz, bit field CTC should not be set to  $00_B$  when  $f_{ADC}$  is 26.7 MHz. During slow-down mode where  $f_{ADC}$  may be reduced to 13.3 MHz, 6.7 MHz etc., CTC can be set to  $00_B$  as long as the divided analog clock  $f_{ADCI}$  does not exceed 10 MHz. However, it is important to note that the conversion error could increase due to loss of charges on the capacitors, if  $f_{ADC}$  becomes too low during slow-down mode.

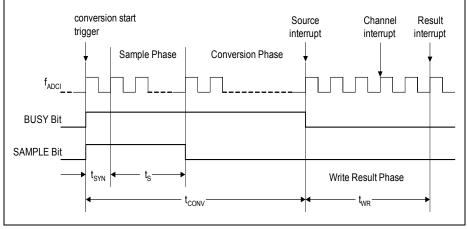

#### 3.18.2 ADC Conversion Sequence

The analog-to-digital conversion procedure consists of the following phases:

- Synchronization phase (t<sub>SYN</sub>)

- Sample phase (t<sub>S</sub>)

- Conversion phase

- Write result phase (t<sub>WR</sub>)

Figure 34 ADC Conversion Timing

#### 3.19.1 JTAG ID Register

This is a read-only register located inside the JTAG module, and is used to recognize the device(s) connected to the JTAG interface. Its content is shifted out when INSTRUCTION register contains the IDCODE command (opcode  $04_H$ ), and the same is also true immediately after reset.

The JTAG ID register contents for the XC866 devices are given in Table 31.

| Device Type | Device Name | JTAG ID                |  |

|-------------|-------------|------------------------|--|

| Flash       | XC866L-4FR  | 1010 0083 <sub>H</sub> |  |

|             | XC866-4FR   | 100F 5083 <sub>H</sub> |  |

|             | XC866L-2FR  | 1010 2083 <sub>H</sub> |  |

|             | XC866-2FR   | 1010 1083 <sub>H</sub> |  |

|             | XC866L-1FR  | 1013 8083 <sub>H</sub> |  |

|             | XC866-1FR   | 1013 8083 <sub>H</sub> |  |

#### Table 31JTAG ID Summary

| ROM | XC866L-4RR | 1013 9083 <sub>H</sub> |

|-----|------------|------------------------|

|     | XC866-4RR  | 1013 9083 <sub>H</sub> |

|     | XC866L-2RR | 1013 9083 <sub>H</sub> |

|     | XC866-2RR  | 1013 9083 <sub>H</sub> |

#### 3.20 Identification Register

The XC866 identity register is located at Page 1 of address B3<sub>H</sub>.

### ID

#### **Identity Register**

#### Reset Value: 0000 0010<sub>B</sub>

| 7      | 6 | 5 | 4 | 3 | 2     | 1 | 0        |

|--------|---|---|---|---|-------|---|----------|

| PRODID |   |   |   |   | VERID | I |          |

|        | I | r | I | I |       | r | <u> </u> |

| Field  | Bits  | Туре | Description                      |

|--------|-------|------|----------------------------------|

| VERID  | [2:0] | r    | Version ID<br>010 <sub>B</sub>   |

| PRODID | [7:3] | r    | Product ID<br>00000 <sub>B</sub> |

#### **Electrical Parameters**

#### 4.1.2 Absolute Maximum Rating

Maximum ratings are the extreme limits to which the XC866 can be subjected to without permanent damage.

| Table 32 | Absolute Maximum Rating Parameters |

|----------|------------------------------------|

|----------|------------------------------------|

| Parameter                                                    | Symbol            | Lim       | it Values                              | Unit | Notes                |  |

|--------------------------------------------------------------|-------------------|-----------|----------------------------------------|------|----------------------|--|

|                                                              |                   | min. max. |                                        |      |                      |  |

| Ambient temperature                                          | T <sub>A</sub>    | -40       | 125                                    | °C   | under bias           |  |

| Storage temperature                                          | T <sub>ST</sub>   | -65       | 150                                    | °C   |                      |  |

| Junction temperature                                         | TJ                | -40       | 150                                    | °C   | under bias           |  |

| Voltage on power supply pin with respect to $V_{\rm SS}$     | V <sub>DDP</sub>  | -0.5      | 6                                      | V    |                      |  |

| Voltage on core supply pin with respect to $V_{\rm SS}$      | V <sub>DDC</sub>  | -0.5      | 3.25                                   | V    |                      |  |

| Voltage on any pin with respect to $V_{\rm SS}$              | V <sub>IN</sub>   | -0.5      | V <sub>DDP</sub> +<br>0.5 or<br>max. 6 | V    | Whatever is<br>lower |  |

| Input current on any pin during overload condition           | I <sub>IN</sub>   | -10       | 10                                     | mA   |                      |  |

| Absolute sum of all input currents during overload condition | $\Sigma  I_{IN} $ | -         | 50                                     | mA   |                      |  |

Note: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. During absolute maximum rating overload conditions ( $V_{IN} > V_{DDP}$  or  $V_{IN} < V_{SS}$ ) the voltage on  $V_{DDP}$  pin with respect to ground ( $V_{SS}$ ) must not exceed the values defined by the absolute maximum ratings.

**Electrical Parameters**

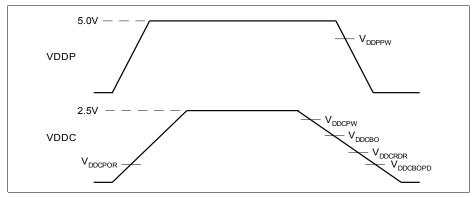

#### 4.2.2 Supply Threshold Characteristics

Figure 36 Supply Threshold Parameters

#### Table 35 Supply Threshold Parameters (Operating Conditions apply)

| Parameters                                                         | Symbol               |    | Limit Values |      |      | Unit | Remarks                  |

|--------------------------------------------------------------------|----------------------|----|--------------|------|------|------|--------------------------|

|                                                                    |                      |    | min.         | typ. | max. |      |                          |

| V <sub>DDC</sub> prewarning voltage <sup>1)</sup>                  | V <sub>DDCPW</sub>   | СС | 2.2          | 2.3  | 2.4  | V    |                          |

| $V_{\text{DDC}}$ brownout voltage in active mode <sup>1)</sup>     | V <sub>DDCBO</sub>   | СС | 2.0          | 2.1  | 2.2  | V    | XC866-4FR,<br>XC866-2FR  |

|                                                                    |                      |    | 2.0          | 2.1  | 2.3  | V    | XC866-1FR,<br>ROM device |

| RAM data retention voltage                                         | V <sub>DDCRDR</sub>  | СС | 0.9          | 1.0  | 1.1  | V    |                          |

| $V_{\text{DDC}}$ brownout voltage in power-down mode <sup>2)</sup> | V <sub>DDCBOPD</sub> | СС | 1.3          | 1.5  | 1.7  | V    |                          |

| $V_{\rm DDP}$ prewarning voltage <sup>3)</sup>                     | V <sub>DDPPW</sub>   | СС | 3.4          | 4.0  | 4.6  | V    |                          |

| Power-on reset voltage <sup>2)4)</sup>                             | V <sub>DDCPOR</sub>  | СС | 1.3          | 1.5  | 1.7  | V    |                          |

<sup>1)</sup> Detection is disabled in power-down mode.

<sup>2)</sup> Detection is enabled in both active and power-down mode.

<sup>3)</sup> Detection is enabled for external power supply of 5.0V. Detection must be disabled for external power supply of 3.3V.

<sup>4)</sup> The reset of EVR is extended by 300 µs typically after the VDDC reaches the power-on reset voltage.