Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | XC800                                                                        |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 86MHz                                                                        |

| Connectivity               | SSI, UART/USART                                                              |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 19                                                                           |

| Program Memory Size        | 16KB (16K x 8)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 768 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                  |

| Data Converters            | A/D 8x10b                                                                    |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 38-TFSOP (0.173", 4.40mm Width)                                              |

| Supplier Device Package    | PG-TSSOP-38                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/saf-xc866-4fri-bc |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Edition 2007-10 Published by Infineon Technologies AG, 81726 München, Germany © Infineon Technologies AG 2007. All Rights Reserved.

#### Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie"). With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of noninfringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

| Data Sheet<br>n History: | 2007-10                                                                                                                                                                         | V1.2                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| V1.0                     | 2006-02                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| Subjects (               | najor changes since last revision)                                                                                                                                              | )                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| Device sur               | nmary table is updated for Flash                                                                                                                                                | 4-Kb and ROM variants.                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| Footnote is              | added to MBC pin; description o                                                                                                                                                 | f $V_{\text{DDP}}$ pin is updated.                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|                          | •                                                                                                                                                                               | s type of register bit field                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| Access typ               | Access type of PAGE bits of all module page registers are corrected to rwh.                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| Access typ               | Access type of Px_DIR register bits are corrected to rwh                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| New bullet               | New bullet point on Flash delivery state is added to the feature list.                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| Digital pov              | er supply voltage are differentiate                                                                                                                                             | ed for 5V and 3.3V variants.                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|                          | 5                                                                                                                                                                               | /oltage on GPIO pins during                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| Figure on                | Power-on reset timing is updated.                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|                          | n History:<br>S Version: V 0.1<br>V1.0,<br>V1.1,<br>Subjects (n<br>Device sum<br>Footnote is<br>Section on<br>PASSWD.F<br>Access type<br>New bullet<br>Digital pow<br>VDDP powe | n History: 2007-10<br>s Version: V 0.1, 2005-01<br>V1.0, 2006-02<br>V1.1, 2006-12<br>Subjects (major changes since last revision)<br>Device summary table is updated for Flash 4<br>Footnote is added to MBC pin; description of<br>Section on bit protection scheme and access<br>PASSWD.PASS are updated.<br>Access type of PAGE bits of all module page<br>Access type of Px_DIR register bits are corr |  |  |  |  |

# We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to:

mcdocu.comments@infineon.com

$\ge$

#### **Summary of Features**

Features (continued):

- Reset generation

- Power-On reset

- Hardware reset

- Brownout reset for core logic supply

- Watchdog timer reset

- Power-Down Wake-up reset

- On-chip OSC and PLL for clock generation

- PLL loss-of-lock detection

- Power saving modes

- slow-down mode

- idle mode

- power-down mode with wake-up capability via RXD or EXINT0

- clock gating control to each peripheral

- Programmable 16-bit Watchdog Timer (WDT)

- Four ports

- 19 pins as digital I/O

- 8 pins as digital/analog input

- · 8-channel, 10-bit ADC

- Three 16-bit timers

- Timer 0 and Timer 1 (T0 and T1)

- Timer 2

- Capture/compare unit for PWM signal generation (CCU6)

- Full-duplex serial interface (UART)

- Synchronous serial channel (SSC)

- · On-chip debug support

- 1 Kbyte of monitor ROM (part of the 8-Kbyte Boot ROM)

- 64 bytes of monitor RAM

- PG-TSSOP-38 pin package

- Temperature range T<sub>A</sub>:

- SAF (-40 to 85 °C)

- SAK (-40 to 125 °C)

#### Summary of Features

#### **XC866 Variant Devices**

The XC866 product family features devices with different configurations and program memory sizes, temperature and quality profiles (Automotive or Industrial), offering cost-effective solution for different application requirements.

The configuration of LIN BSL for XC866 devices are summarized in Table 1.

| Device Name | LIN BSL Support |

|-------------|-----------------|

| XC866       | No              |

| XC866L      | Yes             |

The list of XC866 devices and their differences are summarized in Table 2.

| Device<br>Type      | Device Name        | Power<br>Supply<br>(V) | P-Flash<br>Size<br>(Kbytes) | D-Flash<br>Size<br>(Kbytes) | ROM<br>Size<br>(Kbytes) | Quality<br>Profile <sup>1)</sup> |

|---------------------|--------------------|------------------------|-----------------------------|-----------------------------|-------------------------|----------------------------------|

| Flash <sup>2)</sup> | SAK-XC866*-4FRA    | 5.0                    | 12                          | 4                           | _                       | Automotive                       |

|                     | SAK-XC866*-4FRI    | 5.0                    | 12                          | 4                           | _                       | Industrial                       |

|                     | SAK-XC866*-2FRA    | 5.0                    | 4                           | 4                           | -                       | Automotive                       |

|                     | SAK-XC866*-2FRI    | 5.0                    | 4                           | 4                           | -                       | Industrial                       |

|                     | SAK-XC866*-1FRA    | 5.0                    | _                           | 4                           | -                       | Automotive                       |

|                     | SAK-XC866*-1FRI    | 5.0                    | -                           | 4                           | _                       | Industrial                       |

|                     | SAF-XC866*-4FRA    | 5.0                    | 12                          | 4                           | _                       | Automotive                       |

|                     | SAF-XC866*-4FRI    | 5.0                    | 12                          | 4                           | _                       | Industrial                       |

|                     | SAF-XC866*-2FRA    | 5.0                    | 4                           | 4                           | -                       | Automotive                       |

|                     | SAF-XC866*-2FRI    | 5.0                    | 4                           | 4                           | _                       | Industrial                       |

|                     | SAF-XC866*-1FRA    | 5.0                    | -                           | 4                           | _                       | Automotive                       |

|                     | SAF-XC866*-1FRI    | 5.0                    | -                           | 4                           | _                       | Industrial                       |

|                     | SAK-XC866*-4FRA 3V | 3.3                    | 12                          | 4                           | -                       | Automotive                       |

|                     | SAK-XC866*-4FRI 3V | 3.3                    | 12                          | 4                           | -                       | Industrial                       |

|                     | SAK-XC866*-2FRA 3V | 3.3                    | 4                           | 4                           | _                       | Automotive                       |

|                     | SAK-XC866*-2FRI 3V | 3.3                    | 4                           | 4                           | -                       | Industrial                       |

|                     | SAK-XC866*-1FRA 3V | 3.3                    | _                           | 4                           | -                       | Automotive                       |

#### Table 2 Device Summary

The Port SFRs can be accessed in the standard memory area (RMAP = 0).

# Table 10Port Register Overview

| Addr                    | Register Name            |                        | Bit       | 7   | 6   | 5   | 4      | 3   | 2    | 1   | 0   |

|-------------------------|--------------------------|------------------------|-----------|-----|-----|-----|--------|-----|------|-----|-----|

| RMAP =                  |                          |                        |           |     |     |     |        |     |      |     |     |

| B2 <sub>H</sub>         | PORT PAGE                | Reset: 00 <sub>H</sub> | Bit Field | OP  |     | ST  | STNR 0 |     | PAGE |     |     |

|                         | Page Register for PORT   |                        | Туре      | ,   | N   | -   | N      | r   |      | rwh |     |

| RMAP =                  | 0, Page 0                |                        | .,,,,     |     |     |     |        |     |      |     |     |

| 80 <sub>H</sub>         | P0 DATA                  | Reset: 00 <sub>H</sub> | Bit Field |     | 0   | P5  | P4     | P3  | P2   | P1  | P0  |

|                         | P0 Data Register         |                        | Туре      |     | r   | rwh | rwh    | rwh | rwh  | rwh | rwh |

| 86 <sub>H</sub>         | P0 DIR                   | Reset: 00 <sub>H</sub> | Bit Field |     | 0   | P5  | P4     | P3  | P2   | P1  | P0  |

|                         | P0 Direction Register    |                        | Туре      |     | r   | rw  | rw     | rw  | rw   | rw  | rw  |

| 90 <sub>H</sub>         | P1 DATA                  | Reset: 00 <sub>H</sub> | Bit Field | P7  | P6  | P5  |        | 0   |      | P1  | P0  |

|                         | P1 Data Register         |                        | Туре      | rwh | rwh | rwh |        | r   |      | rwh | rwh |

| 91 <sub>H</sub>         | P1 DIR                   | Reset: 00 <sub>H</sub> | Bit Field | P7  | P6  | P5  |        | 0   |      | P1  | P0  |

|                         | P1 Direction Register    |                        | Туре      | rw  | rw  | rw  |        | r   |      | rw  | rw  |

| A0 <sub>H</sub>         | P2_DATA                  | Reset: 00 <sub>H</sub> | Bit Field | P7  | P6  | P5  | P4     | P3  | P2   | P1  | P0  |

|                         | P2 Data Register         |                        | Туре      | rwh | rwh | rwh | rwh    | rwh | rwh  | rwh | rwh |

| A1 <sub>H</sub>         | P2_DIR                   | Reset: 00 <sub>H</sub> | Bit Field | P7  | P6  | P5  | P4     | P3  | P2   | P1  | P0  |

|                         | P2 Direction Register    |                        | Туре      | rw  | rw  | rw  | rw     | rw  | rw   | rw  | rw  |

| В0 <sub>Н</sub>         | P3_DATA                  | Reset: 00 <sub>H</sub> | Bit Field | P7  | P6  | P5  | P4     | P3  | P2   | P1  | P0  |

|                         | P3 Data Register         |                        | Туре      | rwh | rwh | rwh | rwh    | rwh | rwh  | rwh | rwh |

| B1 <sub>H</sub>         | P3_DIR                   | Reset: 00 <sub>H</sub> | Bit Field | P7  | P6  | P5  | P4     | P3  | P2   | P1  | P0  |

|                         | P3 Direction Register    |                        | Туре      | rw  | rw  | rw  | rw     | rw  | rw   | rw  | rw  |

| RMAP =                  | 0, Page 1                |                        |           |     |     |     |        |     |      |     | 1   |

| 80 <sub>H</sub>         | P0_PUDSEL                | Reset: FF <sub>H</sub> | Bit Field |     | 0   | P5  | P4     | P3  | P2   | P1  | P0  |

| P0 Pull-Up/Pull-Down Se |                          | elect Register         | Туре      |     | r   | rw  | rw     | rw  | rw   | rw  | rw  |

| 86 <sub>H</sub>         | 86 <sub>H</sub> PO PUDEN | Reset: C4 <sub>H</sub> | Bit Field |     | 0   | P5  | P4     | P3  | P2   | P1  | P0  |

|                         | P0 Pull-Up/Pull-Down Er  | hable Register         | Туре      |     | r   | rw  | rw     | rw  | rw   | rw  | rw  |

| 90 <sub>H</sub>         | P1_PUDSEL                | Reset: FF <sub>H</sub> | Bit Field | P7  | P6  | P5  |        | 0   |      | P1  | P0  |

|                         | P1 Pull-Up/Pull-Down Se  | elect Register         | Туре      | rw  | rw  | rw  |        | r   |      | rw  | rw  |

| 91 <sub>H</sub>         | P1_PUDEN                 | Reset: FF <sub>H</sub> | Bit Field | P7  | P6  | P5  |        | 0   |      | P1  | P0  |

|                         | P1 Pull-Up/Pull-Down Er  | nable Register         | Туре      | rw  | rw  | rw  |        | r   |      | rw  | rw  |

| A0 <sub>H</sub>         | P2_PUDSEL                | Reset: FF <sub>H</sub> | Bit Field | P7  | P6  | P5  | P4     | P3  | P2   | P1  | P0  |

|                         | P2 Pull-Up/Pull-Down Se  | elect Register         | Туре      | rw  | rw  | rw  | rw     | rw  | rw   | rw  | rw  |

| A1 <sub>H</sub>         | P2_PUDEN                 | Reset: 00 <sub>H</sub> | Bit Field | P7  | P6  | P5  | P4     | P3  | P2   | P1  | P0  |

|                         | P2 Pull-Up/Pull-Down Er  | nable Register         | Туре      | rw  | rw  | rw  | rw     | rw  | rw   | rw  | rw  |

| B0 <sub>H</sub>         | P3_PUDSEL                | Reset: BF <sub>H</sub> | Bit Field | P7  | P6  | P5  | P4     | P3  | P2   | P1  | P0  |

|                         | P3 Pull-Up/Pull-Down Se  | elect Register         | Туре      | rw  | rw  | rw  | rw     | rw  | rw   | rw  | rw  |

| B1 <sub>H</sub>         | P3_PUDEN                 | Reset: 40 <sub>H</sub> | Bit Field | P7  | P6  | P5  | P4     | P3  | P2   | P1  | P0  |

|                         | P3 Pull-Up/Pull-Down Er  | nable Register         | Туре      | rw  | rw  | rw  | rw     | rw  | rw   | rw  | rw  |

| RMAP =                  | 0, Page 2                |                        |           |     |     |     |        |     |      |     |     |

| 80 <sub>H</sub>         | P0_ALTSEL0               | Reset: 00 <sub>H</sub> | Bit Field |     | 0   | P5  | P4     | P3  | P2   | P1  | P0  |

|                         | P0 Alternate Select 0 Re | gister                 | Туре      |     | r   | rw  | rw     | rw  | rw   | rw  | rw  |

| 86 <sub>H</sub>         | P0_ALTSEL1               | Reset: 00 <sub>H</sub> | Bit Field |     | 0   | P5  | P4     | P3  | P2   | P1  | P0  |

|                         | P0 Alternate Select 1 Re | gister                 | Туре      |     | r   | rw  | rw     | rw  | rw   | rw  | rw  |

| 90 <sub>H</sub>         | P1_ALTSEL0               | Reset: 00 <sub>H</sub> | Bit Field | P7  | P6  | P5  |        | 0   |      | P1  | P0  |

|                         | P1 Alternate Select 0 Re | gister                 | Туре      | rw  | rw  | rw  |        | r   |      | rw  | rw  |

| 91 <sub>H</sub>         | P1_ALTSEL1               | Reset: 00 <sub>H</sub> | Bit Field | P7  | P6  | P5  |        | 0   |      | P1  | P0  |

|                         | P1 Alternate Select 1 Re | gister                 | Туре      | rw  | rw  | rw  |        | r   |      | rw  | rw  |

| в0 <sub>Н</sub>         | P3_ALTSEL0               | Reset: 00 <sub>H</sub> | Bit Field | P7  | P6  | P5  | P4     | P3  | P2   | P1  | P0  |

|                         | P3 Alternate Select 0 Re | gister                 | Туре      | rw  | rw  | rw  | rw     | rw  | rw   | rw  | rw  |

| Table 16    | Flash Data Retention and Endurance (Operating Conditions apply |                               |                      |  |  |  |  |

|-------------|----------------------------------------------------------------|-------------------------------|----------------------|--|--|--|--|

| Retention   | Endurance <sup>1)</sup>                                        | Size                          | Remarks              |  |  |  |  |

| Program Fla | ish                                                            |                               |                      |  |  |  |  |

| 20 years    | 1,000 cycles                                                   | up to 16 Kbytes <sup>2)</sup> | for 16-Kbyte Variant |  |  |  |  |

| 20 years    | 1,000 cycles                                                   | up to 8 Kbytes <sup>2)</sup>  | for 8-Kbyte Variant  |  |  |  |  |

| 20 years    | 1,000 cycles                                                   | up to 4 Kbytes <sup>2)</sup>  | for 4-Kbyte Variant  |  |  |  |  |

| Data Flash  |                                                                |                               | - L                  |  |  |  |  |

| 20 years    | 1,000 cycles                                                   | 4 Kbytes                      |                      |  |  |  |  |

| 5 years     | 10,000 cycles                                                  | 1 Kbyte                       |                      |  |  |  |  |

| 2 years     | 70,000 cycles                                                  | 512 bytes                     |                      |  |  |  |  |

| 2 years     | 100,000 cycles                                                 | 128 bytes                     |                      |  |  |  |  |

Table 16 shows the Flash data retention and endurance targets.

<sup>1)</sup> One cycle refers to the programming of all wordlines in a sector and erasing of sector. The Flash endurance data specified in Table 16 is valid only if the following conditions are fulfilled:

- the maximum number of erase cycles per Flash sector must not exceed 100,000 cycles.

- the maximum number of erase cycles per Flash bank must not exceed 300,000 cycles.

- the maximum number of program cycles per Flash bank must not exceed 2,500,000 cycles.

<sup>2)</sup> If no Flash is used for data, the Program Flash size can be up to the maximum Flash size available in the device variant. Having more Data Flash will mean less Flash is available for Program Flash.

# 3.3.1 Flash Bank Sectorization

The XC866 product family offers four Flash devices with either 8 Kbytes or 16 Kbytes of embedded Flash memory. These Flash memory sizes are made up of two or four 4-Kbyte Flash banks, respectively. Each Flash device consists of Program Flash (P-Flash) bank(s) and a single Data Flash (D-Flash) bank with different sectorization shown in **Figure 11**. Both types can be used for code and data storage. The label "Data" neither implies that the D-Flash is mapped to the data memory region, nor that it can only be used for data storage. It is used to distinguish the different Flash bank sectorizations. The XC866 ROM devices offer a single 4-Kbyte D-Flash bank.

# 3.3.2 Flash Programming Width

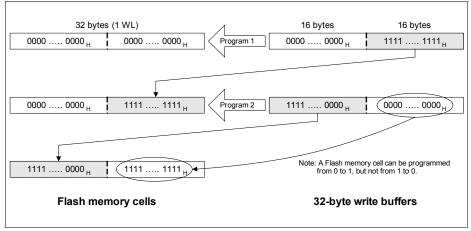

For the P-Flash banks, a programmed wordline (WL) must be erased before it can be reprogrammed as the Flash cells can only withstand one gate disturb. This means that the entire sector containing the WL must be erased since it is impossible to erase a single WL.

For the D-Flash bank, the same WL can be programmed twice before erasing is required as the Flash cells are able to withstand two gate disturbs. Hence, it is possible to program the same WL, for example, with 16 bytes of data in two times (see Figure 12).

## Figure 12 D-Flash Programming

Note: When programming a D-Flash WL the second time, the previously programmed Flash memory cells (whether 0s or 1s) should be reprogrammed with 0s to retain its original contents and to prevent "over-programming".

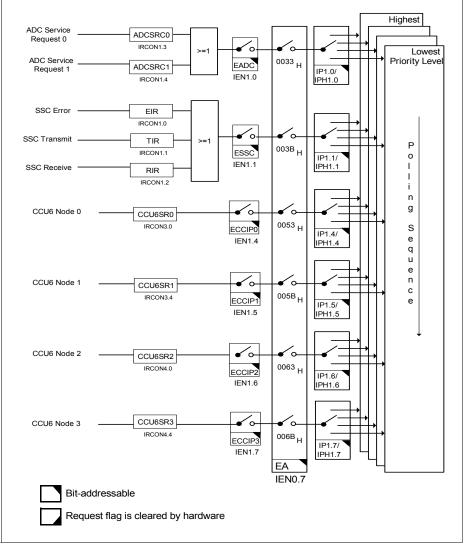

Figure 16 Interrupt Request Sources (Part 3)

# 3.4.2 Interrupt Source and Vector

Each interrupt source has an associated interrupt vector address. This vector is accessed to service the corresponding interrupt source request. The interrupt service of each interrupt source can be individually enabled or disabled via an enable bit. The assignment of the XC866 interrupt sources to the interrupt vector addresses and the corresponding interrupt source enable bits are summarized in Table 17.

| Interrupt<br>Source | t Vector Assignment for XC866<br>Address |                                                 | Enable Bit | SFR    |  |

|---------------------|------------------------------------------|-------------------------------------------------|------------|--------|--|

| NMI                 | 0073 <sub>H</sub>                        | Watchdog Timer NMI                              | NMIWDT     | NMICON |  |

|                     |                                          | PLL NMI                                         | NMIPLL     |        |  |

|                     |                                          | Flash NMI                                       | NMIFLASH   |        |  |

|                     |                                          | VDDC Prewarning NMI                             | NMIVDD     |        |  |

|                     |                                          | VDDP Prewarning NMI                             | NMIVDDP    |        |  |

|                     |                                          | Flash ECC NMI                                   | NMIECC     |        |  |

| XINTR0              | 0003 <sub>H</sub>                        | External Interrupt 0                            | EX0        | IEN0   |  |

| XINTR1              | 000B <sub>H</sub>                        | Timer 0                                         | ET0        |        |  |

| XINTR2              | 0013 <sub>H</sub>                        | External Interrupt 1                            | EX1        |        |  |

| XINTR3              | 001B <sub>H</sub>                        | Timer 1                                         | ET1        |        |  |

| XINTR4              | 0023 <sub>H</sub>                        | UART                                            | ES         |        |  |

| XINTR5              | 002B <sub>H</sub>                        | T2                                              | ET2        |        |  |

|                     |                                          | Fractional Divider<br>(Normal Divider Overflow) |            |        |  |

|                     |                                          | LIN                                             |            |        |  |

## Table 17 Interrupt Vector Addresses

# 3.4.3 Interrupt Priority

Each interrupt source, except for NMI, can be individually programmed to one of the four possible priority levels. The NMI has the highest priority and supersedes all other interrupts. Two pairs of interrupt priority registers (IP and IPH, IP1 and IPH1) are available to program the priority level of each non-NMI interrupt vector.

A low-priority interrupt can be interrupted by a high-priority interrupt, but not by another interrupt of the same or lower priority. Further, an interrupt of the highest priority cannot be interrupted by any other interrupt source.

If two or more requests of different priority levels are received simultaneously, the request of the highest priority is serviced first. If requests of the same priority are received simultaneously, then an internal polling sequence determines which request is serviced first. Thus, within each priority level, there is a second priority structure determined by the polling sequence shown in Table 18.

| Source                                      | Level     |

|---------------------------------------------|-----------|

| Non-Maskable Interrupt (NMI)                | (highest) |

| External Interrupt 0                        | 1         |

| Timer 0 Interrupt                           | 2         |

| External Interrupt 1                        | 3         |

| Timer 1 Interrupt                           | 4         |

| UART Interrupt                              | 5         |

| Timer 2, Fractional Divider, LIN Interrupts | 6         |

| ADC Interrupt                               | 7         |

| SSC Interrupt                               | 8         |

| External Interrupt 2                        | 9         |

| External Interrupt [6:3]                    | 10        |

| CCU6 Interrupt Node Pointer 0               | 11        |

| CCU6 Interrupt Node Pointer 1               | 12        |

| CCU6 Interrupt Node Pointer 2               | 13        |

| CCU6 Interrupt Node Pointer 3               | 14        |

Table 18

Priority Structure within Interrupt Level

# 3.5 Parallel Ports

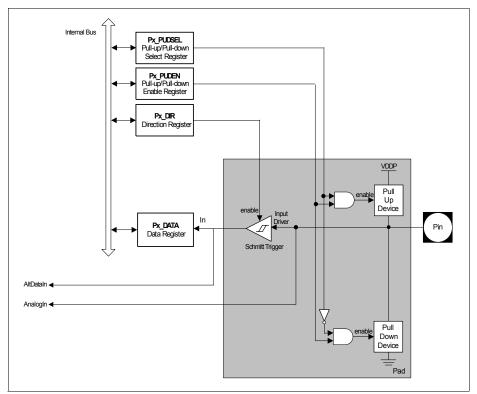

The XC866 has 27 port pins organized into four parallel ports, Port 0 (P0) to Port 3 (P3). Each pin has a pair of internal pull-up and pull-down devices that can be individually enabled or disabled. Ports P0, P1 and P3 are bidirectional and can be used as general purpose input/output (GPIO) or to perform alternate input/output functions for the on-chip peripherals. When configured as an output, the open drain mode can be selected. Port P2 is an input-only port, providing general purpose input functions, alternate input functions for the on-chip peripherals, and also analog inputs for the Analog-to-Digital Converter (ADC).

## **Bidirectional Port Features:**

- Configurable pin direction

- Configurable pull-up/pull-down devices

- · Configurable open drain mode

- Transfer of data through digital inputs and outputs (general purpose I/O)

- Alternate input/output for on-chip peripherals

## Input Port Features:

- · Configurable input driver

- Configurable pull-up/pull-down devices

- Receive of data through digital input (general purpose input)

- · Alternate input for on-chip peripherals

- · Analog input for ADC module

Figure 19 General Structure of Input Port

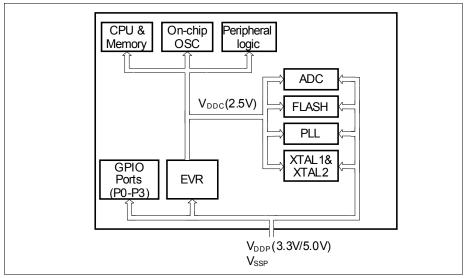

# 3.6 Power Supply System with Embedded Voltage Regulator

The XC866 microcontroller requires two different levels of power supply:

- 3.3 V or 5.0 V for the Embedded Voltage Regulator (EVR) and Ports

- 2.5 V for the core, memory, on-chip oscillator, and peripherals

**Figure 20** shows the XC866 power supply system. A power supply of 3.3 V or 5.0 V must be provided from the external power supply pin. The 2.5 V power supply for the logic is generated by the EVR. The EVR helps to reduce the power consumption of the whole chip and the complexity of the application board design.

The EVR consists of a main voltage regulator and a low power voltage regulator. In active mode, both voltage regulators are enabled. In power-down mode, the main voltage regulator is switched off, while the low power voltage regulator continues to function and provide power supply to the system with low power consumption.

Figure 20 XC866 Power Supply System

## EVR Features:

- Input voltage (V<sub>DDP</sub>): 3.3 V/5.0 V

- Output voltage (V<sub>DDC</sub>): 2.5 V ± 7.5%

- · Low power voltage regulator provided in power-down mode

- V<sub>DDC</sub> and V<sub>DDP</sub> prewarning detection

- V<sub>DDC</sub> brownout detection

# XC866

#### **Functional Description**

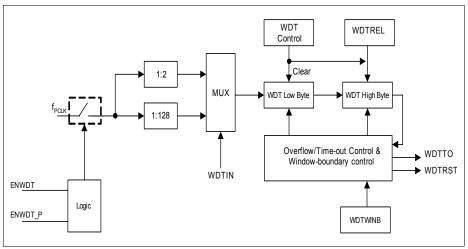

# 3.10 Watchdog Timer

The Watchdog Timer (WDT) provides a highly reliable and secure way to detect and recover from software or hardware failures. The WDT is reset at a regular interval that is predefined by the user. The CPU must service the WDT within this interval to prevent the WDT from causing an XC866 system reset. Hence, routine service of the WDT confirms that the system is functioning properly. This ensures that an accidental malfunction of the XC866 will be aborted in a user-specified time period. In debug mode, the WDT is suspended and stops counting. Therefore, there is no need to refresh the WDT during debugging.

## Features:

- 16-bit Watchdog Timer

- Programmable reload value for upper 8 bits of timer

- Programmable window boundary

- Selectable input frequency of f<sub>PCLK</sub>/2 or f<sub>PCLK</sub>/128

- Time-out detection with NMI generation and reset prewarning activation (after which a system reset will be performed)

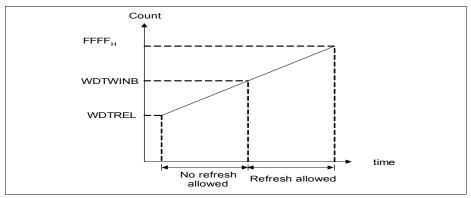

The WDT is a 16-bit timer incremented by a count rate of  $f_{PCLK}/2$  or  $f_{PCLK}/128$ . This 16-bit timer is realized as two concatenated 8-bit timers. The upper 8 bits of the WDT can be preset to a user-programmable value via a watchdog service access in order to modify the watchdog expire time period. The lower 8 bits are reset on each service access. Figure 27 shows the block diagram of the WDT unit.

If the WDT is not serviced before the timer overflow, a system malfunction is assumed. As a result, the WDT NMI is triggered (assert WDTTO) and the reset prewarning is entered. The prewarning period lasts for  $30_{\rm H}$  count, after which the system is reset (assert WDTRST).

The WDT has a "programmable window boundary" which disallows any refresh during the WDT's count-up. A refresh during this window boundary constitutes an invalid access to the WDT, causing the reset prewarning to be entered but without triggering the WDT NMI. The system will still be reset after the prewarning period is over. The window boundary is from  $0000_{\rm H}$  to the value obtained from the concatenation of WDTWINB and  $00_{\rm H}$ .

After being serviced, the WDT continues counting up from the value (<WDTREL>  $* 2^8$ ). The time period for an overflow of the WDT is programmable in two ways:

- the input frequency to the WDT can be selected to be either f<sub>PCLK</sub>/2 or f<sub>PCLK</sub>/128

- the reload value WDTREL for the high byte of WDT can be programmed in register WDTREL

The period,  $P_{WDT}$ , between servicing the WDT and the next overflow can be determined by the following formula:

$$P_{WDT} = \frac{2^{(1+WDTIN \times 6)} \times (2^{16} - WDTREL \times 2^8)}{f_{PCLK}}$$

If the Window-Boundary Refresh feature of the WDT is enabled, the period  $P_{WDT}$  between servicing the WDT and the next overflow is shortened if WDTWINB is greater than WDTREL, see Figure 28. This period can be calculated using the same formula by replacing WDTREL with WDTWINB. For this feature to be useful, WDTWINB should not be smaller than WDTREL.

Figure 28 WDT Timing Diagram

8-bit reload value (BR\_VALUE) for the baud rate timer defined by register BG

The following formulas calculate the final baud rate without and with the fractional divider respectively:

baud rate =

$$\frac{f_{PCLK}}{16 \times 2^{BRPRE} \times (BR \text{ VALUE} + 1)}$$

where  $2^{BRPRE} \times (BR_VALUE + 1) > 1$

baud rate =

$$\frac{f_{PCLK}}{16 \times 2^{BRPRE} \times (BR VALUE + 1)} \times \frac{STEP}{256}$$

The maximum baud rate that can be generated is limited to  $f_{PCLK}/32$ . Hence, for a module clock of 26.7 MHz, the maximum achievable baud rate is 0.83 MBaud.

Standard LIN protocal can support a maximum baud rate of 20kHz, the baud rate accuracy is not critical and the fractional divider can be disabled. Only the prescaler is used for auto baud rate calculation. For LIN fast mode, which supports the baud rate of 20kHz to 115.2kHz, the higher baud rates require the use of the fractional divider for greater accuracy.

**Table 26** lists the various commonly used baud rates with their corresponding parameter settings and deviation errors. The fractional divider is disabled and a module clock of 26.7 MHz is used.

| Baud rate  | Prescaling Factor<br>(2 <sup>BRPRE</sup> ) | Reload Value<br>(BR_VALUE + 1) | Deviation Error |  |

|------------|--------------------------------------------|--------------------------------|-----------------|--|

| 19.2 kBaud | 1 (BRPRE=000 <sub>B</sub> )                | 87 (57 <sub>H</sub> )          | -0.22 %         |  |

| 9600 Baud  | 1 (BRPRE=000 <sub>B</sub> )                | 174 (AE <sub>H</sub> )         | -0.22 %         |  |

| 4800 Baud  | 2 (BRPRE=001 <sub>B</sub> )                | 174 (AE <sub>H</sub> )         | -0.22 %         |  |

| 2400 Baud  | 4 (BRPRE=010 <sub>B</sub> )                | 174 (AE <sub>H</sub> )         | -0.22 %         |  |

| Table 26 | Typical Baud rates for UART with Fractional Divider disabled |

|----------|--------------------------------------------------------------|

|----------|--------------------------------------------------------------|

The fractional divider allows baud rates of higher accuracy (lower deviation error) to be generated. Table 27 lists the resulting deviation errors from generating a baud rate of

# 3.17 Capture/Compare Unit 6

The Capture/Compare Unit 6 (CCU6) provides two independent timers (T12, T13), which can be used for Pulse Width Modulation (PWM) generation, especially for AC-motor control. The CCU6 also supports special control modes for block commutation and multi-phase machines.

The timer T12 can function in capture and/or compare mode for its three channels. The timer T13 can work in compare mode only.

The multi-channel control unit generates output patterns, which can be modulated by T12 and/or T13. The modulation sources can be selected and combined for the signal modulation.

## Timer T12 Features:

- Three capture/compare channels, each channel can be used either as a capture or as a compare channel

- Supports generation of a three-phase PWM (six outputs, individual signals for highside and lowside switches)

- 16-bit resolution, maximum count frequency = peripheral clock frequency

- · Dead-time control for each channel to avoid short-circuits in the power stage

- Concurrent update of the required T12/13 registers

- · Generation of center-aligned and edge-aligned PWM

- · Supports single-shot mode

- · Supports many interrupt request sources

- · Hysteresis-like control mode

## Timer T13 Features:

- · One independent compare channel with one output

- 16-bit resolution, maximum count frequency = peripheral clock frequency

- Can be synchronized to T12

- · Interrupt generation at period-match and compare-match

- Supports single-shot mode

## Additional Features:

- · Implements block commutation for Brushless DC-drives

- Position detection via Hall-sensor pattern

- · Automatic rotational speed measurement for block commutation

- Integrated error handling

- Fast emergency stop without CPU load via external signal (CTRAP)

- · Control modes for multi-channel AC-drives

- · Output levels can be selected and adapted to the power stage

# 3.19 On-Chip Debug Support

The On-Chip Debug Support (OCDS) provides the basic functionality required for the software development and debugging of XC800-based systems.

The OCDS design is based on these principles:

- use the built-in debug functionality of the XC800 Core

- · add a minimum of hardware overhead

- provide support for most of the operations by a Monitor Program

- use standard interfaces to communicate with the Host (a Debugger)

#### Features:

- · Set breakpoints on instruction address and within a specified address range

- Set breakpoints on internal RAM address

- · Support unlimited software breakpoints in Flash/RAM code region

- Process external breaks

- · Step through the program code

The OCDS functional blocks are shown in **Figure 35**. The Monitor Mode Control (MMC) block at the center of OCDS system brings together control signals and supports the overall functionality. The MMC communicates with the XC800 Core, primarily via the Debug Interface, and also receives reset and clock signals. After processing memory address and control signals from the core, the MMC provides proper access to the dedicated extra-memories: a Monitor ROM (holding the code) and a Monitor RAM (for work-data and Monitor-stack). The OCDS system is accessed through the JTAG<sup>1</sup>, which is an interface dedicated exclusively for testing and debugging activities and is not normally used in an application. The dedicated MBC pin is used for external configuration and debugging control.

Note: All the debug functionality described here can normally be used only after XC866 has been started in OCDS mode.

<sup>&</sup>lt;sup>1)</sup> The pins of the JTAG port can be assigned to either Port 0 (primary) or Ports 1 and 2 (secondary). User must set the JTAG pins (TCK and TDI) as input during connection with the OCDS system.

#### **Electrical Parameters**

#### Table 34 Input/Output Characteristics (Operating Conditions apply)

| Parameter                                                                 | Symbol            |        | Limit Values |      | Unit | Test Conditions                                                                                  |

|---------------------------------------------------------------------------|-------------------|--------|--------------|------|------|--------------------------------------------------------------------------------------------------|

|                                                                           |                   |        | min.         | max. |      | Remarks                                                                                          |

| Pull-up current                                                           | I <sub>PU</sub>   | SR     | -            | -5   | μA   | V <sub>IH,min</sub>                                                                              |

|                                                                           |                   |        | -50          | -    | μA   | V <sub>IL,max</sub>                                                                              |

| Pull-down current                                                         | $I_{PD}$          | SR     | -            | 5    | μA   | V <sub>IL,max</sub>                                                                              |

|                                                                           |                   |        | 50           | -    | μA   | V <sub>IH,min</sub>                                                                              |

| Input leakage current <sup>2)</sup>                                       | I <sub>OZ1</sub>  | CC     | -1           | 1    | μA   | 0 < $V_{\rm IN}$ < $V_{\rm DDP}$ ,<br>$T_{\rm A} \le 125^{\circ}$ C , XC866-4FR<br>and XC866-2FR |

|                                                                           |                   |        | -2.5         | 1    | μA   | $0 < V_{IN} < V_{DDP},$<br>$T_A \le 125^{\circ}C, XC866-1FR$<br>and ROM device                   |

| Input current at XTAL1                                                    | $I_{ILX}$         | CC     | - 10         | 10   | μA   |                                                                                                  |

| Overload current on any pin                                               | I <sub>OV</sub>   | SR     | -5           | 5    | mA   |                                                                                                  |

| Absolute sum of overload currents                                         | $\Sigma   I_{OV}$ | <br>SR | -            | 25   | mA   | 3)                                                                                               |

| Voltage on any pin during $V_{\text{DDP}}$ power off                      | V <sub>PO</sub>   | SR     | -            | 0.3  | V    | 4)                                                                                               |

| Maximum current per pin (excluding $V_{\text{DDP}}$ and $V_{\text{SS}}$ ) | I <sub>M</sub>    | SR     | -            | 15   | mA   |                                                                                                  |

| Maximum current for all pins (excluding $V_{\rm DDP}$ and $V_{\rm SS}$ )  | $\Sigma  I_{M} $  | SR     | -            | 60   | mA   |                                                                                                  |

| Maximum current into $V_{\text{DDP}}$                                     | I <sub>MVDE</sub> | SR     | -            | 80   | mA   |                                                                                                  |

| Maximum current out of $V_{\rm SS}$                                       | I <sub>MVSS</sub> | SR     | -            | 80   | mA   |                                                                                                  |

<sup>1)</sup> Not subjected to production test, verified by design/characterization. Hysteresis is implemented to avoid meta stable states and switching due to internal ground bounce. It cannot be guaranteed that it suppresses switching due to external system noise.

<sup>2)</sup> <u>An additional error current ( $l_{INJ}$ ) will flow if an overload current flows through an adjacent pin. TMS pin and RESET pin have internal pull devices and are not included in the input leakage current characteristic.</u>

<sup>3)</sup> Not subjected to production test, verified by design/characterization.

#### **Electrical Parameters**

## 4.3 AC Parameters

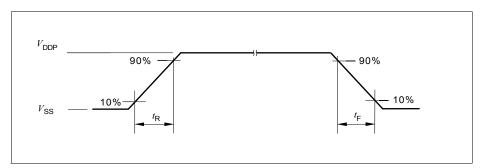

# 4.3.1 Testing Waveforms

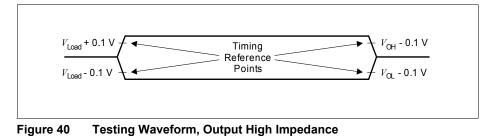

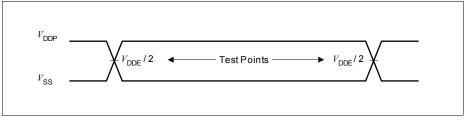

The testing waveforms for rise/fall time, output delay and output high impedance are shown in Figure 38, Figure 39 and Figure 40.

Figure 38 Rise/Fall Time Parameters

Figure 39 Testing Waveform, Output Delay