Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                      |

| Core Processor             | XC800                                                                         |

| Core Size                  | 8-Bit                                                                         |

| Speed                      | 86MHz                                                                         |

| Connectivity               | LINbus, SSI, UART/USART                                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                         |

| Number of I/O              | 19                                                                            |

| Program Memory Size        | 4KB (4K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 768 x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                   |

| Data Converters            | A/D 8x10b                                                                     |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 38-TFSOP (0.173", 4.40mm Width)                                               |

| Supplier Device Package    | PG-TSSOP-38                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/saf-xc866l-1fra-ab |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# XC866 8-Bit Single-Chip Microcontroller

# Microcontrollers

Never stop thinking

#### **General Device Information**

# 2 General Device Information

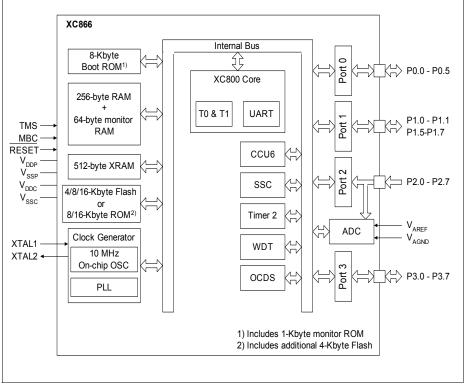

# 2.1 Block Diagram

Figure 2 XC866 Block Diagram

# **General Device Information**

# 2.4 Pin Definitions and Functions

# Table 3 Pin Definitions and Functions

| Symbol | Pin<br>Number | Туре | Reset<br>State | Function                                                                                                                                                    |                                                                                                                            |  |

|--------|---------------|------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--|

| P0     |               | I/O  |                | <b>Port 0</b><br>Port 0 is a 6-bit bidirectional general purpose I/<br>port. It can be used as alternate functions for th<br>JTAG, CCU6, UART, and the SSC. |                                                                                                                            |  |

| P0.0   | 12            |      | Hi-Z           | TCK_0<br>T12HR_1                                                                                                                                            | JTAG Clock Input<br>CCU6 Timer 12 Hardware Run<br>Input                                                                    |  |

|        |               |      |                | CC61_1<br>CLKOUT<br>RXDO_1                                                                                                                                  | Input/Output of Capture/Compare<br>channel 1<br>Clock Output<br>UART Transmit Data Output                                  |  |

| P0.1   | 14            |      | Hi-Z           | TDI_0<br>T13HR_1                                                                                                                                            | JTAG Serial Data Input<br>CCU6 Timer 13 Hardware Run<br>Input                                                              |  |

|        |               |      |                | RXD_1<br>COUT61_1                                                                                                                                           | UART Receive Data Input<br>Output of Capture/Compare<br>channel 1                                                          |  |

| P0.2   | 13            |      | PU             | EXF2_1<br>CTRAP_2<br>TDO_0<br>TXD_1                                                                                                                         | Timer 2 External Flag Output<br>CCU6 Trap Input<br>JTAG Serial Data Output<br>UART Transmit Data Output/<br>Clock Output   |  |

| P0.3   | 2             |      | Hi-Z           | SCK_1<br>COUT63_1                                                                                                                                           | SSC Clock Input/Output<br>Output of Capture/Compare<br>channel 3                                                           |  |

| P0.4   | 3             |      | Hi-Z           | MTSR_1<br>CC62_1                                                                                                                                            | SSC Master Transmit Output/<br>Slave Receive Input<br>Input/Output of Capture/Compare<br>channel 2                         |  |

| P0.5   | 4             |      | Hi-Z           | MRST_1<br>EXINT0_0<br>COUT62_1                                                                                                                              | SSC Master Receive Input/<br>Slave Transmit Output<br>External Interrupt Input 0<br>Output of Capture/Compare<br>channel 2 |  |

# XC866

# **General Device Information**

| Table 3 | Pin Definitions and Functions (cont'd) |      |                |                                                                                                                                                                                                           |                                                                                              |  |  |

|---------|----------------------------------------|------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--|--|

| Symbol  | Pin<br>Number                          | Туре | Reset<br>State | Function                                                                                                                                                                                                  |                                                                                              |  |  |

| P2      |                                        | I    |                | <b>Port 2</b><br>Port 2 is an 8-bit general purpose input-only port. It can be used as alternate functions for the digital inputs of the JTAG and CCU6. It is also used as the analog inputs for the ADC. |                                                                                              |  |  |

| P2.0    | 15                                     |      | Hi-Z           | EXINT1<br>T12HR_2                                                                                                                                                                                         | CCU6 Hall Input 0<br>External Interrupt Input 1<br>CCU6 Timer 12 Hardware Run<br>Input       |  |  |

|         |                                        |      |                | TCK_1<br>CC61_3<br>AN0                                                                                                                                                                                    | JTAG Clock Input<br>Input of Capture/Compare channel 1<br>Analog Input 0                     |  |  |

| P2.1    | 16                                     |      | Hi-Z           | CCPOS1_0<br>EXINT2<br>T13HR_2                                                                                                                                                                             | CCU6 Hall Input 1<br>External Interrupt Input 2<br>CCU6 Timer 13 Hardware Run<br>Input       |  |  |

|         |                                        |      |                | TDI_1<br>CC62_3<br>AN1                                                                                                                                                                                    | JTAG Serial Data Input<br>Input of Capture/Compare channel 2<br>Analog Input 1               |  |  |

| P2.2    | 17                                     |      | Hi-Z           | CCPOS2_0<br>CTRAP_1<br>CC60_3<br>AN2                                                                                                                                                                      | CCU6 Hall Input 2<br>CCU6 Trap Input<br>Input of Capture/Compare channel 0<br>Analog Input 2 |  |  |

| P2.3    | 20                                     |      | Hi-Z           | AN3                                                                                                                                                                                                       | Analog Input 3                                                                               |  |  |

| P2.4    | 21                                     |      | Hi-Z           | AN4                                                                                                                                                                                                       | Analog Input 4                                                                               |  |  |

| P2.5    | 22                                     |      | Hi-Z           | AN5                                                                                                                                                                                                       | Analog Input 5                                                                               |  |  |

| P2.6    | 23                                     |      | Hi-Z           | AN6                                                                                                                                                                                                       | Analog Input 6                                                                               |  |  |

| P2.7    | 26                                     |      | Hi-Z           | AN7                                                                                                                                                                                                       | Analog Input 7                                                                               |  |  |

# 3 Functional Description

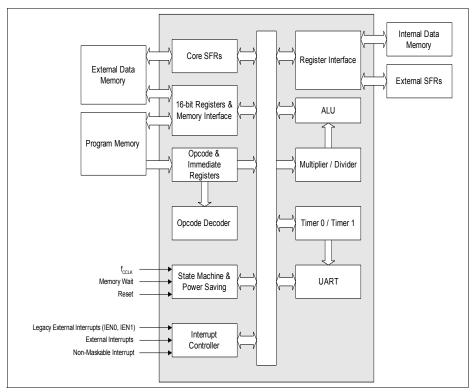

# 3.1 Processor Architecture

The XC866 is based on a high-performance 8-bit Central Processing Unit (CPU) that is compatible with the standard 8051 processor. While the standard 8051 processor is designed around a 12-clock machine cycle, the XC866 CPU uses a 2-clock machine cycle. This allows fast access to ROM or RAM memories without wait state. Access to the Flash memory, however, requires an additional wait state (one machine cycle). The instruction set consists of 45% one-byte, 41% two-byte and 14% three-byte instructions.

The XC866 CPU provides a range of debugging features, including basic stop/start, single-step execution, breakpoint support and read/write access to the data memory, program memory and SFRs.

Figure 5 shows the CPU functional blocks.

Figure 5 CPU Block Diagram

# 3.2.1 Memory Protection Strategy

The XC866 memory protection strategy includes:

- Read-out protection: The Flash Memory can be enabled for read-out protection and ROM memory is always protected.

- Program and erase protection: The Flash memory in all devices can be enabled for program and erase protection.

Flash memory protection is available in two modes:

- Mode 0: Only the P-Flash is protected; the D-Flash is unprotected

- · Mode 1: Both the P-Flash and D-Flash are protected

The selection of each protection mode and the restrictions imposed are summarized in **Table 4**.

| Mode                            | 0                                                                                                                    | 1                                              |  |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------|------------------------------------------------|--|

| Activation                      | Program a valid password via BSL m                                                                                   | node 6                                         |  |

| Selection                       | MSB of password = 0                                                                                                  | MSB of password = 1                            |  |

| P-Flash contents can be read by |                                                                                                                      |                                                |  |

| P-Flash program and erase       | Not possible                                                                                                         | Not possible                                   |  |

| D-Flash contents can be read by | Read instructions in any program memory                                                                              | Read instructions in the<br>P-Flash or D-Flash |  |

| D-Flash program                 | Possible                                                                                                             | Not possible                                   |  |

| D-Flash erase                   | Possible, on the condition that bit<br>DFLASHEN in register MISC_CON<br>is set to 1 prior to each erase<br>operation | Not possible                                   |  |

#### Table 4 Flash Protection Modes

BSL mode 6, which is used for enabling Flash protection, can also be used for disabling Flash protection. Here, the programmed password must be provided by the user. A password match triggers an automatic erase of the read-protected Flash contents, see **Table 5** and **Table 6**, and the programmed password is erased. The Flash protection is then disabled upon the next reset.

#### For XC866-2FR and XC866-4FR devices:

The selection of protection type is summarized in Table 5.

#### Table 5 Flash Protection Type for XC866-2FR and XC866-4FR devices

| PASSWORD              | Type of Protection      | Flash Banks to Erase when<br>Unprotected |

|-----------------------|-------------------------|------------------------------------------|

| 1XXXXXXX <sub>B</sub> | Flash Protection Mode 1 | All Banks                                |

| 0XXXXXXAB             | Flash Protection Mode 0 | P-Flash Bank                             |

#### For XC866-1FR device and ROM devices:

The selection of protection type is summarized in Table 6.

#### Table 6 Flash Protection Type for XC866-1FR device and ROM devices

| PASSWORD              | Type of Protection<br>(Applicable to the<br>whole Flash) | Sectors to Erase when Unprotected | Comments                           |

|-----------------------|----------------------------------------------------------|-----------------------------------|------------------------------------|

| 1XXXXXX <sub>B</sub>  | Read/Program/Erase                                       | All Sectors                       | Compatible to<br>Protection mode 1 |

| 00001XXX <sub>B</sub> | Erase                                                    | Sector 0                          |                                    |

| 00010XXX <sub>B</sub> | Erase                                                    | Sector 0 and 1                    |                                    |

| 00011XXX <sub>B</sub> | Erase                                                    | Sector 0 to 2                     |                                    |

| 00100XXX <sub>B</sub> | Erase                                                    | Sector 0 to 3                     |                                    |

| 00101XXX <sub>B</sub> | Erase                                                    | Sector 0 to 4                     |                                    |

| 00110XXX <sub>B</sub> | Erase                                                    | Sector 0 to 5                     |                                    |

| 00111XXX <sub>B</sub> | Erase                                                    | Sector 0 to 6                     |                                    |

| 01000XXX <sub>B</sub> | Erase                                                    | Sector 0 to 7                     |                                    |

| 01001XXX <sub>B</sub> | Erase                                                    | Sector 0 to 8                     |                                    |

| 01010XXX <sub>B</sub> | Erase                                                    | All Sectors                       |                                    |

| Others                | Erase                                                    | None                              |                                    |

Although no protection scheme can be considered infallible, the XC866 memory protection strategy provides a very high level of protection for a general purpose microcontroller.

# 3.2.3 Bit Protection Scheme

The bit protection scheme prevents direct software writing of selected bits (i.e., protected bits) using the PASSWD register. When the bit field MODE is  $11_B$ , writing  $10011_B$  to the bit field PASS opens access to writing of all protected bits, and writing  $10101_B$  to the bit field PASS closes access to writing of all protected bits. In both cases, the value of the bit field MODE is not changed even if PASSWD register is written with  $98_H$  or  $A8_H$ . It can only be changed when bit field PASS is written with  $11000_B$ , for example, writing D0<sub>H</sub> to PASSWD register disables the bit protection scheme.

The access is opened for maximum 32 CCLKs if the "close access" password is not written. If "open access" password is written again before the end of 32 CCLK cycles, there will be a recount of 32 CCLK cycles. The protected bits include NDIV, WDTEN, PD, and SD.

#### PASSWD Password Register

Reset Value: 07<sub>H</sub>

| 7 | 6 | 5    | 4 | 3 | 2       | 1  | 0  |

|---|---|------|---|---|---------|----|----|

|   |   | PASS |   |   | PROTECT | МС | DE |

|   | 1 | w    |   |   | rh      | r  | w  |

| Field     | Bits  | Туре | Description                                                                                                                                                                                                                                                                                         |

|-----------|-------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MODE      | [1:0] | rw   | Bit Protection Scheme Control bits $00$ Scheme Disabled $11$ Scheme Enabled (default)Others: Scheme EnabledThese two bits cannot be written directly. To changethe value between $11_B$ and $00_B$ , the bit field PASSmust be written with $11000_B$ ; only then, will theMODE[1:0] be registered. |

| PROTECT_S | 2     | rh   | <ul> <li>Bit Protection Signal Status bit</li> <li>This bit shows the status of the protection.</li> <li>0 Software is able to write to all protected bits.</li> <li>1 Software is unable to write to any protected bits.</li> </ul>                                                                |

| PASS      | [7:3] | w    | Password bitsThe Bit Protection Scheme only recognizes threepatterns.11000BEnables writing of the bit field MODE.10011BOpens access to writing of all protected bits.10101BCloses access to writing of all protected bits.                                                                          |

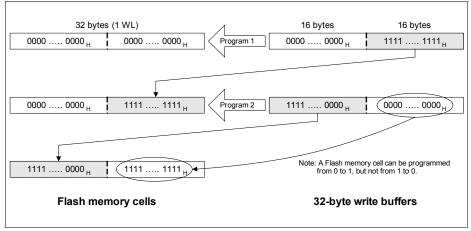

# 3.3.2 Flash Programming Width

For the P-Flash banks, a programmed wordline (WL) must be erased before it can be reprogrammed as the Flash cells can only withstand one gate disturb. This means that the entire sector containing the WL must be erased since it is impossible to erase a single WL.

For the D-Flash bank, the same WL can be programmed twice before erasing is required as the Flash cells are able to withstand two gate disturbs. Hence, it is possible to program the same WL, for example, with 16 bytes of data in two times (see Figure 12).

#### Figure 12 D-Flash Programming

Note: When programming a D-Flash WL the second time, the previously programmed Flash memory cells (whether 0s or 1s) should be reprogrammed with 0s to retain its original contents and to prevent "over-programming".

# XC866

#### **Functional Description**

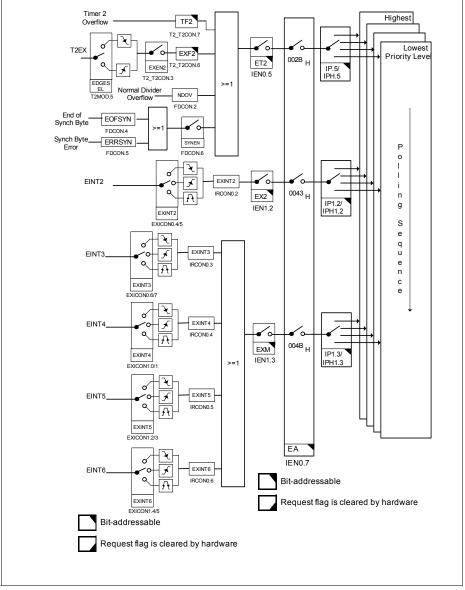

Figure 15 Interrupt Request Sources (Part 2)

# 3.5 Parallel Ports

The XC866 has 27 port pins organized into four parallel ports, Port 0 (P0) to Port 3 (P3). Each pin has a pair of internal pull-up and pull-down devices that can be individually enabled or disabled. Ports P0, P1 and P3 are bidirectional and can be used as general purpose input/output (GPIO) or to perform alternate input/output functions for the on-chip peripherals. When configured as an output, the open drain mode can be selected. Port P2 is an input-only port, providing general purpose input functions, alternate input functions for the on-chip peripherals, and also analog inputs for the Analog-to-Digital Converter (ADC).

#### **Bidirectional Port Features:**

- Configurable pin direction

- Configurable pull-up/pull-down devices

- · Configurable open drain mode

- Transfer of data through digital inputs and outputs (general purpose I/O)

- Alternate input/output for on-chip peripherals

#### Input Port Features:

- · Configurable input driver

- Configurable pull-up/pull-down devices

- Receive of data through digital input (general purpose input)

- · Alternate input for on-chip peripherals

- · Analog input for ADC module

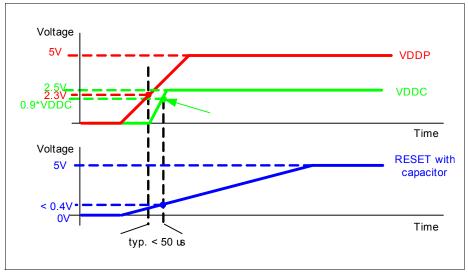

# Figure 22 V<sub>DDP</sub>, V<sub>DDC</sub> and V<sub>RESET</sub> during Power-on Reset

The second type of reset in XC866 is the hardware reset. This reset function can be used <u>during</u> normal operation or when the chip is in power-down mode. A reset input pin RESET is provided for the hardware reset. To ensure the recognition of the hardware reset, pin RESET must be held low for at least 100 ns.

The Watchdog Timer (WDT) module is also capable of resetting the device if it detects a malfunction in the system.

Another type of reset that needs to be detected is a reset while the device is in power-down mode (wake-up reset). While the contents of the static RAM are undefined after a power-on reset, they are well defined after a wake-up reset from power-down mode.

# 3.7.1 Module Reset Behavior

Table 19 shows how the functions of the XC866 are affected by the various reset types. A "∎" means that this function is reset to its default state.

| Module/<br>Function   | Wake-Up<br>Reset                     | Watchdog<br>Reset      | Hardware<br>Reset      | Power-On<br>Reset         | Brownout<br>Reset         |

|-----------------------|--------------------------------------|------------------------|------------------------|---------------------------|---------------------------|

| CPU Core              |                                      |                        |                        |                           |                           |

| Peripherals           |                                      |                        |                        |                           |                           |

| On-Chip<br>Static RAM | Not affected, reliable               | Not affected, reliable | Not affected, reliable | Affected, un-<br>reliable | Affected, un-<br>reliable |

| Oscillator,<br>PLL    |                                      | Not affected           |                        |                           |                           |

| Port Pins             |                                      |                        |                        |                           |                           |

| EVR                   | The voltage regulator is switched on | Not affected           |                        |                           |                           |

| FLASH                 |                                      |                        |                        |                           |                           |

| NMI                   | Disabled                             | Disabled               |                        |                           |                           |

Table 19 Effect of Reset on Device Functions

# 3.7.2 Booting Scheme

When the XC866 is reset, it must identify the type of configuration with which to start the different modes once the reset sequence is complete. Thus, boot configuration information that is required for activation of special modes and conditions needs to be applied by the external world through input pins. After power-on reset or hardware reset, the pins MBC, TMS and P0.0 collectively select the different boot options. Table 20 shows the available boot options in the XC866.

| MBC | TMS | P0.0 | Type of Mode                                                                      | PC Start Value    |

|-----|-----|------|-----------------------------------------------------------------------------------|-------------------|

| 1   | 0   | х    | User Mode; on-chip OSC/PLL non-bypassed                                           | 0000 <sub>H</sub> |

| 0   | 0   | х    | BSL Mode; on-chip OSC/PLL non-bypassed                                            | 0000 <sub>H</sub> |

| 0   | 1   | 0    | OCDS Mode <sup>1)</sup> ; on-chip OSC/PLL non-<br>bypassed                        | 0000 <sub>H</sub> |

| 1   | 1   | 0    | Standalone User (JTAG) Mode <sup>2)</sup> ; on-chip OSC/PLL non-bypassed (normal) | 0000 <sub>H</sub> |

Table 20 XC866 Boot Selection

<sup>1)</sup> The OCDS mode is not accessible if Flash is protected.

<sup>2)</sup> Normal user mode with standard JTAG (TCK,TDI,TDO) pins for hot-attach purpose.

For power saving purposes, the clocks may be disabled or slowed down according to **Table 23**.

# Table 23System frequency (f<sub>sys</sub> = 80 MHz)

| Power Saving Mode | Action                                                                                                                                    |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Idle              | Clock to the CPU is disabled.                                                                                                             |

| Slow-down         | Clocks to the CPU and all the peripherals, including CCU6, are divided by a common programmable factor defined by bit field CMCON.CLKREL. |

| Power-down        | Oscillator and PLL are switched off.                                                                                                      |

8-bit reload value (BR\_VALUE) for the baud rate timer defined by register BG

The following formulas calculate the final baud rate without and with the fractional divider respectively:

baud rate =

$$\frac{f_{PCLK}}{16 \times 2^{BRPRE} \times (BR \text{ VALUE} + 1)}$$

where  $2^{BRPRE} \times (BR_VALUE + 1) > 1$

baud rate =

$$\frac{f_{PCLK}}{16 \times 2^{BRPRE} \times (BR VALUE + 1)} \times \frac{STEP}{256}$$

The maximum baud rate that can be generated is limited to  $f_{PCLK}/32$ . Hence, for a module clock of 26.7 MHz, the maximum achievable baud rate is 0.83 MBaud.

Standard LIN protocal can support a maximum baud rate of 20kHz, the baud rate accuracy is not critical and the fractional divider can be disabled. Only the prescaler is used for auto baud rate calculation. For LIN fast mode, which supports the baud rate of 20kHz to 115.2kHz, the higher baud rates require the use of the fractional divider for greater accuracy.

**Table 26** lists the various commonly used baud rates with their corresponding parameter settings and deviation errors. The fractional divider is disabled and a module clock of 26.7 MHz is used.

| Baud rate  | Prescaling Factor<br>(2 <sup>BRPRE</sup> ) | Reload Value<br>(BR_VALUE + 1) | Deviation Error |

|------------|--------------------------------------------|--------------------------------|-----------------|

| 19.2 kBaud | 1 (BRPRE=000 <sub>B</sub> )                | 87 (57 <sub>H</sub> )          | -0.22 %         |

| 9600 Baud  | 1 (BRPRE=000 <sub>B</sub> )                | 174 (AE <sub>H</sub> )         | -0.22 %         |

| 4800 Baud  | 2 (BRPRE=001 <sub>B</sub> )                | 174 (AE <sub>H</sub> )         | -0.22 %         |

| 2400 Baud  | 4 (BRPRE=010 <sub>B</sub> )                | 174 (AE <sub>H</sub> )         | -0.22 %         |

| Table 26 | Typical Baud rates for UART with Fractional Divider disabled |

|----------|--------------------------------------------------------------|

|----------|--------------------------------------------------------------|

The fractional divider allows baud rates of higher accuracy (lower deviation error) to be generated. Table 27 lists the resulting deviation errors from generating a baud rate of

# 3.13 LIN Protocol

The UART can be used to support the Local Interconnect Network (LIN) protocol for both master and slave operations. The LIN baud rate detection feature provides the capability to detect the baud rate within LIN protocol using Timer 2. This allows the UART to be synchronized to the LIN baud rate for data transmission and reception.

LIN is a holistic communication concept for local interconnected networks in vehicles. The communication is based on the SCI (UART) data format, a single-master/multipleslave concept, a clock synchronization for nodes without stabilized time base. An attractive feature of LIN is self-synchronization of the slave nodes without a crystal or ceramic resonator, which significantly reduces the cost of hardware platform. Hence, the baud rate must be calculated and returned with every message frame.

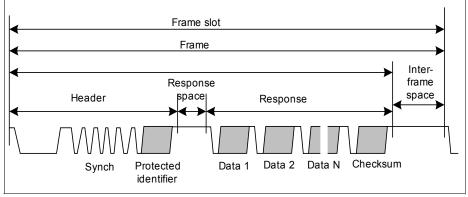

The structure of a LIN frame is shown in Figure 30. The frame consists of the:

- header, which comprises a Break (13-bit time low), Synch Byte (55<sub>H</sub>), and ID field

- response time

- data bytes (according to UART protocol)

- checksum

Figure 30 Structure of LIN Frame

# 3.13.1 LIN Header Transmission

LIN header transmission is only applicable in master mode. In the LIN communication, a master task decides when and which frame is to be transferred on the bus. It also identifies a slave task to provide the data transported by each frame. The information needed for the handshaking between the master and slave tasks is provided by the master task through the header portion of the frame.

The header consists of a break and synch pattern followed by an identifier. Among these three fields, only the break pattern cannot be transmitted as a normal 8-bit UART data.

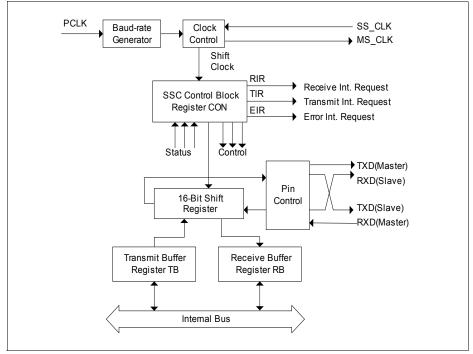

Data is transmitted or received on lines TXD and RXD, which are normally connected to the pins MTSR (Master Transmit/Slave Receive) and MRST (Master Receive/Slave Transmit). The clock signal is output via line MS\_CLK (Master Serial Shift Clock) or input via line SS\_CLK (Slave Serial Shift Clock). Both lines are normally connected to the pin SCLK. Transmission and reception of data are double-buffered.

Figure 31 shows the block diagram of the SSC.

Figure 31 SSC Block Diagram

# XC866

# **Functional Description**

#### Table 31JTAG ID Summary

| ROM | XC866L-4RR | 1013 9083 <sub>H</sub> |

|-----|------------|------------------------|

|     | XC866-4RR  | 1013 9083 <sub>H</sub> |

|     | XC866L-2RR | 1013 9083 <sub>H</sub> |

|     | XC866-2RR  | 1013 9083 <sub>H</sub> |

# 3.20 Identification Register

The XC866 identity register is located at Page 1 of address B3<sub>H</sub>.

#### ID Identity Register

#### Reset Value: 0000 0010<sub>B</sub>

| 7 | 6 | 5      | 4 | 3     | 2 | 1        | 0 |

|---|---|--------|---|-------|---|----------|---|

|   |   | PRODID |   | VERID | I |          |   |

|   | I | r      | I |       | r | <u> </u> |   |

| Field  | Bits  | Туре | Description                      |

|--------|-------|------|----------------------------------|

| VERID  | [2:0] | r    | Version ID<br>010 <sub>B</sub>   |

| PRODID | [7:3] | r    | Product ID<br>00000 <sub>B</sub> |

#### **Electrical Parameters**

# 4.2.3 ADC Characteristics

The values in the table below are given for an analog power supply between 4.5 V to 5.5 V. The ADC can be used with an analog power supply down to 3 V. But in this case, the analog parameters may show a reduced performance. All ground pins ( $V_{SS}$ ) must be externally connected to one single star point in the system. The voltage difference between the ground pins must not exceed 200mV.

| Parameter                                                    | Symbol            |           | Limit Values                            |                  |                            | Unit | Test Conditions/                       |

|--------------------------------------------------------------|-------------------|-----------|-----------------------------------------|------------------|----------------------------|------|----------------------------------------|

|                                                              |                   |           |                                         | typ .            | max.                       | 1    | Remarks                                |

| Analog reference voltage                                     | VARE              | F<br>SR   | V <sub>AGND</sub><br>+ 1                | V <sub>DDP</sub> | V <sub>DDP</sub><br>+ 0.05 | V    |                                        |

| Analog reference<br>ground                                   | VAGN              | D<br>SR   | V <sub>SS</sub><br>- 0.05               | V <sub>SS</sub>  | V <sub>AREF</sub><br>- 1   | V    |                                        |

| Analog input<br>voltage range                                | V <sub>AIN</sub>  | SR        | V <sub>AGND</sub>                       | -                | VAREF                      | V    |                                        |

| ADC clocks                                                   | $f_{ADC}$         |           | -                                       | 20               | 40                         | MHz  | module clock                           |

|                                                              | f <sub>ADCI</sub> |           | -                                       | -                | 10                         | MHz  | internal analog clock<br>See Figure 33 |

| Sample time                                                  | t <sub>S</sub>    | СС        | (2 + INPCR0.STC) ×<br>t <sub>ADCI</sub> |                  |                            | μs   |                                        |

| Conversion time                                              | t <sub>C</sub>    | СС        | See Section 4.2.3.1                     |                  |                            | μs   |                                        |

| Total unadjusted                                             | TUE <sup>1</sup>  | )CC       | -                                       | -                | ±1                         | LSB  | 8-bit conversion. <sup>2)</sup>        |

| error                                                        |                   |           | -                                       | -                | ±2                         | LSB  | 10-bit conversion.                     |

| Differential<br>Nonlinearity                                 | DNL               | СС        | -                                       | ±1               | -                          | LSB  | 10-bit conversion <sup>2)</sup>        |

| Integral<br>Nonlinearity                                     | INL               | СС        | -                                       | ±1               | -                          | LSB  | 10-bit conversion <sup>2)</sup>        |

| Offset                                                       | OFF               | CC        | -                                       | ±1               | -                          | LSB  | 10-bit conversion <sup>2)</sup>        |

| Gain                                                         | GAIN              | CC        | -                                       | ±1               | -                          | LSB  | 10-bit conversion <sup>2)</sup>        |

| Switched<br>capacitance at the<br>reference voltage<br>input | C <sub>ARE</sub>  | FSW<br>CC | -                                       | 10               | 20                         | pF   | 2)3)                                   |

### Table 36ADC Characteristics (Operating Conditions apply; $V_{DDP}$ = 5V Range)

#### **Electrical Parameters**

#### Table 36ADC Characteristics (Operating Conditions apply; $V_{DDP}$ = 5V Range)

| Parameter                                                  | Symbol                   | Limit Values |           |     | Unit | Test Conditions/ |

|------------------------------------------------------------|--------------------------|--------------|-----------|-----|------|------------------|

|                                                            |                          | min.         | typ. max. |     |      | Remarks          |

| Switched<br>capacitance at the<br>analog voltage<br>inputs | C <sub>AINSW</sub><br>CC | _            | 5         | 7   | pF   | 2)4)             |

| Input resistance of the reference input                    | R <sub>AREF</sub> CC     | -            | 1         | 2   | kΩ   | 2)               |

| Input resistance of the selected analog channel            | R <sub>AIN</sub> CC      | -            | 1         | 1.5 | kΩ   | 2)               |

<sup>1)</sup> TUE is tested at  $V_{AREF}$  = 5.0 V,  $V_{AGND}$  = 0 V ,  $V_{DDP}$  = 5.0 V.

<sup>2)</sup> Not subject to production test, verified by design/characterization.

<sup>&</sup>lt;sup>3)</sup> This represents an equivalent switched capacitance. This capacitance is not switched to the reference voltage at once. Instead of this, smaller capacitances are successively switched to the reference voltage.

<sup>&</sup>lt;sup>4)</sup> The sampling capacity of the conversion C-Network is pre-charged to V<sub>AREF</sub>/2 before connecting the input to the C-Network. Because of the parasitic elements, the voltage measured at ANx is lower than V<sub>AREF</sub>/2.