Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                      |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | XC800                                                                         |

| Core Size                  | 8-Bit                                                                         |

| Speed                      | 86MHz                                                                         |

| Connectivity               | LINbus, SSI, UART/USART                                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                         |

| Number of I/O              | 19                                                                            |

| Program Memory Size        | 8KB (8K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 768 x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                   |

| Data Converters            | A/D 8x10b                                                                     |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 38-TFSOP (0.173", 4.40mm Width)                                               |

| Supplier Device Package    | PG-TSSOP-38                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/saf-xc866l-2fri-bc |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Summary of Features**

#### **XC866 Variant Devices**

The XC866 product family features devices with different configurations and program memory sizes, temperature and quality profiles (Automotive or Industrial), offering cost-effective solution for different application requirements.

The configuration of LIN BSL for XC866 devices are summarized in Table 1.

| Table 1 | Device Configuration for LIN BSL |

|---------|----------------------------------|

|---------|----------------------------------|

| Device Name | LIN BSL Support |

|-------------|-----------------|

| XC866       | No              |

| XC866L      | Yes             |

The list of XC866 devices and their differences are summarized in Table 2.

| Device<br>Type      | Device Name        | Power<br>Supply<br>(V) | P-Flash<br>Size<br>(Kbytes) | D-Flash<br>Size<br>(Kbytes) | ROM<br>Size<br>(Kbytes) | Quality<br>Profile <sup>1)</sup> |

|---------------------|--------------------|------------------------|-----------------------------|-----------------------------|-------------------------|----------------------------------|

| Flash <sup>2)</sup> | SAK-XC866*-4FRA    | 5.0                    | 12                          | 4                           | _                       | Automotive                       |

|                     | SAK-XC866*-4FRI    | 5.0                    | 12                          | 4                           | -                       | Industrial                       |

|                     | SAK-XC866*-2FRA    | 5.0                    | 4                           | 4                           | -                       | Automotive                       |

|                     | SAK-XC866*-2FRI    | 5.0                    | 4                           | 4                           | -                       | Industrial                       |

|                     | SAK-XC866*-1FRA    | 5.0                    | _                           | 4                           | -                       | Automotive                       |

|                     | SAK-XC866*-1FRI    | 5.0                    | -                           | 4                           | _                       | Industrial                       |

|                     | SAF-XC866*-4FRA    | 5.0                    | 12                          | 4                           | -                       | Automotive                       |

|                     | SAF-XC866*-4FRI    | 5.0                    | 12                          | 4                           | -                       | Industrial                       |

|                     | SAF-XC866*-2FRA    | 5.0                    | 4                           | 4                           | _                       | Automotive                       |

|                     | SAF-XC866*-2FRI    | 5.0                    | 4                           | 4                           | -                       | Industrial                       |

|                     | SAF-XC866*-1FRA    | 5.0                    | _                           | 4                           | -                       | Automotive                       |

|                     | SAF-XC866*-1FRI    | 5.0                    | _                           | 4                           | -                       | Industrial                       |

|                     | SAK-XC866*-4FRA 3V | 3.3                    | 12                          | 4                           | -                       | Automotive                       |

|                     | SAK-XC866*-4FRI 3V | 3.3                    | 12                          | 4                           | -                       | Industrial                       |

|                     | SAK-XC866*-2FRA 3V | 3.3                    | 4                           | 4                           | _                       | Automotive                       |

|                     | SAK-XC866*-2FRI 3V | 3.3                    | 4                           | 4                           | -                       | Industrial                       |

|                     | SAK-XC866*-1FRA 3V | 3.3                    | -                           | 4                           | _                       | Automotive                       |

#### Table 2 Device Summary

# infineon

#### **Summary of Features**

#### Table 2Device Summary

|     | -                  |     |    |   |    |            |

|-----|--------------------|-----|----|---|----|------------|

|     | SAK-XC866*-1FRI 3V | 3.3 | -  | 4 | -  | Industrial |

|     | SAF-XC866*-4FRA 3V | 3.3 | 12 | 4 | _  | Automotive |

|     | SAF-XC866*-4FRI 3V | 3.3 | 12 | 4 | _  | Industrial |

|     | SAF-XC866*-2FRA 3V | 3.3 | 4  | 4 | _  | Automotive |

|     | SAF-XC866*-2FRI 3V | 3.3 | 4  | 4 | -  | Industrial |

|     | SAF-XC866*-1FRA 3V | 3.3 | -  | 4 | -  | Automotive |

|     | SAF-XC866*-1FRI 3V | 3.3 | -  | 4 | -  | Industrial |

| ROM | SAK-XC866*-4RRA    | 5.0 | -  | 4 | 16 | Automotive |

|     | SAK-XC866*-4RRI    | 5.0 | -  | 4 | 16 | Industrial |

|     | SAK-XC866*-2RRA    | 5.0 | -  | 4 | 8  | Automotive |

|     | SAK-XC866*-2RRI    | 5.0 | -  | 4 | 8  | Industrial |

|     | SAF-XC866*-4RRA    | 5.0 | -  | 4 | 16 | Automotive |

|     | SAF-XC866*-4RRI    | 5.0 | -  | 4 | 16 | Industrial |

|     | SAF-XC866*-2RRA    | 5.0 | _  | 4 | 8  | Automotive |

|     | SAF-XC866*-2RRI    | 5.0 | -  | 4 | 8  | Industrial |

|     | SAK-XC866*-4RRA 3V | 3.3 | -  | 4 | 16 | Automotive |

|     | SAK-XC866*-4RRI 3V | 3.3 | -  | 4 | 16 | Industrial |

|     | SAK-XC866*-2RRA 3V | 3.3 | -  | 4 | 8  | Automotive |

|     | SAK-XC866*-2RRI 3V | 3.3 | _  | 4 | 8  | Industrial |

|     | SAF-XC866*-4RRA 3V | 3.3 | -  | 4 | 16 | Automotive |

|     | SAF-XC866*-4RRI 3V | 3.3 | -  | 4 | 16 | Industrial |

|     | SAF-XC866*-2RRA 3V | 3.3 | -  | 4 | 8  | Automotive |

|     | SAF-XC866*-2RRI 3V | 3.3 | -  | 4 | 8  | Industrial |

1) Industrial is not for Automotive usage

<sup>2)</sup> The flash memory (P-Flash and D-Flash) can be used for code or data.

Note: The asterisk (\*) above denotes the device configuration letters from Table 1.

#### **General Device Information**

## 2 General Device Information

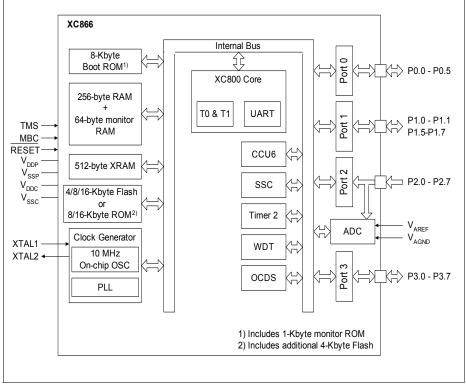

## 2.1 Block Diagram

İnfineon

Figure 2 XC866 Block Diagram

#### **General Device Information**

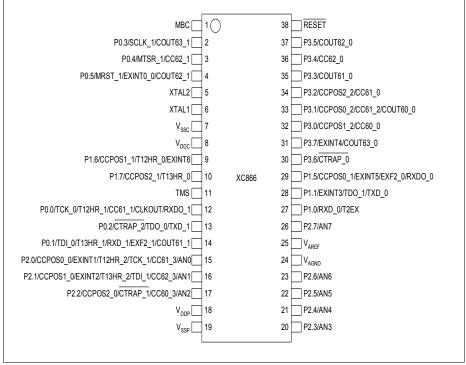

## 2.3 Pin Configuration

Figure 4 XC866 Pin Configuration, PG-TSSOP-38 Package (top view)

| Field | Bits  | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------|-------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OP    | [7:6] | w    | <ul> <li>Operation</li> <li>OX Manual page mode. The value of STNR is ignored and PAGE is directly written.</li> <li>10 New page programming with automatic page saving. The value written to the bit positions of PAGE is stored. In parallel, the previous contents of PAGE are saved in the storage bit field STx indicated by STNR.</li> <li>11 Automatic restore page action. The value written to the bit positions PAGE is ignored and instead, PAGE is overwritten by the contents of the storage bit field STx indicated by STNR.</li> </ul> |

| 0     | 3     | r    | <b>Reserved</b><br>Returns 0 if read; should be written with 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

## XC866

#### **Functional Description**

The Port SFRs can be accessed in the standard memory area (RMAP = 0).

#### Table 10 Port Register Overview

| Addr            | Register Name                        |                        | Bit               | 7   | 6       | 5        | 4        | 3        | 2        | 1        | 0        |

|-----------------|--------------------------------------|------------------------|-------------------|-----|---------|----------|----------|----------|----------|----------|----------|

| RMAP =          | -                                    |                        |                   | -   | -       | -        | -        | -        | _        | -        | -        |

| B2 <sub>H</sub> | PORT PAGE                            | Reset: 00 <sub>H</sub> | Bit Field         | C   | P       | ST       | NR       | 0        |          | PAGE     |          |

| D-H             | Page Register for PORT               |                        | Туре              | -   | N       |          | N        | r        |          | rwh      |          |

| RMAP =          | 0, Page 0                            |                        | 1300              |     |         |          |          | •        |          |          |          |

| 80 <sub>H</sub> | P0_DATA                              | Reset: 00 <sub>H</sub> | Bit Field         |     | 0       | P5       | P4       | P3       | P2       | P1       | P0       |

| ССH             | P0 Data Register                     | Hessell oog            | Туре              |     | r       | rwh      | rwh      | rwh      | rwh      | rwh      | rwh      |

| 86 <sub>H</sub> | P0 DIR                               | Reset: 00 <sub>H</sub> | Bit Field         |     | 0       | P5       | P4       | P3       | P2       | P1       | P0       |

| OOH             | P0 Direction Register                | Hessell oog            | Туре              |     | r       | rw       | rw       | rw       | rw       | rw       | rw       |

| 90 <sub>H</sub> | P1 DATA                              | Reset: 00 <sub>H</sub> | Bit Field         | P7  | P6      | P5       |          | 0        |          | P1       | P0       |

| чч              | P1 Data Register                     | Hessell oog            | Туре              | rwh | rwh     | rwh      |          | r        |          | rwh      | rwh      |

| 91 <sub>H</sub> | P1 DIR                               | Reset: 00 <sub>H</sub> | Bit Field         | P7  | P6      | P5       |          | 0        |          | P1       | P0       |

| ЧH              | P1 Direction Register                | Hessell oog            | Туре              | rw  | rw      | rw       |          | r        |          | rw       | rw       |

| А0 <sub>н</sub> | P2 DATA                              | Reset: 00 <sub>H</sub> | Bit Field         | P7  | P6      | P5       | P4       | P3       | P2       | P1       | P0       |

| AVH             | P2 Data Register                     | Reset. Oug             | Туре              | rwh | rwh     | rwh      | rwh      | rwh      | rwh      | rwh      | rwh      |

| A1 <sub>H</sub> | P2 DIR                               | Reset: 00 <sub>H</sub> | Bit Field         | P7  | P6      | P5       | P4       | P3       | P2       | P1       | P0       |

| П               | P2 Direction Register                | Neset. Oug             | Туре              | rw  | rw      | rw       | rw       | rw       | rw       | rw       | rw       |

| В0 <sub>н</sub> | P3 DATA                              | Reset: 00 <sub>H</sub> | Bit Field         | P7  | P6      | P5       | P4       | P3       | P2       | P1       | P0       |

| BOH             | P3 Data Register                     | Reset. 00H             | Туре              | rwh | rwh     | rwh      | rwh      | rwh      | rwh      | rwh      | rwh      |

| D1              | P3 DIR                               | Reset: 00 <sub>H</sub> | Bit Field         | P7  | P6      | P5       | P4       | P3       | P2       | P1       | P0       |

| B1 <sub>H</sub> | P3 Direction Register                | Reset. 00H             |                   | rw  | rw      | rw       | r4       | rs<br>rw | rv       | rw       | rw       |

|                 | 0, Page 1                            |                        | Туре              | IW  | IW      | IW       | TW       | IW       | TW       | IW       | TW       |

|                 | P0 PUDSEL                            | Boost: EE              | Bit Field         |     | 0       | P5       | P4       | P3       | P2       | P1       | P0       |

| 80 <sub>H</sub> | P0_P0D3EL<br>P0 Pull-Up/Pull-Down Se | Reset: FF <sub>H</sub> |                   |     | -       | -        |          |          |          |          |          |

| 00              | P0 PUDEN                             |                        | Type<br>Bit Field |     | r<br>D  | rw<br>P5 | rw<br>P4 | rw<br>P3 | rw<br>P2 | rw<br>P1 | rw<br>P0 |

| 86 <sub>H</sub> | P0_P0DEN<br>P0 Pull-Up/Pull-Down Er  | Reset: C4 <sub>H</sub> |                   |     | -       |          |          |          |          |          |          |

| ~~              |                                      |                        | Type              |     | r<br>P6 | rw<br>P5 | rw       | rw       | rw       | rw<br>P1 | rw<br>P0 |

| 90 <sub>H</sub> | P1_PUDSEL<br>P1 Pull-Up/Pull-Down Se | Reset: FF <sub>H</sub> | Bit Field         | P7  |         | -        |          | 0        |          |          |          |

| 04              |                                      |                        | Type              | rw  | rw      | rw       |          | r        |          | rw       | rw       |

| 91 <sub>H</sub> | P1_PUDEN<br>P1 Pull-Up/Pull-Down Er  | Reset: FF <sub>H</sub> | Bit Field         | P7  | P6      | P5       |          | 0        |          | P1       | P0       |

| ••              |                                      |                        | Туре              | rw  | rw      | rw       | 54       | r        |          | rw       | rw       |

| A0 <sub>H</sub> | P2_PUDSEL<br>P2 Pull-Up/Pull-Down Se | Reset: FF <sub>H</sub> | Bit Field         | P7  | P6      | P5       | P4       | P3       | P2       | P1       | P0       |

|                 |                                      |                        | Туре              | rw  | rw      | rw       | rw       | rw       | rw       | rw       | rw       |

| A1 <sub>H</sub> | P2_PUDEN<br>P2 Pull-Up/Pull-Down Er  | Reset: 00 <sub>H</sub> | Bit Field         | P7  | P6      | P5       | P4       | P3       | P2       | P1       | P0       |

|                 |                                      |                        | Туре              | rw  | rw      | rw       | rw       | rw       | rw       | rw       | rw       |

| в0 <sub>Н</sub> | P3_PUDSEL<br>P3 Pull-Up/Pull-Down Se | Reset: BF <sub>H</sub> | Bit Field         | P7  | P6      | P5       | P4       | P3       | P2       | P1       | P0       |

| -               |                                      |                        | Туре              | rw  | rw      | rw       | rw       | rw       | rw       | rw       | rw       |

| B1 <sub>H</sub> | P3_PUDEN<br>P3 Pull-Up/Pull-Down Er  | Reset: 40 <sub>H</sub> | Bit Field         | P7  | P6      | P5       | P4       | P3       | P2       | P1       | P0       |

|                 | •                                    | iaule register         | Туре              | rw  | rw      | rw       | rw       | rw       | rw       | rw       | rw       |

|                 | 0, Page 2                            |                        | lava:             |     |         |          |          |          |          |          |          |

| 80 <sub>H</sub> | P0_ALTSEL0                           | Reset: 00 <sub>H</sub> | Bit Field         |     | 0       | P5       | P4       | P3       | P2       | P1       | P0       |

|                 | P0 Alternate Select 0 Re             | 0                      | Туре              |     | r       | rw       | rw       | rw       | rw       | rw       | rw       |

| 86 <sub>H</sub> | P0_ALTSEL1                           | Reset: 00 <sub>H</sub> | Bit Field         |     | 0       | P5       | P4       | P3       | P2       | P1       | P0       |

|                 | P0 Alternate Select 1 Re             | -                      | Туре              |     | r       | rw       | rw       | rw       | rw       | rw       | rw       |

| 90 <sub>H</sub> | P1_ALTSEL0                           | Reset: 00 <sub>H</sub> | Bit Field         | P7  | P6      | P5       |          | 0        |          | P1       | P0       |

|                 | P1 Alternate Select 0 Re             | 0                      | Туре              | rw  | rw      | rw       |          | r        |          | rw       | rw       |

| 91 <sub>H</sub> | P1_ALTSEL1                           | Reset: 00 <sub>H</sub> | Bit Field         | P7  | P6      | P5       |          | 0        |          | P1       | P0       |

|                 | P1 Alternate Select 1 Re             | gister                 | Туре              | rw  | rw      | rw       |          | r        |          | rw       | rw       |

| B0 <sub>H</sub> | P3_ALTSEL0                           | Reset: 00 <sub>H</sub> | Bit Field         | P7  | P6      | P5       | P4       | P3       | P2       | P1       | P0       |

|                 | P3 Alternate Select 0 Re             | gister                 | Туре              | rw  | rw      | rw       | rw       | rw       | rw       | rw       | rw       |

#### Table 11 ADC Register Overview (cont'd)

| Addr            | Register Name                         |                        | Bit       | 7     | 6       | 5   | 4     | 3        | 2    | 1    | 0         |

|-----------------|---------------------------------------|------------------------|-----------|-------|---------|-----|-------|----------|------|------|-----------|

| CA <sub>H</sub> | ADC_RESR0L                            | Reset: 00 <sub>H</sub> | Bit Field | RESU  | LT[1:0] | 0   | VF    | DRC      |      | CHNR | 1         |

|                 | Result Register 0 Low                 |                        | Туре      | r     | h       | r   | rh    | rh       |      | rh   |           |

| CB <sub>H</sub> | ADC_RESR0H                            | Reset: 00 <sub>H</sub> | Bit Field |       |         |     | RESU  | LT[9:2]  | 1    |      |           |

|                 | Result Register 0 High                |                        | Туре      |       |         |     | r     | ħ        |      |      |           |

| ССн             | ADC_RESR1L                            | Reset: 00 <sub>H</sub> | Bit Field | RESU  | LT[1:0] | 0   | VF    | DRC      |      | CHNR |           |

|                 | Result Register 1 Low                 |                        | Туре      | r     | h       | r   | rh    | rh       |      | rh   |           |

| CD <sub>H</sub> | ADC_RESR1H                            | Reset: 00 <sub>H</sub> | Bit Field |       |         |     | RESU  | LT[9:2]  | 1    |      |           |

|                 | Result Register 1 High                |                        | Туре      |       |         |     | r     | h i      |      |      |           |

| CEH             | ADC_RESR2L                            | Reset: 00 <sub>H</sub> | Bit Field | RESU  | LT[1:0] | 0   | VF    | DRC      |      | CHNR |           |

|                 | Result Register 2 Low                 |                        | Туре      | r     | h       | r   | rh    | rh       |      | rh   |           |

| CF <sub>H</sub> | ADC_RESR2H                            | Reset: 00 <sub>H</sub> | Bit Field |       |         |     | RESU  | LT[9:2]  |      |      |           |

|                 | Result Register 2 High                |                        | Туре      |       |         |     | r     | ħ        |      |      |           |

| D2 <sub>H</sub> | ADC_RESR3L                            | Reset: 00 <sub>H</sub> | Bit Field | RESU  | LT[1:0] | 0   | VF    | DRC      |      | CHNR |           |

|                 | Result Register 3 Low                 |                        | Туре      | r     | h       | r   | rh    | rh       |      | rh   |           |

| D3 <sub>H</sub> | ADC_RESR3H                            | Reset: 00 <sub>H</sub> | Bit Field |       |         |     | RESU  | LT[9:2]  | 1    |      |           |

|                 | Result Register 3 High                |                        | Туре      |       |         |     |       | h i      |      |      |           |

| RMAP =          | 0, Page 3                             |                        |           |       |         |     |       |          |      |      |           |

| CA <sub>H</sub> | ADC RESRAOL                           | Reset: 00 <sub>H</sub> | Bit Field | RE    | ESULT[2 | :0] | VF    | DRC      |      | CHNR |           |

| - 11            | Result Register 0, View               |                        | Туре      |       | rh      |     | rh    | rh       |      | rh   |           |

| CB <sub>H</sub> | ADC RESRA0H                           | Reset: 00 <sub>H</sub> | Bit Field |       |         |     | RESUL | T[10:3]  |      |      |           |

| n               | Result Register 0, View               |                        | Туре      |       |         |     |       | h        |      |      |           |

| ССн             | ADC_RESRA1L                           | Reset: 00 <sub>H</sub> | Bit Field | RE    | ESULT[2 | :01 | VF    | DRC      |      | CHNR |           |

| H               | Result Register 1, View               |                        | Туре      |       | rh      | ]   | rh    | rh       |      | rh   |           |

| CD <sub>H</sub> | ADC RESRA1H                           | Reset: 00 <sub>H</sub> | Bit Field |       |         |     |       | T[10:3]  |      |      |           |

| 0DH             | Result Register 1, View               |                        | Туре      |       |         |     |       | h        |      |      |           |

| CEH             | ADC RESRA2L                           | Reset: 00 <sub>H</sub> | Bit Field | RF    | ESULT[2 | ·01 | VF .  | DRC      |      | CHNR |           |

| 0-H             | Result Register 2, View               |                        | Туре      |       |         | .0] | rh    | rh       |      | rh   |           |

| CF <sub>H</sub> | ADC RESRA2H                           | Reset: 00 <sub>H</sub> | Bit Field |       |         |     |       | T[10:3]  |      |      |           |

| 0. H            | Result Register 2, View               |                        | Туре      |       |         |     |       | h        |      |      |           |

| D2 <sub>H</sub> | ADC RESRA3L                           | Reset: 00 <sub>H</sub> | Bit Field | RF    | ESULT[2 | ·01 | VF .  | DRC      |      | CHNR |           |

| 5-H             | Result Register 3, View               |                        | Туре      |       | rh      | .0] | rh    | rh       |      | rh   |           |

| D3 <sub>H</sub> | ADC RESRA3H                           | Reset: 00 <sub>H</sub> | Bit Field |       |         |     |       | _T[10:3] |      |      |           |

| DOH             | Result Register 3, View /             |                        | Туре      |       |         |     |       | h        |      |      |           |

| RMAP =          | 0, Page 4                             |                        | 1300      |       |         |     |       |          |      |      |           |

| CA <sub>H</sub> | ADC RCR0                              | Reset: 00 <sub>H</sub> | Bit Field | VFCTR | WFR     | 0   | IEN   | l        | 0    |      | DRCT      |

| o, H            | Result Control Register (             |                        | Bittiola  |       |         | Ũ   |       |          | Ũ    |      | R         |

|                 |                                       |                        | Туре      | rw    | rw      | r   | rw    |          | r    |      | rw        |

| СВн             | ADC_RCR1                              | Reset: 00 <sub>H</sub> | Bit Field | VFCTR | WFR     | 0   | IEN   |          | 0    |      | DRCT      |

|                 | Result Control Register 1             |                        |           |       |         |     |       |          |      |      | R         |

|                 |                                       |                        | Туре      | rw    | rw      | r   | rw    |          | r    |      | rw        |

| CCH             | ADC_RCR2<br>Result Control Register 2 | Reset: 00 <sub>H</sub> | Bit Field | VFCTR | WFR     | 0   | IEN   |          | 0    |      | DRCT<br>R |

|                 | Ç. A                                  |                        | Туре      | rw    | rw      | r   | rw    |          | r    |      | rw        |

| CD <sub>H</sub> | ADC_RCR3<br>Result Control Register 3 | Reset: 00 <sub>H</sub> | Bit Field | VFCTR | WFR     | 0   | IEN   |          | 0    |      | DRCT      |

|                 |                                       |                        | Туре      | rw    | rw      | r   | rw    |          | r    |      | rw        |

| CEH             | ADC_VFCR                              | Reset: 00 <sub>H</sub> | Bit Field | 1 VV  |         | )   | 1 44  | VFC3     | VFC2 | VFC1 | VFC0      |

| UCH             | Valid Flag Clear Register             |                        | Туре      |       |         | r   |       | WFC3     | WFC2 | W    | WFCU      |

|                 | i g men regiotoi                      |                        | iyhe      | 1     |         |     |       | vv       | ٧V   | vv   | vv        |

| AB <sub>H</sub> | SSC_CONH Reset: 00<br>Control Register High | H Bit Field       | EN             | MS | 0 | AREN   | BEN      | PEN | REN | TEN |

|-----------------|---------------------------------------------|-------------------|----------------|----|---|--------|----------|-----|-----|-----|

|                 | Programming Mode                            | Туре              | rw             | rw | r | rw     | rw       | rw  | rw  | rw  |

|                 | Operating Mode                              | Bit Field         | EN             | MS | 0 | BSY    | BE       | PE  | RE  | TE  |

|                 |                                             | Туре              | rw             | rw | r | rh     | rwh      | rwh | rwh | rwh |

| AC <sub>H</sub> | SSC_TBL Reset: 00                           | H Bit Field       | Field TB_VALUE |    |   |        |          |     |     |     |

|                 | Transmitter Buffer Register Low             |                   | rw             |    |   |        |          |     |     |     |

| AD <sub>H</sub> | SSC_RBL Reset: 00                           | H Bit Field       | RB_VALUE       |    |   |        |          |     |     |     |

|                 | Receiver Buffer Register Low                | Туре              | rh             |    |   |        |          |     |     |     |

| AE <sub>H</sub> | SSC_BRL Reset: 00                           |                   |                |    |   | BR_VA  | _UE[7:0] |     |     |     |

|                 | Baudrate Timer Reload Register Lo           | <sup>w</sup> Туре |                |    |   | r      | N        |     |     |     |

| AF <sub>H</sub> | SSC_BRH Reset: 00                           |                   |                |    |   | BR_VAL | UE[15:8] |     |     |     |

|                 | Baudrate Timer Reload Register Hig          | Ih Type           |                |    |   | r      | N        |     |     |     |

#### Table 14 SSC Register Overview

The OCDS SFRs can be accessed in the mapped memory area (RMAP = 1).

#### Table 15OCDS Register Overview

| Addr            | Register Name                                                           | Bit       | 7           | 6     | 5           | 4           | 3           | 2         | 1          | 0         |

|-----------------|-------------------------------------------------------------------------|-----------|-------------|-------|-------------|-------------|-------------|-----------|------------|-----------|

| RMAP =          | 1                                                                       |           | I.          |       |             |             |             |           |            |           |

| E9 <sub>H</sub> | MMCR2 Reset: 0U <sub>H</sub><br>Monitor Mode Control Register 2         | Bit Field | EXBC_<br>P  | EXBC  | MBCO<br>N_P | MBCO<br>N   | MMEP<br>_P  | MMEP      | MMOD<br>E  | JENA      |

|                 |                                                                         | Туре      | w           | rw    | w           | rwh         | w           | rwh       | rh         | rh        |

| F1 <sub>H</sub> | MMCR Reset: 00 <sub>H</sub><br>Monitor Mode Control Register            | Bit Field | MEXIT<br>_P | MEXIT | MSTEP<br>_P | MSTEP       | MRAM<br>S_P | MRAM<br>S | TRF        | RRF       |

|                 |                                                                         | Туре      | w           | rwh   | w           | rw          | w           | rwh       | rh         | rh        |

| F2 <sub>H</sub> | MMSR Reset: 00 <sub>H</sub><br>Monitor Mode Status Register             | Bit Field | MBCA<br>M   | MBCIN | EXBF        | SWBF        | HWB3<br>F   | HWB2<br>F | HWB1<br>F  | HWB0<br>F |

|                 |                                                                         | Туре      | rw          | rh    | rwh         | rwh         | rwh         | rwh       | rwh        | rwh       |

| F3 <sub>H</sub> | MMBPCR Reset: 00 <sub>H</sub><br>BreakPoints Control Register           | Bit Field | SWBC        | HW    | HWB3C HWB2C |             | B2C         | HWB1<br>C | 31 HWB0C   |           |

|                 |                                                                         | Туре      | rw          | r     | rw r        |             | w           | rw        | r          | w         |

| F4 <sub>H</sub> | MMICR Reset: 00 <sub>H</sub><br>Monitor Mode Interrupt Control Register | Bit Field | DVECT       | DRETR | (           | Ċ           | MMUIE<br>_P | MMUIE     | RRIE_<br>P | RRIE      |

|                 |                                                                         | Туре      | rwh         | rwh   |             | r           | w           | rw        | w          | rw        |

| F5 <sub>H</sub> | MMDR Reset: 00 <sub>H</sub><br>Monitor Mode Data Register               | Bit Field |             |       |             | MN          | IRR         |           |            |           |

|                 | Receive                                                                 | Туре      |             |       |             | r           | h           |           |            |           |

|                 | Transmit                                                                | Bit Field |             |       |             | MN          | 1TR         |           |            |           |

|                 |                                                                         | Туре      |             |       |             | ١           | N           |           |            |           |

| F6 <sub>H</sub> | HWBPSR Reset: 00 <sub>H</sub><br>Hardware Breakpoints Select Register   | Bit Field |             | 0     |             | BPSEL<br>_P |             | BP        | SEL        |           |

|                 |                                                                         | Туре      |             | r     |             | w           |             | r         | w          |           |

| F7 <sub>H</sub> | HWBPDR Reset: 00 <sub>H</sub>                                           | Bit Field |             |       |             | HW          | BPxx        |           |            |           |

|                 | Hardware Breakpoints Data Register                                      |           | rw          |       |             |             |             |           |            |           |

## 3.3 Flash Memory

The Flash memory provides an embedded user-programmable non-volatile memory, allowing fast and reliable storage of user code and data. It is operated from a single 2.5 V supply from the Embedded Voltage Regulator (EVR) and does not require additional programming or erasing voltage. The sectorization of the Flash memory allows each sector to be erased independently.

#### Features

- In-System Programming (ISP) via UART

- In-Application Programming (IAP)

- · Error Correction Code (ECC) for dynamic correction of single-bit errors

- Background program and erase operations for CPU load minimization

- Support for aborting erase operation

- Minimum program width<sup>1)</sup> of 32-byte for D-Flash and 32-byte for P-Flash

- 1-sector minimum erase width

- · 1-byte read access

- · Flash is delivered in erased state (read all zeros)

- Operating supply voltage: 2.5 V ± 7.5 %

- Read access time: 3 × t<sub>CCLK</sub> = 112.5 ns<sup>2)</sup>

- Program time: 209440 /  $f_{SYS}$  = 2.6 ms<sup>3</sup>)

- Erase time: 8175360 /  $f_{SYS}$  = 102 ms<sup>3</sup>)

P-Flash: 32-byte wordline can only be programmed once, i.e., one gate disturb allowed. D-Flash: 32-byte wordline can be programmed twice, i.e., two gate disturbs allowed.

<sup>&</sup>lt;sup>2)</sup>  $f_{svs}$  = 80 MHz ± 7.5% ( $f_{CCLK}$  = 26.7 MHz ± 7.5 %) is the maximum frequency range for Flash read access.

<sup>&</sup>lt;sup>3)</sup>  $f_{sys} = 80 \text{ MHz} \pm 7.5\%$  is the only frequency range for Flash programming and erasing.  $f_{sysmin}$  is used for obtaining the worst case timing.

| Table 16    | Flash Data Retention an | d Endurance (Operat           | ing Conditions apply) |

|-------------|-------------------------|-------------------------------|-----------------------|

| Retention   | Endurance <sup>1)</sup> | Size                          | Remarks               |

| Program Fla | sh                      |                               |                       |

| 20 years    | 1,000 cycles            | up to 16 Kbytes <sup>2)</sup> | for 16-Kbyte Variant  |

| 20 years    | 1,000 cycles            | up to 8 Kbytes <sup>2)</sup>  | for 8-Kbyte Variant   |

| 20 years    | 1,000 cycles            | up to 4 Kbytes <sup>2)</sup>  | for 4-Kbyte Variant   |

| Data Flash  |                         |                               |                       |

| 20 years    | 1,000 cycles            | 4 Kbytes                      |                       |

| 5 years     | 10,000 cycles           | 1 Kbyte                       |                       |

| 2 years     | 70,000 cycles           | 512 bytes                     |                       |

| 2 years     | 100,000 cycles          | 128 bytes                     |                       |

| 1           |                         |                               |                       |

Table 16 shows the Flash data retention and endurance targets.

<sup>1)</sup> One cycle refers to the programming of all wordlines in a sector and erasing of sector. The Flash endurance data specified in **Table 16** is valid only if the following conditions are fulfilled:

- the maximum number of erase cycles per Flash sector must not exceed 100,000 cycles.

- the maximum number of erase cycles per Flash bank must not exceed 300,000 cycles.

- the maximum number of program cycles per Flash bank must not exceed 2,500,000 cycles.

<sup>2)</sup> If no Flash is used for data, the Program Flash size can be up to the maximum Flash size available in the device variant. Having more Data Flash will mean less Flash is available for Program Flash.

#### 3.3.1 Flash Bank Sectorization

The XC866 product family offers four Flash devices with either 8 Kbytes or 16 Kbytes of embedded Flash memory. These Flash memory sizes are made up of two or four 4-Kbyte Flash banks, respectively. Each Flash device consists of Program Flash (P-Flash) bank(s) and a single Data Flash (D-Flash) bank with different sectorization shown in **Figure 11**. Both types can be used for code and data storage. The label "Data" neither implies that the D-Flash is mapped to the data memory region, nor that it can only be used for data storage. It is used to distinguish the different Flash bank sectorizations. The XC866 ROM devices offer a single 4-Kbyte D-Flash bank.

## XC866

#### **Functional Description**

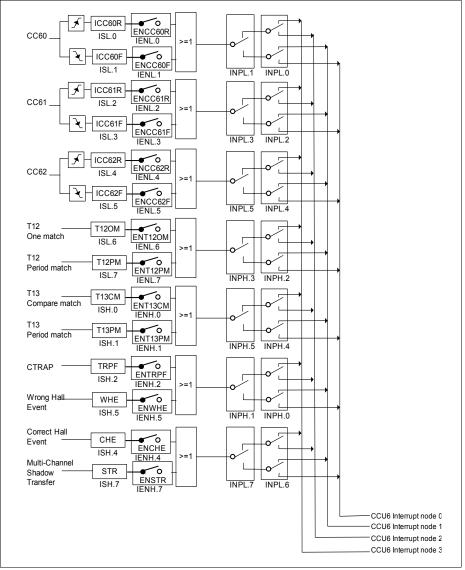

#### Figure 17 Interrupt Request Sources (Part 4)

## 3.4.2 Interrupt Source and Vector

Each interrupt source has an associated interrupt vector address. This vector is accessed to service the corresponding interrupt source request. The interrupt service of each interrupt source can be individually enabled or disabled via an enable bit. The assignment of the XC866 interrupt sources to the interrupt vector addresses and the corresponding interrupt source enable bits are summarized in **Table 17**.

| Interrupt<br>Source | Vector<br>Address | Assignment for XC866                            | Enable Bit | SFR    |

|---------------------|-------------------|-------------------------------------------------|------------|--------|

| NMI                 | 0073 <sub>H</sub> | Watchdog Timer NMI                              | NMIWDT     | NMICON |

|                     |                   | PLL NMI                                         | NMIPLL     |        |

|                     |                   | Flash NMI                                       | NMIFLASH   |        |

|                     |                   | VDDC Prewarning NMI                             | NMIVDD     |        |

|                     |                   | VDDP Prewarning NMI                             | NMIVDDP    |        |

|                     |                   | Flash ECC NMI                                   | NMIECC     |        |

| XINTR0              | 0003 <sub>H</sub> | External Interrupt 0                            | EX0        | IEN0   |

| XINTR1              | 000B <sub>H</sub> | Timer 0                                         | ET0        |        |

| XINTR2              | 0013 <sub>H</sub> | External Interrupt 1                            | EX1        |        |

| XINTR3              | 001B <sub>H</sub> | Timer 1                                         | ET1        |        |

| XINTR4              | 0023 <sub>H</sub> | UART                                            | ES         |        |

| XINTR5              | 002B <sub>H</sub> | T2                                              | ET2        |        |

|                     |                   | Fractional Divider<br>(Normal Divider Overflow) |            |        |

|                     |                   | LIN                                             |            |        |

#### Table 17 Interrupt Vector Addresses

| XINTR6  | 0033 <sub>H</sub> | ADC                  | EADC   | IEN1 |

|---------|-------------------|----------------------|--------|------|

| XINTR7  | 003B <sub>H</sub> | SSC                  | ESSC   |      |

| XINTR8  | 0043 <sub>H</sub> | External Interrupt 2 | EX2    |      |

| XINTR9  | 004B <sub>H</sub> | External Interrupt 3 | EXM    |      |

|         |                   | External Interrupt 4 |        |      |

|         |                   | External Interrupt 5 |        |      |

|         |                   | External Interrupt 6 |        |      |

| XINTR10 | 0053 <sub>H</sub> | CCU6 INP0            | ECCIP0 |      |

| XINTR11 | 005B <sub>H</sub> | CCU6 INP1            | ECCIP1 |      |

| XINTR12 | 0063 <sub>H</sub> | CCU6 INP2            | ECCIP2 |      |

| XINTR13 | 006B <sub>H</sub> | CCU6 INP3            | ECCIP3 |      |

## Table 17 Interrupt Vector Addresses (cont'd)

## XC866

#### **Functional Description**

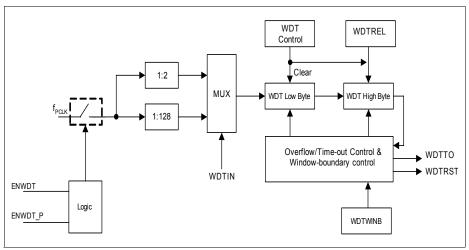

## 3.10 Watchdog Timer

The Watchdog Timer (WDT) provides a highly reliable and secure way to detect and recover from software or hardware failures. The WDT is reset at a regular interval that is predefined by the user. The CPU must service the WDT within this interval to prevent the WDT from causing an XC866 system reset. Hence, routine service of the WDT confirms that the system is functioning properly. This ensures that an accidental malfunction of the XC866 will be aborted in a user-specified time period. In debug mode, the WDT is suspended and stops counting. Therefore, there is no need to refresh the WDT during debugging.

#### Features:

- 16-bit Watchdog Timer

- · Programmable reload value for upper 8 bits of timer

- Programmable window boundary

- Selectable input frequency of f<sub>PCLK</sub>/2 or f<sub>PCLK</sub>/128

- Time-out detection with NMI generation and reset prewarning activation (after which a system reset will be performed)

The WDT is a 16-bit timer incremented by a count rate of  $f_{PCLK}/2$  or  $f_{PCLK}/128$ . This 16-bit timer is realized as two concatenated 8-bit timers. The upper 8 bits of the WDT can be preset to a user-programmable value via a watchdog service access in order to modify the watchdog expire time period. The lower 8 bits are reset on each service access. **Figure 27** shows the block diagram of the WDT unit.

Figure 27 WDT Block Diagram

If the WDT is not serviced before the timer overflow, a system malfunction is assumed. As a result, the WDT NMI is triggered (assert WDTTO) and the reset prewarning is entered. The prewarning period lasts for  $30_{\rm H}$  count, after which the system is reset (assert WDTRST).

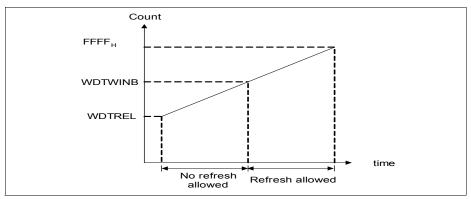

The WDT has a "programmable window boundary" which disallows any refresh during the WDT's count-up. A refresh during this window boundary constitutes an invalid access to the WDT, causing the reset prewarning to be entered but without triggering the WDT NMI. The system will still be reset after the prewarning period is over. The window boundary is from  $0000_{\rm H}$  to the value obtained from the concatenation of WDTWINB and  $00_{\rm H}$ .

After being serviced, the WDT continues counting up from the value (<WDTREL>  $* 2^8$ ). The time period for an overflow of the WDT is programmable in two ways:

- the input frequency to the WDT can be selected to be either f<sub>PCLK</sub>/2 or f<sub>PCLK</sub>/128

- the reload value WDTREL for the high byte of WDT can be programmed in register WDTREL

The period,  $P_{WDT}$ , between servicing the WDT and the next overflow can be determined by the following formula:

$$P_{WDT} = \frac{2^{(1+WDTIN \times 6)} \times (2^{16} - WDTREL \times 2^8)}{f_{PCLK}}$$

If the Window-Boundary Refresh feature of the WDT is enabled, the period  $P_{WDT}$  between servicing the WDT and the next overflow is shortened if WDTWINB is greater than WDTREL, see **Figure 28**. This period can be calculated using the same formula by replacing WDTREL with WDTWINB. For this feature to be useful, WDTWINB should not be smaller than WDTREL.

Figure 28 WDT Timing Diagram

## 3.14 High-Speed Synchronous Serial Interface

The High-Speed Synchronous Serial Interface (SSC) supports full-duplex and half-duplex synchronous communication. The serial clock signal can be generated by the SSC internally (master mode), using its own 16-bit baud-rate generator, or can be received from an external master (slave mode). Data width, shift direction, clock polarity and phase are programmable. This allows communication with SPI-compatible devices or devices using other synchronous serial interfaces.

#### Features:

- · Master and slave mode operation

- Full-duplex or half-duplex operation

- Transmit and receive buffered

- Flexible data format

- Programmable number of data bits: 2 to 8 bits

- Programmable shift direction: LSB or MSB shift first

- Programmable clock polarity: idle low or high state for the shift clock

- Programmable clock/data phase: data shift with leading or trailing edge of the shift clock

- · Variable baud rate

- · Compatible with Serial Peripheral Interface (SPI)

- Interrupt generation

- On a transmitter empty condition

- On a receiver full condition

- On an error condition (receive, phase, baud rate, transmit error)

#### Table 31JTAG ID Summary

| ROM | XC866L-4RR | 1013 9083 <sub>H</sub> |

|-----|------------|------------------------|

|     | XC866-4RR  | 1013 9083 <sub>H</sub> |

|     | XC866L-2RR | 1013 9083 <sub>H</sub> |

|     | XC866-2RR  | 1013 9083 <sub>H</sub> |

#### 3.20 Identification Register

The XC866 identity register is located at Page 1 of address B3<sub>H</sub>.

# ID

#### **Identity Register**

#### Reset Value: 0000 0010<sub>B</sub>

| 7 | 6 | 5      | 4 | 3 | 2 | 1     | 0 |

|---|---|--------|---|---|---|-------|---|

|   | Ι | PRODID | I | I |   | VERID | I |

|   | r |        |   |   |   | r     | L |

| Field  | Bits  | Туре | Description                      |

|--------|-------|------|----------------------------------|

| VERID  | [2:0] | r    | Version ID<br>010 <sub>B</sub>   |

| PRODID | [7:3] | r    | Product ID<br>00000 <sub>B</sub> |

#### **Electrical Parameters**

#### Table 36ADC Characteristics (Operating Conditions apply; $V_{DDP}$ = 5V Range)

| Parameter                                                  | Symbol                   | Li   | mit Valu | es   | Unit | Test Conditions/ |  |

|------------------------------------------------------------|--------------------------|------|----------|------|------|------------------|--|

|                                                            |                          | min. | typ.     | max. |      | Remarks          |  |

| Switched<br>capacitance at the<br>analog voltage<br>inputs | C <sub>AINSW</sub><br>CC | _    | 5        | 7    | pF   | 2)4)             |  |

| Input resistance of the reference input                    | R <sub>AREF</sub> CC     | -    | 1        | 2    | kΩ   | 2)               |  |

| Input resistance of the selected analog channel            | R <sub>AIN</sub> CC      | -    | 1        | 1.5  | kΩ   | 2)               |  |

<sup>1)</sup> TUE is tested at  $V_{AREF}$  = 5.0 V,  $V_{AGND}$  = 0 V ,  $V_{DDP}$  = 5.0 V.

<sup>2)</sup> Not subject to production test, verified by design/characterization.

<sup>&</sup>lt;sup>3)</sup> This represents an equivalent switched capacitance. This capacitance is not switched to the reference voltage at once. Instead of this, smaller capacitances are successively switched to the reference voltage.

<sup>&</sup>lt;sup>4)</sup> The sampling capacity of the conversion C-Network is pre-charged to V<sub>AREF</sub>/2 before connecting the input to the C-Network. Because of the parasitic elements, the voltage measured at ANx is lower than V<sub>AREF</sub>/2.

#### **Electrical Parameters**

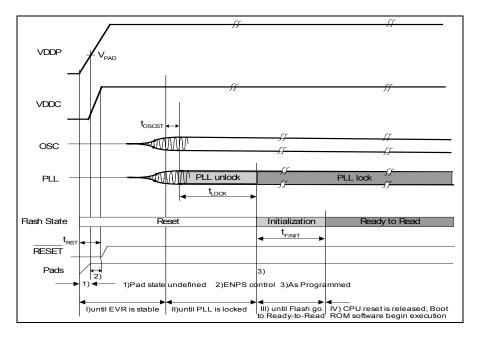

## 4.3.3 Power-on Reset and PLL Timing

| Table 42 | Power-On Reset and PLL Timing (Operating Conditions apply) |

|----------|------------------------------------------------------------|

|----------|------------------------------------------------------------|

| Parameter                           | Symbol                   | Limit Values |      |      | Unit | Test Conditions                                     |

|-------------------------------------|--------------------------|--------------|------|------|------|-----------------------------------------------------|

|                                     |                          | min.         | typ. | max. |      |                                                     |

| Pad operating voltage               | V <sub>PAD</sub> CC      | 2.3          | -    | -    | V    |                                                     |

| On-Chip Oscillator<br>start-up time | t <sub>OSCST</sub><br>CC | _            | -    | 500  | ns   |                                                     |

| Flash initialization time           | t <sub>FINIT</sub> CC    | -            | 160  | -    | μs   |                                                     |

| RESET hold time <sup>1)</sup>       | t <sub>RST</sub> SR      | _            | 500  | _    | μs   | $V_{\text{DDP}}$ rise time (10% – 90%) $\leq$ 500µs |

| PLL lock-in in time                 | t <sub>LOCK</sub> CC     | -            | -    | 200  | μs   |                                                     |

| PLL accumulated jitter              | D <sub>P</sub>           | -            | -    | 0.7  | ns   | 2)                                                  |

<sup>1)</sup> RESET signal has to be active (low) until  $V_{\text{DDC}}$  has reached 90% of its maximum value (typ. 2.5V).

<sup>2)</sup> PLL lock at 80 MHz using a 4 MHz external oscillator. The PLL Divider settings are K = 2, N = 40 and P = 1.

## Figure 42 Power-on Reset Timing

## **Electrical Parameters**

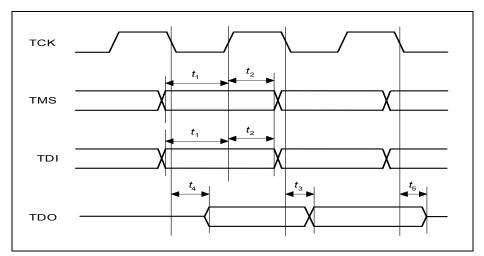

| Table 45 | JTAG Timing (Operating Conditions apply; $C_{L}$ = 50 pF) |

|----------|-----------------------------------------------------------|

|----------|-----------------------------------------------------------|

| Parameter                                     |                       | mbol | Lir  | Unit |    |

|-----------------------------------------------|-----------------------|------|------|------|----|

|                                               |                       |      | min  | max  |    |

| TMS setup to TCK 🦨                            | <i>t</i> <sub>1</sub> | SR   | 8.0  | -    | ns |

| TMS hold to TCK _                             | $t_2$                 | SR   | 5.0  | -    | ns |

| TDI setup to TCK 🦨                            | <i>t</i> <sub>1</sub> | SR   | 11.0 | -    | ns |

| TDI hold to TCK 🦨                             | $t_2$                 | SR   | 6.0  | -    | ns |

| TDO valid output from TCK -                   | $t_3$                 | СС   | -    | 23   | ns |

| TDO high impedance to valid output from TCK 🥆 | $t_4$                 | СС   | -    | 26   | ns |

| TDO valid output to high impedance from TCK ٦ | $t_5$                 | CC   | -    | 18   | ns |

Figure 44 JTAG Timing