Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                      |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | XC800                                                                         |

| Core Size                  | 8-Bit                                                                         |

| Speed                      | 86MHz                                                                         |

| Connectivity               | LINbus, SSI, UART/USART                                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                         |

| Number of I/O              | 19                                                                            |

| Program Memory Size        | 16KB (16K x 8)                                                                |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 768 x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                   |

| Data Converters            | A/D 8x10b                                                                     |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 38-TFSOP (0.173", 4.40mm Width)                                               |

| Supplier Device Package    | PG-TSSOP-38                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/saf-xc866l-4fri-bc |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# infineon

### **Summary of Features**

#### Table 2Device Summary

|     | -                  |     |    |   |    |            |

|-----|--------------------|-----|----|---|----|------------|

|     | SAK-XC866*-1FRI 3V | 3.3 | -  | 4 | -  | Industrial |

|     | SAF-XC866*-4FRA 3V | 3.3 | 12 | 4 | -  | Automotive |

|     | SAF-XC866*-4FRI 3V | 3.3 | 12 | 4 | -  | Industrial |

|     | SAF-XC866*-2FRA 3V | 3.3 | 4  | 4 | _  | Automotive |

|     | SAF-XC866*-2FRI 3V | 3.3 | 4  | 4 | -  | Industrial |

|     | SAF-XC866*-1FRA 3V | 3.3 | -  | 4 | -  | Automotive |

|     | SAF-XC866*-1FRI 3V | 3.3 | -  | 4 | -  | Industrial |

| ROM | SAK-XC866*-4RRA    | 5.0 | -  | 4 | 16 | Automotive |

|     | SAK-XC866*-4RRI    | 5.0 | -  | 4 | 16 | Industrial |

|     | SAK-XC866*-2RRA    | 5.0 | -  | 4 | 8  | Automotive |

|     | SAK-XC866*-2RRI    | 5.0 | -  | 4 | 8  | Industrial |

|     | SAF-XC866*-4RRA    | 5.0 | -  | 4 | 16 | Automotive |

|     | SAF-XC866*-4RRI    | 5.0 | -  | 4 | 16 | Industrial |

|     | SAF-XC866*-2RRA    | 5.0 | _  | 4 | 8  | Automotive |

|     | SAF-XC866*-2RRI    | 5.0 | -  | 4 | 8  | Industrial |

|     | SAK-XC866*-4RRA 3V | 3.3 | -  | 4 | 16 | Automotive |

|     | SAK-XC866*-4RRI 3V | 3.3 | -  | 4 | 16 | Industrial |

|     | SAK-XC866*-2RRA 3V | 3.3 | -  | 4 | 8  | Automotive |

|     | SAK-XC866*-2RRI 3V | 3.3 | _  | 4 | 8  | Industrial |

|     | SAF-XC866*-4RRA 3V | 3.3 | -  | 4 | 16 | Automotive |

|     | SAF-XC866*-4RRI 3V | 3.3 | -  | 4 | 16 | Industrial |

|     | SAF-XC866*-2RRA 3V | 3.3 | -  | 4 | 8  | Automotive |

|     | SAF-XC866*-2RRI 3V | 3.3 | -  | 4 | 8  | Industrial |

1) Industrial is not for Automotive usage

<sup>2)</sup> The flash memory (P-Flash and D-Flash) can be used for code or data.

Note: The asterisk (\*) above denotes the device configuration letters from Table 1.

# **General Device Information**

# 2.4 Pin Definitions and Functions

İnfineon

### Table 3 Pin Definitions and Functions

| Symbol | Pin<br>Number | Туре | Reset<br>State | Function                            |                                                                                                                            |

|--------|---------------|------|----------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| P0     |               | I/O  |                | port. It can b                      | -bit bidirectional general purpose I/O<br>be used as alternate functions for the<br>6, UART, and the SSC.                  |

| P0.0   | 12            |      | Hi-Z           | TCK_0<br>T12HR_1                    | JTAG Clock Input<br>CCU6 Timer 12 Hardware Run<br>Input                                                                    |

|        |               |      |                | CC61_1<br>CLKOUT<br>RXDO_1          | Input/Output of Capture/Compare<br>channel 1<br>Clock Output<br>UART Transmit Data Output                                  |

| P0.1   | 14            |      | Hi-Z           | TDI_0<br>T13HR_1                    | JTAG Serial Data Input<br>CCU6 Timer 13 Hardware Run<br>Input                                                              |

|        |               |      |                | RXD_1<br>COUT61_1                   | UART Receive Data Input                                                                                                    |

| P0.2   | 13            |      | PU             | EXF2_1<br>CTRAP_2<br>TDO_0<br>TXD_1 | Timer 2 External Flag Output<br>CCU6 Trap Input<br>JTAG Serial Data Output<br>UART Transmit Data Output/<br>Clock Output   |

| P0.3   | 2             |      | Hi-Z           | SCK_1<br>COUT63_1                   | SSC Clock Input/Output<br>Output of Capture/Compare<br>channel 3                                                           |

| P0.4   | 3             |      | Hi-Z           | MTSR_1<br>CC62_1                    | SSC Master Transmit Output/<br>Slave Receive Input<br>Input/Output of Capture/Compare<br>channel 2                         |

| P0.5   | 4             |      | Hi-Z           | MRST_1<br>EXINT0_0<br>COUT62_1      | SSC Master Receive Input/<br>Slave Transmit Output<br>External Interrupt Input 0<br>Output of Capture/Compare<br>channel 2 |

# 3 Functional Description

# 3.1 Processor Architecture

The XC866 is based on a high-performance 8-bit Central Processing Unit (CPU) that is compatible with the standard 8051 processor. While the standard 8051 processor is designed around a 12-clock machine cycle, the XC866 CPU uses a 2-clock machine cycle. This allows fast access to ROM or RAM memories without wait state. Access to the Flash memory, however, requires an additional wait state (one machine cycle). The instruction set consists of 45% one-byte, 41% two-byte and 14% three-byte instructions.

The XC866 CPU provides a range of debugging features, including basic stop/start, single-step execution, breakpoint support and read/write access to the data memory, program memory and SFRs.

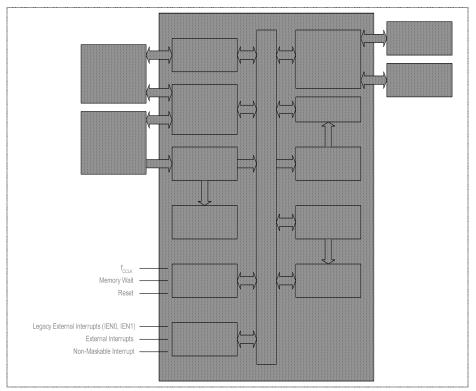

Figure 5 shows the CPU functional blocks.

Figure 5 CPU Block Diagram

#### Table 5 Flash Protection Type for XC866-2FR and XC866-4FR devices

| PASSWORD              | Type of Protection      | Flash Banks to Erase when<br>Unprotected |  |

|-----------------------|-------------------------|------------------------------------------|--|

| 1XXXXXXX <sub>B</sub> | Flash Protection Mode 1 | All Banks                                |  |

| 0XXXXXXAB             | Flash Protection Mode 0 | P-Flash Bank                             |  |

#### For XC866-1FR device and ROM devices:

The selection of protection type is summarized in Table 6.

#### Table 6 Flash Protection Type for XC866-1FR device and ROM devices

| PASSWORD              | Type of Protection<br>(Applicable to the<br>whole Flash) | Sectors to Erase when Unprotected | Comments                           |

|-----------------------|----------------------------------------------------------|-----------------------------------|------------------------------------|

| 1XXXXXX <sub>B</sub>  | Read/Program/Erase                                       | All Sectors                       | Compatible to<br>Protection mode 1 |

| 00001XXX <sub>B</sub> | Erase                                                    | Sector 0                          |                                    |

| 00010XXX <sub>B</sub> | Erase                                                    | Sector 0 and 1                    |                                    |

| 00011XXX <sub>B</sub> | Erase                                                    | Sector 0 to 2                     |                                    |

| 00100XXX <sub>B</sub> | Erase                                                    | Sector 0 to 3                     |                                    |

| 00101XXX <sub>B</sub> | Erase                                                    | Sector 0 to 4                     |                                    |

| 00110XXX <sub>B</sub> | Erase                                                    | Sector 0 to 5                     |                                    |

| 00111XXX <sub>B</sub> | Erase                                                    | Sector 0 to 6                     |                                    |

| 01000XXX <sub>B</sub> | Erase                                                    | Sector 0 to 7                     |                                    |

| 01001XXX <sub>B</sub> | Erase                                                    | Sector 0 to 8                     |                                    |

| 01010XXX <sub>B</sub> | Erase                                                    | All Sectors                       |                                    |

| Others                | Erase                                                    | None                              |                                    |

Although no protection scheme can be considered infallible, the XC866 memory protection strategy provides a very high level of protection for a general purpose microcontroller.

# 3.2.2 Special Function Register

The Special Function Registers (SFRs) occupy direct internal data memory space in the range  $80_H$  to FF<sub>H</sub>. All registers, except the program counter, reside in the SFR area. The SFRs include pointers and registers that provide an interface between the CPU and the on-chip peripherals. As the 128-SFR range is less than the total number of registers required, address extension mechanisms are required to increase the number of addressable SFRs. The address extension mechanisms include:

- Mapping

- Paging

# 3.2.2.1 Address Extension by Mapping

Address extension is performed at the system level by mapping. The SFR area is extended into two portions: the standard (non-mapped) SFR area and the mapped SFR area. Each portion supports the same address range  $80_H$  to FF<sub>H</sub>, bringing the number of addressable SFRs to 256. The extended address range is not directly controlled by the CPU instruction itself, but is derived from bit RMAP in the system control register SYSCON0 at address  $8F_H$ . To access SFRs in the mapped area, bit RMAP in SFR SYSCON0 must be set. Alternatively, the SFRs in the standard area can be accessed by clearing bit RMAP. The SFR area can be selected as shown in **Figure 8**.

#### SYSCON0 System Control Register 0 Reset Value: 00<sub>H</sub> 2 1 0 7 6 5 4 3 0 1 0 RMAP r rw r rw

| Field | Bits    | Туре | Description                                                                                                                                                               |  |

|-------|---------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| RMAP  | 0       | rw   | <ul> <li>Special Function Register Map Control</li> <li>The access to the standard SFR area is enabled.</li> <li>The access to the mapped SFR area is enabled.</li> </ul> |  |

| 1     | 2       | rw   | <b>Reserved</b><br>Returns the last value if read; should be written<br>with 1.                                                                                           |  |

| 0     | 1,[7:3] | r    | <b>Reserved</b><br>Returns 0 if read; should be written with 0.                                                                                                           |  |

# 3.2.3 Bit Protection Scheme

The bit protection scheme prevents direct software writing of selected bits (i.e., protected bits) using the PASSWD register. When the bit field MODE is  $11_B$ , writing  $10011_B$  to the bit field PASS opens access to writing of all protected bits, and writing  $10101_B$  to the bit field PASS closes access to writing of all protected bits. In both cases, the value of the bit field MODE is not changed even if PASSWD register is written with  $98_H$  or  $A8_H$ . It can only be changed when bit field PASS is written with  $11000_B$ , for example, writing D0<sub>H</sub> to PASSWD register disables the bit protection scheme.

The access is opened for maximum 32 CCLKs if the "close access" password is not written. If "open access" password is written again before the end of 32 CCLK cycles, there will be a recount of 32 CCLK cycles. The protected bits include NDIV, WDTEN, PD, and SD.

#### PASSWD Password Register

Reset Value: 07<sub>H</sub>

| 7 | 6    | 5 | 4 | 3 | 2       | 1  | 0  |

|---|------|---|---|---|---------|----|----|

|   | PASS |   |   |   | PROTECT | МС | DE |

|   | W    |   |   |   |         | r  | w  |

| Field     | Bits  | Туре | Description                                                                                                                                                                                                                                                                                 |  |

|-----------|-------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MODE      | [1:0] | rw   | Bit Protection Scheme Control bits00Scheme Disabled11Scheme Enabled (default)Others: Scheme EnabledThese two bits cannot be written directly. To changethe value between $11_B$ and $00_B$ , the bit field PASSmust be written with $11000_B$ ; only then, will theMODE[1:0] be registered. |  |

| PROTECT_S | 2     | rh   | <ul> <li>Bit Protection Signal Status bit</li> <li>This bit shows the status of the protection.</li> <li>0 Software is able to write to all protected bits.</li> <li>1 Software is unable to write to any protected bits.</li> </ul>                                                        |  |

| PASS      | [7:3] | w    | Password bitsThe Bit Protection Scheme only recognizes threepatterns.11000BEnables writing of the bit field MODE.10011BOpens access to writing of all protected bits.10101BCloses access to writing of all protected bits.                                                                  |  |

| Table 16 Flash Data Retention and Endurance (Operating Condition |                         |                               |                      |  |  |  |

|------------------------------------------------------------------|-------------------------|-------------------------------|----------------------|--|--|--|

| Retention                                                        | Endurance <sup>1)</sup> | Size                          | Remarks              |  |  |  |

| Program Fla                                                      | sh                      |                               |                      |  |  |  |

| 20 years                                                         | 1,000 cycles            | up to 16 Kbytes <sup>2)</sup> | for 16-Kbyte Variant |  |  |  |

| 20 years                                                         | 1,000 cycles            | up to 8 Kbytes <sup>2)</sup>  | for 8-Kbyte Variant  |  |  |  |

| 20 years                                                         | 1,000 cycles            | up to 4 Kbytes <sup>2)</sup>  | for 4-Kbyte Variant  |  |  |  |

| Data Flash                                                       |                         |                               |                      |  |  |  |

| 20 years                                                         | 1,000 cycles            | 4 Kbytes                      |                      |  |  |  |

| 5 years                                                          | 10,000 cycles           | 1 Kbyte                       |                      |  |  |  |

| 2 years                                                          | 70,000 cycles           | 512 bytes                     |                      |  |  |  |

| 2 years                                                          | 100,000 cycles          | 128 bytes                     |                      |  |  |  |

| 1                                                                |                         |                               |                      |  |  |  |

Table 16 shows the Flash data retention and endurance targets.

<sup>1)</sup> One cycle refers to the programming of all wordlines in a sector and erasing of sector. The Flash endurance data specified in **Table 16** is valid only if the following conditions are fulfilled:

- the maximum number of erase cycles per Flash sector must not exceed 100,000 cycles.

- the maximum number of erase cycles per Flash bank must not exceed 300,000 cycles.

- the maximum number of program cycles per Flash bank must not exceed 2,500,000 cycles.

<sup>2)</sup> If no Flash is used for data, the Program Flash size can be up to the maximum Flash size available in the device variant. Having more Data Flash will mean less Flash is available for Program Flash.

### 3.3.1 Flash Bank Sectorization

The XC866 product family offers four Flash devices with either 8 Kbytes or 16 Kbytes of embedded Flash memory. These Flash memory sizes are made up of two or four 4-Kbyte Flash banks, respectively. Each Flash device consists of Program Flash (P-Flash) bank(s) and a single Data Flash (D-Flash) bank with different sectorization shown in **Figure 11**. Both types can be used for code and data storage. The label "Data" neither implies that the D-Flash is mapped to the data memory region, nor that it can only be used for data storage. It is used to distinguish the different Flash bank sectorizations. The XC866 ROM devices offer a single 4-Kbyte D-Flash bank.

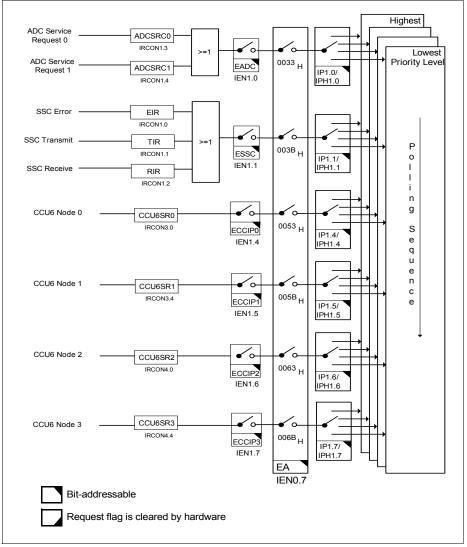

Figure 16 Interrupt Request Sources (Part 3)

| XINTR6  | 0033 <sub>H</sub> | ADC                  | EADC   | IEN1 |

|---------|-------------------|----------------------|--------|------|

| XINTR7  | 003B <sub>H</sub> | SSC                  | ESSC   |      |

| XINTR8  | 0043 <sub>H</sub> | External Interrupt 2 | EX2    |      |

| XINTR9  | 004B <sub>H</sub> | External Interrupt 3 | EXM    |      |

|         |                   | External Interrupt 4 |        |      |

|         |                   | External Interrupt 5 |        |      |

|         |                   | External Interrupt 6 |        |      |

| XINTR10 | 0053 <sub>H</sub> | CCU6 INP0            | ECCIP0 |      |

| XINTR11 | 005B <sub>H</sub> | CCU6 INP1            | ECCIP1 |      |

| XINTR12 | 0063 <sub>H</sub> | CCU6 INP2            | ECCIP2 |      |

| XINTR13 | 006B <sub>H</sub> | CCU6 INP3            | ECCIP3 |      |

# Table 17 Interrupt Vector Addresses (cont'd)

# 3.4.3 Interrupt Priority

Each interrupt source, except for NMI, can be individually programmed to one of the four possible priority levels. The NMI has the highest priority and supersedes all other interrupts. Two pairs of interrupt priority registers (IP and IPH, IP1 and IPH1) are available to program the priority level of each non-NMI interrupt vector.

A low-priority interrupt can be interrupted by a high-priority interrupt, but not by another interrupt of the same or lower priority. Further, an interrupt of the highest priority cannot be interrupted by any other interrupt source.

If two or more requests of different priority levels are received simultaneously, the request of the highest priority is serviced first. If requests of the same priority are received simultaneously, then an internal polling sequence determines which request is serviced first. Thus, within each priority level, there is a second priority structure determined by the polling sequence shown in **Table 18**.

| Source                                      | Level     |

|---------------------------------------------|-----------|

| Non-Maskable Interrupt (NMI)                | (highest) |

| External Interrupt 0                        | 1         |

| Timer 0 Interrupt                           | 2         |

| External Interrupt 1                        | 3         |

| Timer 1 Interrupt                           | 4         |

| UART Interrupt                              | 5         |

| Timer 2, Fractional Divider, LIN Interrupts | 6         |

| ADC Interrupt                               | 7         |

| SSC Interrupt                               | 8         |

| External Interrupt 2                        | 9         |

| External Interrupt [6:3]                    | 10        |

| CCU6 Interrupt Node Pointer 0               | 11        |

| CCU6 Interrupt Node Pointer 1               | 12        |

| CCU6 Interrupt Node Pointer 2               | 13        |

| CCU6 Interrupt Node Pointer 3               | 14        |

Table 18

Priority Structure within Interrupt Level

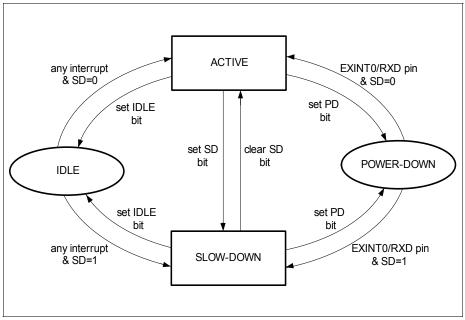

#### 3.9 Power Saving Modes

The power saving modes of the XC866 provide flexible power consumption through a combination of techniques, including:

- Stopping the CPU clock

- · Stopping the clocks of individual system components

- Reducing clock speed of some peripheral components

- · Power-down of the entire system with fast restart capability

After a reset, the active mode (normal operating mode) is selected by default (see **Figure 26**) and the system runs in the main system clock frequency. From active mode, different power saving modes can be selected by software. They are:

- · Idle mode

- Slow-down mode

- Power-down mode

Figure 26 Transition between Power Saving Modes

# 3.11 Universal Asynchronous Receiver/Transmitter

The Universal Asynchronous Receiver/Transmitter (UART) provides a full-duplex asynchronous receiver/transmitter, i.e., it can transmit and receive simultaneously. It is also receive-buffered, i.e., it can commence reception of a second byte before a previously received byte has been read from the receive register. However, if the first byte still has not been read by the time reception of the second byte is complete, one of the bytes will be lost.

#### Features:

- · Full-duplex asynchronous modes

- 8-bit or 9-bit data frames, LSB first

- fixed or variable baud rate

- · Receive buffered

- Multiprocessor communication

- Interrupt generation on the completion of a data transmission or reception

The UART can operate in the four modes as shown in **Table 25**. Data is transmitted on TXD and received on RXD.

| Operating Mode               | Baud Rate                                      |

|------------------------------|------------------------------------------------|

| Mode 0: 8-bit shift register | f <sub>PCLK</sub> /2                           |

| Mode 1: 8-bit shift UART     | Variable                                       |

| Mode 2: 9-bit shift UART     | f <sub>PCLK</sub> /32 or f <sub>PCLK</sub> /64 |

| Mode 3: 9-bit shift UART     | Variable                                       |

There are several ways to generate the baud rate clock for the serial port, depending on the mode in which it is operating. In mode 0, the baud rate for the transfer is fixed at  $f_{PCLK}/2$ . In mode 2, the baud rate is generated internally based on the UART input clock and can be configured to either  $f_{PCLK}/32$  or  $f_{PCLK}/64$ . The variable baud rate is set by either the underflow rate on the dedicated baud-rate generator, or by the overflow rate on Timer 1.

115.2 kHz, using different module clock frequencies. The fractional divider is enabled (fractional divider mode) and the corresponding parameter settings are shown.

#### Table 27 Deviation Error for UART with Fractional Divider enabled

| f <sub>PCLK</sub> | Prescaling Factor<br>(2 <sup>BRPRE</sup> ) | Reload Value<br>(BR_VALUE + 1) | STEP                   | Deviation<br>Error |

|-------------------|--------------------------------------------|--------------------------------|------------------------|--------------------|

| 26.67 MHz         | 1                                          | 10 (A <sub>H</sub> )           | 177 (B1 <sub>H</sub> ) | +0.03 %            |

| 13.33 MHz         | 1                                          | 7 (7 <sub>H</sub> )            | 248 (F8 <sub>H</sub> ) | +0.11 %            |

| 6.67 MHz          | 1                                          | 3 (3 <sub>H</sub> )            | 212 (D4 <sub>H</sub> ) | -0.16 %            |

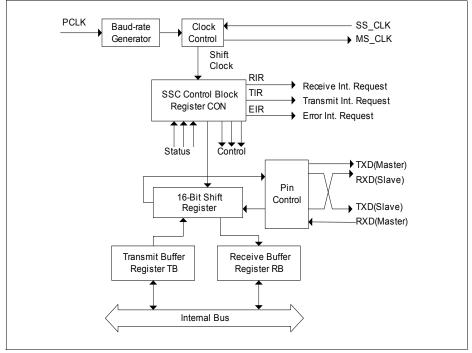

Data is transmitted or received on lines TXD and RXD, which are normally connected to the pins MTSR (Master Transmit/Slave Receive) and MRST (Master Receive/Slave Transmit). The clock signal is output via line MS\_CLK (Master Serial Shift Clock) or input via line SS\_CLK (Slave Serial Shift Clock). Both lines are normally connected to the pin SCLK. Transmission and reception of data are double-buffered.

Figure 31 shows the block diagram of the SSC.

Figure 31 SSC Block Diagram

# XC866

#### **Functional Description**

# 3.18 Analog-to-Digital Converter

The XC866 includes a high-performance 10-bit Analog-to-Digital Converter (ADC) with eight multiplexed analog input channels. The ADC uses a successive approximation technique to convert the analog voltage levels from up to eight different sources. The analog input channels of the ADC are available at Port 2.

#### Features:

- Successive approximation

- 8-bit or 10-bit resolution (TUE of ± 1 LSB and ± 2 LSB, respectively)

- Eight analog channels

- · Four independent result registers

- Result data protection for slow CPU access (wait-for-read mode)

- · Single conversion mode

- Autoscan functionality

- · Limit checking for conversion results

- Data reduction filter (accumulation of up to 2 conversion results)

- · Two independent conversion request sources with programmable priority

- Selectable conversion request trigger

- · Flexible interrupt generation with configurable service nodes

- · Programmable sample time

- · Programmable clock divider

- · Cancel/restart feature for running conversions

- · Integrated sample and hold circuitry

- · Compensation of offset errors

- · Low power modes

# 4 Electrical Parameters

**Chapter 4** provides the characteristics of the electrical parameters which are implementation-specific for the XC866.

Note: The electrical parameters are valid for the XC866-4FR and XC866-2FR. The electrical parameters for the ROM variants and XC866-1FR are preliminary, differences from XC866-4FR and XC866-2FR are stated explicitly.

#### 4.1 General Parameters

The general parameters are described here to aid the users in interpreting the parameters mainly in **Section 4.2** and **Section 4.3**.

#### 4.1.1 Parameter Interpretation

The parameters listed in this section represent partly the characteristics of the XC866 and partly its requirements on the system. To aid interpreting the parameters easily when evaluating them for a design, they are indicated by the abbreviations in the "Symbol" column:

• cc

These parameters indicate **C**ontroller **C**haracteristics, which are distinctive features of the XC866 and must be regarded for a system design.

• SR

These parameters indicate **S**ystem **R**equirements, which must be provided by the microcontroller system in which the XC866 is designed in.

#### 4.1.2 Absolute Maximum Rating

Maximum ratings are the extreme limits to which the XC866 can be subjected to without permanent damage.

| Table 32 | Absolute Maximum Rating Parameters |

|----------|------------------------------------|

|----------|------------------------------------|

| Parameter                                                    | Symbol            | Lim  | Limit Values                           |    | Notes                |

|--------------------------------------------------------------|-------------------|------|----------------------------------------|----|----------------------|

|                                                              |                   | min. | max.                                   |    |                      |

| Ambient temperature                                          | T <sub>A</sub>    | -40  | 125                                    | °C | under bias           |

| Storage temperature                                          | T <sub>ST</sub>   | -65  | 150                                    | °C |                      |

| Junction temperature                                         | TJ                | -40  | 150                                    | °C | under bias           |

| Voltage on power supply pin with respect to $V_{\rm SS}$     | V <sub>DDP</sub>  | -0.5 | 6                                      | V  |                      |

| Voltage on core supply pin with respect to $V_{\rm SS}$      | V <sub>DDC</sub>  | -0.5 | 3.25                                   | V  |                      |

| Voltage on any pin with respect to $V_{\rm SS}$              | V <sub>IN</sub>   | -0.5 | V <sub>DDP</sub> +<br>0.5 or<br>max. 6 | V  | Whatever is<br>lower |

| Input current on any pin during overload condition           | I <sub>IN</sub>   | -10  | 10                                     | mA |                      |

| Absolute sum of all input currents during overload condition | $\Sigma  I_{IN} $ | -    | 50                                     | mA |                      |

Note: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. During absolute maximum rating overload conditions ( $V_{IN} > V_{DDP}$  or  $V_{IN} < V_{SS}$ ) the voltage on  $V_{DDP}$  pin with respect to ground ( $V_{SS}$ ) must not exceed the values defined by the absolute maximum ratings.

#### Table 34 Input/Output Characteristics (Operating Conditions apply)

| Parameter                                                                                                       | Symbol            |    | Limit Values                |                           | Unit | Test Conditions                                                                                  |  |

|-----------------------------------------------------------------------------------------------------------------|-------------------|----|-----------------------------|---------------------------|------|--------------------------------------------------------------------------------------------------|--|

|                                                                                                                 |                   |    | min.                        | max.                      |      | Remarks                                                                                          |  |

| Input low voltage at<br>XTAL1                                                                                   | V <sub>ILX</sub>  | SR | V <sub>SS</sub> -<br>0.5    | $0.3 \times V_{ m DDC}$   | V    |                                                                                                  |  |

| Input high voltage at XTAL1                                                                                     | V <sub>IHX</sub>  | SR | $0.7 \times V_{\text{DDC}}$ | V <sub>DDC</sub><br>+ 0.5 | V    |                                                                                                  |  |

| Pull-up current                                                                                                 | I <sub>PU</sub>   | SR | -                           | -10                       | μA   | V <sub>IH,min</sub>                                                                              |  |

|                                                                                                                 |                   |    | -150                        | -                         | μA   | V <sub>IL,max</sub>                                                                              |  |

| Pull-down current                                                                                               | $I_{PD}$          | SR | -                           | 10                        | μA   | V <sub>IL,max</sub>                                                                              |  |

|                                                                                                                 |                   |    | 150                         | -                         | μA   | V <sub>IH,min</sub>                                                                              |  |

| Input leakage current <sup>2)</sup>                                                                             | I <sub>OZ1</sub>  | CC | -1                          | 1                         | μA   | 0 < $V_{\rm IN}$ < $V_{\rm DDP}$ ,<br>$T_{\rm A} \le 125^{\circ}$ C , XC866-4FR<br>and XC866-2FR |  |

|                                                                                                                 |                   |    | -2.5                        | 1                         | μA   | $0 < V_{IN} < V_{DDP},$<br>$T_A \le 125^{\circ}C, XC866-1FR$<br>and ROM device                   |  |

| Input current at XTAL1                                                                                          | $I_{ILX}$         | CC | -10                         | 10                        | μA   |                                                                                                  |  |

| Overload current on any pin                                                                                     | I <sub>OV</sub>   | SR | -5                          | 5                         | mA   |                                                                                                  |  |

| Absolute sum of overload currents                                                                               | $\Sigma  I_{OV} $ | SR | -                           | 25                        | mA   | 3)                                                                                               |  |

| Voltage on any pin during $V_{\text{DDP}}$ power off                                                            | V <sub>PO</sub>   | SR | -                           | 0.3                       | V    | 4)                                                                                               |  |

| $\begin{tabular}{l} \hline Maximum current per \\ pin (excluding $V_{\rm DDP}$ and $V_{\rm SS}$) \end{tabular}$ | I <sub>M</sub>    | SR | -                           | 15                        | mA   |                                                                                                  |  |

| Maximum current for all pins (excluding $V_{\rm DDP}$ and $V_{\rm SS}$ )                                        | $\Sigma  I_{M} $  | SR | -                           | 60                        | mA   |                                                                                                  |  |

| Maximum current into $V_{\text{DDP}}$                                                                           | I <sub>MVDE</sub> | SR | -                           | 80                        | mA   |                                                                                                  |  |

| Maximum current out of $V_{\rm SS}$                                                                             | I <sub>MVSS</sub> | SR | -                           | 80                        | mA   |                                                                                                  |  |

# Table 39Power Supply Current Parameters (Operating Conditions apply;<br/> $V_{\text{DDP}}$ = 3.3V range)

| Parameter                           | Symbol           | Limit              | Limit Values       |    | <b>Test Condition</b>                  |

|-------------------------------------|------------------|--------------------|--------------------|----|----------------------------------------|

|                                     |                  | typ. <sup>1)</sup> | max. <sup>2)</sup> | 1  | Remarks                                |

| V <sub>DDP</sub> = 3.3V Range       |                  | -                  |                    | 4  |                                        |

| Active Mode                         | I <sub>DDP</sub> | 21.5               | 23.3               | mA | 3)                                     |

| Idle Mode                           | I <sub>DDP</sub> | 16.4               | 18.9               | mA | XC866-4FR,<br>XC866-2FR <sup>4)</sup>  |

|                                     |                  | 11.2               | 13.5               | mA | XC866-1FR,<br>ROM device <sup>4)</sup> |

| Active Mode with slow-down enabled  | I <sub>DDP</sub> | 6.8                | 8                  | mA | XC866-4FR,<br>XC866-2FR <sup>5)</sup>  |

|                                     |                  | 5.4                | 7.3                | mA | XC866-1FR,<br>ROM device <sup>5)</sup> |

| Idle Mode with slow-down<br>enabled | I <sub>DDP</sub> | 6.8                | 7.8                | mA | XC866-4FR,<br>XC866-2FR <sup>6)</sup>  |

|                                     |                  | 4.9                | 6.9                | mA | XC866-1FR,<br>ROM device <sup>6)</sup> |

<sup>1)</sup> The typical  $I_{\text{DDP}}$  values are periodically measured at  $T_{\text{A}}$  = + 25 °C and  $V_{\text{DDP}}$  = 3.3 V.

<sup>2)</sup> The maximum  $I_{\text{DDP}}$  values are measured under worst case conditions ( $T_{\text{A}}$  = + 125 °C and  $V_{\text{DDP}}$  = 3.6 V).

<sup>3)</sup> I<sub>DDP</sub> (active mode) is measured with: CPU clock and input clock to all peripherals running at 26.7 MHz(set by on-chip oscillator of 10 MHz and NDIV in PLL\_CON to 0010<sub>B</sub>), RESET =  $V_{DDP}$ , no load on ports.

<sup>4)</sup> I<sub>DDP</sub> (idle mode) is measured with: <u>CPU clock</u> disabled, watchdog timer disabled, input clock to all peripherals enabled and running at 26.7 MHz, <u>RESET</u> = V<sub>DDP</sub>, no load on ports.

<sup>5)</sup> I<sub>DDP</sub> (active mode with slow-down mode) is measured with: <u>CPU</u> clock and input clock to all peripherals running at 833 KHz by setting CLKREL in CMCON to 0101<sub>B</sub>, <u>RESET</u> = V<sub>DDP</sub>, no load on ports.

<sup>6)</sup> I<sub>DDP</sub> (idle mode with slow-down mode) is measured with: CPU clock disabled, watchdog timer disabled, input <u>clock to all peripherals enable and running at 833 KHz by setting CLKREL in CMCON to 0101<sub>B</sub>,, <u>RESET = V<sub>DDP</sub>, no load on ports.</u></u>

http://www.infineon.com