Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| <b>.</b>                   |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Details                    |                                                                               |

| Product Status             | Obsolete                                                                      |

| Core Processor             | XC800                                                                         |

| Core Size                  | 8-Bit                                                                         |

| Speed                      | 86MHz                                                                         |

| Connectivity               | LINbus, SSI, UART/USART                                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                         |

| Number of I/O              | 19                                                                            |

| Program Memory Size        | 16KB (16K x 8)                                                                |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 768 x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                   |

| Data Converters            | A/D 8x10b                                                                     |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 38-TFSOP (0.173", 4.40mm Width)                                               |

| Supplier Device Package    | PG-TSSOP-38                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/saf-xc866l-4fri-be |

XC866 Data Sheet

Revision History: 2007-10 V1.2

Previous Version: V 0.1, 2005-01

V1.0, 2006-02 V1.1, 2006-12

| Page | Subjects (major changes since last revision)                                                                    |

|------|-----------------------------------------------------------------------------------------------------------------|

| 3    | Device summary table is updated for Flash 4-Kb and ROM variants.                                                |

| 13   | Footnote is added to MBC pin; description of $V_{\rm DDP}$ pin is updated.                                      |

| 25   | Section on bit protection scheme and access type of register bit field PASSWD.PASS are updated.                 |

| 26   | Access type of PAGE bits of all module page registers are corrected to rwh.                                     |

| 29   | Access type of Px_DIR register bits are corrected to rwh                                                        |

| 38   | New bullet point on Flash delivery state is added to the feature list.                                          |

| 88   | Digital power supply voltage are differentiated for 5V and 3.3V variants.                                       |

| 89   | New parameters on XTAL1 hysteresis and Voltage on GPIO pins during $V_{\rm DDP}$ power-off condition are added. |

| 104  | Figure on Power-on reset timing is updated.                                                                     |

|      |                                                                                                                 |

## We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to:

mcdocu.comments@infineon.com

#### **Summary of Features**

### **Ordering Information**

The ordering code for Infineon Technologies microcontrollers provides an exact reference to the required product. This ordering code identifies:

- The derivative itself, i.e. its function set, the temperature range, and the supply voltage

- · the package and the type of delivery

For the available ordering codes for the XC866, please refer to your responsible sales representative or your local distributor.

As this document refers to all the derivatives, some descriptions may not apply to a specific product. For simplicity all versions are referred to by the term XC866 throughout this document.

# **General Device Information**

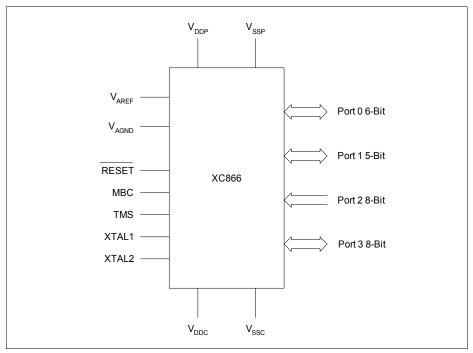

# 2.2 Logic Symbol

Figure 3 XC866 Logic Symbol

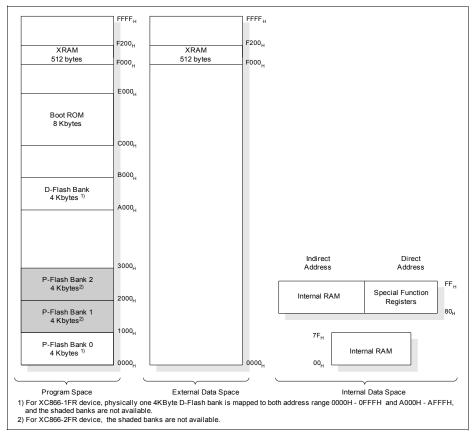

## 3.2 Memory Organization

The XC866 CPU operates in the following five address spaces:

- 8 Kbytes of Boot ROM program memory

- · 256 bytes of internal RAM data memory

- 512 bytes of XRAM memory (XRAM can be read/written as program memory or external data memory)

- · a 128-byte Special Function Register area

- 4/8/16 Kbytes of Flash program memory (Flash devices); or 8/16 Kbytes of ROM program memory, with additional 4 Kbytes of Flash (ROM devices)

Figure 6 illustrates the memory address spaces of the XC866-4FR device.

Figure 6 Memory Map of XC866 Flash Devices

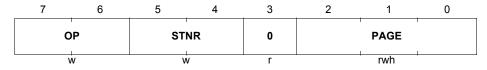

The page register has the following definition:

## MOD\_PAGE Page Register for module MOD

Reset Value: 00<sub>H</sub>

| Field | Bits  | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------|-------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PAGE  | [2:0] | rwh  | Page Bits When written, the value indicates the new page. When read, the value indicates the currently active page.                                                                                                                                                                                                                                                                                                                           |

| STNR  | [5:4] | w    | Storage Number This number indicates which storage bit field is the target of the operation defined by bit field OP. If OP = 10 <sub>B</sub> , the contents of PAGE are saved in STx before being overwritten with the new value. If OP = 11 <sub>B</sub> , the contents of PAGE are overwritten by the contents of STx. The value written to the bit positions of PAGE is ignored.  O ST0 is selected. O ST1 is selected. T ST3 is selected. |

Table 11 ADC Register Overview (cont'd)

| CA <sub>H</sub> |                                                                       |            |            | 6          | 5          | 4          | 3     | 2      | 1          | 0          |

|-----------------|-----------------------------------------------------------------------|------------|------------|------------|------------|------------|-------|--------|------------|------------|

|                 | ADC_CHINFR Reset: 00 <sub>H</sub>                                     | Bit Field  | CHINF      | CHINF      | CHINF      | CHINF      | CHINF | CHINF  | CHINF      | CHINF      |

|                 | Channel Interrupt Flag Register                                       |            | 7          | 6          | 5          | 4          | 3     | 2      | 1          | 0          |

|                 |                                                                       | Туре       | rh         | rh         | rh         | rh         | rh    | rh     | rh         | rh         |

| CB <sub>H</sub> | ADC_CHINCR Reset: 00 <sub>H</sub>                                     | Bit Field  | CHINC      | CHINC      | CHINC      | CHINC      | CHINC | CHINC  | CHINC      | CHINC      |

|                 | Channel Interrupt Clear Register                                      |            | 7          | 6          | 5          | 4          | 3     | 2      | 1          | 0          |

|                 |                                                                       | Type       | w          | W          | W          | W          | w     | W      | w          | w          |

| CCH             | ADC_CHINSR Reset: 00 <sub>H</sub>                                     | Bit Field  | CHINS      | CHINS      | CHINS      | CHINS      | CHINS | CHINS  | CHINS      | CHINS      |

|                 | Channel Interrupt Set Register                                        | _          | 7          | 6          | 5          | 4          | 3     | 2      | 1          | 0          |

|                 |                                                                       | Туре       | w          | W          | w          | W          | w     | W      | w          | w          |

| CD <sub>H</sub> | ADC_CHINPR Reset: 00 <sub>H</sub>                                     | Bit Field  | CHINP      | CHINP      | CHINP      | CHINP      | CHINP | CHINP  | CHINP      | CHINP      |

|                 | Channel Interrupt Node Pointer<br>Register                            | _          | 7          | 6          | 5          | 4          | 3     | 2      | 1          | 0          |

|                 |                                                                       | Туре       | rw         | rw         | rw         | rw         | rw    | rw     | rw         | rw         |

| CEH             | ADC_EVINFR Reset: 00 <sub>H</sub> Event Interrupt Flag Register       | Bit Field  | EVINF<br>7 | EVINF<br>6 | EVINF<br>5 | EVINF<br>4 | (     | )      | EVINF<br>1 | EVINF<br>0 |

|                 | Event interrupt Flag Register                                         | Time       | rh         | rh         | rh         | rh         |       |        | rh         | rh         |

| 05              | ADO EVINOR Deserti 00                                                 | Type       |            |            |            |            |       | r<br>) |            |            |

| CF <sub>H</sub> | ADC_EVINCR Reset: 00 <sub>H</sub> Event Interrupt Clear Flag Register | Bit Field  | EVINC<br>7 | EVINC<br>6 | EVINC<br>5 | EVINC<br>4 | ,     | )      | EVINC<br>1 | EVINC<br>0 |

|                 | Event interrupt olear riag register                                   | Туре       | w          | W          | w          | W          |       |        | w          | w          |

| D2 <sub>H</sub> | ADC_EVINSR Reset: 00 <sub>H</sub>                                     | Bit Field  | EVINS      | EVINS      | EVINS      | EVINS      | (     |        | EVINS      | EVINS      |

| DZH             | Event Interrupt Set Flag Register                                     | Dit i leiu | 7          | 6          | 5          | 4          | ,     | ,      | 1          | 0          |

|                 |                                                                       | Туре       | w          | w          | w          | w          |       | r      | w          | w          |

| D3 <sub>H</sub> | ADC EVINPR Reset: 00 <sub>H</sub>                                     | Bit Field  | EVINP      | EVINP      | EVINP      | EVINP      |       | )      | EVINP      | EVINP      |

| Бон             | Event Interrupt Node Pointer Register                                 | Dit i icia | 7          | 6          | 5          | 4          | `     | ,      | 1          | 0          |

|                 | ,                                                                     | Туре       | rw         | rw         | rw         | rw         |       | r      | rw         | rw         |

| RMAP =          | 0, Page 6                                                             | * .        |            |            |            |            |       |        |            |            |

| CA <sub>H</sub> | ADC_CRCR1 Reset: 00 <sub>H</sub>                                      | Bit Field  | CH7        | CH6        | CH5        | CH4        |       | (      | )          |            |

| - 11            | Conversion Request Control Register 1                                 |            |            |            |            |            |       |        |            |            |

|                 |                                                                       | Туре       | rwh        | rwh        | rwh        | rwh        |       |        | r          |            |

| СВн             | ADC_CRPR1 Reset: 00 <sub>H</sub>                                      | Bit Field  | CHP7       | CHP6       | CHP5       | CHP4       |       | (      | )          |            |

|                 | Conversion Request Pending                                            |            |            |            |            |            |       |        |            |            |

|                 | Register 1                                                            | Туре       | rwh        | rwh        | rwh        | rwh        |       | I      | r          |            |

| CCH             | ADC_CRMR1 Reset: 00 <sub>H</sub>                                      | Bit Field  | Rsv        | LDEV       | CLR        | SCAN       | ENSI  | ENTR   | EN         | GT         |

|                 | Conversion Request Mode Register 1                                    |            |            |            | PND        |            |       |        |            |            |

|                 |                                                                       | Type       | r          | W          | W          | rw         | rw    | rw     |            | w          |

| CD <sub>H</sub> | ADC_QMR0 Reset: 00 <sub>H</sub>                                       | Bit Field  | CEV        | TREV       | FLUSH      | CLRV       | TRMD  | ENTR   | EN         | GT         |

|                 | Queue Mode Register 0                                                 | Туре       | w          | W          | W          | W          | rw    | rw     | r          | W          |

| CE <sub>H</sub> | ADC_QSR0 Reset: 20 <sub>H</sub>                                       | Bit Field  | Rsv        | 0          | EMPTY      | EV         |       | (      | )          |            |

|                 | Queue Status Register 0                                               | Туре       | r          | r          | rh         | rh         |       |        | r          |            |

| CF <sub>H</sub> | ADC_Q0R0 Reset: 00 <sub>H</sub>                                       | Bit Field  | EXTR       | ENSI       | RF         | V          | 0     | R      | EQCHN      | R          |

|                 | Queue 0 Register 0                                                    | Туре       | rh         | rh         | rh         | rh         | r     |        | rh         |            |

| D2 <sub>H</sub> | ADC_QBUR0 Reset: 00 <sub>H</sub>                                      | Bit Field  | EXTR       | ENSI       | RF         | V          | 0     | R      | EQCHN      | R          |

| ••              | Queue Backup Register 0                                               | Туре       | rh         | rh         | rh         | rh         | r     |        | rh         |            |

| D2 <sub>H</sub> | ADC_QINR0 Reset: 00 <sub>H</sub>                                      | Bit Field  | EXTR       | ENSI       | RF         |            | )     | R      | EQCHN      | R          |

|                 | Queue Input Register 0                                                | Туре       | w          | w          | w          |            | r     |        | w          |            |

The Timer 2 SFRs can be accessed in the standard memory area (RMAP = 0).

# Table 12 Timer 2 Register Overview

| Addr            | Register Name                        |                        | Bit       | 7   | 6    | 5 | 4 | 3     | 2   | 1 | 0          |

|-----------------|--------------------------------------|------------------------|-----------|-----|------|---|---|-------|-----|---|------------|

| C0 <sub>H</sub> | T2_T2CON<br>Timer 2 Control Register | Reset: 00 <sub>H</sub> | Bit Field | TF2 | EXF2 | ( | ) | EXEN2 | TR2 | 0 | CP/<br>RL2 |

|                 |                                      |                        | Туре      | rwh | rwh  | ı | r | rw    | rwh | r | rw         |

# Table 13 CCU6 Register Overview (cont'd)

| Addr            | Register Name                                                                         | Bit               | 7              | 6           | 5               | 4           | 3           | 2           | 1           | 0           |  |

|-----------------|---------------------------------------------------------------------------------------|-------------------|----------------|-------------|-----------------|-------------|-------------|-------------|-------------|-------------|--|

| FD <sub>H</sub> | CCU6_CC61RH Reset: 00 <sub>H</sub>                                                    | Bit Field         | -              |             |                 |             | 1VH         |             |             |             |  |

| , DH            | Capture/Compare Register for Channel CC61 High                                        |                   |                |             |                 |             |             |             |             |             |  |

|                 |                                                                                       | Туре              |                |             |                 |             | h           |             |             |             |  |

| FE <sub>H</sub> | CCU6_CC62RL Reset: 00 <sub>H</sub> Capture/Compare Register for Channel CC62 Low      |                   |                |             |                 |             |             |             |             |             |  |

|                 |                                                                                       | Type              | rh             |             |                 |             |             |             |             |             |  |

| FF <sub>H</sub> | CCU6_CC62RH Reset: 00 <sub>H</sub> Capture/Compare Register for Channel CC62 High     | Bit Field Type    |                |             |                 |             | h           |             |             |             |  |

| PMAP =          | : 0, Page 2                                                                           | Туре              |                |             |                 |             | 11          |             |             |             |  |

| 9A <sub>H</sub> | CCU6_T12MSELL Reset: 00 <sub>H</sub>                                                  | Bit Field         |                | MSF         | EL61            |             |             | MSF         | EL60        |             |  |

| 57 tH           | T12 Capture/Compare Mode Select Register Low                                          | Туре              |                |             | w               |             |             |             | w           |             |  |

| OR.             | CCU6_T12MSELH Reset: 00 <sub>H</sub>                                                  | Bit Field         | DBYP           | 1           | W<br>HSYNC      |             |             |             | EL62        |             |  |

| 9B <sub>H</sub> | T12 Capture/Compare Mode Select Register High                                         |                   |                |             |                 |             |             |             |             |             |  |

| 00              | * *                                                                                   | Туре              | rw             | ENE 10      | rw              | FNOO        | FNICO       |             | W           | FNOO        |  |

| 9C <sub>H</sub> | CCU6_IENL Reset: 00 <sub>H</sub> Capture/Compare Interrupt Enable Register Low        | Bit Field         | ENT12<br>PM    | ENT12<br>OM | ENCC<br>62F     | ENCC<br>62R | ENCC<br>61F | ENCC<br>61R | ENCC<br>60F | ENCC<br>60R |  |

|                 | •                                                                                     | Туре              | rw             | rw          | rw              | rw          | rw          | rw          | rw          | rw          |  |

| 9D <sub>H</sub> | CCU6_IENH Reset: 00 <sub>H</sub> Capture/Compare Interrupt Enable Register High       | Bit Field         | ENSTR          | EN<br>IDLE  | EN<br>WHE       | EN<br>CHE   | 0           | EN<br>TRPF  | ENT13<br>PM | ENT13<br>CM |  |

|                 | , , , , , , , , , , , , , , , , , , ,                                                 | Туре              | rw             | rw          | rw              | rw          | r           | rw          | rw          | rw          |  |

| 9E <sub>H</sub> | CCU6_INPL Reset: 40 <sub>H</sub> Capture/Compare Interrupt Node                       | Bit Field         | INPCHE INPCC62 |             | INPCC61 INPCC60 |             |             |             |             |             |  |

|                 | Pointer Register Low                                                                  | Туре              | rw rw          |             |                 | w           | r           |             |             |             |  |

| 9F <sub>H</sub> | CCU6_INPH Reset: 39 <sub>H</sub> Capture/Compare Interrupt Node Pointer Register High | Bit Field         |                | 0           | INPT13          |             | INPT12      |             | INPERR      |             |  |

|                 |                                                                                       | Туре              |                | r           |                 | w           |             | W           |             | W           |  |

| A4 <sub>H</sub> | CCU6_ISSL Reset: 00 <sub>H</sub> Capture/Compare Interrupt Status Set Register Low    | Bit Field         | ST12P<br>M     | ST12O<br>M  | F               | R           | F           | SCC61<br>R  | F           | R           |  |

|                 | •                                                                                     | Туре              | W              | w           | W               | w           | W           | W           | W           | W           |  |

| A5 <sub>H</sub> | CCU6_ISSH Reset: 00 <sub>H</sub> Capture/Compare Interrupt Status Set                 | Bit Field         | SSTR           | SIDLE       | SWHE            |             |             | STRPF       | ST13<br>PM  | ST13<br>CM  |  |

|                 | Register High                                                                         | Туре              | W              | w           | w               | w           | W           | W           | w           | W           |  |

| A6 <sub>H</sub> | CCU6_PSLR Reset: 00 <sub>H</sub> Passive State Level Register                         | Bit Field         | PSL63          | 0           |                 |             |             | SL          |             |             |  |

|                 | -                                                                                     | Туре              | rwh            | r           |                 |             |             | vh          |             |             |  |

| A7 <sub>H</sub> | CCU6_MCMCTR Reset: 00 <sub>H</sub> Multi-Channel Mode Control Register                | Bit Field         |                | 0           |                 | SYN         | 0           |             | SWSEL       |             |  |

| Ε.Δ.            | •                                                                                     | Type              |                | r<br>T10    |                 | W           | r           | <u> </u>    | T42         | T40         |  |

| FA <sub>H</sub> | CCU6_TCTR2L Reset: 00 <sub>H</sub> Timer Control Register 2 Low                       | Bit Field         | 0              |             | TED             |             | T13TEC      |             | T13<br>SSC  | T12<br>SSC  |  |

|                 |                                                                                       | Туре              | r              |             | W               |             | rw          |             | rw          | rw          |  |

| FB <sub>H</sub> | CCU6_TCTR2H Reset: 00 <sub>H</sub> Timer Control Register 2 High                      | Bit Field         |                |             | )<br>r          |             |             | RSEL        |             | RSEL        |  |

| EC              | CCU6_MODCTRL Reset: 00 <sub>H</sub>                                                   | Type<br>Bit Field | MC             | 0           | r               |             |             | W ODEN      | r           | w           |  |

| FC <sub>H</sub> | Modulation Control Register Low                                                       |                   | MEN            |             | T12MODEN        |             |             |             |             |             |  |

| ED.             | COULD MODOTDI'                                                                        | Type              | TW FOT40       | r           | rw              |             |             |             |             |             |  |

| FD <sub>H</sub> | CCU6_MODCTRH Reset: 00 <sub>H</sub> Modulation Control Register High                  | Bit Field         | ECT13<br>O     | 0           | T13MODEN        |             |             |             |             |             |  |

|                 |                                                                                       | Туре              | rw             | r           | rw              |             |             |             |             |             |  |

| FE <sub>H</sub> | CCU6_TRPCTRL Reset: 00 <sub>H</sub> Trap Control Register Low                         | Bit Field         |                |             | 0               |             |             |             | TRPM1       | -           |  |

|                 | Trap Contion Register Low                                                             | Type              | <u> </u>       |             | r               |             |             | rw          | rw          | rw          |  |

## Table 13 CCU6 Register Overview (cont'd)

| Addr            | Register Name                                                          | Bit       | 7              | 6            | 5            | 4          | 3            | 2          | 1            | 0          |  |

|-----------------|------------------------------------------------------------------------|-----------|----------------|--------------|--------------|------------|--------------|------------|--------------|------------|--|

| FF <sub>H</sub> | CCU6_TRPCTRH Reset: 00 <sub>H</sub>                                    | Bit Field | TRPPE          | TRPEN        |              |            | TRE          | PEN        |              | I.         |  |

|                 | Trap Control Register High                                             |           | N              | 13           |              |            |              |            |              |            |  |

|                 |                                                                        | Type      | rw             | rw           |              |            | r            | w          |              |            |  |

| RMAP =          | 0, Page 3                                                              |           |                |              |              |            |              |            |              |            |  |

| 9A <sub>H</sub> | CCU6_MCMOUTL Reset: 00 <sub>H</sub> Multi-Channel Mode Output Register | Bit Field | 0              | R            |              |            | МС           | MP         |              |            |  |

|                 | Low                                                                    | Type      | r              | rh           |              |            | r            | h          |              |            |  |

| 9B <sub>H</sub> | CCU6_MCMOUTH Reset: 00 <sub>H</sub> Multi-Channel Mode Output Register | Bit Field | (              | 0            |              | CURH       |              |            | EXPH         |            |  |

|                 | High                                                                   | Туре      |                | r            |              | rh         |              |            | rh           |            |  |

| 9C <sub>H</sub> | CCU6_ISL Reset: 00 <sub>H</sub> Capture/Compare Interrupt Status       | Bit Field | T12PM          | T12OM        | ICC62F       | ICC62<br>R | ICC61F       | ICC61<br>R | ICC60F       | ICC60<br>R |  |

|                 | Register Low                                                           | Type      | rh             | rh           | rh           | rh         | rh           | rh         | rh           | rh         |  |

| 9D <sub>H</sub> | CCU6_ISH Reset: 00 <sub>H</sub> Capture/Compare Interrupt Status       | Bit Field | STR            | IDLE         | WHE          | CHE        | TRPS         | TRPF       | T13PM        | T13CM      |  |

|                 | Register High                                                          | Type      | rh             | rh           | rh           | rh         | rh           | rh         | rh           | rh         |  |

| 9E <sub>H</sub> | CCU6_PISEL0L Reset: 00 <sub>H</sub>                                    | Bit Field | IST            | RP           | ISC          | C62        | ISC          | C61        | ISC          | C60        |  |

|                 | Port Input Select Register 0 Low                                       | Туре      | r              | w            | r            | N          | r            | w          | rw rw        |            |  |

| 9F <sub>H</sub> | CCU6_PISEL0H Reset: 00 <sub>H</sub> Port Input Select Register 0 High  | Bit Field | IST12HR ISPOS2 |              | ISPOS1       |            | ISPOS0       |            |              |            |  |

|                 |                                                                        | Type      | rw rw rw       |              |              |            |              | rw         |              |            |  |

| A4 <sub>H</sub> | CCU6_PISEL2 Reset: 00 <sub>H</sub>                                     | Bit Field | 0 IST13I       |              |              |            |              |            | 3HR          |            |  |

|                 | Port Input Select Register 2                                           | Туре      | r rw           |              |              |            |              |            |              | W          |  |

| FA <sub>H</sub> | CCU6_T12L Reset: 00 <sub>H</sub>                                       | Bit Field | T12CVL         |              |              |            |              |            |              |            |  |

|                 | Timer T12 Counter Register Low                                         | Туре      | rwh            |              |              |            |              |            |              |            |  |

| FB <sub>H</sub> | CCU6_T12H Reset: 00 <sub>H</sub>                                       | Bit Field | T12CVH         |              |              |            |              |            |              |            |  |

|                 | Timer T12 Counter Register High                                        | Туре      | rwh            |              |              |            |              |            |              |            |  |

| FC <sub>H</sub> | CCU6_T13L Reset: 00 <sub>H</sub>                                       | Bit Field | T13CVL         |              |              |            |              |            |              |            |  |

|                 | Timer T13 Counter Register Low                                         | Туре      | rwh            |              |              |            |              |            |              |            |  |

| $FD_H$          | CCU6_T13H Reset: 00 <sub>H</sub>                                       | Bit Field |                |              |              | T13        | CVH          |            |              |            |  |

|                 | Timer T13 Counter Register High                                        | Туре      |                |              |              | rv         | vh           |            |              |            |  |

| FE <sub>H</sub> | CCU6_CMPSTATL Reset: 00 <sub>H</sub> Compare State Register Low        | Bit Field | 0              | CC63<br>ST   | CCPO<br>S2   | CCPO<br>S1 | CCPO<br>S0   | CC62<br>ST | CC61<br>ST   | CC60<br>ST |  |

|                 |                                                                        | Туре      | r              | rh           | rh           | rh         | rh           | rh         | rh           | rh         |  |

| FF <sub>H</sub> | CCU6_CMPSTATH Reset: 00 <sub>H</sub> Compare State Register High       | Bit Field | T13IM          | COUT<br>63PS | COUT<br>62PS | CC62<br>PS | COUT<br>61PS | CC61<br>PS | COUT<br>60PS | CC60<br>PS |  |

|                 |                                                                        | Туре      | rwh            | rwh          | rwh          | rwh        | rwh          | rwh        | rwh          | rwh        |  |

The SSC SFRs can be accessed in the standard memory area (RMAP = 0).

# Table 14 SSC Register Overview

| Addr            | Register Name                                                                 |  | Bit       | 7  | 6  | 5  | 4  | 3  | 2   | 1   | 0   |

|-----------------|-------------------------------------------------------------------------------|--|-----------|----|----|----|----|----|-----|-----|-----|

| RMAP =          | 0                                                                             |  | •         |    |    |    |    |    |     |     |     |

| A9 <sub>H</sub> | A9 <sub>H</sub> SSC_PISEL Reset: 00 <sub>H</sub> Port Input Select Register   |  | Bit Field |    |    | 0  |    |    | CIS | SIS | MIS |

|                 |                                                                               |  | Туре      | r  |    |    |    |    | rw  | rw  | rw  |

| $AA_H$          | AA <sub>H</sub> SSC_CONL Control Register Low Programming Mode Operating Mode |  | Bit Field | LB | PO | PH | HB |    | В   | M   |     |

|                 |                                                                               |  | Туре      | rw | rw | rw | rw | rw |     |     |     |

|                 |                                                                               |  | Bit Field | 0  |    |    |    | BC |     |     |     |

|                 |                                                                               |  | Туре      |    |    | r  |    |    | r   | h   |     |

# 3.3 Flash Memory

The Flash memory provides an embedded user-programmable non-volatile memory, allowing fast and reliable storage of user code and data. It is operated from a single 2.5 V supply from the Embedded Voltage Regulator (EVR) and does not require additional programming or erasing voltage. The sectorization of the Flash memory allows each sector to be erased independently.

#### **Features**

- In-System Programming (ISP) via UART

- In-Application Programming (IAP)

- Error Correction Code (ECC) for dynamic correction of single-bit errors

- Background program and erase operations for CPU load minimization

- Support for aborting erase operation

- Minimum program width<sup>1)</sup> of 32-byte for D-Flash and 32-byte for P-Flash

- 1-sector minimum erase width

- · 1-byte read access

- Flash is delivered in erased state (read all zeros)

- Operating supply voltage: 2.5 V ± 7.5 %

- Read access time: 3 × t<sub>CCLK</sub> = 112.5 ns<sup>2)</sup>

- Program time: 209440 /  $f_{SYS}$  = 2.6 ms<sup>3)</sup>

- Erase time:  $8175360 / f_{SYS} = 102 \text{ ms}^{3)}$

Data Sheet 38 V1.2. 2007-10

P-Flash: 32-byte wordline can only be programmed once, i.e., one gate disturb allowed. D-Flash: 32-byte wordline can be programmed twice, i.e., two gate disturbs allowed.

$f_{\rm sys}$  = 80 MHz ± 7.5% ( $f_{\rm CCLK}$  = 26.7 MHz ± 7.5 %) is the maximum frequency range for Flash read access.

<sup>&</sup>lt;sup>3)</sup>  $f_{\rm sys}$  = 80 MHz ± 7.5% is the only frequency range for Flash programming and erasing.  $f_{\rm sysmin}$  is used for obtaining the worst case timing.

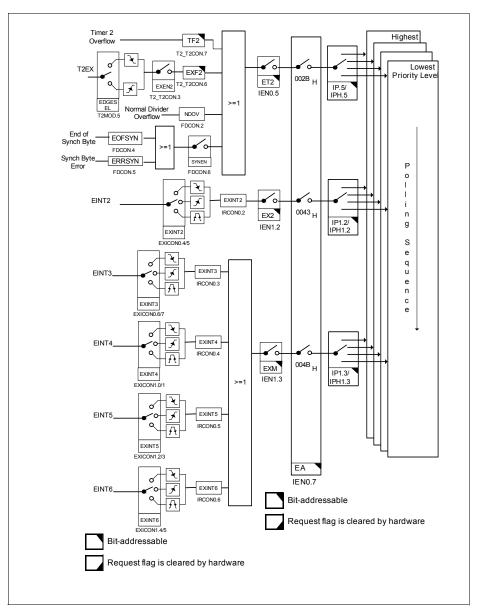

Figure 15 Interrupt Request Sources (Part 2)

115.2 kHz, using different module clock frequencies. The fractional divider is enabled (fractional divider mode) and the corresponding parameter settings are shown.

Table 27 Deviation Error for UART with Fractional Divider enabled

| f <sub>PCLK</sub> | Prescaling Factor (2 <sup>BRPRE</sup> ) | Reload Value<br>(BR_VALUE + 1) | STEP                   | Deviation<br>Error |

|-------------------|-----------------------------------------|--------------------------------|------------------------|--------------------|

| 26.67 MHz         | 1                                       | 10 (A <sub>H</sub> )           | 177 (B1 <sub>H</sub> ) | +0.03 %            |

| 13.33 MHz         | 1                                       | 7 (7 <sub>H</sub> )            | 248 (F8 <sub>H</sub> ) | +0.11 %            |

| 6.67 MHz          | 1                                       | 3 (3 <sub>H</sub> )            | 212 (D4 <sub>H</sub> ) | -0.16 %            |

## 3.18 Analog-to-Digital Converter

The XC866 includes a high-performance 10-bit Analog-to-Digital Converter (ADC) with eight multiplexed analog input channels. The ADC uses a successive approximation technique to convert the analog voltage levels from up to eight different sources. The analog input channels of the ADC are available at Port 2.

#### Features:

- Successive approximation

- 8-bit or 10-bit resolution (TUE of ± 1 LSB and ± 2 LSB, respectively)

- · Eight analog channels

- · Four independent result registers

- Result data protection for slow CPU access (wait-for-read mode)

- · Single conversion mode

- · Autoscan functionality

- · Limit checking for conversion results

- Data reduction filter (accumulation of up to 2 conversion results)

- · Two independent conversion request sources with programmable priority

- Selectable conversion request trigger

- · Flexible interrupt generation with configurable service nodes

- · Programmable sample time

- · Programmable clock divider

- · Cancel/restart feature for running conversions

- Integrated sample and hold circuitry

- Compensation of offset errors

- Low power modes

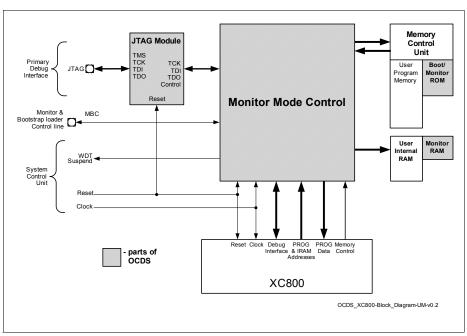

Figure 35 OCDS Block Diagram

# 3.19.1 JTAG ID Register

This is a read-only register located inside the JTAG module, and is used to recognize the device(s) connected to the JTAG interface. Its content is shifted out when INSTRUCTION register contains the IDCODE command (opcode  $04_{\rm H}$ ), and the same is also true immediately after reset.

The JTAG ID register contents for the XC866 devices are given in Table 31.

Table 31 JTAG ID Summary

| Device Type | <b>Device Name</b> | JTAG ID                |  |

|-------------|--------------------|------------------------|--|

| Flash       | XC866L-4FR         | 1010 0083 <sub>H</sub> |  |

|             | XC866-4FR          | 100F 5083 <sub>H</sub> |  |

|             | XC866L-2FR         | 1010 2083 <sub>H</sub> |  |

|             | XC866-2FR          | 1010 1083 <sub>H</sub> |  |

|             | XC866L-1FR         | 1013 8083 <sub>H</sub> |  |

|             | XC866-1FR          | 1013 8083 <sub>H</sub> |  |

| Table 31 | JTAG ID Summary |

|----------|-----------------|

|----------|-----------------|

| ROM | XC866L-4RR | 1013 9083 <sub>H</sub> |

|-----|------------|------------------------|

|     | XC866-4RR  | 1013 9083 <sub>H</sub> |

|     | XC866L-2RR | 1013 9083 <sub>H</sub> |

|     | XC866-2RR  | 1013 9083 <sub>H</sub> |

# 3.20 Identification Register

The XC866 identity register is located at Page 1 of address B3<sub>H</sub>.

ID Identity Register

Reset Value: 0000 0010<sub>B</sub>

2 1 0

| 7 | 6 | 5      | 4 | 3 | 2 | 1     | 0 |

|---|---|--------|---|---|---|-------|---|

|   |   | PRODID |   |   |   | VERID |   |

|   | į | 1      | 1 | 1 |   | į     |   |

|   |   | r      |   |   |   | r     |   |

| Field  | Bits  | Туре | Description                      |

|--------|-------|------|----------------------------------|

| VERID  | [2:0] | r    | Version ID<br>010 <sub>B</sub>   |

| PRODID | [7:3] | r    | Product ID<br>00000 <sub>B</sub> |

Table 34 Input/Output Characteristics (Operating Conditions apply)

| Parameter                                                                                                                                                | Symbol            |    | Limit Values          |                        | Unit | Test Conditions                                                                       |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----|-----------------------|------------------------|------|---------------------------------------------------------------------------------------|--|

|                                                                                                                                                          |                   |    | min.                  | max.                   |      | Remarks                                                                               |  |

| Input low voltage at XTAL1                                                                                                                               | $V_{ILX}$         | SR | V <sub>SS</sub> - 0.5 | $V_{\rm DDC}$          | V    |                                                                                       |  |

| Input high voltage at XTAL1                                                                                                                              | $V_{IHX}$         | SR | $V_{ m DDC}$          | V <sub>DDC</sub> + 0.5 | V    |                                                                                       |  |

| Pull-up current                                                                                                                                          | $I_{PU}$          | SR | _                     | -10                    | μΑ   | $V_{IH,min}$                                                                          |  |

|                                                                                                                                                          |                   |    | -150                  | _                      | μΑ   | $V_{IL,max}$                                                                          |  |

| Pull-down current                                                                                                                                        | $I_{PD}$          | SR | _                     | 10                     | μΑ   | $V_{IL,max}$                                                                          |  |

|                                                                                                                                                          |                   |    | 150                   | _                      | μΑ   | $V_{IH,min}$                                                                          |  |

| Input leakage current <sup>2)</sup>                                                                                                                      | $I_{OZ1}$         | CC | -1                    | 1                      | μΑ   | 0 < $V_{\rm IN}$ < $V_{\rm DDP}$ ,<br>$T_{\rm A} \le$ 125°C , XC866-4FR and XC866-2FR |  |

|                                                                                                                                                          |                   |    | -2.5                  | 1                      | μΑ   | 0 < $V_{\rm IN}$ < $V_{\rm DDP}$ ,<br>$T_{\rm A}$ ≤ 125°C, XC866-1FR and ROM device   |  |

| Input current at XTAL1                                                                                                                                   | $I_{ILX}$         | CC | -10                   | 10                     | μΑ   |                                                                                       |  |

| Overload current on any pin                                                                                                                              | $I_{OV}$          | SR | -5                    | 5                      | mA   |                                                                                       |  |

| Absolute sum of overload currents                                                                                                                        | $\Sigma  I_{OV} $ | SR | _                     | 25                     | mA   | 3)                                                                                    |  |

| Voltage on any pin during $V_{\rm DDP}$ power off                                                                                                        | $V_{PO}$          | SR | _                     | 0.3                    | V    | 4)                                                                                    |  |

| $\label{eq:maximum}                                   $                                                                                                  | $I_{M}$           | SR | -                     | 15                     | mA   |                                                                                       |  |

| $\label{eq:maximum} \begin{array}{l} \text{Maximum current for all} \\ \text{pins (excluding } V_{\text{DDP}} \\ \text{and } V_{\text{SS}}) \end{array}$ | $\Sigma  I_{M} $  | SR | -                     | 60                     | mA   |                                                                                       |  |

| $\begin{array}{c} {\rm Maximum~current~into} \\ {\cal V}_{\rm DDP} \end{array}$                                                                          | $I_{MVDD}$        | SR | _                     | 80                     | mA   |                                                                                       |  |

| $\begin{array}{c} \text{Maximum current out of} \\ V_{\text{SS}} \end{array}$                                                                            | $I_{MVSS}$        | SR | _                     | 80                     | mA   |                                                                                       |  |

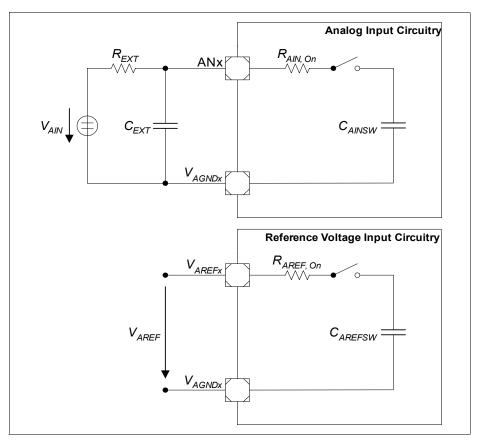

Figure 37 ADC Input Circuits

# 4.2.3.1 ADC Conversion Timing

```

Conversion time, t_C = t_{ADC} \times (1 + r \times (3 + n + STC)), where r = CTC + 2 for CTC = 00_B, 01_B or 10_B, r = 32 for CTC = 11_B, CTC = Conversion Time Control (GLOBCTR.CTC), STC = Sample Time Control (INPCR0.STC), n = 8 or 10 (for 8-bit and 10-bit conversion respectively), t_{ADC} = 1 / f_{ADC}

```

## 4.2.4 Power Supply Current

Table 37 Power Supply Current Parameters (Operating Conditions apply;  $V_{\text{DDP}} = 5V \text{ range}$ )

| Parameter                          | Symbol       | Limit              | Values             | Unit | Test Condition<br>Remarks              |  |

|------------------------------------|--------------|--------------------|--------------------|------|----------------------------------------|--|

|                                    |              | typ. <sup>1)</sup> | max. <sup>2)</sup> |      |                                        |  |

| $V_{\rm DDP}$ = 5V Range           |              | 1                  |                    | •    |                                        |  |

| Active Mode                        | $I_{DDP}$    | 22.6               | 24.5               | mA   | 3)                                     |  |

| Idle Mode                          | $I_{DDP}$    | 17.2               | 19.7               | mA   | XC866-4FR,<br>XC866-2FR <sup>4)</sup>  |  |

|                                    |              | 12.5               | 14                 | mA   | XC866-1FR,<br>ROM device <sup>4)</sup> |  |

| Active Mode with slow-down enabled | $I_{DDP}$    | 7.2                | 8.2                | mA   | XC866-4FR,<br>XC866-2FR <sup>5)</sup>  |  |

|                                    |              | 5.6                | 7.5                | mA   | XC866-1FR,<br>ROM device <sup>5)</sup> |  |

| Idle Mode with slow-down enabled   | vn $I_{DDP}$ | 7.1                | 8                  | mA   | XC866-4FR,<br>XC866-2FR <sup>6)</sup>  |  |

|                                    |              | 5.1                | 7.2                | mA   | XC866-1FR,<br>ROM device <sup>6)</sup> |  |

<sup>1)</sup> The typical  $I_{\rm DDP}$  values are periodically measured at  $T_{\rm A}$  = + 25 °C and  $V_{\rm DDP}$  = 5.0 V.

The maximum  $I_{\rm DDP}$  values are measured under worst case conditions ( $T_{\rm A}$  = + 125 °C and  $V_{\rm DDP}$  = 5.5 V).

<sup>3)</sup> I<sub>DDP</sub> (active mode) is measured with: CPU clock and input clock to all peripherals running at 26.7 MHz(set by on-chip oscillator of 10 MHz and NDIV in PLL\_CON to 0010<sub>B</sub>), RESET = V<sub>DDP</sub>, no load on ports.

<sup>4)</sup> I<sub>DDP</sub> (idle mode) is measured with: <u>CPU clock</u> disabled, watchdog timer disabled, input clock to all peripherals enabled and running at 26.7 MHz, <u>RESET</u> = V<sub>DDP</sub>, no load on ports.

<sup>5)</sup> I<sub>DDP</sub> (active mode with slow-down mode) is measured with: CPU clock and input clock to all peripherals running at 833 KHz by setting CLKREL in CMCON to 0101<sub>B</sub>, RESET = V<sub>DDP</sub>, no load on ports.

<sup>6)</sup> I<sub>DDP</sub> (idle mode with slow-down mode) is measured with: CPU clock disabled, watchdog timer disabled, input clock to all peripherals enabled and running at 833 KHz by setting CLKREL in CMCON to 0101<sub>B</sub>, RESET = V<sub>DDP</sub>, no load on ports.

Table 40 Power Down Current (Operating Conditions apply;  $V_{\rm DDP}$  = 3.3V range )

| Parameter                     | Symbol    | Limit                                 | Values | Unit | Test Condition                                               |  |

|-------------------------------|-----------|---------------------------------------|--------|------|--------------------------------------------------------------|--|

|                               |           | typ. <sup>1)</sup> max. <sup>2)</sup> |        |      | Remarks                                                      |  |

| $V_{\rm DDP}$ = 3.3V Range    |           |                                       | 1      |      |                                                              |  |

| Power-Down Mode <sup>3)</sup> | $I_{PDP}$ | 1                                     | 10     | μΑ   | $T_{A} = + 25  {}^{\circ}\text{C.}^{4)}$                     |  |

|                               |           | -                                     | 30     | μΑ   | $T_A$ = + 85 °C, XC866-<br>4FR, XC866-2FR <sup>4)5)</sup>    |  |

|                               |           | -                                     | 35     | μΑ   | $T_{A}$ = + 85 °C, XC866-<br>1FR, ROM device <sup>4)5)</sup> |  |

<sup>1)</sup> The typical  $I_{PDP}$  values are measured at  $V_{DDP}$  = 3.3 V.

$<sup>^{2)}~</sup>$  The maximum  $I_{\rm PDP}$  values are measured at  $V_{\rm DDP}$  = 3.6 V.

<sup>&</sup>lt;sup>3)</sup>  $I_{PDP}$  (power-down mode) has a maximum value of 200  $\mu A$  at  $T_A$  = + 125 °C.

<sup>4)</sup> I<sub>PDP</sub> (power-down mode) is measured with: RESET = V<sub>DDP</sub>, V<sub>AGND</sub>= V<sub>SS</sub>, RXD/INT0= V<sub>DDP</sub>; rest of the ports are programmed to be input with either internal pull devices enabled or driven externally to ensure no floating inputs.

<sup>&</sup>lt;sup>5)</sup> Not subject to production test, verified by design/characterization.

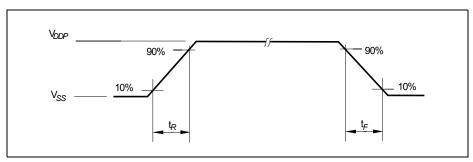

# 4.3.2 Output Rise/Fall Times

Table 41 Output Rise/Fall Times Parameters (Operating Conditions apply)

| Parameter                  | Symbol                          | Limit<br>Values |      | Unit | Test Conditions      |  |  |

|----------------------------|---------------------------------|-----------------|------|------|----------------------|--|--|

|                            |                                 | min.            | max. |      |                      |  |  |

| $V_{\rm DDP}$ = 5V Range   | "                               | '               |      | '    | 1                    |  |  |

| Rise/fall times 1) 2)      | t <sub>R</sub> , t <sub>F</sub> | _               | 10   | ns   | 20 pF. <sup>3)</sup> |  |  |

| $V_{\rm DDP}$ = 3.3V Range | "                               | '               |      | '    | 1                    |  |  |

| Rise/fall times 1) 2)      | t <sub>R</sub> , t <sub>F</sub> | _               | 10   | ns   | 20 pF. <sup>4)</sup> |  |  |

<sup>1)</sup> Rise/Fall time measurements are taken with 10% - 90% of the pad supply.

$<sup>^{\</sup>rm 4)}$  Additional rise/fall time valid for C  $_{\rm L}$  = 20pF - 100pF @ 0.225 ns/pF.

Figure 41 Rise/Fall Times Parameters

<sup>&</sup>lt;sup>2)</sup> Not all parameters are 100% tested, but are verified by design/characterization and test correlation.

$<sup>^{3)}</sup>$  Additional rise/fall time valid for  $C_L$  = 20pF - 100pF @ 0.125 ns/pF.

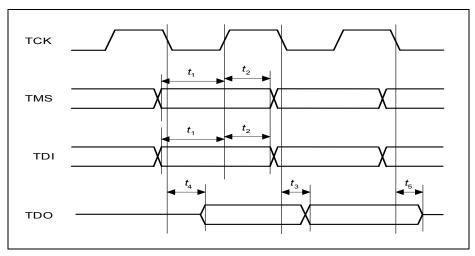

Table 45 JTAG Timing (Operating Conditions apply;  $C_L = 50 \text{ pF}$ )

| Parameter                                     |                       | mbol | Lir  | Unit |    |

|-----------------------------------------------|-----------------------|------|------|------|----|

|                                               |                       |      | min  | max  |    |

| TMS setup to TCK _r                           | $t_1$                 | SR   | 8.0  | -    | ns |

| TMS hold to TCK _r                            | $t_2$                 | SR   | 5.0  | -    | ns |

| TDI setup to TCK _r                           | $t_1$                 | SR   | 11.0 | -    | ns |

| TDI hold to TCK _/                            | $t_2$                 | SR   | 6.0  | _    | ns |

| TDO valid output from TCK ¬_                  | $t_3$                 | CC   | _    | 23   | ns |

| TDO high impedance to valid output from TCK ¬ | <i>t</i> <sub>4</sub> | CC   | _    | 26   | ns |

| TDO valid output to high impedance from TCK ٦ | <i>t</i> <sub>5</sub> | CC   | _    | 18   | ns |

Figure 44 JTAG Timing