Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                     |

| Core Processor             | XC800                                                                        |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 86MHz                                                                        |

| Connectivity               | SSI, UART/USART                                                              |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 19                                                                           |

| Program Memory Size        | 8KB (8K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 768 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                  |

| Data Converters            | A/D 8x10b                                                                    |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 38-TFSOP (0.173", 4.40mm Width)                                              |

| Supplier Device Package    | PG-TSSOP-38                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/sak-xc866-2fri-bc |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# XC866 8-Bit Single-Chip Microcontroller

# Microcontrollers

Never stop thinking

# **General Device Information**

# 2.4 Pin Definitions and Functions

# Table 3 Pin Definitions and Functions

| Symbol | Pin<br>Number | Туре | Reset<br>State | Function                            |                                                                                                                            |

|--------|---------------|------|----------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| P0     |               | I/O  |                | port. It can b                      | -bit bidirectional general purpose I/O<br>be used as alternate functions for the<br>6, UART, and the SSC.                  |

| P0.0   | 12            |      | Hi-Z           | TCK_0<br>T12HR_1                    | JTAG Clock Input<br>CCU6 Timer 12 Hardware Run<br>Input                                                                    |

|        |               |      |                | CC61_1<br>CLKOUT<br>RXDO_1          | Input/Output of Capture/Compare<br>channel 1<br>Clock Output<br>UART Transmit Data Output                                  |

| P0.1   | 14            |      | Hi-Z           | TDI_0<br>T13HR_1                    | JTAG Serial Data Input<br>CCU6 Timer 13 Hardware Run<br>Input                                                              |

|        |               |      |                | RXD_1<br>COUT61_1                   | UART Receive Data Input<br>Output of Capture/Compare<br>channel 1                                                          |

| P0.2   | 13            |      | PU             | EXF2_1<br>CTRAP_2<br>TDO_0<br>TXD_1 | Timer 2 External Flag Output<br>CCU6 Trap Input<br>JTAG Serial Data Output<br>UART Transmit Data Output/<br>Clock Output   |

| P0.3   | 2             |      | Hi-Z           | SCK_1<br>COUT63_1                   | SSC Clock Input/Output<br>Output of Capture/Compare<br>channel 3                                                           |

| P0.4   | 3             |      | Hi-Z           | MTSR_1<br>CC62_1                    | SSC Master Transmit Output/<br>Slave Receive Input<br>Input/Output of Capture/Compare<br>channel 2                         |

| P0.5   | 4             |      | Hi-Z           | MRST_1<br>EXINT0_0<br>COUT62_1      | SSC Master Receive Input/<br>Slave Transmit Output<br>External Interrupt Input 0<br>Output of Capture/Compare<br>channel 2 |

# 3.2.1 Memory Protection Strategy

The XC866 memory protection strategy includes:

- Read-out protection: The Flash Memory can be enabled for read-out protection and ROM memory is always protected.

- Program and erase protection: The Flash memory in all devices can be enabled for program and erase protection.

Flash memory protection is available in two modes:

- Mode 0: Only the P-Flash is protected; the D-Flash is unprotected

- · Mode 1: Both the P-Flash and D-Flash are protected

The selection of each protection mode and the restrictions imposed are summarized in **Table 4**.

| Mode                            | 0                                                                                                                    | 1                                              |  |  |  |  |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------|------------------------------------------------|--|--|--|--|

| Activation                      | Program a valid password via BSL mode 6                                                                              |                                                |  |  |  |  |

| Selection                       | MSB of password = 0                                                                                                  | MSB of password = 1                            |  |  |  |  |

| P-Flash contents can be read by | Read instructions in the<br>P-Flash                                                                                  | Read instructions in the<br>P-Flash or D-Flash |  |  |  |  |

| P-Flash program and erase       | Not possible                                                                                                         | Not possible                                   |  |  |  |  |

| D-Flash contents can be read by | Read instructions in the<br>P-Flash or D-Flash                                                                       |                                                |  |  |  |  |

| D-Flash program                 | Possible                                                                                                             | Not possible                                   |  |  |  |  |

| D-Flash erase                   | Possible, on the condition that bit<br>DFLASHEN in register MISC_CON<br>is set to 1 prior to each erase<br>operation | Not possible                                   |  |  |  |  |

#### Table 4 Flash Protection Modes

BSL mode 6, which is used for enabling Flash protection, can also be used for disabling Flash protection. Here, the programmed password must be provided by the user. A password match triggers an automatic erase of the read-protected Flash contents, see **Table 5** and **Table 6**, and the programmed password is erased. The Flash protection is then disabled upon the next reset.

#### For XC866-2FR and XC866-4FR devices:

The selection of protection type is summarized in Table 5.

# Note: The RMAP bit must be cleared/set by ANL or ORL instructions. The rest bits of SYSCON0 should not be modified.

As long as bit RMAP is set, the mapped SFR area can be accessed. This bit is not cleared automatically by hardware. Thus, before standard/mapped registers are accessed, bit RMAP must be cleared/set, respectively, by software.

Figure 8 Address Extension by Mapping

# 3.2.2.2 Address Extension by Paging

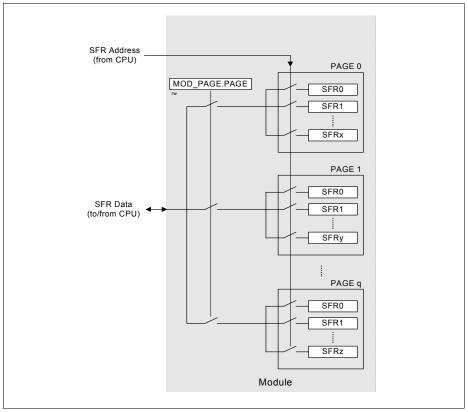

Address extension is further performed at the module level by paging. With the address extension by mapping, the XC866 has a 256-SFR address range. However, this is still less than the total number of SFRs needed by the on-chip peripherals. To meet this requirement, some peripherals have a built-in local address extension mechanism for increasing the number of addressable SFRs. The extended address range is not directly controlled by the CPU instruction itself, but is derived from bit field PAGE in the module page register MOD\_PAGE. Hence, the bit field PAGE must be programmed before accessing the SFR of the target module. Each module may contain a different number of pages and a different number of SFRs per page, depending on the specific requirement. Besides setting the correct RMAP bit value to select the SFR area, the user must also ensure that a valid PAGE is selected to target the desired SFR. A page inside the extended address range can be selected as shown in Figure 9.

Figure 9 Address Extension by Paging

| AB <sub>H</sub> | SSC_CONH Reset: 00 <sub>H</sub><br>Control Register High | Bit Field | EN            | MS | 0 | AREN   | BEN      | PEN | REN | TEN |

|-----------------|----------------------------------------------------------|-----------|---------------|----|---|--------|----------|-----|-----|-----|

|                 | Programming Mode                                         | Туре      | rw            | rw | r | rw     | rw       | rw  | rw  | rw  |

|                 | Operating Mode                                           |           | EN            | MS | 0 | BSY    | BE       | PE  | RE  | TE  |

|                 |                                                          |           | rw            | rw | r | rh     | rwh      | rwh | rwh | rwh |

| ACH             | SSC_TBL Reset: 00 <sub>H</sub>                           | Bit Field | TB_VALUE      |    |   |        |          |     |     |     |

|                 | Transmitter Buffer Register Low                          |           | rw            |    |   |        |          |     |     |     |

| AD <sub>H</sub> | SSC_RBL Reset: 00 <sub>H</sub>                           | Bit Field | RB_VALUE      |    |   |        |          |     |     |     |

|                 | Receiver Buffer Register Low                             | Туре      | rh            |    |   |        |          |     |     |     |

| AE <sub>H</sub> | SSC_BRL Reset: 00 <sub>H</sub>                           | Bit Field | BR_VALUE[7:0] |    |   |        |          |     |     |     |

|                 | Baudrate Timer Reload Register Low                       | Туре      | rw            |    |   |        |          |     |     |     |

| AF <sub>H</sub> | SSC_BRH Reset: 00 <sub>H</sub>                           | Bit Field |               |    |   | BR_VAL | UE[15:8] |     |     |     |

|                 | Baudrate Timer Reload Register High                      | Туре      | rw            |    |   |        |          |     |     |     |

# Table 14 SSC Register Overview

The OCDS SFRs can be accessed in the mapped memory area (RMAP = 1).

# Table 15OCDS Register Overview

| Addr            | Register Name                                                           | Bit       | 7             | 6         | 5           | 4                   | 3           | 2         | 1          | 0         |

|-----------------|-------------------------------------------------------------------------|-----------|---------------|-----------|-------------|---------------------|-------------|-----------|------------|-----------|

| RMAP =          | 1                                                                       |           |               |           | 1           |                     |             |           |            |           |

| E9 <sub>H</sub> | MMCR2 Reset: 0U <sub>H</sub><br>Monitor Mode Control Register 2         | Bit Field | EXBC_<br>P    | EXBC      | MBCO<br>N_P | MBCO<br>N           | MMEP<br>_P  | MMEP      | MMOD<br>E  | JENA      |

|                 |                                                                         | Туре      | w             | rw        | w           | rwh                 | w           | rwh       | rh         | rh        |

| F1 <sub>H</sub> | MMCR Reset: 00 <sub>H</sub><br>Monitor Mode Control Register            | Bit Field | MEXIT<br>_P   | MEXIT     | MSTEP<br>_P | MSTEP               | MRAM<br>S_P | MRAM<br>S | TRF        | RRF       |

|                 |                                                                         | Туре      | w             | rwh       | w           | rw                  | w           | rwh       | rh         | rh        |

| F2 <sub>H</sub> | MMSR Reset: 00 <sub>H</sub><br>Monitor Mode Status Register             | Bit Field | MBCA<br>M     | MBCIN     | EXBF        | SWBF                | HWB3<br>F   | HWB2<br>F | HWB1<br>F  | HWB0<br>F |

|                 |                                                                         | Туре      | rw            | rh        | rwh         | rwh                 | rwh         | rwh       | rwh        | rwh       |

| F3 <sub>H</sub> | MMBPCR Reset: 00 <sub>H</sub><br>BreakPoints Control Register           | Bit Field | SWBC          | HWB3C HWB |             | B2C HWB1 HWB0C<br>C |             | B0C       |            |           |

|                 |                                                                         | Туре      | rw            | r         | rw i        |                     | rw rw       |           | rw         |           |

| F4 <sub>H</sub> | MMICR Reset: 00 <sub>H</sub><br>Monitor Mode Interrupt Control Register | Bit Field | DVECT         | DRETR     | (           | )                   | MMUIE<br>_P | MMUIE     | RRIE_<br>P | RRIE      |

|                 |                                                                         | Туре      | rwh           | rwh       | rwh r       |                     | w           | rw        | w          | rw        |

| F5 <sub>H</sub> | MMDR Reset: 00 <sub>H</sub><br>Monitor Mode Data Register               | Bit Field | MMRR          |           |             |                     |             |           |            |           |

|                 | Receive                                                                 | Туре      | rh            |           |             |                     |             |           |            |           |

|                 | Transmit                                                                | Bit Field | MMTR          |           |             |                     |             |           |            |           |

|                 |                                                                         | Туре      |               |           |             | ١                   | N           |           |            |           |

| F6 <sub>H</sub> | HWBPSR Reset: 00 <sub>H</sub><br>Hardware Breakpoints Select Register   | Bit Field | 0 BPSEL<br>_P |           | BPSEL       |                     |             |           |            |           |

|                 |                                                                         | Туре      |               | r         |             | w                   |             | r         | w          |           |

| F7 <sub>H</sub> | HWBPDR Reset: 00 <sub>H</sub>                                           | Bit Field |               |           |             | HW                  | BPxx        |           |            |           |

|                 | Hardware Breakpoints Data Register                                      | Туре      |               |           |             | r                   | w           |           |            |           |

# XC866

#### **Functional Description**

# 3.3 Flash Memory

The Flash memory provides an embedded user-programmable non-volatile memory, allowing fast and reliable storage of user code and data. It is operated from a single 2.5 V supply from the Embedded Voltage Regulator (EVR) and does not require additional programming or erasing voltage. The sectorization of the Flash memory allows each sector to be erased independently.

#### Features

- In-System Programming (ISP) via UART

- In-Application Programming (IAP)

- · Error Correction Code (ECC) for dynamic correction of single-bit errors

- Background program and erase operations for CPU load minimization

- Support for aborting erase operation

- Minimum program width<sup>1)</sup> of 32-byte for D-Flash and 32-byte for P-Flash

- 1-sector minimum erase width

- · 1-byte read access

- · Flash is delivered in erased state (read all zeros)

- Operating supply voltage: 2.5 V ± 7.5 %

- Read access time: 3 × t<sub>CCLK</sub> = 112.5 ns<sup>2)</sup>

- Program time: 209440 /  $f_{SYS}$  = 2.6 ms<sup>3</sup>)

- Erase time: 8175360 /  $f_{SYS}$  = 102 ms<sup>3</sup>)

P-Flash: 32-byte wordline can only be programmed once, i.e., one gate disturb allowed. D-Flash: 32-byte wordline can be programmed twice, i.e., two gate disturbs allowed.

<sup>&</sup>lt;sup>2)</sup>  $f_{svs}$  = 80 MHz ± 7.5% ( $f_{CCLK}$  = 26.7 MHz ± 7.5 %) is the maximum frequency range for Flash read access.

<sup>&</sup>lt;sup>3)</sup>  $f_{sys} = 80 \text{ MHz} \pm 7.5\%$  is the only frequency range for Flash programming and erasing.  $f_{sysmin}$  is used for obtaining the worst case timing.

# XC866

#### **Functional Description**

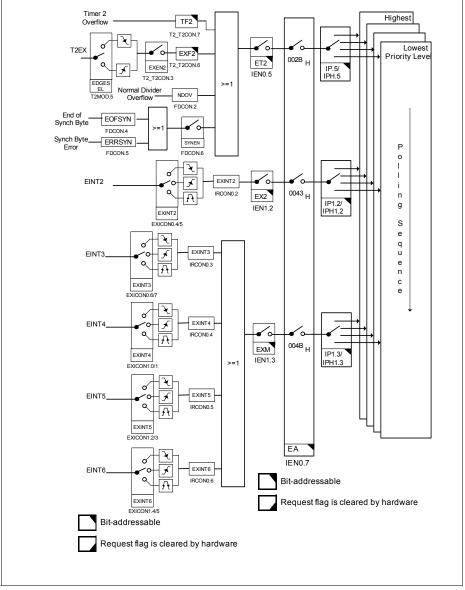

Figure 15 Interrupt Request Sources (Part 2)

# XC866

# **Functional Description**

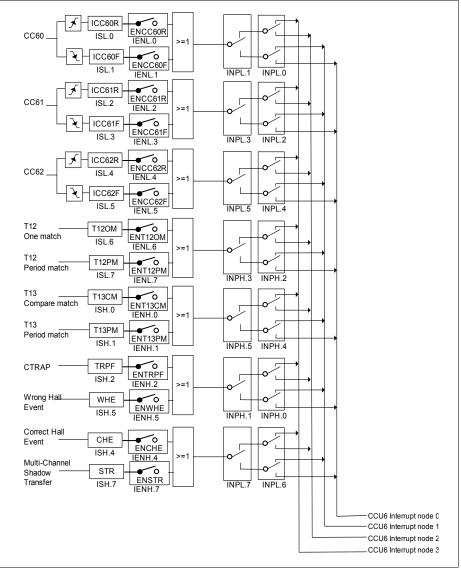

#### Figure 17 Interrupt Request Sources (Part 4)

# 3.4.3 Interrupt Priority

Each interrupt source, except for NMI, can be individually programmed to one of the four possible priority levels. The NMI has the highest priority and supersedes all other interrupts. Two pairs of interrupt priority registers (IP and IPH, IP1 and IPH1) are available to program the priority level of each non-NMI interrupt vector.

A low-priority interrupt can be interrupted by a high-priority interrupt, but not by another interrupt of the same or lower priority. Further, an interrupt of the highest priority cannot be interrupted by any other interrupt source.

If two or more requests of different priority levels are received simultaneously, the request of the highest priority is serviced first. If requests of the same priority are received simultaneously, then an internal polling sequence determines which request is serviced first. Thus, within each priority level, there is a second priority structure determined by the polling sequence shown in Table 18.

| Source                                      | Level     |  |  |  |  |

|---------------------------------------------|-----------|--|--|--|--|

| Non-Maskable Interrupt (NMI)                | (highest) |  |  |  |  |

| External Interrupt 0                        | 1         |  |  |  |  |

| Timer 0 Interrupt                           | 2         |  |  |  |  |

| External Interrupt 1                        | 3         |  |  |  |  |

| Timer 1 Interrupt                           | 4         |  |  |  |  |

| UART Interrupt                              | 5         |  |  |  |  |

| Timer 2, Fractional Divider, LIN Interrupts | 6         |  |  |  |  |

| ADC Interrupt                               | 7         |  |  |  |  |

| SSC Interrupt                               | 8         |  |  |  |  |

| External Interrupt 2                        | 9         |  |  |  |  |

| External Interrupt [6:3]                    | 10        |  |  |  |  |

| CCU6 Interrupt Node Pointer 0               | 11        |  |  |  |  |

| CCU6 Interrupt Node Pointer 1               | 12        |  |  |  |  |

| CCU6 Interrupt Node Pointer 2               | 13        |  |  |  |  |

| CCU6 Interrupt Node Pointer 3               | 14        |  |  |  |  |

Table 18

Priority Structure within Interrupt Level

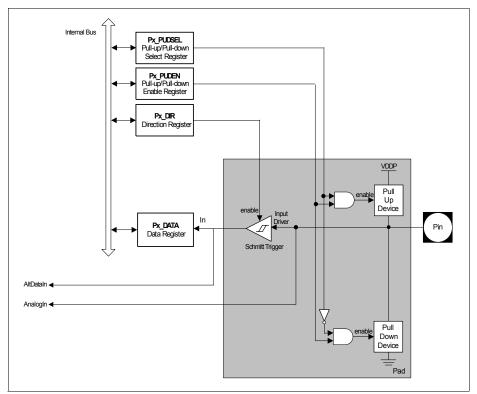

Figure 19 General Structure of Input Port

# 3.7 Reset Control

The XC866 has five types of reset: power-on reset, hardware reset, watchdog timer reset, power-down wake-up reset, and brownout reset.

When the XC866 is first powered up, the status of certain pins (see **Table 20**) must be defined to ensure proper start operation of the device. At the end of a reset sequence, the sampled values are latched to select the desired boot option, which cannot be modified until the next power-on reset or hardware reset. This guarantees stable conditions during the normal operation of the device.

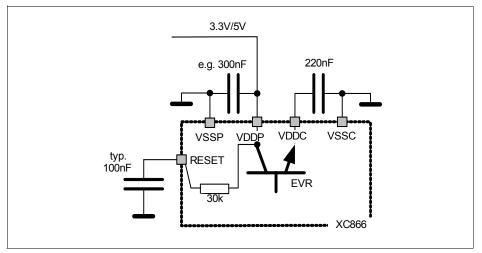

In order to power up the system properly, the external reset pin RESET must be asserted until  $V_{DDC}$  reaches  $0.9^*V_{DDC}$ . The delay of external reset can be realized by an external capacitor at RESET pin. This capacitor value must be selected so that  $V_{RESET}$  reaches 0.4 V, but not before  $V_{DDC}$  reaches 0.9\*  $V_{DDC}$ .

A typical application example is shown in Figure 21.  $V_{DDP}$  capacitor value is 300 nF.  $V_{DDC}$  capacitor value is 220 nF. The capacitor connected to RESET pin is 100 nF.

Typically, the time taken for  $V_{DDC}$  to reach  $0.9^*V_{DDC}$  is less than 50 µs once  $V_{DDP}$  reaches 2.3V. Hence, based on the condition that 10% to 90%  $V_{DDP}$  (slew rate) is less than 500 µs, the RESET pin should be held low for 500 µs typically. See Figure 22.

# 3.7.1 Module Reset Behavior

Table 19 shows how the functions of the XC866 are affected by the various reset types. A "∎" means that this function is reset to its default state.

| Module/<br>Function   | Wake-Up<br>Reset                     | Watchdog<br>Reset      | Hardware<br>Reset      | Power-On<br>Reset         | Brownout<br>Reset         |

|-----------------------|--------------------------------------|------------------------|------------------------|---------------------------|---------------------------|

| CPU Core              |                                      |                        |                        |                           |                           |

| Peripherals           |                                      |                        |                        |                           |                           |

| On-Chip<br>Static RAM | Not affected, reliable               | Not affected, reliable | Not affected, reliable | Affected, un-<br>reliable | Affected, un-<br>reliable |

| Oscillator,<br>PLL    |                                      | Not affected           |                        |                           |                           |

| Port Pins             |                                      |                        |                        |                           |                           |

| EVR                   | The voltage regulator is switched on | Not affected           |                        |                           |                           |

| FLASH                 |                                      |                        |                        |                           |                           |

| NMI                   | Disabled                             | Disabled               |                        |                           |                           |

Table 19 Effect of Reset on Device Functions

# 3.7.2 Booting Scheme

When the XC866 is reset, it must identify the type of configuration with which to start the different modes once the reset sequence is complete. Thus, boot configuration information that is required for activation of special modes and conditions needs to be applied by the external world through input pins. After power-on reset or hardware reset, the pins MBC, TMS and P0.0 collectively select the different boot options. Table 20 shows the available boot options in the XC866.

| MBC | TMS | P0.0 | Type of Mode                                                                      | PC Start Value    |

|-----|-----|------|-----------------------------------------------------------------------------------|-------------------|

| 1   | 0   | х    | User Mode; on-chip OSC/PLL non-bypassed                                           | 0000 <sub>H</sub> |

| 0   | 0   | х    | BSL Mode; on-chip OSC/PLL non-bypassed                                            | 0000 <sub>H</sub> |

| 0   | 1   | 0    | OCDS Mode <sup>1)</sup> ; on-chip OSC/PLL non-<br>bypassed                        | 0000 <sub>H</sub> |

| 1   | 1   | 0    | Standalone User (JTAG) Mode <sup>2)</sup> ; on-chip OSC/PLL non-bypassed (normal) | 0000 <sub>H</sub> |

Table 20 XC866 Boot Selection

<sup>1)</sup> The OCDS mode is not accessible if Flash is protected.

<sup>2)</sup> Normal user mode with standard JTAG (TCK,TDI,TDO) pins for hot-attach purpose.

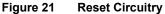

#### 3.9 Power Saving Modes

The power saving modes of the XC866 provide flexible power consumption through a combination of techniques, including:

- Stopping the CPU clock

- · Stopping the clocks of individual system components

- Reducing clock speed of some peripheral components

- · Power-down of the entire system with fast restart capability

After a reset, the active mode (normal operating mode) is selected by default (see **Figure 26**) and the system runs in the main system clock frequency. From active mode, different power saving modes can be selected by software. They are:

- · Idle mode

- Slow-down mode

- Power-down mode

Figure 26 Transition between Power Saving Modes

# 3.16 Timer 2

Timer 2 is a 16-bit general purpose timer (THL2) that has two modes of operation, a 16-bit auto-reload mode and a 16-bit one channel capture mode. If the prescalar is disabled, Timer 2 counts with an input clock of PCLK/12. Timer 2 continues counting as long as it is enabled.

| Table 29           | Timer 2 Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mode               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Auto-reload        | <ul> <li>Up/Down Count Disabled</li> <li>Count up only</li> <li>Start counting from 16-bit reload value, overflow at FFFF<sub>H</sub></li> <li>Reload event configurable for trigger by overflow condition only, or by negative/positive edge at input pin T2EX as well</li> <li>Programmble reload value in register RC2</li> <li>Interrupt is generated with reload event</li> </ul>                                                                                                                                                                                                                                         |

|                    | <ul> <li>Up/Down Count Enabled</li> <li>Count up or down, direction determined by level at input pin T2EX</li> <li>No interrupt is generated</li> <li>Count up <ul> <li>Start counting from 16-bit reload value, overflow at FFFF<sub>H</sub></li> <li>Reload event triggered by overflow condition</li> <li>Programmble reload value in register RC2</li> </ul> </li> <li>Count down <ul> <li>Start counting from FFFF<sub>H</sub>, underflow at value defined in register RC2</li> <li>Reload event triggered by underflow condition <ul> <li>Reload event triggered by underflow condition</li> </ul> </li> </ul></li></ul> |

| Channel<br>capture | <ul> <li>Count up only</li> <li>Start counting from 0000<sub>H</sub>, overflow at FFFF<sub>H</sub></li> <li>Reload event triggered by overflow condition</li> <li>Reload value fixed at 0000<sub>H</sub></li> <li>Capture event triggered by falling/rising edge at pin T2EX</li> <li>Captured timer value stored in register RC2</li> <li>Interrupt is generated with reload or capture event</li> </ul>                                                                                                                                                                                                                      |

For module clock  $f_{ADC}$  = 26.7 MHz, the analog clock  $f_{ADCI}$  frequency can be selected as shown in **Table 30**.

| Module Clock f <sub>ADC</sub> | СТС                       | Prescaling Ratio | Analog Clock f <sub>ADCI</sub> |

|-------------------------------|---------------------------|------------------|--------------------------------|

| 26.7 MHz                      | 00 <sub>B</sub>           | ÷ 2              | 13.3 MHz (N.A)                 |

|                               | 01 <sub>B</sub>           | ÷ 3              | 8.9 MHz                        |

|                               | 10 <sub>B</sub>           | ÷ 4              | 6.7 MHz                        |

|                               | 11 <sub>B</sub> (default) | ÷ 32             | 833.3 kHz                      |

# Table 30f\_ADCIFrequency Selection

As  $f_{ADCI}$  cannot exceed 10 MHz, bit field CTC should not be set to  $00_B$  when  $f_{ADC}$  is 26.7 MHz. During slow-down mode where  $f_{ADC}$  may be reduced to 13.3 MHz, 6.7 MHz etc., CTC can be set to  $00_B$  as long as the divided analog clock  $f_{ADCI}$  does not exceed 10 MHz. However, it is important to note that the conversion error could increase due to loss of charges on the capacitors, if  $f_{ADC}$  becomes too low during slow-down mode.

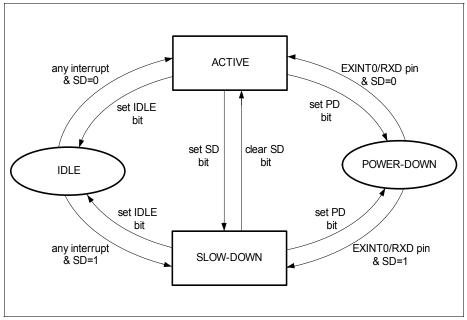

# 3.18.2 ADC Conversion Sequence

The analog-to-digital conversion procedure consists of the following phases:

- Synchronization phase (t<sub>SYN</sub>)

- Sample phase (t<sub>S</sub>)

- Conversion phase

- Write result phase (t<sub>WR</sub>)

Figure 34 ADC Conversion Timing

# 4 Electrical Parameters

**Chapter 4** provides the characteristics of the electrical parameters which are implementation-specific for the XC866.

Note: The electrical parameters are valid for the XC866-4FR and XC866-2FR. The electrical parameters for the ROM variants and XC866-1FR are preliminary, differences from XC866-4FR and XC866-2FR are stated explicitly.

#### 4.1 General Parameters

The general parameters are described here to aid the users in interpreting the parameters mainly in **Section 4.2** and **Section 4.3**.

#### 4.1.1 Parameter Interpretation

The parameters listed in this section represent partly the characteristics of the XC866 and partly its requirements on the system. To aid interpreting the parameters easily when evaluating them for a design, they are indicated by the abbreviations in the "Symbol" column:

• cc

These parameters indicate **C**ontroller **C**haracteristics, which are distinctive features of the XC866 and must be regarded for a system design.

• SR

These parameters indicate **S**ystem **R**equirements, which must be provided by the microcontroller system in which the XC866 is designed in.

<sup>4)</sup> Not subjected to production test, verified by design/characterization. However, for applications with strict low power-down current requirements, it is mandatory that no active voltage source is supplied at any GPIO pin when VDDP is powered off.

#### Table 36ADC Characteristics (Operating Conditions apply; $V_{DDP}$ = 5V Range)

| Parameter                                                  | Symbol                   | Limit Values |      |      | Unit | Test Conditions/ |

|------------------------------------------------------------|--------------------------|--------------|------|------|------|------------------|

|                                                            |                          | min.         | typ. | max. |      | Remarks          |

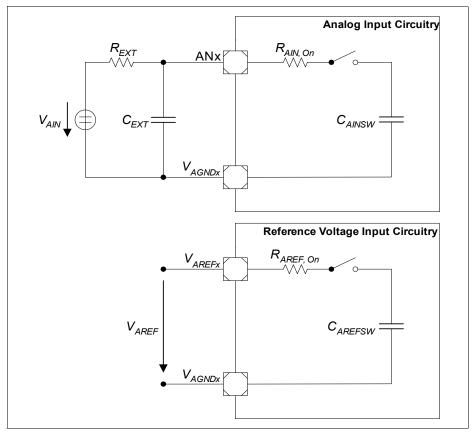

| Switched<br>capacitance at the<br>analog voltage<br>inputs | C <sub>AINSW</sub><br>CC | _            | 5    | 7    | pF   | 2)4)             |

| Input resistance of the reference input                    | R <sub>AREF</sub> CC     | -            | 1    | 2    | kΩ   | 2)               |

| Input resistance of the selected analog channel            | R <sub>AIN</sub> CC      | -            | 1    | 1.5  | kΩ   | 2)               |

<sup>1)</sup> TUE is tested at  $V_{AREF}$  = 5.0 V,  $V_{AGND}$  = 0 V ,  $V_{DDP}$  = 5.0 V.

<sup>2)</sup> Not subject to production test, verified by design/characterization.

<sup>&</sup>lt;sup>3)</sup> This represents an equivalent switched capacitance. This capacitance is not switched to the reference voltage at once. Instead of this, smaller capacitances are successively switched to the reference voltage.

<sup>&</sup>lt;sup>4)</sup> The sampling capacity of the conversion C-Network is pre-charged to V<sub>AREF</sub>/2 before connecting the input to the C-Network. Because of the parasitic elements, the voltage measured at ANx is lower than V<sub>AREF</sub>/2.

# 4.2.3.1 ADC Conversion Timing

Conversion time,  $t_C = t_{ADC} \times (1 + r \times (3 + n + STC))$ , where r = CTC + 2 for CTC =  $00_B$ ,  $01_B$  or  $10_B$ , r = 32 for CTC =  $11_B$ , CTC = Conversion Time Control (GLOBCTR.CTC), STC = Sample Time Control (INPCR0.STC), n = 8 or 10 (for 8-bit and 10-bit conversion respectively),  $t_{ADC} = 1 / f_{ADC}$