Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | XC800                                                                        |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 86MHz                                                                        |

| Connectivity               | SSI, UART/USART                                                              |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 19                                                                           |

| Program Memory Size        | 16KB (16K x 8)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 768 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                  |

| Data Converters            | A/D 8x10b                                                                    |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 38-TFSOP (0.173", 4.40mm Width)                                              |

| Supplier Device Package    | PG-TSSOP-38                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/sak-xc866-4fri-bc |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Data Sheet<br>n History: | 2007-10                                                                                                                                                                         | V1.2                               |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| V1.0                     | 2006-02                                                                                                                                                                         |                                    |

| Subjects (               | najor changes since last revision)                                                                                                                                              | )                                  |

| Device sur               | nmary table is updated for Flash                                                                                                                                                | 4-Kb and ROM variants.             |

| Footnote is              | added to MBC pin; description o                                                                                                                                                 | f $V_{\text{DDP}}$ pin is updated. |

|                          | •                                                                                                                                                                               | s type of register bit field       |

| Access typ               | e of PAGE bits of all module page                                                                                                                                               | registers are corrected to rwh.    |

| Access typ               | e of Px_DIR register bits are corr                                                                                                                                              | ected to rwh                       |

| New bullet               | point on Flash delivery state is a                                                                                                                                              | dded to the feature list.          |

| Digital pov              | er supply voltage are differentiate                                                                                                                                             | ed for 5V and 3.3V variants.       |

|                          | 5                                                                                                                                                                               | /oltage on GPIO pins during        |

| Figure on                | Power-on reset timing is updated.                                                                                                                                               |                                    |

|                          | n History:<br>S Version: V 0.1<br>V1.0,<br>V1.1,<br>Subjects (n<br>Device sum<br>Footnote is<br>Section on<br>PASSWD.F<br>Access type<br>New bullet<br>Digital pow<br>VDDP powe |                                    |

## We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to:

mcdocu.comments@infineon.com

$\ge$

#### **Summary of Features**

#### **Ordering Information**

The ordering code for Infineon Technologies microcontrollers provides an exact reference to the required product. This ordering code identifies:

- The derivative itself, i.e. its function set, the temperature range, and the supply voltage

- the package and the type of delivery

For the available ordering codes for the XC866, please refer to your responsible sales representative or your local distributor.

As this document refers to all the derivatives, some descriptions may not apply to a specific product. For simplicity all versions are referred to by the term XC866 throughout this document.

#### **General Device Information**

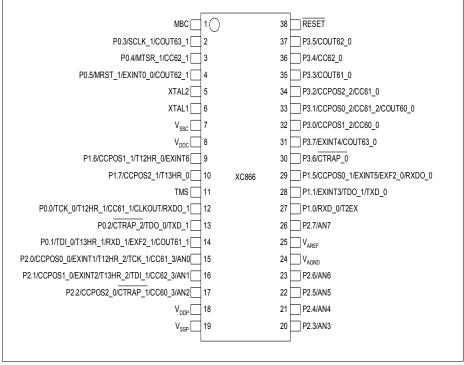

# 2.3 Pin Configuration

Figure 4 XC866 Pin Configuration, PG-TSSOP-38 Package (top view)

# XC866

# **General Device Information**

| Table 3 | Pin D         | efinitio | ons and        | Functions (c                         | ont'd)                                                                                                                                       |

|---------|---------------|----------|----------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol  | Pin<br>Number | Туре     | Reset<br>State | Function                             |                                                                                                                                              |

| P2      |               | I        |                | can be used inputs of the            | bit general purpose input-only port. It<br>as alternate functions for the digital<br>JTAG and CCU6. It is also used as the<br>s for the ADC. |

| P2.0    | 15            |          | Hi-Z           | EXINT1<br>T12HR_2                    | CCU6 Hall Input 0<br>External Interrupt Input 1<br>CCU6 Timer 12 Hardware Run<br>Input                                                       |

|         |               |          |                | TCK_1<br>CC61_3<br>AN0               | JTAG Clock Input<br>Input of Capture/Compare channel 1<br>Analog Input 0                                                                     |

| P2.1    | 16            |          | Hi-Z           | CCPOS1_0<br>EXINT2<br>T13HR_2        | CCU6 Hall Input 1<br>External Interrupt Input 2<br>CCU6 Timer 13 Hardware Run<br>Input                                                       |

|         |               |          |                | TDI_1<br>CC62_3<br>AN1               | JTAG Serial Data Input<br>Input of Capture/Compare channel 2<br>Analog Input 1                                                               |

| P2.2    | 17            |          | Hi-Z           | CCPOS2_0<br>CTRAP_1<br>CC60_3<br>AN2 | CCU6 Hall Input 2<br>CCU6 Trap Input<br>Input of Capture/Compare channel 0<br>Analog Input 2                                                 |

| P2.3    | 20            |          | Hi-Z           | AN3                                  | Analog Input 3                                                                                                                               |

| P2.4    | 21            |          | Hi-Z           | AN4                                  | Analog Input 4                                                                                                                               |

| P2.5    | 22            |          | Hi-Z           | AN5                                  | Analog Input 5                                                                                                                               |

| P2.6    | 23            |          | Hi-Z           | AN6                                  | Analog Input 6                                                                                                                               |

| P2.7    | 26            |          | Hi-Z           | AN7                                  | Analog Input 7                                                                                                                               |

# **General Device Information**

| Table 5 |               |      | ins and        |                                                                                                                    | ontaj                                                                |  |  |  |  |  |

|---------|---------------|------|----------------|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|--|--|--|--|--|

| Symbol  | Pin<br>Number | Туре | Reset<br>State | Function                                                                                                           |                                                                      |  |  |  |  |  |

| P3      |               | I    |                | <b>Port 3</b><br>Port 3 is a bidirectional general purpose I/O pc<br>can be used as alternate functions for the CC |                                                                      |  |  |  |  |  |

| P3.0    | 32            |      | Hi-Z           | CCPOS1_2<br>CC60_0                                                                                                 | CCU6 Hall Input 1<br>Input/Output of Capture/Compare<br>channel 0    |  |  |  |  |  |

| P3.1    | 33            |      | Hi-Z           | CCPOS0_2<br>CC61_2                                                                                                 | CCU6 Hall Input 0<br>Input/Output of Capture/Compare<br>channel 1    |  |  |  |  |  |

|         |               |      |                | COUT60_0                                                                                                           | Output of Capture/Compare<br>channel 0                               |  |  |  |  |  |

| P3.2    | 34            |      | Hi-Z           | CCPOS2_2<br>CC61_0                                                                                                 | CCU6 Hall Input 2<br>Input/Output of Capture/Compare<br>channel 1    |  |  |  |  |  |

| P3.3    | 35            |      | Hi-Z           | COUT61_0                                                                                                           | Output of Capture/Compare<br>channel 1                               |  |  |  |  |  |

| P3.4    | 36            |      | Hi-Z           | CC62_0                                                                                                             | Input/Output of Capture/Compare<br>channel 2                         |  |  |  |  |  |

| P3.5    | 37            |      | Hi-Z           | COUT62_0                                                                                                           | Output of Capture/Compare<br>channel 2                               |  |  |  |  |  |

| P3.6    | 30            |      | PD             | CTRAP_0                                                                                                            | CCU6 Trap Input                                                      |  |  |  |  |  |

| P3.7    | 31            |      | Hi-Z           | EXINT4<br>COUT63_0                                                                                                 | External Interrupt Input 4<br>Output of Capture/Compare<br>channel 3 |  |  |  |  |  |

## Table 3Pin Definitions and Functions (cont'd)

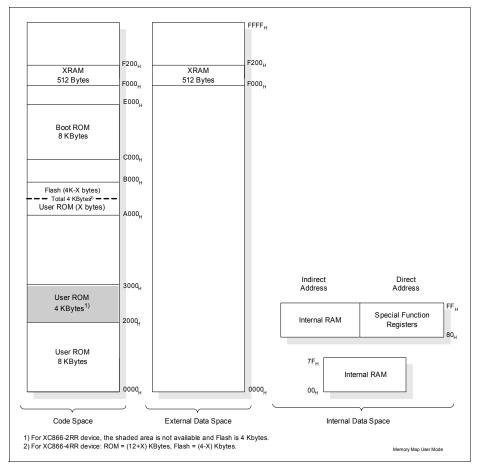

# Figure 7 illustrates the memory address spaces of the XC866-4RR device.

Figure 7 Memory Map of XC866 ROM Devices

## Table 11 ADC Register Overview (cont'd)

| Addr            | Register Name                                                              | Bit               | 7          | 6          | 5          | 4          | 3          | 2          | 1            | 0          |

|-----------------|----------------------------------------------------------------------------|-------------------|------------|------------|------------|------------|------------|------------|--------------|------------|

| CA <sub>H</sub> | ADC_CHINFR Reset: 00 <sub>H</sub><br>Channel Interrupt Flag Register       | Bit Field         | CHINF<br>7 | CHINF<br>6 | CHINF<br>5 | CHINF<br>4 | CHINF<br>3 | CHINF<br>2 | CHINF<br>1   | CHINF<br>0 |

|                 |                                                                            | Туре              | rh           | rh         |

| CB <sub>H</sub> | ADC_CHINCR Reset: 00 <sub>H</sub><br>Channel Interrupt Clear Register      | Bit Field         | CHINC<br>7 | CHINC<br>6 | CHINC<br>5 | CHINC<br>4 | CHINC<br>3 | CHINC<br>2 | CHINC<br>1   | CHINC<br>0 |

|                 |                                                                            | Туре              | w          | w          | w          | w          | w          | w          | w            | w          |

| CCH             | ADC_CHINSR Reset: 00 <sub>H</sub><br>Channel Interrupt Set Register        | Bit Field         | CHINS<br>7 | CHINS<br>6 | CHINS<br>5 | CHINS<br>4 | CHINS<br>3 | CHINS<br>2 | CHINS<br>1   | CHINS<br>0 |

|                 |                                                                            | Туре              | w          | w          | w          | w          | w          | w          | w            | w          |

| CD <sub>H</sub> | ADC_CHINPR Reset: 00 <sub>H</sub><br>Channel Interrupt Node Pointer        | Bit Field         | CHINP<br>7 | CHINP<br>6 | CHINP<br>5 | CHINP<br>4 | CHINP<br>3 | CHINP<br>2 | CHINP<br>1   | CHINP<br>0 |

|                 | Register                                                                   | Туре              | rw           | rw         |

| CEH             | ADC_EVINFR Reset: 00 <sub>H</sub><br>Event Interrupt Flag Register         | Bit Field         | EVINF<br>7 | EVINF<br>6 | EVINF<br>5 | EVINF<br>4 | (          | )          | EVINF<br>1   | EVINF<br>0 |

|                 |                                                                            | Туре              | rh         | rh         | rh         | rh         |            | r          | rh           | rh         |

| CF <sub>H</sub> | ADC_EVINCR Reset: 00 <sub>H</sub><br>Event Interrupt Clear Flag Register   | Bit Field         | EVINC<br>7 | EVINC<br>6 | EVINC<br>5 | EVINC<br>4 | (          | )          | EVINC<br>1   | EVINC<br>0 |

|                 |                                                                            | Туре              | w          | w          | w          | w          |            | r          | w<br>EVINS   | w          |

| D2 <sub>H</sub> | ADC_EVINSR Reset: 00 <sub>H</sub><br>Event Interrupt Set Flag Register     | Bit Field         | EVINS<br>7 | EVINS<br>6 | EVINS<br>5 | EVINS<br>4 | (          | 0 E        |              | EVINS<br>0 |

|                 |                                                                            | Туре              | w          | w          | w          | w          |            | r          | w            | w          |

| D3 <sub>H</sub> | ADC_EVINPR Reset: 00 <sub>H</sub><br>Event Interrupt Node Pointer Register | Bit Field         | EVINP<br>7 | EVINP<br>6 | EVINP<br>5 | EVINP<br>4 | (          | )          | EVINP<br>1   | EVINP<br>0 |

|                 |                                                                            | Туре              | rw         | rw         | rw         | rw         | r          |            | rw           | rw         |

|                 | 0, Page 6                                                                  |                   |            |            |            |            |            |            |              |            |

| CA <sub>H</sub> | ADC_CRCR1 Reset: 00 <sub>H</sub><br>Conversion Request Control Register 1  | Bit Field         | CH7        | CH6        | CH5        | CH4        |            | (          | 0            |            |

|                 |                                                                            | Туре              | rwh        | rwh        | rwh        | rwh        |            |            | r            |            |

| CB <sub>H</sub> | ADC_CRPR1 Reset: 00 <sub>H</sub><br>Conversion Request Pending             | Bit Field         | CHP7       | CHP6       | CHP5       | CHP4       |            |            | 0            |            |

|                 | Register 1                                                                 | Туре              | rwh        | rwh        | rwh        | rwh        |            |            | r            |            |

| CCH             | ADC_CRMR1 Reset: 00 <sub>H</sub><br>Conversion Request Mode Register 1     | Bit Field         | Rsv        | LDEV       | CLR<br>PND | SCAN       | ENSI       | ENTR       | EN           | GT         |

|                 |                                                                            | Туре              | r          | w          | w          | rw         | rw         | rw         |              | w          |

| CD <sub>H</sub> | ADC_QMR0 Reset: 00 <sub>H</sub><br>Queue Mode Register 0                   | Bit Field<br>Type | CEV<br>w   | TREV<br>w  | FLUSH<br>w | CLRV<br>w  | TRMD<br>rw | ENTR<br>rw |              | GT<br>w    |

| CEH             | ADC_QSR0 Reset: 20 <sub>H</sub><br>Queue Status Register 0                 | Bit Field         | Rsv        | 0          | EMPTY      | EV         |            |            | 0            |            |

| 05              |                                                                            | Type<br>Dit Field |            | r          | rh         | rh         | 0          |            | r            | D          |

| CF <sub>H</sub> | ADC_Q0R0 Reset: 00 <sub>H</sub><br>Queue 0 Register 0                      | Bit Field<br>Type | EXTR<br>rh | ENSI<br>rh | RF<br>rh   | V<br>rh    | 0<br>r     | F          | REQCHN<br>rh | ĸ          |

| D2 <sub>H</sub> | ADC QBUR0 Reset: 00 <sub>H</sub>                                           | Bit Field         | EXTR       | ENSI       | RF         | V          | 0          | R          | REQCHN       | R          |

|                 | Queue Backup Register 0                                                    | Туре              | rh         | rh         | rh         | rh         | r          |            | rh           |            |

| D2 <sub>H</sub> | ADC_QINR0 Reset: 00 <sub>H</sub>                                           | Bit Field         | EXTR       | ENSI       | RF         |            | )          | F          | REQCHN       | R          |

|                 | Queue Input Register 0                                                     | Туре              | w          | W          | w          | 1          | r          |            | W            |            |

The Timer 2 SFRs can be accessed in the standard memory area (RMAP = 0).

## Table 12Timer 2 Register Overview

| Addr            | Register Name                        |                        | Bit       | 7   | 6    | 5 | 4 | 3     | 2   | 1 | 0          |

|-----------------|--------------------------------------|------------------------|-----------|-----|------|---|---|-------|-----|---|------------|

| C0 <sub>H</sub> | T2_T2CON<br>Timer 2 Control Register | Reset: 00 <sub>H</sub> | Bit Field | TF2 | EXF2 | ( | ) | EXEN2 | TR2 | 0 | CP/<br>RL2 |

|                 |                                      |                        | Туре      | rwh | rwh  |   | r | rw    | rwh | r | rw         |

## Table 12Timer 2 Register Overview (cont'd)

| C1 <sub>H</sub> | T2_T2MOD<br>Timer 2 Mode Register | Reset: 00 <sub>H</sub> | Bit Field | T2<br>REGS | T2<br>RHEN | EDGE<br>SEL | PREN | T2PRE  | DCEN |  |  |  |

|-----------------|-----------------------------------|------------------------|-----------|------------|------------|-------------|------|--------|------|--|--|--|

|                 |                                   |                        | Туре      | rw         | rw         | rw          | rw   | rw     | rw   |  |  |  |

| C2 <sub>H</sub> | T2_RC2L                           | Reset: 00 <sub>H</sub> | Bit Field |            |            |             | RC2  | [7:0]  |      |  |  |  |

|                 | Timer 2 Reload/Capture            | Register Low           | Туре      |            |            |             | rv   | /h     |      |  |  |  |

| C3 <sub>H</sub> | T2_RC2H                           | Reset: 00 <sub>H</sub> | Bit Field |            |            |             | RC2  | [15:8] |      |  |  |  |

|                 | Timer 2 Reload/Capture            | Register High          | Туре      | rwh        |            |             |      |        |      |  |  |  |

| C4 <sub>H</sub> | T2_T2L                            | Reset: 00 <sub>H</sub> | Bit Field |            |            |             | THL  | 2[7:0] |      |  |  |  |

|                 | Timer 2 Register Low              |                        | Туре      | rwh        |            |             |      |        |      |  |  |  |

| C5 <sub>H</sub> | T2_T2H                            | Reset: 00 <sub>H</sub> | Bit Field |            |            |             | THL2 | [15:8] |      |  |  |  |

|                 | Timer 2 Register High             |                        | Туре      |            |            |             | rv   | vh     |      |  |  |  |

The CCU6 SFRs can be accessed in the standard memory area (RMAP = 0).

## Table 13 CCU6 Register Overview

| Addr            | Register Name                                                                | Bit       | 7          | 6          | 5          | 4          | 3          | 2          | 1          | 0          |  |

|-----------------|------------------------------------------------------------------------------|-----------|------------|------------|------------|------------|------------|------------|------------|------------|--|

| RMAP =          | 0                                                                            |           |            | 1          | 1          |            |            | 1          |            | 1          |  |

| A3 <sub>H</sub> | CCU6_PAGE Reset: 00 <sub>H</sub>                                             | Bit Field | C          | P          | ST         | NR         | 0          |            | PAGE       |            |  |

|                 | Page Register for CCU6                                                       | Туре      | ١          | w w r rwh  |            |            |            |            |            |            |  |

| RMAP =          | 0, Page 0                                                                    |           |            |            |            |            |            |            |            |            |  |

| 9A <sub>H</sub> | CCU6_CC63SRL Reset: 00 <sub>H</sub><br>Capture/Compare Shadow Register for   | Bit Field | CC63SL     |            |            |            |            |            |            |            |  |

|                 | Channel CC63 Low                                                             | Туре      |            |            |            | r          | w          |            |            |            |  |

| 9B <sub>H</sub> | CCU6_CC63SRH Reset: 00 <sub>H</sub><br>Capture/Compare Shadow Register for   | Bit Field |            |            |            | CC6        | 3SH        |            |            |            |  |

|                 | Channel CC63 High                                                            | Туре      |            |            |            | r          | w          |            |            |            |  |

| 9C <sub>H</sub> | CCU6_TCTR4L Reset: 00 <sub>H</sub><br>Timer Control Register 4 Low           | Bit Field | T12<br>STD | T12<br>STR | (          | )          | DTRES      | T12<br>RES | T12RS      | T12RR      |  |

|                 |                                                                              | Туре      | w          | w          |            | r          | w          | w          | w          | w          |  |

| 9D <sub>H</sub> | CCU6_TCTR4H Reset: 00 <sub>H</sub><br>Timer Control Register 4 High          | Bit Field | T13<br>STD | T13<br>STR |            | 0          |            | T13<br>RES | T13RS      | T13RR      |  |

|                 |                                                                              | Туре      | w          | w          |            | r          |            | w          | w          | w          |  |

| 9E <sub>H</sub> | CCU6_MCMOUTSL Reset: 00 <sub>H</sub><br>Multi-Channel Mode Output Shadow     | Bit Field | STRM<br>CM | 0          | MCMPS      |            |            |            |            |            |  |

|                 | Register Low                                                                 | Туре      | w          | r          |            |            | r          | w          |            |            |  |

| 9F <sub>H</sub> | CCU6_MCMOUTSH Reset: 00 <sub>H</sub>                                         | Bit Field | STRHP      | 0          | CURHS EXP  |            |            |            | EXPHS      |            |  |

|                 | Multi-Channel Mode Output Shadow<br>Register High                            | Туре      | w          | r          |            | rw         |            | rw         |            |            |  |

| A4 <sub>H</sub> | CCU6_ISRL Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Status         | Bit Field | RT12P<br>M | RT12O<br>M | RCC62<br>F | RCC62<br>R | RCC61<br>F | RCC61<br>R | RCC60<br>F | RCC60<br>R |  |

|                 | Reset Register Low                                                           | Туре      | w          | w          | w          | w          | w          | w          | w          | w          |  |

| A5 <sub>H</sub> | CCU6_ISRH Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Status         | Bit Field | RSTR       | RIDLE      | RWHE       | RCHE       | 0          | RTRPF      | RT13<br>PM | RT13<br>CM |  |

|                 | Reset Register High                                                          | Туре      | w          | w          | w          | w          | r          | w          | w          | w          |  |

| A6 <sub>H</sub> | CCU6_CMPMODIFL Reset: 00 <sub>H</sub><br>Compare State Modification Register | Bit Field | 0          | MCC63<br>S |            | 0          |            | MCC62<br>S | MCC61<br>S | MCC60<br>S |  |

|                 | Low                                                                          | Туре      | r          | w          |            | r          |            | w          | w          | w          |  |

| A7 <sub>H</sub> | CCU6_CMPMODIFH Reset: 00 <sub>H</sub><br>Compare State Modification Register | Bit Field | 0          | MCC63<br>R |            | 0          |            | MCC62<br>R | MCC61<br>R | MCC60<br>R |  |

|                 | High                                                                         | Туре      | r          | w          |            | r          |            | w          | w          | w          |  |

| FA <sub>H</sub> | CCU6_CC60SRL Reset: 00 <sub>H</sub><br>Capture/Compare Shadow Register for   | Bit Field |            |            |            | CC         | 60SL       |            |            |            |  |

|                 | Channel CC60 Low                                                             | Туре      |            |            |            | n          | wh         |            |            |            |  |

## Table 13 CCU6 Register Overview (cont'd)

| Addr            | Register Name                                                                               | Bit               | 7                 | 6           | 5           | 4           | 3           | 2           | 1           | 0           |  |  |

|-----------------|---------------------------------------------------------------------------------------------|-------------------|-------------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|--|--|

| FD <sub>H</sub> | CCU6_CC61RH Reset: 00 <sub>H</sub><br>Capture/Compare Register for Channel                  | Bit Field         |                   |             |             | CC6         | 51VH        |             |             |             |  |  |

|                 | CC61 High                                                                                   | Туре              |                   |             |             | r           | 'n          |             |             |             |  |  |

| FE <sub>H</sub> | CCU6_CC62RL Reset: 00 <sub>H</sub><br>Capture/Compare Register for Channel                  | Bit Field         | CC62VL            |             |             |             |             |             |             |             |  |  |

|                 | CC62 Low                                                                                    | Туре              | rh                |             |             |             |             |             |             |             |  |  |

| FF <sub>H</sub> | CCU6_CC62RH Reset: 00 <sub>H</sub><br>Capture/Compare Register for Channel                  | Bit Field         |                   |             |             | CCE         | 62VH        |             |             |             |  |  |

|                 | CC62 High                                                                                   | Туре              |                   |             |             | r           | 'n          |             |             |             |  |  |

|                 | 0, Page 2                                                                                   | 1                 |                   |             |             |             |             |             |             |             |  |  |

| 9A <sub>H</sub> | CCU6_T12MSELL Reset: 00 <sub>H</sub><br>T12 Capture/Compare Mode Select<br>Register Low     | Bit Field         |                   |             | EL61        |             |             |             | EL60        |             |  |  |

|                 | •                                                                                           | Туре              | 5510              | r           | W           |             |             |             | W           |             |  |  |

| 9B <sub>H</sub> | CCU6_T12MSELH Reset: 00 <sub>H</sub><br>T12 Capture/Compare Mode Select<br>Register High    | Bit Field         | DBYP              |             | HSYNC       |             |             |             | EL62        |             |  |  |

|                 |                                                                                             | Туре              | rw                | ENT 10      | rw          | FNOO        | ENICO       |             | W           | ENGO        |  |  |

| 9C <sub>H</sub> | CCU6_IENL Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Enable<br>Register Low        | Bit Field         | ENT12<br>PM       | ENT12<br>OM | ENCC<br>62F | ENCC<br>62R | ENCC<br>61F | ENCC<br>61R | ENCC<br>60F | ENCC<br>60R |  |  |

|                 | •                                                                                           | Туре              | rw                | rw          | rw          | rw          | rw          | rw          | rw          | rw          |  |  |

| 9D <sub>H</sub> | CCU6_IENH Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Enable<br>Register High       | Bit Field         | ENSTR             | EN<br>IDLE  | EN<br>WHE   | EN<br>CHE   | 0           | EN<br>TRPF  | ENT13<br>PM | ENT13<br>CM |  |  |

| 05              |                                                                                             | Type              | rw                | rw          | rw          | rw<br>CC62  | r           | rw          | rw          | rw          |  |  |

| 9E <sub>H</sub> | CCU6_INPL Reset: 40 <sub>H</sub><br>Capture/Compare Interrupt Node<br>Pointer Register Low  | Bit Field         |                   | CHE         |             |             | INPCC61 INP |             |             | CC60        |  |  |

| 05              | ÷                                                                                           | Type<br>Bit Field | rw rw<br>0 INPT13 |             |             |             | w<br>7T12   |             | w<br>ERR    |             |  |  |

| 9F <sub>H</sub> | CCU6_INPH Reset: 39 <sub>H</sub><br>Capture/Compare Interrupt Node<br>Pointer Register High | Type              |                   | r           |             | w           |             | rw          |             | W           |  |  |

| A4 <sub>H</sub> | CCU6_ISSL Reset: 00 <sub>H</sub>                                                            | Bit Field         | ST12P             | ST120       |             | SCC62       |             | SCC61       |             | SCC60       |  |  |

|                 | Capture/Compare Interrupt Status Set<br>Register Low                                        | Туре              | M                 | M           | F           | R           | F           | R           | F           | R           |  |  |

| A5 <sub>H</sub> | CCU6_ISSH Reset: 00 <sub>H</sub>                                                            | Bit Field         | SSTR              | SIDLE       | SWHE        | SCHE        |             |             | ST13        | ST13        |  |  |

| AJH             | Capture/Compare Interrupt Status Set<br>Register High                                       | Туре              | w                 | W           | w           | w           | w           | w           | PM          | CM          |  |  |

| A6 <sub>H</sub> | CCU6 PSLR Reset: 00 <sub>H</sub>                                                            | Bit Field         | PSL63             | 0           | vv          | vv          |             | SL          | vv          | vv          |  |  |

| A0H             | Passive State Level Register                                                                | Туре              | rwh               | r           |             |             |             | vh          |             |             |  |  |

| A7 <sub>H</sub> | CCU6_MCMCTR Reset: 00 <sub>H</sub>                                                          | Bit Field         |                   | )           | SW          | SYN         | 0           |             | SWSEL       |             |  |  |

|                 | Multi-Channel Mode Control Register                                                         | Туре              |                   | r           | r           | w           | r           |             | rw          |             |  |  |

| FA <sub>H</sub> | CCU6_TCTR2L Reset: 00 <sub>H</sub><br>Timer Control Register 2 Low                          | Bit Field         | 0                 | T13         | TED         |             | T13TEC      | ;           | T13<br>SSC  | T12<br>SSC  |  |  |

|                 |                                                                                             | Туре              | r                 | r           | w           |             | rw          |             | rw          | rw          |  |  |

| FB <sub>H</sub> | CCU6_TCTR2H Reset: 00 <sub>H</sub>                                                          | Bit Field         |                   |             | 0           |             | T13F        | RSEL        | T12         | RSEL        |  |  |

|                 | Timer Control Register 2 High                                                               | Туре              |                   |             | r           |             |             | w           | r           | w           |  |  |

| FC <sub>H</sub> | CCU6_MODCTRL Reset: 00 <sub>H</sub><br>Modulation Control Register Low                      | Bit Field         | MC<br>MEN         | 0           |             |             | T12MODEN    |             |             |             |  |  |

|                 |                                                                                             | Туре              | rw                | r           |             |             |             | w           |             |             |  |  |

| FD <sub>H</sub> | CCU6_MODCTRH Reset: 00 <sub>H</sub><br>Modulation Control Register High                     | Bit Field         | ECT13<br>O        | 0           |             |             | T13M        | ODEN        |             |             |  |  |

|                 |                                                                                             | Туре              | rw                | r           |             |             | r           | w           |             |             |  |  |

| FE <sub>H</sub> | CCU6_TRPCTRL Reset: 00 <sub>H</sub><br>Trap Control Register Low                            | Bit Field         |                   |             | 0           |             |             |             | TRPM1       | -           |  |  |

|                 | Trap Control Register Low                                                                   | Туре              |                   |             | r           |             |             | rw          | rw          | rw          |  |  |

## Table 13 CCU6 Register Overview (cont'd)

| Addr            | Register Name                                                             | Bit       | 7     | 6            | 5            | 4          | 3            | 2          | 1            | 0          |  |  |

|-----------------|---------------------------------------------------------------------------|-----------|-------|--------------|--------------|------------|--------------|------------|--------------|------------|--|--|

| FF <sub>H</sub> | CCU6_TRPCTRH Reset: 00 <sub>H</sub>                                       | Bit Field |       | TRPEN        |              |            | TRF          | PEN        |              |            |  |  |

|                 | Trap Control Register High                                                |           | N     | 13           |              |            |              |            |              |            |  |  |

|                 |                                                                           | Туре      | rw    | v rw rw      |              |            |              |            |              |            |  |  |

| RMAP =          | 0, Page 3                                                                 |           |       |              |              |            |              |            |              |            |  |  |

| 9A <sub>H</sub> | CCU6_MCMOUTL Reset: 00 <sub>H</sub><br>Multi-Channel Mode Output Register | Bit Field | 0     | R            | MCMP         |            |              |            |              |            |  |  |

|                 | Low                                                                       | Туре      | r     | rh           |              |            | r            | h          |              |            |  |  |

| 9B <sub>H</sub> | CCU6_MCMOUTH Reset: 00 <sub>H</sub><br>Multi-Channel Mode Output Register | Bit Field | (     | )            |              | CURH       |              |            | EXPH         |            |  |  |

|                 | High                                                                      | Туре      |       | r            |              | rh         |              |            | rh           |            |  |  |

| 9C <sub>H</sub> | CCU6_ISL Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Status       | Bit Field | T12PM | T12OM        | ICC62F       | R          | ICC61F       | ICC61<br>R | ICC60F       | ICC60<br>R |  |  |

|                 | Register Low                                                              | Туре      | rh    | rh           | rh           | rh         | rh           | rh         | rh           | rh         |  |  |

| 9D <sub>H</sub> | CCU6_ISH Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Status       | Bit Field | STR   | IDLE         | WHE          | CHE        | TRPS         | TRPF       | T13PM        | T13CM      |  |  |

|                 | Register High                                                             | Туре      | rh    | rh           | rh           | rh         | rh           | rh         | rh           | rh         |  |  |

| 9E <sub>H</sub> | CCU6_PISEL0L Reset: 00 <sub>H</sub>                                       | Bit Field | IST   | RP           | ISC          | C62        | ISC          | C61        |              |            |  |  |

|                 | Port Input Select Register 0 Low                                          | Туре      | r     | w            | r            | w          | r            |            |              |            |  |  |

| 9F <sub>H</sub> | CCU6_PISEL0H Reset: 00 <sub>H</sub><br>Port Input Select Register 0 High  | Bit Field | IST1  | 2HR          | ISPOS2 IS    |            | ISP          | POS1 ISF   |              | OS0        |  |  |

|                 |                                                                           | Туре      | r     | w            | n            | w          | n            | w          | n            | w          |  |  |

| A4 <sub>H</sub> | CCU6_PISEL2 Reset: 00 <sub>H</sub>                                        | Bit Field |       |              | (            | 2          |              |            | IST1         | 3HR        |  |  |

|                 | Port Input Select Register 2                                              | Туре      |       |              |              | r          |              |            | n            | w          |  |  |

| FA <sub>H</sub> | CCU6_T12L Reset: 00 <sub>H</sub>                                          | Bit Field |       |              |              | T12        | CVL          |            |              |            |  |  |

|                 | Timer T12 Counter Register Low                                            | Туре      |       |              |              | r.         | vh           |            |              |            |  |  |

| FB <sub>H</sub> | CCU6_T12H Reset: 00 <sub>H</sub>                                          | Bit Field |       |              |              | T12        | CVH          |            |              |            |  |  |

|                 | Timer T12 Counter Register High                                           | Туре      |       |              |              | ٢٧         | vh           |            |              |            |  |  |

| FC <sub>H</sub> | CCU6_T13L Reset: 00 <sub>H</sub>                                          | Bit Field |       |              |              | T13        | CVL          |            |              |            |  |  |

|                 | Timer T13 Counter Register Low                                            | Туре      |       |              |              | r.         | vh           |            |              |            |  |  |

| FD <sub>H</sub> | CCU6_T13H Reset: 00 <sub>H</sub>                                          | Bit Field |       |              |              | T13        | CVH          |            |              |            |  |  |

|                 | Timer T13 Counter Register High                                           | Туре      |       |              |              | n          | vh           |            |              |            |  |  |

| FE <sub>H</sub> | CCU6_CMPSTATL Reset: 00 <sub>H</sub><br>Compare State Register Low        | Bit Field | 0     | CC63<br>ST   | CCPO<br>S2   | CCPO<br>S1 | CCPO<br>S0   | CC62<br>ST | CC61<br>ST   | CC60<br>ST |  |  |

|                 |                                                                           | Туре      | r     | rh           | rh           | rh         | rh           | rh         | rh           | rh         |  |  |

| FF <sub>H</sub> | CCU6_CMPSTATH Reset: 00 <sub>H</sub><br>Compare State Register High       | Bit Field | T13IM | COUT<br>63PS | COUT<br>62PS | CC62<br>PS | COUT<br>61PS | CC61<br>PS | COUT<br>60PS | CC60<br>PS |  |  |

|                 |                                                                           | Туре      | rwh   | rwh          | rwh          | rwh        | rwh          | rwh        | rwh          | rwh        |  |  |

The SSC SFRs can be accessed in the standard memory area (RMAP = 0).

# Table 14SSC Register Overview

| Addr            | Register Name                            |                        | Bit       | 7  | 6  | 5  | 4  | 3 | 2   | 1   | 0   |

|-----------------|------------------------------------------|------------------------|-----------|----|----|----|----|---|-----|-----|-----|

| RMAP =          | 0                                        |                        | •         |    |    |    |    |   |     |     |     |

| A9 <sub>H</sub> | SSC_PISEL                                | Reset: 00 <sub>H</sub> | Bit Field |    |    | 0  |    |   | CIS | SIS | MIS |

|                 | Port Input Select Regist                 | er                     | Туре      |    |    | r  |    |   | rw  | rw  | rw  |

| AA <sub>H</sub> | SSC_CONL                                 | Reset: 00 <sub>H</sub> | Bit Field | LB | PO | PH | HB |   | В   | М   |     |

|                 | Control Register Low<br>Programming Mode |                        | Туре      | rw | rw | rw | rw |   | r   | w   |     |

|                 | Operating Mode                           |                        | Bit Field |    |    | 0  |    |   | B   | С   |     |

|                 |                                          |                        | Туре      |    |    | r  |    |   | r   | h   |     |

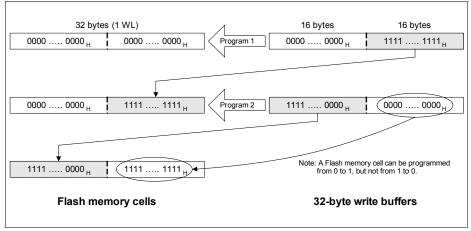

# 3.3.2 Flash Programming Width

For the P-Flash banks, a programmed wordline (WL) must be erased before it can be reprogrammed as the Flash cells can only withstand one gate disturb. This means that the entire sector containing the WL must be erased since it is impossible to erase a single WL.

For the D-Flash bank, the same WL can be programmed twice before erasing is required as the Flash cells are able to withstand two gate disturbs. Hence, it is possible to program the same WL, for example, with 16 bytes of data in two times (see Figure 12).

### Figure 12 D-Flash Programming

Note: When programming a D-Flash WL the second time, the previously programmed Flash memory cells (whether 0s or 1s) should be reprogrammed with 0s to retain its original contents and to prevent "over-programming".

# XC866

## **Functional Description**

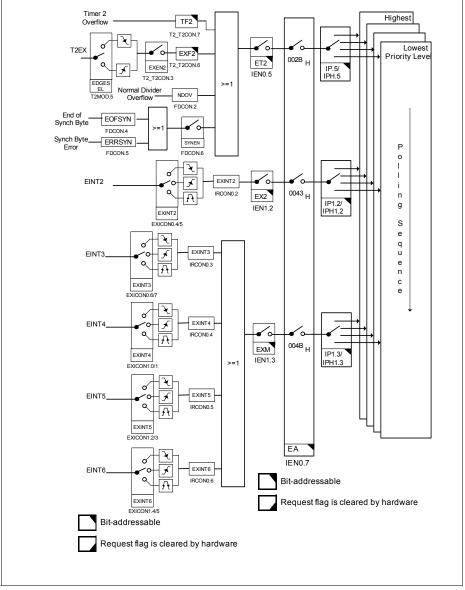

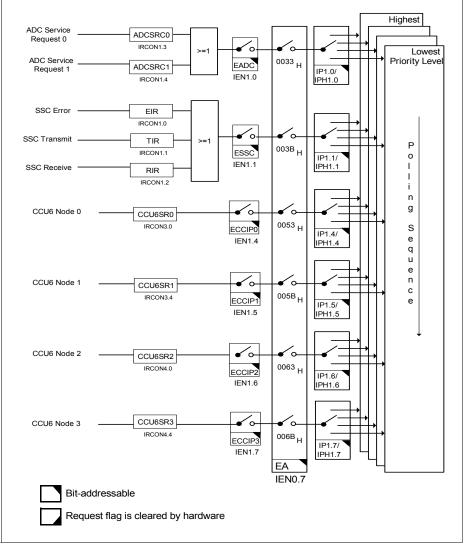

Figure 15 Interrupt Request Sources (Part 2)

Figure 16 Interrupt Request Sources (Part 3)

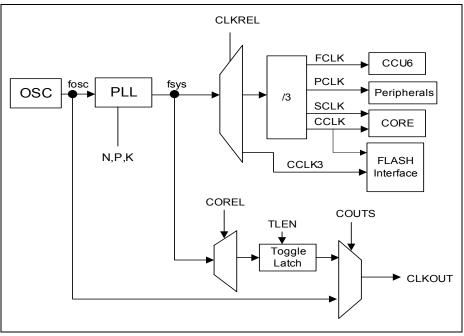

## 3.8.2 Clock Management

The CGU generates all clock signals required within the microcontroller from a single clock,  $f_{sys}$ . During normal system operation, the typical frequencies of the different modules are as follow:

- CPU clock: CCLK, SCLK = 26.7 MHz

- CCU6 clock: FCLK = 26.7 MHz

- Other peripherals: PCLK = 26.7 MHz

- Flash Interface clock: CCLK3 = 80 MHz and CCLK = 26.7 MHz

In addition, different clock frequency can output to pin CLKOUT(P0.0). The clock output frequency can further be divided by 2 using toggle latch (bit TLEN is set to 1), the resulting output frequency has 50% duty cycle. **Figure 25** shows the clock distribution of the XC866.

Figure 25 Clock Generation from f<sub>svs</sub>

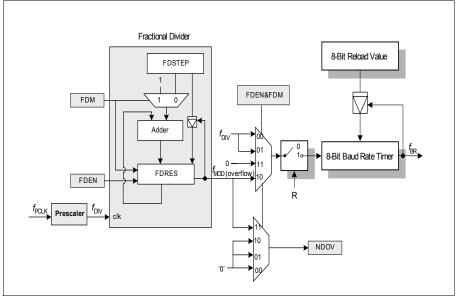

# 3.11.1 Baud-Rate Generator

The baud-rate generator is based on a programmable 8-bit reload value, and includes divider stages (i.e., prescaler and fractional divider) for generating a wide range of baud rates based on its input clock  $f_{PCLK}$ , see Figure 29.

### Figure 29 Baud-rate Generator Circuitry

The baud rate timer is a count-down timer and is clocked by either the output of the fractional divider ( $f_{MOD}$ ) if the fractional divider is enabled (FDCON.FDEN = 1), or the output of the prescaler ( $f_{DIV}$ ) if the fractional divider is disabled (FDEN = 0). For baud rate generation, the fractional divider must be configured to fractional divider mode (FDCON.FDM = 0). This allows the baud rate control run bit BCON.R to be used to start or stop the baud rate timer. At each timer underflow, the timer is reloaded with the 8-bit reload value in register BG and one clock pulse is generated for the serial channel.

Enabling the fractional divider in normal divider mode (FDEN = 1 and FDM = 1) stops the baud rate timer and nullifies the effect of bit BCON.R. See Section 3.12.

The baud rate  $(f_{BR})$  value is dependent on the following parameters:

- Input clock f<sub>PCLK</sub>

- Prescaling factor (2<sup>BRPRE</sup>) defined by bit field BRPRE in register BCON

- Fractional divider (STEP/256) defined by register FDSTEP (to be considered only if fractional divider is enabled and operating in fractional divider mode)

# 3.15 Timer 0 and Timer 1

Timers 0 and 1 are count-up timers which are incremented every machine cycle, or in terms of the input clock, every 2 PCLK cycles. They are fully compatible and can be configured in four different operating modes for use in a variety of applications, see **Table 28**. In modes 0, 1 and 2, the two timers operate independently, but in mode 3, their functions are specialized.

| Mode | Operation                                                                                                                                                                  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | <b>13-bit timer</b><br>The timer is essentially an 8-bit counter with a divide-by-32 prescaler.<br>This mode is included solely for compatibility with Intel 8048 devices. |

| 1    | <b>16-bit timer</b><br>The timer registers, TLx and THx, are concatenated to form a 16-bit counter.                                                                        |

| 2    | <b>8-bit timer with auto-reload</b><br>The timer register TLx is reloaded with a user-defined 8-bit value in THx upon overflow.                                            |

| 3    | Timer 0 operates as two 8-bit timersThe timer registers, TL0 and TH0, operate as two separate 8-bit counters.Timer 1 is halted and retains its count even if enabled.      |

#### Table 28 Timer 0 and Timer 1 Modes

XC866

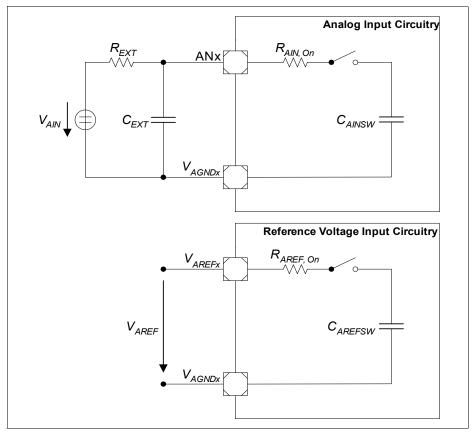

# 3.18 Analog-to-Digital Converter

The XC866 includes a high-performance 10-bit Analog-to-Digital Converter (ADC) with eight multiplexed analog input channels. The ADC uses a successive approximation technique to convert the analog voltage levels from up to eight different sources. The analog input channels of the ADC are available at Port 2.

## Features:

- Successive approximation

- 8-bit or 10-bit resolution (TUE of ± 1 LSB and ± 2 LSB, respectively)

- Eight analog channels

- · Four independent result registers

- Result data protection for slow CPU access

(wait-for-read mode)

- · Single conversion mode

- · Autoscan functionality

- · Limit checking for conversion results

- Data reduction filter (accumulation of up to 2 conversion results)

- · Two independent conversion request sources with programmable priority

- Selectable conversion request trigger

- · Flexible interrupt generation with configurable service nodes

- Programmable sample time

- · Programmable clock divider

- · Cancel/restart feature for running conversions

- · Integrated sample and hold circuitry

- · Compensation of offset errors

- · Low power modes

### **Electrical Parameters**

# 4.2.3.1 ADC Conversion Timing

Conversion time,  $t_C = t_{ADC} \times (1 + r \times (3 + n + STC))$ , where r = CTC + 2 for CTC =  $00_B$ ,  $01_B$  or  $10_B$ , r = 32 for CTC =  $11_B$ , CTC = Conversion Time Control (GLOBCTR.CTC), STC = Sample Time Control (INPCR0.STC), n = 8 or 10 (for 8-bit and 10-bit conversion respectively),  $t_{ADC} = 1 / f_{ADC}$

#### **Electrical Parameters**

## 4.2.4 Power Supply Current

# Table 37Power Supply Current Parameters (Operating Conditions apply; $V_{\text{DDP}}$ = 5V range )

| Parameter                           | Symbol           | Limit Values       |                    | Unit | Test Condition                         |

|-------------------------------------|------------------|--------------------|--------------------|------|----------------------------------------|

|                                     |                  | typ. <sup>1)</sup> | max. <sup>2)</sup> | +    | Remarks                                |

| V <sub>DDP</sub> = 5V Range         |                  |                    |                    |      |                                        |

| Active Mode                         | I <sub>DDP</sub> | 22.6               | 24.5               | mA   | 3)                                     |

| Idle Mode                           | I <sub>DDP</sub> | 17.2               | 19.7               | mA   | XC866-4FR,<br>XC866-2FR <sup>4)</sup>  |

|                                     |                  | 12.5               | 14                 | mA   | XC866-1FR,<br>ROM device <sup>4)</sup> |

| Active Mode with slow-down enabled  | I <sub>DDP</sub> | 7.2                | 8.2                | mA   | XC866-4FR,<br>XC866-2FR <sup>5)</sup>  |

|                                     |                  | 5.6                | 7.5                | mA   | XC866-1FR,<br>ROM device <sup>5)</sup> |

| Idle Mode with slow-down<br>enabled | I <sub>DDP</sub> | 7.1                | 8                  | mA   | XC866-4FR,<br>XC866-2FR <sup>6)</sup>  |

|                                     |                  | 5.1                | 7.2                | mA   | XC866-1FR,<br>ROM device <sup>6)</sup> |

<sup>1)</sup> The typical  $I_{\text{DDP}}$  values are periodically measured at  $T_{\text{A}}$  = + 25 °C and  $V_{\text{DDP}}$  = 5.0 V.

<sup>2)</sup> The maximum  $I_{\text{DDP}}$  values are measured under worst case conditions ( $T_{\text{A}}$  = + 125 °C and  $V_{\text{DDP}}$  = 5.5 V).

- <sup>3)</sup> I<sub>DDP</sub> (active mode) is measured with: CPU clock and input clock to all peripherals running at 26.7 MHz(set by on-chip oscillator of 10 MHz and NDIV in PLL\_CON to 0010<sub>B</sub>), RESET =  $V_{DDP}$ , no load on ports.

- <sup>4)</sup> I<sub>DDP</sub> (idle mode) is measured with: <u>CPU clock disabled</u>, watchdog timer disabled, input clock to all peripherals enabled and running at 26.7 MHz, <u>RESET</u> = V<sub>DDP</sub>, no load on ports.

- <sup>5)</sup> I<sub>DDP</sub> (active mode with slow-down mode) is measured with: CPU clock and input clock to all peripherals running at 833 KHz by setting CLKREL in CMCON to 0101<sub>B</sub>, RESET = V<sub>DDP</sub>, no load on ports.

- <sup>6)</sup> I<sub>DDP</sub> (idle mode with slow-down mode) is measured with: CPU clock disabled, watchdog timer disabled, input <u>clock to</u> all peripherals enabled and running at 833 KHz by setting CLKREL in CMCON to 0101<sub>B</sub>, <u>RESET</u> = V<sub>DDP</sub>, no load on ports.

#### **Electrical Parameters**

# Table 40Power Down Current (Operating Conditions apply; $V_{\text{DDP}}$ = 3.3Vrange )

| Parameter                     | Symbol           | Limit Values       |                    | Unit | Test Condition                                               |

|-------------------------------|------------------|--------------------|--------------------|------|--------------------------------------------------------------|

|                               |                  | typ. <sup>1)</sup> | max. <sup>2)</sup> |      | Remarks                                                      |

| V <sub>DDP</sub> = 3.3V Range |                  | - 4                | 1                  | 1    |                                                              |

| Power-Down Mode <sup>3)</sup> | I <sub>PDP</sub> | 1                  | 10                 | μA   | $T_{\rm A}$ = + 25 °C. <sup>4</sup> )                        |

|                               |                  | -                  | 30                 | μA   | $T_{A}$ = + 85 °C, XC866-<br>4FR, XC866-2FR <sup>4)5)</sup>  |

|                               |                  | -                  | 35                 | μA   | $T_{A}$ = + 85 °C, XC866-<br>1FR, ROM device <sup>4)5)</sup> |

<sup>1)</sup> The typical  $I_{PDP}$  values are measured at  $V_{DDP}$  = 3.3 V.

$^{2)}\,$  The maximum  $I_{\rm PDP}$  values are measured at  $V_{\rm DDP}$  = 3.6 V.

<sup>3)</sup> I<sub>PDP</sub> (power-down mode) has a maximum value of 200  $\mu$ A at  $T_A$  = + 125 °C.

<sup>4)</sup> I<sub>PDP</sub> (power-down mode) is measured with: RESET = V<sub>DDP</sub>, V<sub>AGND</sub>= V<sub>SS</sub>, RXD/INT0= V<sub>DDP</sub>; rest of the ports are programmed to be input with either internal pull devices enabled or driven externally to ensure no floating inputs.

<sup>5)</sup> Not subject to production test, verified by design/characterization.