Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                      |

| Core Processor             | XC800                                                                         |

| Core Size                  | 8-Bit                                                                         |

| Speed                      | 86MHz                                                                         |

| Connectivity               | LINbus, SSI, UART/USART                                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                         |

| Number of I/O              | 19                                                                            |

| Program Memory Size        | 8KB (8K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 768 x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                   |

| Data Converters            | A/D 8x10b                                                                     |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 38-TFSOP (0.173", 4.40mm Width)                                               |

| Supplier Device Package    | PG-TSSOP-38                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/sak-xc866l-2fri-be |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Edition 2007-10 Published by Infineon Technologies AG, 81726 München, Germany © Infineon Technologies AG 2007. All Rights Reserved.

#### Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie"). With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of noninfringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

| Data Sheet<br>n History: | 2007-10                                                                                                                                                                         | V1.2                               |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| V1.0                     | 2006-02                                                                                                                                                                         |                                    |

| Subjects (               | najor changes since last revision)                                                                                                                                              | )                                  |

| Device sur               | nmary table is updated for Flash                                                                                                                                                | 4-Kb and ROM variants.             |

| Footnote is              | added to MBC pin; description o                                                                                                                                                 | f $V_{\text{DDP}}$ pin is updated. |

|                          | •                                                                                                                                                                               | s type of register bit field       |

| Access typ               | e of PAGE bits of all module page                                                                                                                                               | registers are corrected to rwh.    |

| Access typ               | e of Px_DIR register bits are corr                                                                                                                                              | ected to rwh                       |

| New bullet               | point on Flash delivery state is a                                                                                                                                              | dded to the feature list.          |

| Digital pov              | er supply voltage are differentiate                                                                                                                                             | ed for 5V and 3.3V variants.       |

|                          | 5                                                                                                                                                                               | /oltage on GPIO pins during        |

| Figure on                | Power-on reset timing is updated.                                                                                                                                               |                                    |

|                          | n History:<br>S Version: V 0.1<br>V1.0,<br>V1.1,<br>Subjects (n<br>Device sum<br>Footnote is<br>Section on<br>PASSWD.F<br>Access type<br>New bullet<br>Digital pow<br>VDDP powe |                                    |

# We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to:

mcdocu.comments@infineon.com

$\ge$

# XC866

# **General Device Information**

| Table 3 | Pin D         | efinitio | ons and        | Functions (c                         | ont'd)                                                                                                                                       |

|---------|---------------|----------|----------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol  | Pin<br>Number | Туре     | Reset<br>State | Function                             |                                                                                                                                              |

| P2      |               | I        |                | can be used inputs of the            | bit general purpose input-only port. It<br>as alternate functions for the digital<br>JTAG and CCU6. It is also used as the<br>s for the ADC. |

| P2.0    | 15            |          | Hi-Z           | EXINT1<br>T12HR_2                    | CCU6 Hall Input 0<br>External Interrupt Input 1<br>CCU6 Timer 12 Hardware Run<br>Input                                                       |

|         |               |          |                | TCK_1<br>CC61_3<br>AN0               | JTAG Clock Input<br>Input of Capture/Compare channel 1<br>Analog Input 0                                                                     |

| P2.1    | 16            |          | Hi-Z           | CCPOS1_0<br>EXINT2<br>T13HR_2        | CCU6 Hall Input 1<br>External Interrupt Input 2<br>CCU6 Timer 13 Hardware Run<br>Input                                                       |

|         |               |          |                | TDI_1<br>CC62_3<br>AN1               | JTAG Serial Data Input<br>Input of Capture/Compare channel 2<br>Analog Input 1                                                               |

| P2.2    | 17            |          | Hi-Z           | CCPOS2_0<br>CTRAP_1<br>CC60_3<br>AN2 | CCU6 Hall Input 2<br>CCU6 Trap Input<br>Input of Capture/Compare channel 0<br>Analog Input 2                                                 |

| P2.3    | 20            |          | Hi-Z           | AN3                                  | Analog Input 3                                                                                                                               |

| P2.4    | 21            |          | Hi-Z           | AN4                                  | Analog Input 4                                                                                                                               |

| P2.5    | 22            |          | Hi-Z           | AN5                                  | Analog Input 5                                                                                                                               |

| P2.6    | 23            |          | Hi-Z           | AN6                                  | Analog Input 6                                                                                                                               |

| P2.7    | 26            |          | Hi-Z           | AN7                                  | Analog Input 7                                                                                                                               |

# XC866

#### **General Device Information**

| Symbol            | Pin<br>Number | Туре | Reset<br>State | Function                                                              |

|-------------------|---------------|------|----------------|-----------------------------------------------------------------------|

| V <sub>DDP</sub>  | 18            | -    | -              | I/O Port Supply (3.3 V/5.0 V)<br>Also used by EVR and analog modules. |

| V <sub>SSP</sub>  | 19            | -    | -              | I/O Port Ground                                                       |

| V <sub>DDC</sub>  | 8             | -    | -              | Core Supply Monitor (2.5 V)                                           |

| V <sub>ssc</sub>  | 7             | -    | _              | Core Supply Ground                                                    |

| V <sub>AREF</sub> | 25            | -    | -              | ADC Reference Voltage                                                 |

| V <sub>AGND</sub> | 24            | -    | _              | ADC Reference Ground                                                  |

| XTAL1             | 6             | I    | Hi-Z           | External Oscillator Input<br>(NC if not needed)                       |

| XTAL2             | 5             | 0    | Hi-Z           | External Oscillator Output<br>(NC if not needed)                      |

| TMS               | 11            | I    | PD             | Test Mode Select                                                      |

| RESET             | 38            | I    | PU             | Reset Input                                                           |

| MBC <sup>1)</sup> | 1             | I    | PU             | Monitor & BootStrap Loader Control                                    |

#### Table 3 Pin Definitions and Functions (cont'd)

<sup>1)</sup> An external pull-up device in the range of 4.7 k $\Omega$  to 100 k $\Omega$  is required to enter user mode. Alternatively MBC can be tied to high if alternate functions (for debugging) of the pin are not utilized.

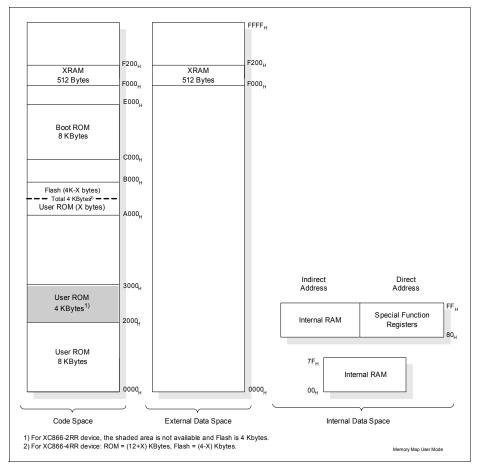

# Figure 7 illustrates the memory address spaces of the XC866-4RR device.

Figure 7 Memory Map of XC866 ROM Devices

| Field | Bits  | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------|-------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OP    | [7:6] | W    | <ul> <li>Operation</li> <li>OX Manual page mode. The value of STNR is ignored and PAGE is directly written.</li> <li>10 New page programming with automatic page saving. The value written to the bit positions of PAGE is stored. In parallel, the previous contents of PAGE are saved in the storage bit field STx indicated by STNR.</li> <li>11 Automatic restore page action. The value written to the bit positions PAGE is ignored and instead, PAGE is overwritten by the contents of the storage bit field STx indicated by STNR.</li> </ul> |

| 0     | 3     | r    | <b>Reserved</b><br>Returns 0 if read; should be written with 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

#### Table 11 ADC Register Overview (cont'd)

| Addr                      | Register Name                         |                        | Bit       | 7     | 6       | 5   | 4    | 3        | 2     | 1    | 0     |

|---------------------------|---------------------------------------|------------------------|-----------|-------|---------|-----|------|----------|-------|------|-------|

| CA <sub>H</sub>           | ADC_RESR0L                            | Reset: 00 <sub>H</sub> | Bit Field | RESU  | LT[1:0] | 0   | VF   | DRC      |       | CHNR |       |

|                           | Result Register 0 Low                 |                        | Туре      | r     | h       | r   | rh   | rh       |       | rh   |       |

| CB <sub>H</sub>           | ADC_RESR0H                            | Reset: 00 <sub>H</sub> | Bit Field |       |         |     | RESU | LT[9:2]  | 1     |      |       |

|                           | Result Register 0 High                |                        | Туре      |       |         |     | r    | ħ        |       |      |       |

| CCH                       | ADC_RESR1L                            | Reset: 00 <sub>H</sub> | Bit Field | RESU  | LT[1:0] | 0   | VF   | DRC      |       | CHNR |       |

|                           | Result Register 1 Low                 |                        | Туре      | r     | h       | r   | rh   | rh       |       | rh   |       |

| CD <sub>H</sub>           | ADC RESR1H                            | Reset: 00 <sub>H</sub> | Bit Field |       |         | i   | RESU | LT[9:2]  |       |      |       |

|                           | Result Register 1 High                |                        | Туре      |       |         |     | r    | h i      |       |      |       |

| CEH                       | ADC RESR2L                            | Reset: 00 <sub>H</sub> | Bit Field | RESU  | LT[1:0] | 0   | VF   | DRC      |       | CHNR |       |

|                           | Result Register 2 Low                 |                        | Туре      | r     | h       | r   | rh   | rh       |       | rh   |       |

| CF <sub>H</sub>           | ADC RESR2H                            | Reset: 00 <sub>H</sub> | Bit Field |       |         | i   | RESU | LT[9:2]  |       |      |       |

| - 11                      | Result Register 2 High                |                        | Туре      |       |         |     |      | h i      |       |      |       |

| D2 <sub>H</sub>           | ADC_RESR3L                            | Reset: 00 <sub>H</sub> | Bit Field | RESU  | LT[1:0] | 0   | VF   | DRC      |       | CHNR |       |

|                           | Result Register 3 Low                 |                        | Туре      | r     |         | r   | rh   | rh       |       | rh   |       |

| D3 <sub>H</sub>           | ADC RESR3H                            | Reset: 00 <sub>H</sub> | Bit Field |       |         |     | RESU | LT[9:2]  |       |      |       |

|                           | Result Register 3 High                |                        | Туре      |       |         |     |      | h i      |       |      |       |

| RMAP =                    | = 0, Page 3                           |                        | . ) [ -   |       |         |     |      |          |       |      |       |

| CA <sub>H</sub>           | ADC RESRAOL                           | Reset: 00 <sub>H</sub> | Bit Field | RF    | ESULT[2 | ·01 | VF   | DRC      |       | CHNR |       |

| 0, H                      | Result Register 0, View A             |                        | Туре      |       |         | .0] | rh   | rh       |       | rh   |       |

| CBH                       | ADC RESRAOH                           | Reset: 00 <sub>H</sub> | Bit Field |       |         |     |      | _T[10:3] |       |      |       |

| ODH                       | Result Register 0, View A             |                        | Туре      |       |         |     |      | h        |       |      |       |

| CCH                       | ADC RESRA1L                           | Reset: 00 <sub>H</sub> | Bit Field | RF    | ESULT[2 | ·01 | VF . | DRC      |       | CHNR |       |

| OOH                       | Result Register 1, View A             |                        | Туре      | T.L   | rh      | .0] | rh   | rh       |       | rh   |       |

| CD <sub>H</sub>           | ADC RESRA1H                           | Reset: 00 <sub>H</sub> | Bit Field |       |         |     |      | _T[10:3] |       |      |       |

| ODH                       | Result Register 1, View A             |                        | Туре      |       |         |     |      | h        |       |      |       |

| CEH                       | ADC RESRA2L                           | Reset: 00 <sub>H</sub> | Bit Field | D     | ESULT[2 | ·01 | VF   | DRC      |       | CHNR |       |

| СГН                       | Result Register 2, View A             |                        | Type      | INL   | rh      | .0] | rh   | rh       |       | rh   |       |

| CF <sub>H</sub>           | ADC RESRA2H                           | Reset: 00 <sub>H</sub> | Bit Field |       |         |     |      | _T[10:3] |       |      |       |

| CFH                       | Result Register 2, View A             |                        | Туре      |       |         |     |      | h        |       |      |       |

| D2 <sub>H</sub>           | ADC RESRA3L                           | Reset: 00 <sub>H</sub> | Bit Field | D     | ESULT[2 | .01 | VF   | DRC      |       | CHNR |       |

| DZH                       | Result Register 3, View A             |                        | Type      | R     | rh      | .0] | rh   | rh       |       | rh   |       |

| D2                        | ADC RESRA3H                           |                        | Bit Field |       | m       |     |      |          |       | m    |       |

| D3 <sub>H</sub>           | Result Register 3, View A             | Reset: 00 <sub>H</sub> |           |       |         |     |      | _T[10:3] |       |      |       |

|                           |                                       |                        | Туре      |       |         |     | I    | 'n       |       |      |       |

|                           | O, Page 4                             | D                      | Bit Field | VECTR | WFR     | 0   | IEN  | 1        | 0     |      | DRCT  |

| CA <sub>H</sub>           | Result Control Register (             | Reset: 00 <sub>H</sub> | BIT FIEID | VECTR | WFR     | 0   | IEN  |          | 0     |      | R     |

|                           | result control register e             | ,                      | Туре      | rw    | rw      | r   | rw   |          | r     |      | rw    |

| CB <sub>H</sub>           | ADC RCR1                              | Reset: 00 <sub>H</sub> | Bit Field | VFCTR | WFR     | 0   | IEN  |          | 0     |      | DRCT  |

| CDH                       | Result Control Register 1             |                        | DILFIEIU  | VFUIR | WER     | 0   | IEIN |          | 0     |      | R     |

|                           | 3                                     |                        | Туре      | rw    | rw      | r   | rw   |          | r     |      | rw    |

| CCH                       | ADC RCR2                              | Reset: 00 <sub>H</sub> | Bit Field | VFCTR | WFR     | 0   | IEN  |          | 0     |      | DRCT  |

| Result Control Register 2 |                                       |                        |           |       |         |     |      |          |       | R    |       |

|                           |                                       |                        | Туре      | rw    | rw      | r   | rw   |          | r     |      | rw    |

| CD <sub>H</sub>           | ADC_RCR3                              | Reset: 00 <sub>H</sub> | Bit Field | VFCTR | WFR     | 0   | IEN  |          | 0     |      | DRCT  |

|                           | Result Control Register 3             | 3                      |           |       |         |     |      |          |       |      | R     |

|                           |                                       |                        | Туре      | rw    | rw      | r   | rw   |          | r     |      | rw    |

|                           |                                       |                        | Bit Field |       |         | )   |      | VFC3     | VFC2  | VFC1 | VFC0  |

| CEH                       | ADC_VFCR<br>Valid Flag Clear Register | Reset: 00 <sub>H</sub> | BILFIEID  |       |         | 5   |      | VI 05    | VI 02 | VICI | VI C0 |

#### Table 13 CCU6 Register Overview (cont'd)

| Addr            | Register Name                                                                                   | Bit       | 7   | 6    | 5     | 4    | 3          | 2    | 1      | 0    |

|-----------------|-------------------------------------------------------------------------------------------------|-----------|-----|------|-------|------|------------|------|--------|------|

| FB <sub>H</sub> | CCU6_CC60SRH Reset: 00 <sub>H</sub><br>Capture/Compare Shadow Register for                      | Bit Field |     | I    | I     | CC6  | 0SH        | I    | 1      | 1    |

|                 | Channel CC60 High                                                                               | Туре      |     |      |       | rv   | vh         |      |        |      |

| FC <sub>H</sub> | CCU6_CC61SRL Reset: 00 <sub>H</sub><br>Capture/Compare Shadow Register for                      | Bit Field |     |      |       | CCE  | i1SL       |      |        |      |

|                 | Channel CC61 Low                                                                                | Туре      |     |      |       | rv   | vh         |      |        |      |

| FD <sub>H</sub> | CCU6_CC61SRH Reset: 00 <sub>H</sub><br>Capture/Compare Shadow Register for                      | Bit Field |     |      |       |      | 1SH        |      |        |      |

|                 | Channel CC61 High                                                                               | Туре      |     |      |       |      | vh         |      |        |      |

| FE <sub>H</sub> | CCU6_CC62SRL Reset: 00 <sub>H</sub><br>Capture/Compare Shadow Register for<br>Channel CC62 Low  | Bit Field |     |      |       |      | 2SL        |      |        |      |

|                 |                                                                                                 | Туре      |     |      |       |      | vh         |      |        |      |

| FF <sub>H</sub> | CCU6_CC62SRH Reset: 00 <sub>H</sub><br>Capture/Compare Shadow Register for<br>Channel CC62 High | Bit Field |     |      |       |      | 2SH        |      |        |      |

| -               | Ũ                                                                                               | Туре      |     |      |       | rv   | vh         |      |        |      |

|                 | 0, Page 1                                                                                       | Bit Field |     |      |       | 000  | 2)//       |      |        |      |

| 9A <sub>H</sub> | CCU6_CC63RL Reset: 00 <sub>H</sub><br>Capture/Compare Register for Channel<br>CC63 Low          |           |     |      |       |      | 3VL        |      |        |      |

| 00              |                                                                                                 | Type      |     |      |       |      | h          |      |        |      |

| 9B <sub>H</sub> | CCU6_CC63RH Reset: 00 <sub>H</sub><br>Capture/Compare Register for Channel<br>CC63 High         | Bit Field |     |      |       |      | 3VH        |      |        |      |

|                 | -                                                                                               | Type      |     |      |       |      | h<br>D) (I |      |        |      |

| 9C <sub>H</sub> | CCU6_T12PRL Reset: 00 <sub>H</sub><br>Timer T12 Period Register Low                             | Bit Field |     |      |       |      | PVL        |      |        |      |

|                 | -                                                                                               | Туре      |     |      |       |      | vh         |      |        |      |

| 9D <sub>H</sub> | CCU6_T12PRH Reset: 00 <sub>H</sub><br>Timer T12 Period Register High                            | Bit Field |     |      |       |      | PVH        |      |        |      |

|                 |                                                                                                 | Туре      |     |      |       |      | vh         |      |        |      |

| 9E <sub>H</sub> | CCU6_T13PRL Reset: 00 <sub>H</sub><br>Timer T13 Period Register Low                             | Bit Field |     |      |       |      | PVL        |      |        |      |

|                 | 8                                                                                               | Туре      |     |      |       |      | vh         |      |        |      |

| 9F <sub>H</sub> | CCU6_T13PRH Reset: 00 <sub>H</sub><br>Timer T13 Period Register High                            | Bit Field |     |      |       |      | PVH        |      |        |      |

|                 |                                                                                                 | Туре      |     |      |       |      | vh         |      |        |      |

| A4 <sub>H</sub> | CCU6_T12DTCL Reset: 00 <sub>H</sub><br>Dead-Time Control Register for Timer                     | Bit Field |     |      |       |      | ГM         |      |        |      |

|                 | T12 Low                                                                                         | Туре      |     |      |       | r    | N          |      |        |      |

| A5 <sub>H</sub> | CCU6_T12DTCH Reset: 00 <sub>H</sub><br>Dead-Time Control Register for Timer                     | Bit Field | 0   | DTR2 | DTR1  | DTR0 | 0          | DTE2 | DTE1   | DTE0 |

|                 | T12 High                                                                                        | Туре      | r   | rh   | rh    | rh   | r          | rw   | rw     | rw   |

| A6 <sub>H</sub> | CCU6_TCTR0L Reset: 00 <sub>H</sub><br>Timer Control Register 0 Low                              | Bit Field | СТМ | CDIR | STE12 | T12R | T12<br>PRE |      | T12CLK |      |

|                 |                                                                                                 | Туре      | rw  | rh   | rh    | rh   | rw         |      | rw     |      |

| A7 <sub>H</sub> | CCU6_TCTR0H Reset: 00 <sub>H</sub><br>Timer Control Register 0 High                             | Bit Field | (   | )    | STE13 | T13R | T13<br>PRE |      | T13CLK |      |

|                 |                                                                                                 | Туре      |     | r    | rh    | rh   | rw         |      | rw     |      |

| FA <sub>H</sub> | CCU6_CC60RL Reset: 00 <sub>H</sub><br>Capture/Compare Register for Channel                      | Bit Field |     |      |       |      | 60VL       |      |        |      |

|                 | CC60 Low                                                                                        | Туре      |     |      |       |      | h          |      |        |      |

| FB <sub>H</sub> | CCU6_CC60RH Reset: 00 <sub>H</sub><br>Capture/Compare Register for Channel<br>CC60 High         | Bit Field |     |      |       |      | 0VH        |      |        |      |

|                 | e e                                                                                             | Туре      |     |      |       |      | h          |      |        |      |

| FC <sub>H</sub> | CCU6_CC61RL Reset: 00 <sub>H</sub><br>Capture/Compare Register for Channel                      | Bit Field |     |      |       |      | 51VL       |      |        |      |

|                 | CC61 Low                                                                                        | Туре      |     |      |       | r    | h          |      |        |      |

| P-Flash              | D-Flash            |

|----------------------|--------------------|

|                      | Sector 0: 1-Kbyte  |

|                      | Sector 1: 1-Kbyte  |

| Sector 0: 3.75-Kbyte | Sector 2: 512-byte |

|                      | Sector 3: 512-byte |

|                      | Sector 4: 256-byte |

|                      | Sector 5: 256-byte |

|                      | Sector 6: 128-byte |

|                      | Sector 7: 128-byte |

| Sector 1: 128-byte   | Sector 8: 128-byte |

| Sector 2: 128-byte   | Sector 9: 128-byte |

#### Figure 11 Flash Bank Sectorization

The internal structure of each Flash bank represents a sector architecture for flexible erase capability. The minimum erase width is always a complete sector, and sectors can be erased separately or in parallel. Contrary to standard EPROMs, erased Flash memory cells contain 0s.

The D-Flash bank is divided into more physical sectors for extended erasing and reprogramming capability; even numbers for each sector size are provided to allow greater flexibility and the ability to adapt to a wide range of application requirements.

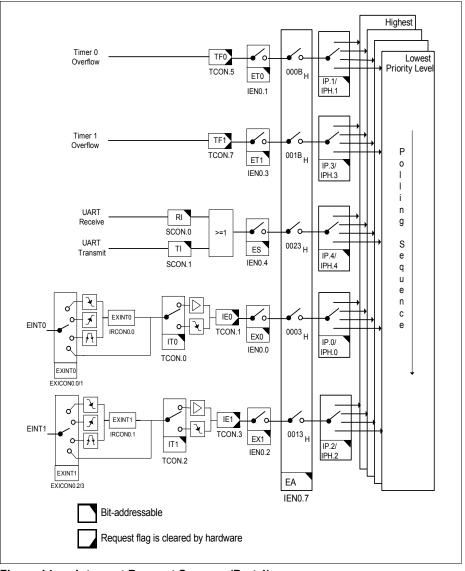

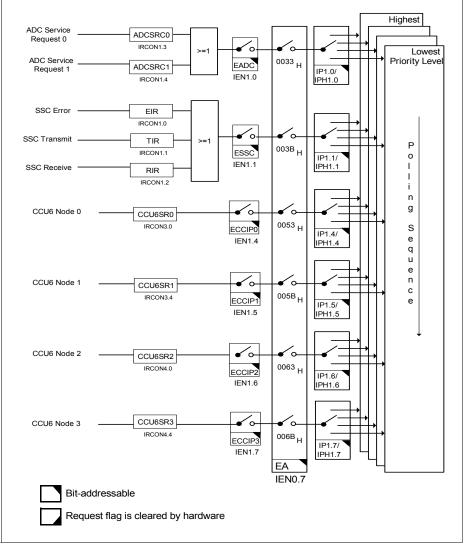

Figure 14 Interrupt Request Sources (Part 1)

# XC866

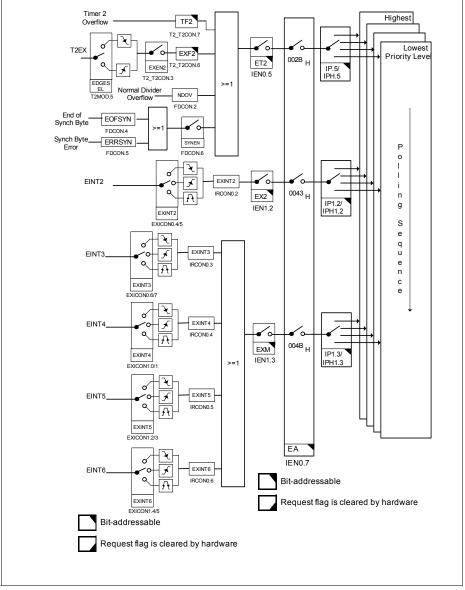

Figure 15 Interrupt Request Sources (Part 2)

Figure 16 Interrupt Request Sources (Part 3)

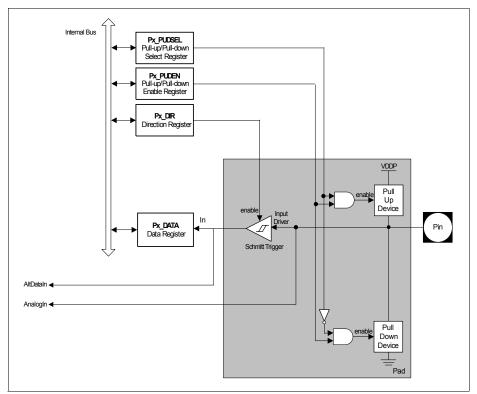

Figure 19 General Structure of Input Port

# 3.7.1 Module Reset Behavior

Table 19 shows how the functions of the XC866 are affected by the various reset types. A "∎" means that this function is reset to its default state.

| Module/<br>Function   | Wake-Up<br>Reset                     | Watchdog<br>Reset      | Hardware<br>Reset      | Power-On<br>Reset         | Brownout<br>Reset         |

|-----------------------|--------------------------------------|------------------------|------------------------|---------------------------|---------------------------|

| CPU Core              |                                      |                        |                        |                           |                           |

| Peripherals           |                                      |                        |                        |                           |                           |

| On-Chip<br>Static RAM | Not affected, reliable               | Not affected, reliable | Not affected, reliable | Affected, un-<br>reliable | Affected, un-<br>reliable |

| Oscillator,<br>PLL    |                                      | Not affected           |                        |                           |                           |

| Port Pins             |                                      |                        |                        |                           |                           |

| EVR                   | The voltage regulator is switched on | Not affected           |                        |                           |                           |

| FLASH                 |                                      |                        |                        |                           |                           |

| NMI                   | Disabled                             | Disabled               |                        |                           |                           |

Table 19 Effect of Reset on Device Functions

# 3.7.2 Booting Scheme

When the XC866 is reset, it must identify the type of configuration with which to start the different modes once the reset sequence is complete. Thus, boot configuration information that is required for activation of special modes and conditions needs to be applied by the external world through input pins. After power-on reset or hardware reset, the pins MBC, TMS and P0.0 collectively select the different boot options. Table 20 shows the available boot options in the XC866.

| MBC | TMS | P0.0 | Type of Mode                                                                      | PC Start Value    |

|-----|-----|------|-----------------------------------------------------------------------------------|-------------------|

| 1   | 0   | х    | User Mode; on-chip OSC/PLL non-bypassed                                           | 0000 <sub>H</sub> |

| 0   | 0   | х    | BSL Mode; on-chip OSC/PLL non-bypassed                                            | 0000 <sub>H</sub> |

| 0   | 1   | 0    | OCDS Mode <sup>1)</sup> ; on-chip OSC/PLL non-<br>bypassed                        | 0000 <sub>H</sub> |

| 1   | 1   | 0    | Standalone User (JTAG) Mode <sup>2)</sup> ; on-chip OSC/PLL non-bypassed (normal) | 0000 <sub>H</sub> |

Table 20 XC866 Boot Selection

<sup>1)</sup> The OCDS mode is not accessible if Flash is protected.

<sup>2)</sup> Normal user mode with standard JTAG (TCK,TDI,TDO) pins for hot-attach purpose.

115.2 kHz, using different module clock frequencies. The fractional divider is enabled (fractional divider mode) and the corresponding parameter settings are shown.

#### Table 27 Deviation Error for UART with Fractional Divider enabled

| f <sub>PCLK</sub> | Prescaling Factor<br>(2 <sup>BRPRE</sup> ) | Reload Value<br>(BR_VALUE + 1) | STEP                   | Deviation<br>Error |

|-------------------|--------------------------------------------|--------------------------------|------------------------|--------------------|

| 26.67 MHz         | 1                                          | 10 (A <sub>H</sub> )           | 177 (B1 <sub>H</sub> ) | +0.03 %            |

| 13.33 MHz         | 1                                          | 7 (7 <sub>H</sub> )            | 248 (F8 <sub>H</sub> ) | +0.11 %            |

| 6.67 MHz          | 1                                          | 3 (3 <sub>H</sub> )            | 212 (D4 <sub>H</sub> ) | -0.16 %            |

# 3.14 High-Speed Synchronous Serial Interface

The High-Speed Synchronous Serial Interface (SSC) supports full-duplex and half-duplex synchronous communication. The serial clock signal can be generated by the SSC internally (master mode), using its own 16-bit baud-rate generator, or can be received from an external master (slave mode). Data width, shift direction, clock polarity and phase are programmable. This allows communication with SPI-compatible devices or devices using other synchronous serial interfaces.

#### Features:

- · Master and slave mode operation

- Full-duplex or half-duplex operation

- Transmit and receive buffered

- Flexible data format

- Programmable number of data bits: 2 to 8 bits

- Programmable shift direction: LSB or MSB shift first

- Programmable clock polarity: idle low or high state for the shift clock

- Programmable clock/data phase: data shift with leading or trailing edge of the shift clock

- · Variable baud rate

- Compatible with Serial Peripheral Interface (SPI)

- Interrupt generation

- On a transmitter empty condition

- On a receiver full condition

- On an error condition (receive, phase, baud rate, transmit error)

# XC866

# **Electrical Parameters**

#### Table 34 Input/Output Characteristics (Operating Conditions apply)

| Parameter                                                   | Symb               | ol | Limit                       | Values                      | Unit | <b>Test Conditions</b>    |  |

|-------------------------------------------------------------|--------------------|----|-----------------------------|-----------------------------|------|---------------------------|--|

|                                                             |                    |    | min.                        | min. max.                   |      | Remarks                   |  |

| V <sub>DDP</sub> = 3.3V Range                               |                    |    |                             |                             |      |                           |  |

| Output low voltage                                          | V <sub>OL</sub>    | СС | -                           | 1.0                         | V    | I <sub>OL</sub> = 8 mA    |  |

|                                                             |                    |    | _                           | 0.4                         | V    | I <sub>OL</sub> = 2.5 mA  |  |

| Output high voltage                                         | V <sub>OH</sub>    | СС | V <sub>DDP</sub> -<br>1.0   | -                           | V    | I <sub>OH</sub> = -8 mA   |  |

|                                                             |                    |    | V <sub>DDP</sub> - 0.4      | -                           | V    | I <sub>OH</sub> = -2.5 mA |  |

| nput low voltage on<br>port pins<br>all except P0.0 & P0.1) | V <sub>ILP</sub> : | SR | -                           | $0.3 \times V_{\text{DDP}}$ | V    | CMOS Mode                 |  |

| nput low voltage on<br>20.0 & P0.1                          | V <sub>ILP0</sub>  | SR | -0.2                        | $0.3 \times V_{\text{DDP}}$ | V    | CMOS Mode                 |  |

| n <u>put lo</u> w voltage on<br>RESET pin                   | V <sub>ILR</sub>   | SR | _                           | $0.3 \times V_{\text{DDP}}$ | V    | CMOS Mode                 |  |

| nput low voltage on<br>MS pin                               | V <sub>ILT</sub>   | SR | -                           | $0.3 \times V_{\text{DDP}}$ | V    | CMOS Mode                 |  |

| put high voltage on<br>ort pins<br>ill except P0.0 & P0.1)  | V <sub>IHP</sub>   | SR | $0.7 \times V_{\text{DDP}}$ | -                           | V    | CMOS Mode                 |  |

| put high voltage on<br>0.0 & P0.1                           | V <sub>IHP0</sub>  | SR | $0.7 \times V_{\text{DDP}}$ | V <sub>DDP</sub>            | V    | CMOS Mode                 |  |

| put high voltage on<br>ESET pin                             | V <sub>IHR</sub>   | SR | $0.7 \times V_{\text{DDP}}$ | -                           | V    | CMOS Mode                 |  |

| iput high voltage on<br>MS pin                              | V <sub>IHT</sub> : | SR | $0.75 \times V_{ m DDP}$    | -                           | V    | CMOS Mode                 |  |

| iput Hysteresis <sup>1)</sup> on<br>ort pins                | HYS                | СС | $0.03 \times V_{ m DDP}$    | -                           | V    | CMOS Mode                 |  |

| iput Hysteresis <sup>1)</sup> on<br>TAL1                    | HYSX               | CC | $0.07 \times V_{ m DDC}$    | -                           | V    |                           |  |

| nput low voltage at<br>TAL1                                 | V <sub>ILX</sub>   | SR | V <sub>SS</sub> -<br>0.5    | $0.3 \times V_{\text{DDC}}$ | V    |                           |  |

| nput high voltage at<br>(TAL1                               | V <sub>IHX</sub>   | SR | $0.7 \times V_{\text{DDC}}$ | V <sub>DDC</sub><br>+ 0.5   | V    |                           |  |

#### **Electrical Parameters**

#### 4.2.4 Power Supply Current

# Table 37Power Supply Current Parameters (Operating Conditions apply; $V_{\text{DDP}}$ = 5V range )

| Parameter                           | Symbol           | Limit Values       |                    | Unit | Test Condition                         |  |

|-------------------------------------|------------------|--------------------|--------------------|------|----------------------------------------|--|

|                                     |                  | typ. <sup>1)</sup> | max. <sup>2)</sup> |      | Remarks                                |  |

| V <sub>DDP</sub> = 5V Range         |                  |                    |                    |      |                                        |  |

| Active Mode                         | I <sub>DDP</sub> | 22.6               | 24.5               | mA   | 3)                                     |  |

| Idle Mode                           | I <sub>DDP</sub> | 17.2               | 19.7               | mA   | XC866-4FR,<br>XC866-2FR <sup>4)</sup>  |  |

|                                     |                  | 12.5               | 14                 | mA   | XC866-1FR,<br>ROM device <sup>4)</sup> |  |

| Active Mode with slow-down enabled  | I <sub>DDP</sub> | 7.2                | 8.2                | mA   | XC866-4FR,<br>XC866-2FR <sup>5)</sup>  |  |

|                                     |                  | 5.6                | 7.5                | mA   | XC866-1FR,<br>ROM device <sup>5)</sup> |  |

| Idle Mode with slow-down<br>enabled | I <sub>DDP</sub> | 7.1                | 8                  | mA   | XC866-4FR,<br>XC866-2FR <sup>6)</sup>  |  |

|                                     |                  | 5.1                | 7.2                | mA   | XC866-1FR,<br>ROM device <sup>6)</sup> |  |

<sup>1)</sup> The typical  $I_{\text{DDP}}$  values are periodically measured at  $T_{\text{A}}$  = + 25 °C and  $V_{\text{DDP}}$  = 5.0 V.

<sup>2)</sup> The maximum  $I_{\text{DDP}}$  values are measured under worst case conditions ( $T_{\text{A}}$  = + 125 °C and  $V_{\text{DDP}}$  = 5.5 V).

- <sup>3)</sup> I<sub>DDP</sub> (active mode) is measured with: CPU clock and input clock to all peripherals running at 26.7 MHz(set by on-chip oscillator of 10 MHz and NDIV in PLL\_CON to 0010<sub>B</sub>), RESET =  $V_{DDP}$ , no load on ports.

- <sup>4)</sup> I<sub>DDP</sub> (idle mode) is measured with: <u>CPU clock disabled</u>, watchdog timer disabled, input clock to all peripherals enabled and running at 26.7 MHz, <u>RESET</u> = V<sub>DDP</sub>, no load on ports.

- <sup>5)</sup> I<sub>DDP</sub> (active mode with slow-down mode) is measured with: CPU clock and input clock to all peripherals running at 833 KHz by setting CLKREL in CMCON to 0101<sub>B</sub>, RESET = V<sub>DDP</sub>, no load on ports.

- <sup>6)</sup> I<sub>DDP</sub> (idle mode with slow-down mode) is measured with: CPU clock disabled, watchdog timer disabled, input <u>clock to</u> all peripherals enabled and running at 833 KHz by setting CLKREL in CMCON to 0101<sub>B</sub>, <u>RESET</u> = V<sub>DDP</sub>, no load on ports.

#### **Electrical Parameters**

#### 4.3 AC Parameters

## 4.3.1 Testing Waveforms

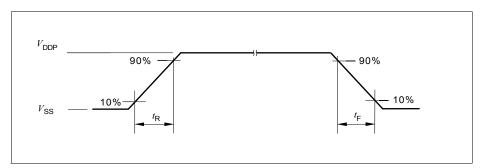

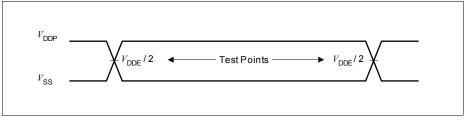

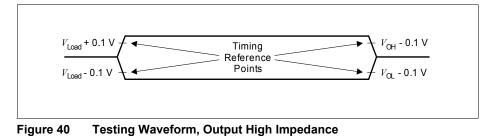

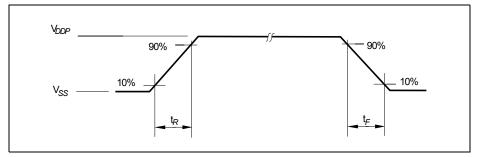

The testing waveforms for rise/fall time, output delay and output high impedance are shown in Figure 38, Figure 39 and Figure 40.

Figure 38 Rise/Fall Time Parameters

Figure 39 Testing Waveform, Output Delay

#### **Electrical Parameters**

# 4.3.2 Output Rise/Fall Times

# Table 41 Output Rise/Fall Times Parameters (Operating Conditions apply)

| Parameter                     | Symbol                          | Limit<br>Values |      | Unit | Test Conditions      |  |

|-------------------------------|---------------------------------|-----------------|------|------|----------------------|--|

|                               |                                 | min.            | max. |      |                      |  |

| V <sub>DDP</sub> = 5V Range   |                                 |                 |      |      |                      |  |

| Rise/fall times 1) 2)         | t <sub>R</sub> , t <sub>F</sub> | -               | 10   | ns   | 20 pF. <sup>3)</sup> |  |

| V <sub>DDP</sub> = 3.3V Range |                                 |                 |      |      |                      |  |

| Rise/fall times 1) 2)         | t <sub>R</sub> , t <sub>F</sub> | -               | 10   | ns   | 20 pF. <sup>4)</sup> |  |

<sup>1)</sup> Rise/Fall time measurements are taken with 10% - 90% of the pad supply.

<sup>2)</sup> Not all parameters are 100% tested, but are verified by design/characterization and test correlation.

<sup>3)</sup> Additional rise/fall time valid for  $C_L = 20pF - 100pF @ 0.125 ns/pF$ .

<sup>4)</sup> Additional rise/fall time valid for  $C_L = 20pF - 100pF @ 0.225 ns/pF$ .

Figure 41 Rise/Fall Times Parameters