Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Discontinued at Digi-Key                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | XC800                                                                        |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 86MHz                                                                        |

| Connectivity               | SSI, UART/USART                                                              |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 19                                                                           |

| Program Memory Size        | 4KB (4K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 768 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                  |

| Data Converters            | A/D 8x10b                                                                    |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 38-TFSOP (0.173", 4.40mm Width)                                              |

| Supplier Device Package    | PG-TSSOP-38                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xc8661fraabkxuma1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Summary of Features**

#### **XC866 Variant Devices**

The XC866 product family features devices with different configurations and program memory sizes, temperature and quality profiles (Automotive or Industrial), offering cost-effective solution for different application requirements.

The configuration of LIN BSL for XC866 devices are summarized in Table 1.

| Table 1 | Device Configuration for LIN BSL |

|---------|----------------------------------|

|---------|----------------------------------|

| Device Name | LIN BSL Support |

|-------------|-----------------|

| XC866       | No              |

| XC866L      | Yes             |

The list of XC866 devices and their differences are summarized in Table 2.

| Device<br>Type      | Device Name        | Power<br>Supply<br>(V) | P-Flash<br>Size<br>(Kbytes) | D-Flash<br>Size<br>(Kbytes) | ROM<br>Size<br>(Kbytes) | Quality<br>Profile <sup>1)</sup> |

|---------------------|--------------------|------------------------|-----------------------------|-----------------------------|-------------------------|----------------------------------|

| Flash <sup>2)</sup> | SAK-XC866*-4FRA    | 5.0                    | 12                          | 4                           | _                       | Automotive                       |

|                     | SAK-XC866*-4FRI    | 5.0                    | 12                          | 4                           | -                       | Industrial                       |

|                     | SAK-XC866*-2FRA    | 5.0                    | 4                           | 4                           | -                       | Automotive                       |

|                     | SAK-XC866*-2FRI    | 5.0                    | 4                           | 4                           | -                       | Industrial                       |

|                     | SAK-XC866*-1FRA    | 5.0                    | _                           | 4                           | -                       | Automotive                       |

|                     | SAK-XC866*-1FRI    | 5.0                    | -                           | 4                           | _                       | Industrial                       |

|                     | SAF-XC866*-4FRA    | 5.0                    | 12                          | 4                           | -                       | Automotive                       |

|                     | SAF-XC866*-4FRI    | 5.0                    | 12                          | 4                           | -                       | Industrial                       |

|                     | SAF-XC866*-2FRA    | 5.0                    | 4                           | 4                           | _                       | Automotive                       |

|                     | SAF-XC866*-2FRI    | 5.0                    | 4                           | 4                           | -                       | Industrial                       |

|                     | SAF-XC866*-1FRA    | 5.0                    | _                           | 4                           | -                       | Automotive                       |

|                     | SAF-XC866*-1FRI    | 5.0                    | _                           | 4                           | -                       | Industrial                       |

|                     | SAK-XC866*-4FRA 3V | 3.3                    | 12                          | 4                           | -                       | Automotive                       |

|                     | SAK-XC866*-4FRI 3V | 3.3                    | 12                          | 4                           | -                       | Industrial                       |

|                     | SAK-XC866*-2FRA 3V | 3.3                    | 4                           | 4                           | _                       | Automotive                       |

|                     | SAK-XC866*-2FRI 3V | 3.3                    | 4                           | 4                           | -                       | Industrial                       |

|                     | SAK-XC866*-1FRA 3V | 3.3                    | -                           | 4                           | _                       | Automotive                       |

#### Table 2 Device Summary

# XC866

#### **General Device Information**

| Symbol            | Pin<br>Number | Туре | Reset<br>State | Function                                                              |

|-------------------|---------------|------|----------------|-----------------------------------------------------------------------|

| V <sub>DDP</sub>  | 18            | -    | -              | I/O Port Supply (3.3 V/5.0 V)<br>Also used by EVR and analog modules. |

| V <sub>SSP</sub>  | 19            | -    | -              | I/O Port Ground                                                       |

| V <sub>DDC</sub>  | 8             | -    | -              | Core Supply Monitor (2.5 V)                                           |

| V <sub>ssc</sub>  | 7             | -    | -              | Core Supply Ground                                                    |

| V <sub>AREF</sub> | 25            | -    | -              | ADC Reference Voltage                                                 |

| V <sub>AGND</sub> | 24            | _    | -              | ADC Reference Ground                                                  |

| XTAL1             | 6             | I    | Hi-Z           | External Oscillator Input<br>(NC if not needed)                       |

| XTAL2             | 5             | 0    | Hi-Z           | External Oscillator Output<br>(NC if not needed)                      |

| TMS               | 11            | I    | PD             | Test Mode Select                                                      |

| RESET             | 38            | I    | PU             | Reset Input                                                           |

| MBC <sup>1)</sup> | 1             | I    | PU             | Monitor & BootStrap Loader Control                                    |

## Table 3 Pin Definitions and Functions (cont'd)

<sup>1)</sup> An external pull-up device in the range of 4.7 k $\Omega$  to 100 k $\Omega$  is required to enter user mode. Alternatively MBC can be tied to high if alternate functions (for debugging) of the pin are not utilized.

## Table 13 CCU6 Register Overview (cont'd)

| Addr            | Register Name                                                             | Bit       | 7         | 6            | 5            | 4          | 3            | 2          | 1            | 0          |

|-----------------|---------------------------------------------------------------------------|-----------|-----------|--------------|--------------|------------|--------------|------------|--------------|------------|

| FF <sub>H</sub> | CCU6_TRPCTRH Reset: 00 <sub>H</sub>                                       | Bit Field |           | TRPEN        |              |            | TR           | PEN        |              |            |

|                 | Trap Control Register High                                                |           | N         | 13           |              |            |              |            |              |            |

|                 |                                                                           | Туре      | rw        | rw           |              |            | r            | w          |              |            |

| RMAP =          | 0, Page 3                                                                 |           |           |              |              |            |              |            |              |            |

| 9A <sub>H</sub> | CCU6_MCMOUTL Reset: 00 <sub>H</sub><br>Multi-Channel Mode Output Register | Bit Field | 0         | R            | MCMP         |            |              |            |              |            |

|                 | Low                                                                       | Туре      | r         | rh           |              |            | r            | h          |              |            |

| 9B <sub>H</sub> | CCU6_MCMOUTH Reset: 00 <sub>H</sub><br>Multi-Channel Mode Output Register | Bit Field | (         | )            | CURH         |            |              |            | EXPH         |            |

|                 | High                                                                      | Туре      | 1         | r            |              | rh         |              |            | rh           |            |

| 9C <sub>H</sub> | CCU6_ISL Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Status       | Bit Field | T12PM     | T12OM        | ICC62F       | R          | ICC61F       | R          | ICC60F       | ICC60<br>R |

|                 | Register Low                                                              | Туре      | rh        | rh           | rh           | rh         | rh           | rh         | rh           | rh         |

| 9D <sub>H</sub> | CCU6_ISH Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Status       | Bit Field | STR       | IDLE         | WHE          | CHE        | TRPS         | TRPF       | T13PM        | T13CM      |

|                 | Register High                                                             | Туре      | rh        | rh           | rh           | rh         | rh           | rh         | rh           | rh         |

| 9E <sub>H</sub> | CCU6_PISEL0L Reset: 00 <sub>H</sub>                                       | Bit Field | ISTRP     |              | ISCC62 ISC   |            | C61 ISCC60   |            | C60          |            |

|                 | Port Input Select Register 0 Low                                          | Туре      | rw rw r   |              |              | w rw       |              |            |              |            |

| 9F <sub>H</sub> | CCU6_PISEL0H Reset: 00 <sub>H</sub><br>Port Input Select Register 0 High  | Bit Field | IST12HR   |              | ISPOS2 ISP   |            | OS1 ISPOS0   |            | OS0          |            |

|                 |                                                                           | Туре      | rw rw rw  |              |              |            | w rw         |            |              |            |

| A4 <sub>H</sub> | CCU6_PISEL2 Reset: 00 <sub>H</sub>                                        | Bit Field | 0 IST13HR |              |              |            |              |            | 3HR          |            |

|                 | Port Input Select Register 2                                              | Туре      | r rw      |              |              |            |              |            | w            |            |

| FA <sub>H</sub> | CCU6_T12L Reset: 00 <sub>H</sub>                                          | Bit Field | T12CVL    |              |              |            |              |            |              |            |

|                 | Timer T12 Counter Register Low                                            | Туре      | rwh       |              |              |            |              |            |              |            |

| FB <sub>H</sub> | CCU6_T12H Reset: 00 <sub>H</sub>                                          | Bit Field | T12CVH    |              |              |            |              |            |              |            |

|                 | Timer T12 Counter Register High                                           | Туре      | rwh       |              |              |            |              |            |              |            |

| FC <sub>H</sub> | CCU6_T13L Reset: 00 <sub>H</sub>                                          | Bit Field | T13CVL    |              |              |            |              |            |              |            |

|                 | Timer T13 Counter Register Low                                            | Туре      | rwh       |              |              |            |              |            |              |            |

| FD <sub>H</sub> | CCU6_T13H Reset: 00 <sub>H</sub>                                          | Bit Field |           |              |              | T13        | CVH          |            |              |            |

|                 | Timer T13 Counter Register High                                           | Туре      |           |              |              | n          | vh           |            |              |            |

| FE <sub>H</sub> | CCU6_CMPSTATL Reset: 00 <sub>H</sub><br>Compare State Register Low        | Bit Field | 0         | CC63<br>ST   | CCPO<br>S2   | CCPO<br>S1 | CCPO<br>S0   | CC62<br>ST | CC61<br>ST   | CC60<br>ST |

|                 |                                                                           | Туре      | r         | rh           | rh           | rh         | rh           | rh         | rh           | rh         |

| FF <sub>H</sub> | CCU6_CMPSTATH Reset: 00 <sub>H</sub><br>Compare State Register High       | Bit Field | T13IM     | COUT<br>63PS | COUT<br>62PS | CC62<br>PS | COUT<br>61PS | CC61<br>PS | COUT<br>60PS | CC60<br>PS |

|                 |                                                                           | Туре      | rwh       | rwh          | rwh          | rwh        | rwh          | rwh        | rwh          | rwh        |

The SSC SFRs can be accessed in the standard memory area (RMAP = 0).

# Table 14SSC Register Overview

| Addr            | Register Name                            |                        | Bit       | 7  | 6  | 5  | 4  | 3 | 2   | 1   | 0   |

|-----------------|------------------------------------------|------------------------|-----------|----|----|----|----|---|-----|-----|-----|

| RMAP =          | 0                                        |                        | •         |    |    |    |    |   |     |     |     |

| A9 <sub>H</sub> | SSC_PISEL                                | Reset: 00 <sub>H</sub> | Bit Field |    |    | 0  |    |   | CIS | SIS | MIS |

|                 | Port Input Select Registe                | er                     | Туре      |    |    | r  |    |   | rw  | rw  | rw  |

| AA <sub>H</sub> | SSC_CONL                                 | Reset: 00 <sub>H</sub> | Bit Field | LB | PO | PH | HB |   | В   | М   |     |

|                 | Control Register Low<br>Programming Mode |                        | Туре      | rw | rw | rw | rw |   | r   | w   |     |

|                 | Operating Mode                           |                        | Bit Field | 0  |    |    | BC |   |     |     |     |

|                 |                                          |                        | Туре      |    |    | r  |    |   | r   | h   |     |

| P-Flash              | D-Flash            |

|----------------------|--------------------|

|                      | Sector 0: 1-Kbyte  |

|                      | Sector 1: 1-Kbyte  |

| Sector 0: 3.75-Kbyte | Sector 2: 512-byte |

|                      | Sector 3: 512-byte |

|                      | Sector 4: 256-byte |

|                      | Sector 5: 256-byte |

|                      | Sector 6: 128-byte |

|                      | Sector 7: 128-byte |

| Sector 1: 128-byte   | Sector 8: 128-byte |

| Sector 2: 128-byte   | Sector 9: 128-byte |

#### Figure 11 Flash Bank Sectorization

İnfineon

The internal structure of each Flash bank represents a sector architecture for flexible erase capability. The minimum erase width is always a complete sector, and sectors can be erased separately or in parallel. Contrary to standard EPROMs, erased Flash memory cells contain 0s.

The D-Flash bank is divided into more physical sectors for extended erasing and reprogramming capability; even numbers for each sector size are provided to allow greater flexibility and the ability to adapt to a wide range of application requirements.

# 3.3.2 Flash Programming Width

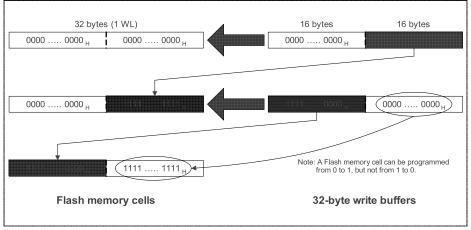

For the P-Flash banks, a programmed wordline (WL) must be erased before it can be reprogrammed as the Flash cells can only withstand one gate disturb. This means that the entire sector containing the WL must be erased since it is impossible to erase a single WL.

For the D-Flash bank, the same WL can be programmed twice before erasing is required as the Flash cells are able to withstand two gate disturbs. Hence, it is possible to program the same WL, for example, with 16 bytes of data in two times (see **Figure 12**).

## Figure 12 D-Flash Programming

Note: When programming a D-Flash WL the second time, the previously programmed Flash memory cells (whether 0s or 1s) should be reprogrammed with 0s to retain its original contents and to prevent "over-programming".

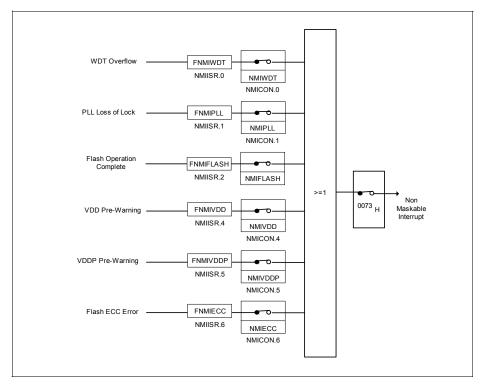

# 3.4 Interrupt System

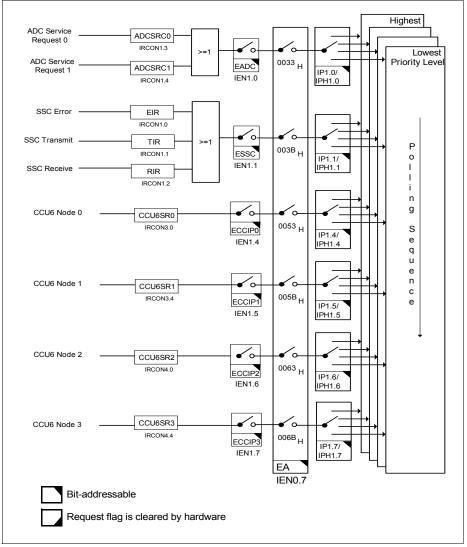

The XC800 Core supports one non-maskable interrupt (NMI) and 14 maskable interrupt requests. In addition to the standard interrupt functions supported by the core, e.g., configurable interrupt priority and interrupt masking, the XC866 interrupt system provides extended interrupt support capabilities such as the mapping of each interrupt vector to several interrupt sources to increase the number of interrupt sources supported, and additional status registers for detecting and determining the interrupt source.

# 3.4.1 Interrupt Source

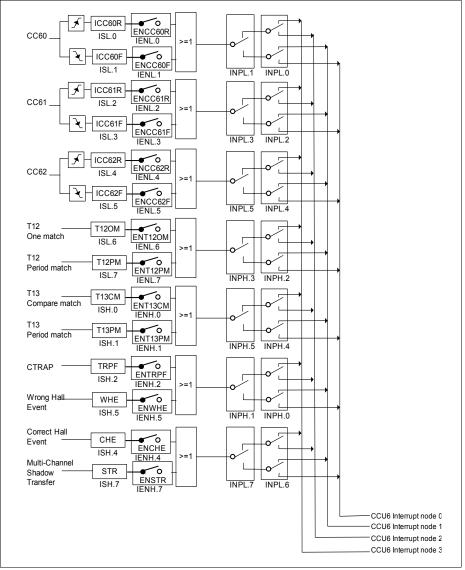

Figure 13 to Figure 17 give a general overview of the interrupt sources and illustrates the request and control flags.

# Figure 13 Non-Maskable Interrupt Request Sources

Figure 16 Interrupt Request Sources (Part 3)

# XC866

# **Functional Description**

## Figure 17 Interrupt Request Sources (Part 4)

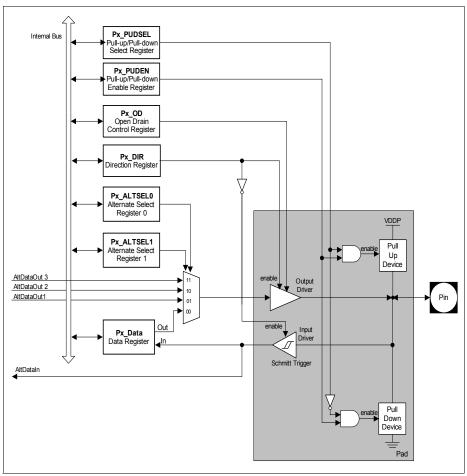

Figure 18 General Structure of Bidirectional Port

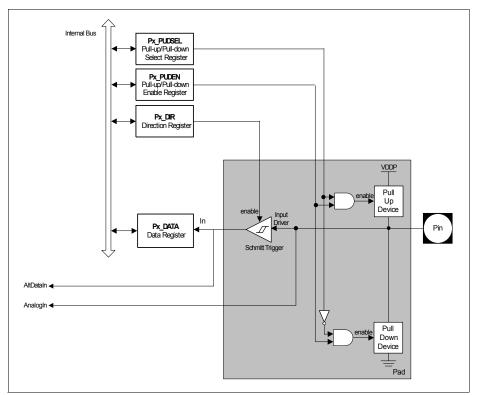

Figure 19 General Structure of Input Port

# 3.7.1 Module Reset Behavior

**Table 19** shows how the functions of the XC866 are affected by the various reset types. A "∎" means that this function is reset to its default state.

| Module/<br>Function   | Wake-Up<br>Reset                     | Watchdog<br>Reset      | Hardware<br>Reset      | Power-On<br>Reset         | Brownout<br>Reset         |

|-----------------------|--------------------------------------|------------------------|------------------------|---------------------------|---------------------------|

| CPU Core              |                                      |                        |                        |                           |                           |

| Peripherals           |                                      |                        |                        |                           |                           |

| On-Chip<br>Static RAM | Not affected, reliable               | Not affected, reliable | Not affected, reliable | Affected, un-<br>reliable | Affected, un-<br>reliable |

| Oscillator,<br>PLL    |                                      | Not affected           |                        |                           |                           |

| Port Pins             |                                      |                        |                        |                           |                           |

| EVR                   | The voltage regulator is switched on | Not affected           |                        |                           |                           |

| FLASH                 |                                      |                        |                        |                           |                           |

| NMI                   | Disabled                             | Disabled               |                        |                           |                           |

Table 19 Effect of Reset on Device Functions

# 3.7.2 Booting Scheme

When the XC866 is reset, it must identify the type of configuration with which to start the different modes once the reset sequence is complete. Thus, boot configuration information that is required for activation of special modes and conditions needs to be applied by the external world through input pins. After power-on reset or hardware reset, the pins MBC, TMS and P0.0 collectively select the different boot options. **Table 20** shows the available boot options in the XC866.

| MBC | TMS | P0.0 | Type of Mode                                                                      | PC Start Value    |

|-----|-----|------|-----------------------------------------------------------------------------------|-------------------|

| 1   | 0   | х    | User Mode; on-chip OSC/PLL non-bypassed                                           | 0000 <sub>H</sub> |

| 0   | 0   | х    | BSL Mode; on-chip OSC/PLL non-bypassed                                            | 0000 <sub>H</sub> |

| 0   | 1   | 0    | OCDS Mode <sup>1)</sup> ; on-chip OSC/PLL non-<br>bypassed                        | 0000 <sub>H</sub> |

| 1   | 1   | 0    | Standalone User (JTAG) Mode <sup>2)</sup> ; on-chip OSC/PLL non-bypassed (normal) | 0000 <sub>H</sub> |

Table 20 XC866 Boot Selection

<sup>1)</sup> The OCDS mode is not accessible if Flash is protected.

<sup>2)</sup> Normal user mode with standard JTAG (TCK,TDI,TDO) pins for hot-attach purpose.

| ······································ |                                                        |                                                                                                      |                                                                                                                                           |                                                                                                                                                                                   |                                                                                                                                                                                                                                             |  |  |  |

|----------------------------------------|--------------------------------------------------------|------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| fosc                                   | Ν                                                      | Ρ                                                                                                    | κ                                                                                                                                         | fsys                                                                                                                                                                              |                                                                                                                                                                                                                                             |  |  |  |

| 10 MHz                                 | 16                                                     | 1                                                                                                    | 2                                                                                                                                         | 80 MHz                                                                                                                                                                            |                                                                                                                                                                                                                                             |  |  |  |

| 10 MHz                                 | 16                                                     | 1                                                                                                    | 2                                                                                                                                         | 80 MHz                                                                                                                                                                            |                                                                                                                                                                                                                                             |  |  |  |

| 8 MHz                                  | 20                                                     | 1                                                                                                    | 2                                                                                                                                         | 80 MHz                                                                                                                                                                            |                                                                                                                                                                                                                                             |  |  |  |

| 5 MHz                                  | 32                                                     | 1                                                                                                    | 2                                                                                                                                         | 80 MHz                                                                                                                                                                            |                                                                                                                                                                                                                                             |  |  |  |

|                                        | fosc           10 MHz           10 MHz           8 MHz | 10 MHz         16           10 MHz         16           10 MHz         16           8 MHz         20 | fosc         N         P           10 MHz         16         1           10 MHz         16         1           8 MHz         20         1 | fosc         N         P         K           10 MHz         16         1         2           10 MHz         16         1         2           8 MHz         20         1         2 | fosc         N         P         K         fsys           10 MHz         16         1         2         80 MHz           10 MHz         16         1         2         80 MHz           8 MHz         20         1         2         80 MHz |  |  |  |

# Table 21 System frequency (f<sub>svs</sub> = 80 MHz)

Table 22 shows the VCO range for the XC866.

| Table 22 VCO Range | VCO Range |

|--------------------|-----------|

|--------------------|-----------|

| f <sub>VCOmin</sub> | f <sub>VCOmax</sub> | f <sub>VCOFREEmin</sub> | f <sub>VCOFREEmax</sub> | Unit |

|---------------------|---------------------|-------------------------|-------------------------|------|

| 150                 | 200                 | 20                      | 80                      | MHz  |

| 100                 | 150                 | 10                      | 80                      | MHz  |

# 3.8.1 Recommended External Oscillator Circuits

The oscillator circuit, a Pierce oscillator, is designed to work with both, an external crystal oscillator or an external stable clock source. It basically consists of an inverting amplifier and a feedback element with XTAL1 as input, and XTAL2 as output.

When using a crystal, a proper external oscillator circuitry must be connected to both pins, XTAL1 and XTAL2. The crystal frequency can be within the range of 4 MHz to 12 MHz. Additionally, it is necessary to have two load capacitances  $C_{X1}$  and  $C_{X2}$ , and depending on the crystal type, a series resistor  $R_{X2}$ , to limit the current. A test resistor  $R_Q$  may be temporarily inserted to measure the oscillation allowance (negative resistance) of the oscillator circuitry.  $R_Q$  values are typically specified by the crystal vendor. The  $C_{X1}$  and  $C_{X2}$  values shown in **Figure 24** can be used as starting points for the negative resistance evaluation and for non-productive systems. The exact values and related operating range are dependent on the crystal frequency and have to be determined and optimized together with the final target system is strongly recommended to verify the input amplitude at XTAL1 and to determine the actual oscillation allowance (margin negative resistance) for the oscillator-crystal system.

When using an external clock signal, the signal must be connected to XTAL1. XTAL2 is left open (unconnected).

The oscillator can also be used in combination with a ceramic resonator. The final circuitry must also be verified by the resonator vendor.

Figure 24 shows the recommended external oscillator circuitries for both operating modes, external crystal mode and external input clock mode.

# 3.9 Power Saving Modes

The power saving modes of the XC866 provide flexible power consumption through a combination of techniques, including:

- Stopping the CPU clock

- · Stopping the clocks of individual system components

- Reducing clock speed of some peripheral components

- · Power-down of the entire system with fast restart capability

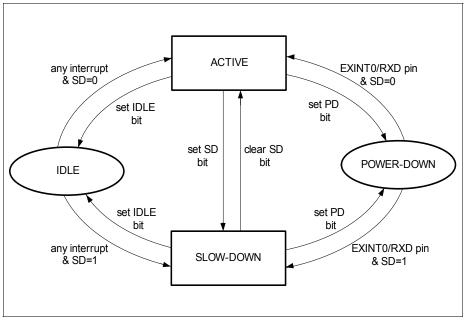

After a reset, the active mode (normal operating mode) is selected by default (see **Figure 26**) and the system runs in the main system clock frequency. From active mode, different power saving modes can be selected by software. They are:

- · Idle mode

- Slow-down mode

- Power-down mode

Figure 26 Transition between Power Saving Modes

If the WDT is not serviced before the timer overflow, a system malfunction is assumed. As a result, the WDT NMI is triggered (assert WDTTO) and the reset prewarning is entered. The prewarning period lasts for  $30_{\rm H}$  count, after which the system is reset (assert WDTRST).

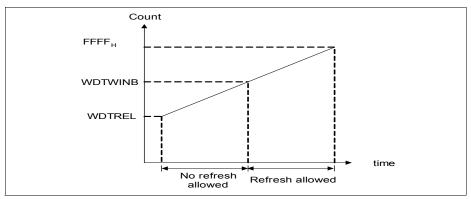

The WDT has a "programmable window boundary" which disallows any refresh during the WDT's count-up. A refresh during this window boundary constitutes an invalid access to the WDT, causing the reset prewarning to be entered but without triggering the WDT NMI. The system will still be reset after the prewarning period is over. The window boundary is from  $0000_{\rm H}$  to the value obtained from the concatenation of WDTWINB and  $00_{\rm H}$ .

After being serviced, the WDT continues counting up from the value (<WDTREL>  $* 2^8$ ). The time period for an overflow of the WDT is programmable in two ways:

- the input frequency to the WDT can be selected to be either f<sub>PCLK</sub>/2 or f<sub>PCLK</sub>/128

- the reload value WDTREL for the high byte of WDT can be programmed in register WDTREL

The period,  $P_{WDT}$ , between servicing the WDT and the next overflow can be determined by the following formula:

$$P_{WDT} = \frac{2^{(1+WDTIN \times 6)} \times (2^{16} - WDTREL \times 2^8)}{f_{PCLK}}$$

If the Window-Boundary Refresh feature of the WDT is enabled, the period  $P_{WDT}$  between servicing the WDT and the next overflow is shortened if WDTWINB is greater than WDTREL, see **Figure 28**. This period can be calculated using the same formula by replacing WDTREL with WDTWINB. For this feature to be useful, WDTWINB should not be smaller than WDTREL.

Figure 28 WDT Timing Diagram

# 3.17 Capture/Compare Unit 6

The Capture/Compare Unit 6 (CCU6) provides two independent timers (T12, T13), which can be used for Pulse Width Modulation (PWM) generation, especially for AC-motor control. The CCU6 also supports special control modes for block commutation and multi-phase machines.

The timer T12 can function in capture and/or compare mode for its three channels. The timer T13 can work in compare mode only.

The multi-channel control unit generates output patterns, which can be modulated by T12 and/or T13. The modulation sources can be selected and combined for the signal modulation.

## Timer T12 Features:

- Three capture/compare channels, each channel can be used either as a capture or as a compare channel

- Supports generation of a three-phase PWM (six outputs, individual signals for highside and lowside switches)

- 16-bit resolution, maximum count frequency = peripheral clock frequency

- · Dead-time control for each channel to avoid short-circuits in the power stage

- Concurrent update of the required T12/13 registers

- · Generation of center-aligned and edge-aligned PWM

- · Supports single-shot mode

- · Supports many interrupt request sources

- · Hysteresis-like control mode

## Timer T13 Features:

- · One independent compare channel with one output

- 16-bit resolution, maximum count frequency = peripheral clock frequency

- Can be synchronized to T12

- · Interrupt generation at period-match and compare-match

- Supports single-shot mode

## Additional Features:

- · Implements block commutation for Brushless DC-drives

- Position detection via Hall-sensor pattern

- · Automatic rotational speed measurement for block commutation

- Integrated error handling

- Fast emergency stop without CPU load via external signal (CTRAP)

- · Control modes for multi-channel AC-drives

- · Output levels can be selected and adapted to the power stage

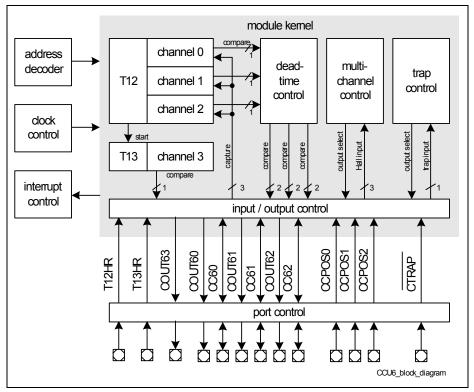

The block diagram of the CCU6 module is shown in Figure 32.

Figure 32 CCU6 Block Diagram

# XC866

#### **Functional Description**

# 3.18 Analog-to-Digital Converter

The XC866 includes a high-performance 10-bit Analog-to-Digital Converter (ADC) with eight multiplexed analog input channels. The ADC uses a successive approximation technique to convert the analog voltage levels from up to eight different sources. The analog input channels of the ADC are available at Port 2.

## Features:

- Successive approximation

- 8-bit or 10-bit resolution (TUE of ± 1 LSB and ± 2 LSB, respectively)

- Eight analog channels

- · Four independent result registers

- Result data protection for slow CPU access (wait-for-read mode)

- · Single conversion mode

- Autoscan functionality

- · Limit checking for conversion results

- Data reduction filter (accumulation of up to 2 conversion results)

- · Two independent conversion request sources with programmable priority

- Selectable conversion request trigger

- · Flexible interrupt generation with configurable service nodes

- · Programmable sample time

- · Programmable clock divider

- · Cancel/restart feature for running conversions

- · Integrated sample and hold circuitry

- · Compensation of offset errors

- · Low power modes

#### **Electrical Parameters**

## 4.1.2 Absolute Maximum Rating

Maximum ratings are the extreme limits to which the XC866 can be subjected to without permanent damage.

| Table 32 | Absolute Maximum Rating Parameters |

|----------|------------------------------------|

|----------|------------------------------------|

| Parameter                                                    | Symbol                | Symbol Limit Va |                                        | Unit | Notes                |  |

|--------------------------------------------------------------|-----------------------|-----------------|----------------------------------------|------|----------------------|--|

|                                                              |                       | min.            | max.                                   |      |                      |  |

| Ambient temperature                                          | T <sub>A</sub>        | -40             | 125                                    | °C   | under bias           |  |

| Storage temperature                                          | T <sub>ST</sub>       | -65             | 150                                    | °C   |                      |  |

| Junction temperature                                         | TJ                    | -40             | 150                                    | °C   | under bias           |  |

| Voltage on power supply pin with respect to $V_{\rm SS}$     | V <sub>DDP</sub>      | -0.5            | 6                                      | V    |                      |  |

| Voltage on core supply pin with respect to $V_{\rm SS}$      | V <sub>DDC</sub>      | -0.5            | 3.25                                   | V    |                      |  |

| Voltage on any pin with respect to $V_{\rm SS}$              | V <sub>IN</sub>       | -0.5            | V <sub>DDP</sub> +<br>0.5 or<br>max. 6 | V    | Whatever is<br>lower |  |

| Input current on any pin during overload condition           | I <sub>IN</sub>       | -10             | 10                                     | mA   |                      |  |

| Absolute sum of all input currents during overload condition | $\Sigma  I_{\sf IN} $ | -               | 50                                     | mA   |                      |  |

Note: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. During absolute maximum rating overload conditions ( $V_{IN} > V_{DDP}$  or  $V_{IN} < V_{SS}$ ) the voltage on  $V_{DDP}$  pin with respect to ground ( $V_{SS}$ ) must not exceed the values defined by the absolute maximum ratings.

#### **Electrical Parameters**

# Table 39Power Supply Current Parameters (Operating Conditions apply;<br/> $V_{\text{DDP}}$ = 3.3V range)

| Parameter                          | Symbol             | Limit Values       |                    | Unit | <b>Test Condition</b>                  |  |

|------------------------------------|--------------------|--------------------|--------------------|------|----------------------------------------|--|

|                                    |                    | typ. <sup>1)</sup> | max. <sup>2)</sup> | 1    | Remarks                                |  |

| V <sub>DDP</sub> = 3.3V Range      |                    | -                  |                    | 4    |                                        |  |

| Active Mode                        | I <sub>DDP</sub>   | 21.5               | 23.3               | mA   | 3)                                     |  |

| Idle Mode                          | I <sub>DDP</sub>   | 16.4               | 18.9               | mA   | XC866-4FR,<br>XC866-2FR <sup>4)</sup>  |  |

|                                    |                    | 11.2               | 13.5               | mA   | XC866-1FR,<br>ROM device <sup>4)</sup> |  |

| Active Mode with slow-down enabled | n I <sub>DDP</sub> | 6.8                | 8                  | mA   | XC866-4FR,<br>XC866-2FR <sup>5)</sup>  |  |

|                                    |                    | 5.4                | 7.3                | mA   | XC866-1FR,<br>ROM device <sup>5)</sup> |  |

| Idle Mode with slow-down enabled   | I <sub>DDP</sub>   | 6.8                | 7.8                | mA   | XC866-4FR,<br>XC866-2FR <sup>6)</sup>  |  |

|                                    |                    | 4.9                | 6.9                | mA   | XC866-1FR,<br>ROM device <sup>6)</sup> |  |

<sup>1)</sup> The typical  $I_{\text{DDP}}$  values are periodically measured at  $T_{\text{A}}$  = + 25 °C and  $V_{\text{DDP}}$  = 3.3 V.

<sup>2)</sup> The maximum  $I_{\text{DDP}}$  values are measured under worst case conditions ( $T_{\text{A}}$  = + 125 °C and  $V_{\text{DDP}}$  = 3.6 V).

<sup>3)</sup> I<sub>DDP</sub> (active mode) is measured with: CPU clock and input clock to all peripherals running at 26.7 MHz(set by on-chip oscillator of 10 MHz and NDIV in PLL\_CON to 0010<sub>B</sub>), RESET =  $V_{DDP}$ , no load on ports.

<sup>4)</sup> I<sub>DDP</sub> (idle mode) is measured with: <u>CPU clock</u> disabled, watchdog timer disabled, input clock to all peripherals enabled and running at 26.7 MHz, <u>RESET</u> = V<sub>DDP</sub>, no load on ports.

<sup>5)</sup> I<sub>DDP</sub> (active mode with slow-down mode) is measured with: <u>CPU</u> clock and input clock to all peripherals running at 833 KHz by setting CLKREL in CMCON to 0101<sub>B</sub>, <u>RESET</u> = V<sub>DDP</sub>, no load on ports.

<sup>6)</sup> I<sub>DDP</sub> (idle mode with slow-down mode) is measured with: CPU clock disabled, watchdog timer disabled, input <u>clock to all peripherals enable and running at 833 KHz by setting CLKREL in CMCON to 0101<sub>B</sub>,, <u>RESET = V<sub>DDP</sub>, no load on ports.</u></u>

## **Electrical Parameters**

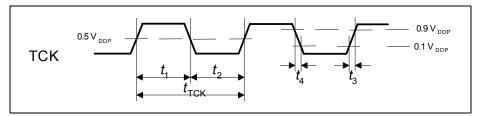

# 4.3.5 JTAG Timing

# Table 44TCK Clock Timing (Operating Conditions apply; $C_L = 50 \text{ pF}$ )

| Parameter           | Symbol              | Lir | Limits |    |

|---------------------|---------------------|-----|--------|----|

|                     |                     | min | max    |    |

| TCK clock period    | t <sub>TCK</sub> SR | 50  | -      | ns |

| TCK high time       | t <sub>1</sub> SR   | 20  | -      | ns |

| TCK low time        | t <sub>2</sub> SR   | 20  | -      | ns |

| TCK clock rise time | t <sub>3</sub> SR   | -   | 4      | ns |

| TCK clock fall time | t <sub>4</sub> SR   | -   | 4      | ns |

Figure 43 TCK Clock Timing