Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                     |

| Core Processor             | XC800                                                                        |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 86MHz                                                                        |

| Connectivity               | SSI, UART/USART                                                              |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 19                                                                           |

| Program Memory Size        | 4KB (4K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 768 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                  |

| Data Converters            | A/D 8x10b                                                                    |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 38-TFSOP (0.173", 4.40mm Width)                                              |

| Supplier Device Package    | PG-TSSOP-38                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xc8661friabfxuma1 |

Edition 2007-10

Published by Infineon Technologies AG, 81726 München, Germany

© Infineon Technologies AG 2007.

All Rights Reserved.

#### Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie"). With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

# XC866

8-Bit Single-Chip Microcontroller

## Microcontrollers

## **General Device Information**

## 2.4 Pin Definitions and Functions

Table 3 Pin Definitions and Functions

| Symbol | Pin<br>Number | Туре | Reset<br>State | Function                                                                                                                                      |                                                                                                              |  |  |  |  |

|--------|---------------|------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--|--|--|--|

| P0     |               | I/O  |                | Port 0 Port 0 is a 6-bit bidirectional general purpose I/O port. It can be used as alternate functions for the JTAG, CCU6, UART, and the SSC. |                                                                                                              |  |  |  |  |

| P0.0   | 12            |      | Hi-Z           | TCK_0<br>T12HR_1                                                                                                                              | JTAG Clock Input<br>CCU6 Timer 12 Hardware Run<br>Input                                                      |  |  |  |  |

|        |               |      |                | CC61_1<br>CLKOUT<br>RXDO_1                                                                                                                    | Input/Output of Capture/Compare<br>channel 1<br>Clock Output<br>UART Transmit Data Output                    |  |  |  |  |

| P0.1   | 14            |      | Hi-Z           | TDI_0<br>T13HR_1                                                                                                                              | JTAG Serial Data Input<br>CCU6 Timer 13 Hardware Run<br>Input                                                |  |  |  |  |

|        |               |      |                | RXD_1<br>COUT61_1                                                                                                                             | UART Receive Data Input Output of Capture/Compare channel 1                                                  |  |  |  |  |

| P0.2   | 13            |      | PU             | EXF2_1<br>CTRAP_2<br>TDO_0<br>TXD_1                                                                                                           | Timer 2 External Flag Output CCU6 Trap Input JTAG Serial Data Output UART Transmit Data Output/ Clock Output |  |  |  |  |

| P0.3   | 2             |      | Hi-Z           | SCK_1<br>COUT63_1                                                                                                                             | SSC Clock Input/Output<br>Output of Capture/Compare<br>channel 3                                             |  |  |  |  |

| P0.4   | 3             |      | Hi-Z           | MTSR_1<br>CC62_1                                                                                                                              | SSC Master Transmit Output/<br>Slave Receive Input<br>Input/Output of Capture/Compare<br>channel 2           |  |  |  |  |

| P0.5   | 4             |      | Hi-Z           | MRST_1 EXINT0 0                                                                                                                               | SSC Master Receive Input/ Slave Transmit Output External Interrupt Input 0                                   |  |  |  |  |

|        |               |      |                | COUT62_1                                                                                                                                      | Output of Capture/Compare channel 2                                                                          |  |  |  |  |

The Port SFRs can be accessed in the standard memory area (RMAP = 0).

Table 10 Port Register Overview

| Addr             | Register Name                                                                             | Register Name          |                   | 7        | 6        | 5        | 4    | 3       | 2    | 1        | 0        |

|------------------|-------------------------------------------------------------------------------------------|------------------------|-------------------|----------|----------|----------|------|---------|------|----------|----------|

| RMAP =           | •                                                                                         |                        |                   |          |          |          |      |         |      |          |          |

| B2 <sub>H</sub>  | PORT PAGE                                                                                 | Reset: 00 <sub>H</sub> | Bit Field         | C        | )P       | STNR 0   |      | 0       | PAGE |          |          |

| "                | Page Register for PORT                                                                    |                        | Type w            |          |          | w r      |      | rwh     |      |          |          |

| RMAP =           | 0, Page 0                                                                                 |                        | . )   -           |          |          |          |      | -       |      |          |          |

| 80 <sub>H</sub>  | PO DATA                                                                                   | Reset: 00 <sub>H</sub> | Bit Field         |          | 0        | P5       | P4   | P3      | P2   | P1       | P0       |

| п                | P0 Data Register                                                                          |                        | Туре              |          | r        | rwh      | rwh  | rwh     | rwh  | rwh      | rwh      |

| 86 <sub>H</sub>  | P0 DIR                                                                                    | Reset: 00 <sub>H</sub> | Bit Field         |          | 0        | P5       | P4   | P3      | P2   | P1       | P0       |

| п                | P0 Direction Register                                                                     |                        | Туре              |          | r        | rw       | rw   | rw      | rw   | rw       | rw       |

| 90 <sub>H</sub>  | P1 DATA                                                                                   | Reset: 00 <sub>H</sub> | Bit Field         | P7       | P6       | P5       |      | 0       |      | P1       | P0       |

|                  | P1 Data Register                                                                          |                        | Туре              | rwh      | rwh      | rwh      |      | r       |      | rwh      | rwh      |

| 91 <sub>H</sub>  | P1 DIR                                                                                    | Reset: 00 <sub>H</sub> | Bit Field         | P7       | P6       | P5       |      | 0       |      | P1       | P0       |

| - П              | P1 Direction Register                                                                     |                        | Туре              | rw       | rw       | rw       |      | r       |      | rw       | rw       |

| A0 <sub>H</sub>  | P2 DATA                                                                                   | Reset: 00 <sub>H</sub> | Bit Field         | P7       | P6       | P5       | P4   | P3      | P2   | P1       | P0       |

|                  | P2 Data Register                                                                          |                        | Type              | rwh      | rwh      | rwh      | rwh  | rwh     | rwh  | rwh      | rwh      |

| A1 <sub>H</sub>  | P2 DIR                                                                                    | Reset: 00 <sub>H</sub> | Bit Field         | P7       | P6       | P5       | P4   | P3      | P2   | P1       | P0       |

| н                | P2 Direction Register                                                                     |                        | Туре              | rw       | rw       | rw       | rw   | rw      | rw   | rw       | rw       |

| B0 <sub>H</sub>  | P3 DATA                                                                                   | Reset: 00 <sub>H</sub> | Bit Field         | P7       | P6       | P5       | P4   | P3      | P2   | P1       | P0       |

| _ v <sub>H</sub> | P3 Data Register                                                                          |                        | Туре              | rwh      | rwh      | rwh      | rwh  | rwh     | rwh  | rwh      | rwh      |

| B1 <sub>H</sub>  | P3 DIR                                                                                    | Reset: 00 <sub>H</sub> | Bit Field         | P7       | P6       | P5       | P4   | P3      | P2   | P1       | P0       |

| D'H              | P3 Direction Register                                                                     | resett oo <sub>H</sub> | Туре              | rw       | rw       | rw       | rw   | rw      | rw   | rw       | rw       |

| RMAP =           | 0, Page 1                                                                                 |                        | 1,500             |          |          |          |      |         |      | . **     | . •••    |

| 80 <sub>H</sub>  | P0 PUDSEL                                                                                 | Reset: FF <sub>H</sub> | Bit Field         |          | 0        | P5       | P4   | P3      | P2   | P1       | P0       |

| ООН              | P0 Pull-Up/Pull-Down Select Register                                                      |                        | Type              |          | r        | rw       | rw   | rw      | rw   | rw       | rw       |

| 86               | 6 <sub>H</sub> <b>P0_PUDEN Reset: C4<sub>H</sub></b> P0 Pull-Up/Pull-Down Enable Register |                        | Bit Field         |          | 0        | P5       | P4   | P3      | P2   | P1       | P0       |

| оон              |                                                                                           |                        | Type              |          | r        | rw       | rw   | rw      | rw   | rw       | rw       |

| 90 <sub>H</sub>  | P1 PUDSEL                                                                                 | Reset: FF <sub>H</sub> | Bit Field         | P7       | P6       | P5       | 1 ** | 0       | 1 44 | P1       | P0       |

| ЭОН              | P1 Pull-Up/Pull-Down S                                                                    |                        | Туре              | rw       | rw       | rw       |      | r       |      | rw       | rw       |

| 91 <sub>H</sub>  | P1 PUDEN                                                                                  | Reset: FF <sub>H</sub> | Bit Field         | P7       | P6       | P5       |      | 0       |      | P1       | P0       |

| 3 IH             | P1 Pull-Up/Pull-Down E                                                                    |                        | Туре              | rw       | rw       | rw       |      | r       |      | rw       | rw       |

| A0 <sub>H</sub>  | P2 PUDSEL                                                                                 | Reset: FF <sub>H</sub> | Bit Field         | P7       | P6       | P5       | P4   | P3      | P2   | P1       | P0       |

| A OH             | P2 Pull-Up/Pull-Down S                                                                    |                        | Туре              | rw       | rw       | rw       | rw   | rw      | rw   | rw       | rw       |

| A1 <sub>H</sub>  | P2 PUDEN                                                                                  | Reset: 00 <sub>H</sub> | Bit Field         | P7       | P6       | P5       | P4   | P3      | P2   | P1       | P0       |

| ΑΉ               | P2 Pull-Up/Pull-Down E                                                                    |                        | Type              | rw       | rw       | rw       | rw   | rw      | rw   | rw       | rw       |

| B0 <sub>H</sub>  | P3 PUDSEL                                                                                 | Reset: BF <sub>H</sub> | Bit Field         | P7       | P6       | P5       | P4   | P3      | P2   | P1       | P0       |

| Бон              | P3 Pull-Up/Pull-Down S                                                                    |                        | Type              | rw       | rw       | rw       | rw   | rw      | rw   | rw       | rw       |

| B1 <sub>H</sub>  | P3 PUDEN                                                                                  | Reset: 40 <sub>H</sub> | Bit Field         | P7       | P6       | P5       | P4   | P3      | P2   | P1       | P0       |

| ын               | P3 Pull-Up/Pull-Down E                                                                    |                        | Туре              | rw       | rw       | rw       | rw   | rw      | rw   | rw       | rw       |

| DMAD -           | 0, Page 2                                                                                 | 5                      | , ybe             | I VV     | 1 44     | I VV     | 1 44 | I VV    | I VV | I VV     | I VV     |

| 80 <sub>H</sub>  | PO ALTSELO                                                                                | Reset: 00 <sub>H</sub> | Bit Field         |          | 0        | P5       | P4   | P3      | P2   | P1       | P0       |

| оон              | P0_ALTSEL0 P0 Alternate Select 0 Re                                                       |                        | Туре              |          | r        | rw       | rw   | rw      | rw   | rw       | rw       |

| 96               | P0 ALTSEL1                                                                                | Reset: 00 <sub>H</sub> | Bit Field         |          | 0        | P5       | P4   | P3      | P2   | P1       | P0       |

| 86 <sub>H</sub>  | P0_ALTSELT P0 Alternate Select 1 Re                                                       |                        | Туре              |          | r        | rw       | rw   | rw      | rw   | rw       | rw       |

| 00               | P1 ALTSEL0                                                                                | Reset: 00 <sub>H</sub> | Bit Field         | P7       | P6       | P5       | ıw   | 0<br>0  | ıw   | P1       | P0       |

| 90 <sub>H</sub>  | P1_ALTSEL0 P1 Alternate Select 0 Re                                                       |                        |                   |          | -        |          |      |         |      |          | -        |

| 01               | P1 ALTSEL1                                                                                | •                      | Type<br>Bit Field | rw<br>P7 | rw<br>P6 | rw<br>P5 |      | r<br>0  |      | rw<br>P1 | rw<br>P0 |

| 91 <sub>H</sub>  | P1_ALTSEL1 P1 Alternate Select 1 Re                                                       | Reset: 00 <sub>H</sub> |                   |          | -        |          |      |         |      |          | -        |

| D0               |                                                                                           |                        | Type              | rw<br>P7 | rw<br>P6 | rw       | D4   | r<br>P3 | P2   | rw<br>P1 | rw<br>P0 |

| B0 <sub>H</sub>  | P3_ALTSEL0 P3 Alternate Select 0 Re                                                       | Reset: 00 <sub>H</sub> | Bit Field         |          | -        | P5       | P4   |         |      |          | -        |

|                  | . 57 mornate ocicot o Ne                                                                  | .g.5(6)                | Туре              | rw       | rw       | rw       | rw   | rw      | rw   | rw       | rw       |

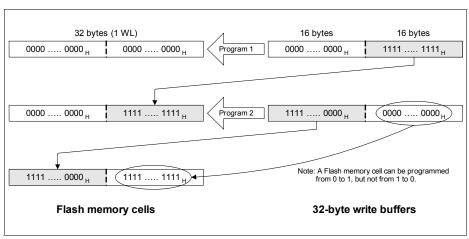

## 3.3.2 Flash Programming Width

For the P-Flash banks, a programmed wordline (WL) must be erased before it can be reprogrammed as the Flash cells can only withstand one gate disturb. This means that the entire sector containing the WL must be erased since it is impossible to erase a single WL.

For the D-Flash bank, the same WL can be programmed twice before erasing is required as the Flash cells are able to withstand two gate disturbs. Hence, it is possible to program the same WL, for example, with 16 bytes of data in two times (see Figure 12).

Figure 12 D-Flash Programming

Note: When programming a D-Flash WL the second time, the previously programmed Flash memory cells (whether 0s or 1s) should be reprogrammed with 0s to retain its original contents and to prevent "over-programming".

## 3.4.3 Interrupt Priority

Each interrupt source, except for NMI, can be individually programmed to one of the four possible priority levels. The NMI has the highest priority and supersedes all other interrupts. Two pairs of interrupt priority registers (IP and IPH, IP1 and IPH1) are available to program the priority level of each non-NMI interrupt vector.

A low-priority interrupt can be interrupted by a high-priority interrupt, but not by another interrupt of the same or lower priority. Further, an interrupt of the highest priority cannot be interrupted by any other interrupt source.

If two or more requests of different priority levels are received simultaneously, the request of the highest priority is serviced first. If requests of the same priority are received simultaneously, then an internal polling sequence determines which request is serviced first. Thus, within each priority level, there is a second priority structure determined by the polling sequence shown in **Table 18**.

Table 18 Priority Structure within Interrupt Level

| Level     |  |  |  |  |  |  |

|-----------|--|--|--|--|--|--|

| (highest) |  |  |  |  |  |  |

| 1         |  |  |  |  |  |  |

| 2         |  |  |  |  |  |  |

| 3         |  |  |  |  |  |  |

| 4         |  |  |  |  |  |  |

| 5         |  |  |  |  |  |  |

| 6         |  |  |  |  |  |  |

| 7         |  |  |  |  |  |  |

| 8         |  |  |  |  |  |  |

| 9         |  |  |  |  |  |  |

| 10        |  |  |  |  |  |  |

| 11        |  |  |  |  |  |  |

| 12        |  |  |  |  |  |  |

| 13        |  |  |  |  |  |  |

| 14        |  |  |  |  |  |  |

|           |  |  |  |  |  |  |

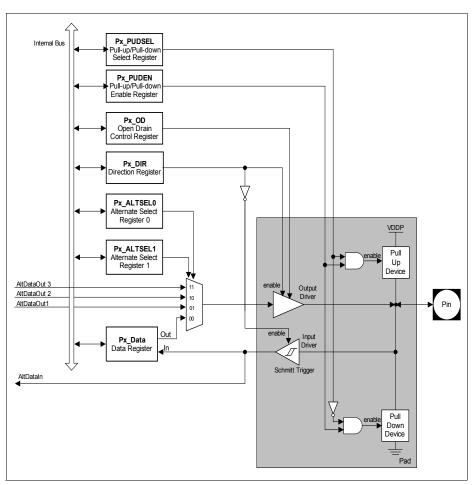

Figure 18 General Structure of Bidirectional Port

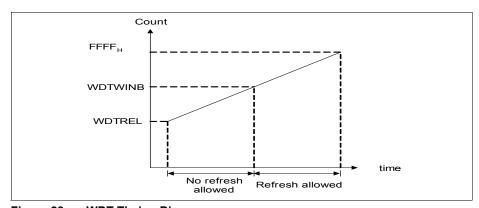

If the WDT is not serviced before the timer overflow, a system malfunction is assumed. As a result, the WDT NMI is triggered (assert WDTTO) and the reset prewarning is entered. The prewarning period lasts for  $30_{\rm H}$  count, after which the system is reset (assert WDTRST).

The WDT has a "programmable window boundary" which disallows any refresh during the WDT's count-up. A refresh during this window boundary constitutes an invalid access to the WDT, causing the reset prewarning to be entered but without triggering the WDT NMI. The system will still be reset after the prewarning period is over. The window boundary is from  $0000_{\rm H}$  to the value obtained from the concatenation of WDTWINB and  $00_{\rm H}$ .

After being serviced, the WDT continues counting up from the value (<WDTREL> \* 2<sup>8</sup>). The time period for an overflow of the WDT is programmable in two ways:

- the input frequency to the WDT can be selected to be either f<sub>PCLK</sub>/2 or f<sub>PCLK</sub>/128

- the reload value WDTREL for the high byte of WDT can be programmed in register WDTREL

The period,  $P_{WDT}$ , between servicing the WDT and the next overflow can be determined by the following formula:

$$P_{WDT} = \frac{2^{(1+WDTIN\times6)} \times (2^{16} - WDTREL \times 2^{8})}{f_{PCLK}}$$

If the Window-Boundary Refresh feature of the WDT is enabled, the period  $P_{WDT}$  between servicing the WDT and the next overflow is shortened if WDTWINB is greater than WDTREL, see **Figure 28**. This period can be calculated using the same formula by replacing WDTREL with WDTWINB. For this feature to be useful, WDTWINB should not be smaller than WDTREL.

Figure 28 WDT Timing Diagram

**Table 24** lists the possible watchdog time range that can be achieved for different module clock frequencies . Some numbers are rounded to 3 significant digits.

Table 24 Watchdog Time Ranges

| Reload value in WDTREL | Prescaler for f <sub>PCLK</sub> |                 |  |  |  |  |  |  |

|------------------------|---------------------------------|-----------------|--|--|--|--|--|--|

|                        | 2 (WDTIN = 0)                   | 128 (WDTIN = 1) |  |  |  |  |  |  |

|                        | 26.7 MHz                        | 26.7 MHz        |  |  |  |  |  |  |

| FF <sub>H</sub>        | 19.2 μs                         | 1.23 ms         |  |  |  |  |  |  |

| 7F <sub>H</sub>        | 2.48 ms                         | 159 ms          |  |  |  |  |  |  |

| 00 <sub>H</sub>        | 4.92 ms                         | 315 ms          |  |  |  |  |  |  |

## 3.14 High-Speed Synchronous Serial Interface

The High-Speed Synchronous Serial Interface (SSC) supports full-duplex and half-duplex synchronous communication. The serial clock signal can be generated by the SSC internally (master mode), using its own 16-bit baud-rate generator, or can be received from an external master (slave mode). Data width, shift direction, clock polarity and phase are programmable. This allows communication with SPI-compatible devices or devices using other synchronous serial interfaces.

#### Features:

- Master and slave mode operation

- Full-duplex or half-duplex operation

- Transmit and receive buffered

- · Flexible data format

- Programmable number of data bits: 2 to 8 bits

- Programmable shift direction: LSB or MSB shift first

- Programmable clock polarity: idle low or high state for the shift clock

- Programmable clock/data phase: data shift with leading or trailing edge of the shift clock

- · Variable baud rate

- Compatible with Serial Peripheral Interface (SPI)

- · Interrupt generation

- On a transmitter empty condition

- On a receiver full condition

- On an error condition (receive, phase, baud rate, transmit error)

## 3.18 Analog-to-Digital Converter

The XC866 includes a high-performance 10-bit Analog-to-Digital Converter (ADC) with eight multiplexed analog input channels. The ADC uses a successive approximation technique to convert the analog voltage levels from up to eight different sources. The analog input channels of the ADC are available at Port 2.

#### Features:

- Successive approximation

- 8-bit or 10-bit resolution (TUE of ± 1 LSB and ± 2 LSB, respectively)

- · Eight analog channels

- · Four independent result registers

- Result data protection for slow CPU access (wait-for-read mode)

- · Single conversion mode

- · Autoscan functionality

- · Limit checking for conversion results

- Data reduction filter (accumulation of up to 2 conversion results)

- · Two independent conversion request sources with programmable priority

- Selectable conversion request trigger

- · Flexible interrupt generation with configurable service nodes

- · Programmable sample time

- · Programmable clock divider

- · Cancel/restart feature for running conversions

- Integrated sample and hold circuitry

- Compensation of offset errors

- Low power modes

| Table 31 | JTAG ID Summary |

|----------|-----------------|

|----------|-----------------|

| ROM | XC866L-4RR | 1013 9083 <sub>H</sub> |  |  |

|-----|------------|------------------------|--|--|

|     | XC866-4RR  | 1013 9083 <sub>H</sub> |  |  |

|     | XC866L-2RR | 1013 9083 <sub>H</sub> |  |  |

|     | XC866-2RR  | 1013 9083 <sub>H</sub> |  |  |

## 3.20 Identification Register

The XC866 identity register is located at Page 1 of address B3<sub>H</sub>.

ID Identity Register

**Reset Value: 0000 0010<sub>B</sub>**2 1 0

|   | 7 | 6  | 5      | 4  | 3  | 2 | 1     | 0 |

|---|---|----|--------|----|----|---|-------|---|

|   |   | I  | PRODID | I  | I  |   | VERID |   |

|   |   | I. | עועטאץ | I. | T. |   | VERID |   |

| _ |   |    | r      |    |    | • | r     |   |

| Field  | Bits  | Туре | Description                      |

|--------|-------|------|----------------------------------|

| VERID  | [2:0] | r    | Version ID<br>010 <sub>B</sub>   |

| PRODID | [7:3] | r    | Product ID<br>00000 <sub>B</sub> |

Table 34 Input/Output Characteristics (Operating Conditions apply)

| Parameter                                                                                                                                                                 | Symbol            |          | Limit                 | Values                  | Unit | Test Conditions                                                                          |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------|-----------------------|-------------------------|------|------------------------------------------------------------------------------------------|--|

|                                                                                                                                                                           |                   |          | min.                  | max.                    |      | Remarks                                                                                  |  |

| Input low voltage at XTAL1                                                                                                                                                | $V_{ILX}$         | SR       | V <sub>SS</sub> - 0.5 | $0.3 \times V_{ m DDC}$ | V    |                                                                                          |  |

| Input high voltage at XTAL1                                                                                                                                               | $V_{IHX}$         | SR       | $V_{ m DDC}$          | V <sub>DDC</sub> + 0.5  | V    |                                                                                          |  |

| Pull-up current                                                                                                                                                           | $I_{PU}$          | SR       | _                     | -10                     | μΑ   | $V_{IH,min}$                                                                             |  |

|                                                                                                                                                                           |                   |          | -150                  | _                       | μΑ   | $V_{IL,max}$                                                                             |  |

| Pull-down current                                                                                                                                                         | $I_{PD}$          | SR       | _                     | 10                      | μΑ   | $V_{IL,max}$                                                                             |  |

|                                                                                                                                                                           |                   |          | 150                   | _                       | μΑ   | $V_{IH,min}$                                                                             |  |

| Input leakage current <sup>2)</sup>                                                                                                                                       | I <sub>OZ1</sub>  | CC       | -1                    | 1                       | μA   | 0 < $V_{\rm IN}$ < $V_{\rm DDP}$ ,<br>$T_{\rm A} \le$ 125°C , XC866-4FR and XC866-2FR    |  |

|                                                                                                                                                                           |                   |          | -2.5                  | 1                       | μΑ   | 0 < $V_{\rm IN}$ < $V_{\rm DDP}$ ,<br>$T_{\rm A} \le$ 125°C, XC866-1FR<br>and ROM device |  |

| Input current at XTAL1                                                                                                                                                    | $I_{ILX}$         | CC       | -10                   | 10                      | μΑ   |                                                                                          |  |

| Overload current on any pin                                                                                                                                               | $I_{OV}$          | SR       | -5                    | 5                       | mA   |                                                                                          |  |

| Absolute sum of overload currents                                                                                                                                         | $\Sigma   I_{OV}$ | <br>SR   | _                     | 25                      | mA   | 3)                                                                                       |  |

| Voltage on any pin during $V_{\rm DDP}$ power off                                                                                                                         | $V_{PO}$          | SR       | _                     | 0.3                     | V    | 4)                                                                                       |  |

| $\label{eq:maximum} \begin{array}{l} \hline & \\ \text{Maximum current per} \\ \text{pin (excluding } V_{\text{DDP}} \text{ and} \\ V_{\text{SS}}) \\ \end{array}$        | $I_{M}$           | SR       | _                     | 15                      | mA   |                                                                                          |  |

| $\label{eq:maximum} \begin{array}{l} \hline \text{Maximum current for all} \\ \text{pins (excluding } V_{\text{DDP}} \\ \text{and } V_{\text{SS}}) \\ \hline \end{array}$ | $\Sigma  I_{M} $  | SR       | _                     | 60                      | mA   |                                                                                          |  |

| $\begin{array}{c} {\rm Maximum~current~into} \\ V_{\rm DDP} \end{array}$                                                                                                  | $I_{MVDI}$        | OP<br>SR | _                     | 80                      | mA   |                                                                                          |  |

| $\begin{tabular}{ll} \hline \textbf{Maximum current out of} \\ V_{\rm SS} \\ \hline \end{tabular}$                                                                        | I <sub>MVS</sub>  | SR       | _                     | 80                      | mA   |                                                                                          |  |

Table 34 Input/Output Characteristics (Operating Conditions apply)

| Parameter                                                | Symbol              | Limit                  | Values                        | Unit | Test Conditions<br>Remarks |  |

|----------------------------------------------------------|---------------------|------------------------|-------------------------------|------|----------------------------|--|

|                                                          |                     | min.                   | max.                          |      |                            |  |

| $V_{DDP}$ = 3.3V Range                                   |                     |                        |                               |      |                            |  |

| Output low voltage                                       | $V_{OL}$ CC         | _                      | 1.0                           | V    | $I_{\rm OL}$ = 8 mA        |  |

|                                                          |                     | _                      | 0.4                           | V    | $I_{\rm OL}$ = 2.5 mA      |  |

| Output high voltage                                      | V <sub>OH</sub> CC  | V <sub>DDP</sub> - 1.0 | _                             | V    | $I_{\text{OH}}$ = -8 mA    |  |

|                                                          |                     | V <sub>DDP</sub> - 0.4 | _                             | V    | I <sub>OH</sub> = -2.5 mA  |  |

| Input low voltage on port pins (all except P0.0 & P0.1)  | $V_{ILP}$ SR        | _                      | $0.3 \times V_{\mathrm{DDP}}$ | V    | CMOS Mode                  |  |

| Input low voltage on P0.0 & P0.1                         | $V_{\rm ILP0}$ SR   | -0.2                   | $0.3 \times V_{\text{DDP}}$   | V    | CMOS Mode                  |  |

| Input low voltage on RESET pin                           | $V_{ILR}$ SR        | _                      | $V_{ m DDP}$                  | V    | CMOS Mode                  |  |

| Input low voltage on TMS pin                             | $V_{ILT}$ SR        | _                      | $V_{ m DDP}$                  | V    | CMOS Mode                  |  |

| Input high voltage on port pins (all except P0.0 & P0.1) | V <sub>IHP</sub> SR | $V_{\text{DDP}}$       | _                             | V    | CMOS Mode                  |  |

| Input high voltage on P0.0 & P0.1                        | $V_{IHP0}SR$        | $0.7 \times V_{DDP}$   | $V_{DDP}$                     | V    | CMOS Mode                  |  |

| Input high voltage on RESET pin                          | $V_{IHR}$ SR        | $0.7 \times V_{DDP}$   | _                             | V    | CMOS Mode                  |  |

| Input high voltage on TMS pin                            | $V_{IHT}$ SR        | $V_{DDP}$              | _                             | V    | CMOS Mode                  |  |

| Input Hysteresis <sup>1)</sup> on<br>Port pins           | HYS CC              | $V_{ m DDP}$           | _                             | V    | CMOS Mode                  |  |

| Input Hysteresis <sup>1)</sup> on<br>XTAL1               | HYSXCC              | $V_{ m DDC}$           | _                             | V    |                            |  |

| Input low voltage at XTAL1                               | $V_{ILX}$ SR        | V <sub>SS</sub> - 0.5  | $V_{ m DDC}$                  | V    |                            |  |

| Input high voltage at<br>XTAL1                           | $V_{IHX}$ SR        | $V_{ m DDC}$           | V <sub>DDC</sub> + 0.5        | V    |                            |  |

Table 36 ADC Characteristics (Operating Conditions apply;  $V_{DDP}$  = 5V Range)

|                                                   |                       | • •  |          | •    | 117, 001 |                  |  |

|---------------------------------------------------|-----------------------|------|----------|------|----------|------------------|--|

| Parameter                                         | Symbol                | Li   | mit Valu | es   | Unit     | Test Conditions/ |  |

|                                                   |                       | min. | typ.     | max. |          | Remarks          |  |

| Switched capacitance at the analog voltage inputs | C <sub>AINSW</sub> CC | _    | 5        | 7    | pF       | 2)4)             |  |

| Input resistance of the reference input           | R <sub>AREF</sub> CC  | _    | 1        | 2    | kΩ       | 2)               |  |

| Input resistance of the selected analog channel   | R <sub>AIN</sub> CC   | _    | 1        | 1.5  | kΩ       | 2)               |  |

<sup>&</sup>lt;sup>1)</sup> TUE is tested at  $V_{\rm AREF}$  = 5.0 V,  $V_{\rm AGND}$  = 0 V ,  $V_{\rm DDP}$  = 5.0 V.

<sup>&</sup>lt;sup>2)</sup> Not subject to production test, verified by design/characterization.

<sup>3)</sup> This represents an equivalent switched capacitance. This capacitance is not switched to the reference voltage at once. Instead of this, smaller capacitances are successively switched to the reference voltage.

<sup>4)</sup> The sampling capacity of the conversion C-Network is pre-charged to V<sub>AREF</sub>/2 before connecting the input to the C-Network. Because of the parasitic elements, the voltage measured at ANx is lower than V<sub>AREF</sub>/2.

## 4.2.4 Power Supply Current

Table 37 Power Supply Current Parameters (Operating Conditions apply;  $V_{\text{DDP}} = 5V \text{ range}$ )

| Parameter                          | Symbol    | Limit              | Values             | Unit | Test Condition<br>Remarks              |  |

|------------------------------------|-----------|--------------------|--------------------|------|----------------------------------------|--|

|                                    |           | typ. <sup>1)</sup> | max. <sup>2)</sup> |      |                                        |  |

| $V_{\rm DDP}$ = 5V Range           | 1         |                    |                    | •    |                                        |  |

| Active Mode                        | $I_{DDP}$ | 22.6               | 24.5               | mA   | 3)                                     |  |

| Idle Mode                          | $I_{DDP}$ | 17.2               | 19.7               | mA   | XC866-4FR,<br>XC866-2FR <sup>4)</sup>  |  |

|                                    |           | 12.5               | 14                 | mA   | XC866-1FR,<br>ROM device <sup>4)</sup> |  |

| Active Mode with slow-down enabled | $I_{DDP}$ | 7.2                | 8.2                | mA   | XC866-4FR,<br>XC866-2FR <sup>5)</sup>  |  |

|                                    |           | 5.6                | 7.5                | mA   | XC866-1FR,<br>ROM device <sup>5)</sup> |  |

| Idle Mode with slow-down enabled   | $I_{DDP}$ | 7.1                | 8                  | mA   | XC866-4FR,<br>XC866-2FR <sup>6)</sup>  |  |

|                                    |           | 5.1                | 7.2                | mA   | XC866-1FR,<br>ROM device <sup>6)</sup> |  |

<sup>1)</sup> The typical  $I_{\rm DDP}$  values are periodically measured at  $T_{\rm A}$  = + 25 °C and  $V_{\rm DDP}$  = 5.0 V.

The maximum  $I_{\rm DDP}$  values are measured under worst case conditions ( $T_{\rm A}$  = + 125 °C and  $V_{\rm DDP}$  = 5.5 V).

<sup>3)</sup> I<sub>DDP</sub> (active mode) is measured with: CPU clock and input clock to all peripherals running at 26.7 MHz(set by on-chip oscillator of 10 MHz and NDIV in PLL\_CON to 0010<sub>B</sub>), RESET = V<sub>DDP</sub>, no load on ports.

<sup>4)</sup> I<sub>DDP</sub> (idle mode) is measured with: <u>CPU clock</u> disabled, watchdog timer disabled, input clock to all peripherals enabled and running at 26.7 MHz, <u>RESET</u> = V<sub>DDP</sub>, no load on ports.

<sup>5)</sup> I<sub>DDP</sub> (active mode with slow-down mode) is measured with: CPU clock and input clock to all peripherals running at 833 KHz by setting CLKREL in CMCON to 0101<sub>B</sub>, RESET = V<sub>DDP</sub>, no load on ports.

<sup>6)</sup> I<sub>DDP</sub> (idle mode with slow-down mode) is measured with: CPU clock disabled, watchdog timer disabled, input clock to all peripherals enabled and running at 833 KHz by setting CLKREL in CMCON to 0101<sub>B</sub>, RESET = V<sub>DDP</sub>, no load on ports.

Table 38 Power Down Current (Operating Conditions apply;  $V_{\text{DDP}}$  = 5V range )

| Parameter                     | Symbol    | Limit              | Values             | Unit | Test Condition<br>Remarks                                    |  |

|-------------------------------|-----------|--------------------|--------------------|------|--------------------------------------------------------------|--|

|                               |           | typ. <sup>1)</sup> | max. <sup>2)</sup> |      |                                                              |  |

| $V_{DDP}$ = 5V Range          |           |                    |                    |      |                                                              |  |

| Power-Down Mode <sup>3)</sup> | $I_{PDP}$ | 1                  | 10                 | μΑ   | $T_{A} = + 25  {}^{\circ}\text{C.}^{4)}$                     |  |

|                               |           | -                  | 30                 | μΑ   | $T_A$ = + 85 °C, XC866-4FR, XC866-2FR <sup>4)5</sup>         |  |

|                               |           | -                  | 35                 | μΑ   | $T_{A}$ = + 85 °C, XC866-<br>1FR, ROM device <sup>4)5)</sup> |  |

<sup>&</sup>lt;sup>1)</sup> The typical  $I_{\rm PDP}$  values are measured at  $V_{\rm DDP}$  = 5.0 V.

<sup>&</sup>lt;sup>2)</sup> The maximum  $I_{\rm PDP}$  values are measured at  $V_{\rm DDP}$  = 5.5 V.

<sup>&</sup>lt;sup>3)</sup>  $I_{PDP}$  (power-down mode) has a maximum value of 200  $\mu$ A at  $T_A$  = + 125 °C.

<sup>4)</sup> I<sub>PDP</sub> (power-down mode) is measured with: RESET = V<sub>DDP</sub>, V<sub>AGND</sub>= V<sub>SS</sub>, RXD/INT0 = V<sub>DDP</sub>; rest of the ports are programmed to be input with either internal pull devices enabled or driven externally to ensure no floating inputs.

<sup>&</sup>lt;sup>5)</sup> Not subject to production test, verified by design/characterization.

#### 4.3 AC Parameters

## 4.3.1 Testing Waveforms

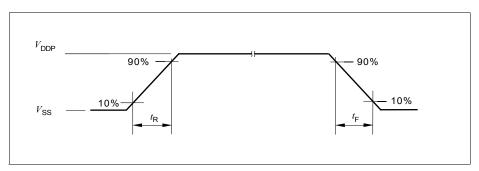

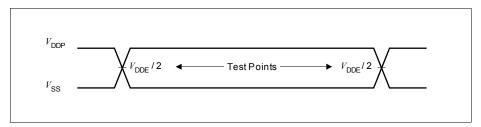

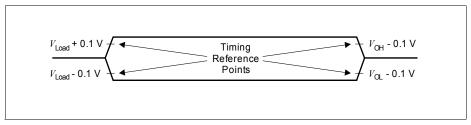

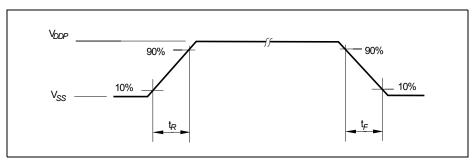

The testing waveforms for rise/fall time, output delay and output high impedance are shown in Figure 38, Figure 39 and Figure 40.

Figure 38 Rise/Fall Time Parameters

Figure 39 Testing Waveform, Output Delay

Figure 40 Testing Waveform, Output High Impedance

## 4.3.2 Output Rise/Fall Times

Table 41 Output Rise/Fall Times Parameters (Operating Conditions apply)

| Parameter                  | Symbol                          | Limit<br>Values |      | Unit | Test Conditions      |  |  |

|----------------------------|---------------------------------|-----------------|------|------|----------------------|--|--|

|                            |                                 | min.            | max. |      |                      |  |  |

| $V_{\rm DDP}$ = 5V Range   |                                 |                 | •    | '    | 1                    |  |  |

| Rise/fall times 1) 2)      | t <sub>R</sub> , t <sub>F</sub> | _               | 10   | ns   | 20 pF. <sup>3)</sup> |  |  |

| $V_{\rm DDP}$ = 3.3V Range |                                 |                 | •    | '    | 1                    |  |  |

| Rise/fall times 1) 2)      | t <sub>R</sub> , t <sub>F</sub> | _               | 10   | ns   | 20 pF. <sup>4)</sup> |  |  |

$<sup>^{1)}</sup>$  Rise/Fall time measurements are taken with 10% - 90% of the pad supply.

$<sup>^{\</sup>rm 4)}$  Additional rise/fall time valid for C  $_{\rm L}$  = 20pF - 100pF @ 0.225 ns/pF.

Figure 41 Rise/Fall Times Parameters

<sup>&</sup>lt;sup>2)</sup> Not all parameters are 100% tested, but are verified by design/characterization and test correlation.

$<sup>^{3)}</sup>$  Additional rise/fall time valid for  $C_L$  = 20pF - 100pF @ 0.125 ns/pF.

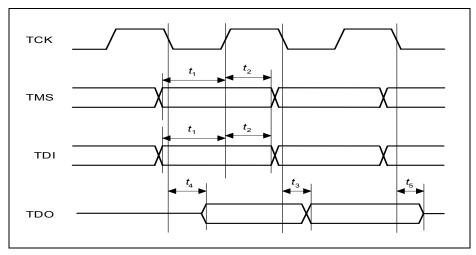

Table 45 JTAG Timing (Operating Conditions apply;  $C_L = 50 \text{ pF}$ )

| Parameter                                      | Symbol |    | Limits |     | Unit |

|------------------------------------------------|--------|----|--------|-----|------|

|                                                |        |    | min    | max |      |

| TMS setup to TCK _r                            | $t_1$  | SR | 8.0    | -   | ns   |

| TMS hold to TCK _r                             | $t_2$  | SR | 5.0    | -   | ns   |

| TDI setup to TCK _r                            | $t_1$  | SR | 11.0   | _   | ns   |

| TDI hold to TCK _/                             | $t_2$  | SR | 6.0    | -   | ns   |

| TDO valid output from TCK ¬_                   | $t_3$  | CC | _      | 23  | ns   |

| TDO high impedance to valid output from TCK ٦  | $t_4$  | CC | _      | 26  | ns   |

| TDO valid output to high impedance from TCK ٦_ | $t_5$  | CC | _      | 18  | ns   |

Figure 44 JTAG Timing