Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Last Time Buy                                                                |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | XC800                                                                        |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 86MHz                                                                        |

| Connectivity               | SSI, UART/USART                                                              |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 19                                                                           |

| Program Memory Size        | 8KB (8K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 768 × 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                  |

| Data Converters            | A/D 8x10b                                                                    |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 38-TFSOP (0.173", 4.40mm Width)                                              |

| Supplier Device Package    | PG-TSSOP-38                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xc8662fribefxuma1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

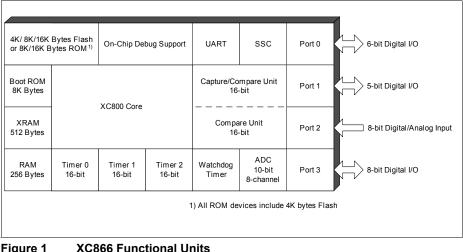

# 8-Bit Single-Chip Microcontroller XC800 Family

#### 1 **Summary of Features**

- High-performance XC800 Core •

- compatible with standard 8051 processor

- two clocks per machine cycle architecture (for memory access without wait state)

- two data pointers

- On-chip memory

- 8 Kbytes of Boot ROM

- 256 bytes of RAM

- 512 bytes of XRAM

- 4/8/16 Kbytes of Flash; or 8/16 Kbytes of ROM, with additional 4 Kbytes of Flash (includes memory protection strategy)

- I/O port supply at 3.3 V/5.0 V and core logic supply at 2.5 V (generated by embedded voltage regulator)

(further features are on next page)

# XC866

# **General Device Information**

| Symbol | Pin<br>Number | Туре | Reset<br>State | Function           |                                                                               |

|--------|---------------|------|----------------|--------------------|-------------------------------------------------------------------------------|

| P3     |               | I    |                |                    | directional general purpose I/O port. It as alternate functions for the CCU6. |

| P3.0   | 32            |      | Hi-Z           | CCPOS1_2<br>CC60_0 | CCU6 Hall Input 1<br>Input/Output of Capture/Compare<br>channel 0             |

| P3.1   | 33            |      | Hi-Z           | CCPOS0_2<br>CC61_2 | CCU6 Hall Input 0<br>Input/Output of Capture/Compare<br>channel 1             |

|        |               |      |                | COUT60_0           | Output of Capture/Compare<br>channel 0                                        |

| P3.2   | 34            |      | Hi-Z           | CCPOS2_2<br>CC61_0 | CCU6 Hall Input 2<br>Input/Output of Capture/Compare<br>channel 1             |

| P3.3   | 35            |      | Hi-Z           | COUT61_0           | Output of Capture/Compare<br>channel 1                                        |

| P3.4   | 36            |      | Hi-Z           | CC62_0             | Input/Output of Capture/Compare<br>channel 2                                  |

| P3.5   | 37            |      | Hi-Z           | COUT62_0           | Output of Capture/Compare<br>channel 2                                        |

| P3.6   | 30            |      | PD             | CTRAP_0            | CCU6 Trap Input                                                               |

| P3.7   | 31            |      | Hi-Z           | EXINT4<br>COUT63_0 | External Interrupt Input 4<br>Output of Capture/Compare<br>channel 3          |

## Table 3Pin Definitions and Functions (cont'd)

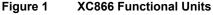

# 3.2 Memory Organization

İnfineon

The XC866 CPU operates in the following five address spaces:

- · 8 Kbytes of Boot ROM program memory

- 256 bytes of internal RAM data memory

- 512 bytes of XRAM memory (XRAM can be read/written as program memory or external data memory)

- a 128-byte Special Function Register area

- 4/8/16 Kbytes of Flash program memory (Flash devices); or 8/16 Kbytes of ROM program memory, with additional 4 Kbytes of Flash (ROM devices)

Figure 6 illustrates the memory address spaces of the XC866-4FR device.

### Figure 6 Memory Map of XC866 Flash Devices

### Table 5 Flash Protection Type for XC866-2FR and XC866-4FR devices

| PASSWORD              | Type of Protection      | Flash Banks to Erase when<br>Unprotected |

|-----------------------|-------------------------|------------------------------------------|

| 1XXXXXXX <sub>B</sub> | Flash Protection Mode 1 | All Banks                                |

| 0XXXXXXAB             | Flash Protection Mode 0 | P-Flash Bank                             |

#### For XC866-1FR device and ROM devices:

The selection of protection type is summarized in Table 6.

#### Table 6 Flash Protection Type for XC866-1FR device and ROM devices

| PASSWORD              | Type of Protection<br>(Applicable to the<br>whole Flash) | Sectors to Erase when Unprotected | Comments                           |

|-----------------------|----------------------------------------------------------|-----------------------------------|------------------------------------|

| 1XXXXXX <sub>B</sub>  | Read/Program/Erase                                       | All Sectors                       | Compatible to<br>Protection mode 1 |

| 00001XXX <sub>B</sub> | Erase                                                    | Sector 0                          |                                    |

| 00010XXX <sub>B</sub> | Erase                                                    | Sector 0 and 1                    |                                    |

| 00011XXX <sub>B</sub> | Erase                                                    | Sector 0 to 2                     |                                    |

| 00100XXX <sub>B</sub> | Erase                                                    | Sector 0 to 3                     |                                    |

| 00101XXX <sub>B</sub> | Erase                                                    | Sector 0 to 4                     |                                    |

| 00110XXX <sub>B</sub> | Erase                                                    | Sector 0 to 5                     |                                    |

| 00111XXX <sub>B</sub> | Erase                                                    | Sector 0 to 6                     |                                    |

| 01000XXX <sub>B</sub> | Erase                                                    | Sector 0 to 7                     |                                    |

| 01001XXX <sub>B</sub> | Erase                                                    | Sector 0 to 8                     |                                    |

| 01010XXX <sub>B</sub> | Erase                                                    | All Sectors                       |                                    |

| Others                | Erase                                                    | None                              |                                    |

Although no protection scheme can be considered infallible, the XC866 memory protection strategy provides a very high level of protection for a general purpose microcontroller.

In order to access a register located in a page different from the actual one, the current page must be left. This is done by reprogramming the bit field PAGE in the page register. Only then can the desired access be performed.

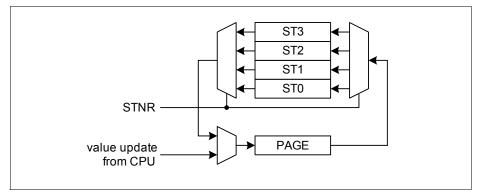

If an interrupt routine is initiated between the page register access and the module register access, and the interrupt needs to access a register located in another page, the current page setting can be saved, the new one programmed and finally, the old page setting restored. This is possible with the storage fields STx (x = 0 - 3) for the save and restore action of the current page setting. By indicating which storage bit field should be used in parallel with the new page value, a single write operation can:

- Save the contents of PAGE in STx before overwriting with the new value (this is done in the beginning of the interrupt routine to save the current page setting and program the new page number); or

- Overwrite the contents of PAGE with the contents of STx, ignoring the value written to the bit positions of PAGE

(this is done at the end of the interrupt routine to restore the previous page setting before the interrupt occurred)

### Figure 10 Storage Elements for Paging

With this mechanism, a certain number of interrupt routines (or other routines) can perform page changes without reading and storing the previously used page information. The use of only write operations makes the system simpler and faster. Consequently, this mechanism significantly improves the performance of short interrupt routines.

The XC866 supports local address extension for:

- Parallel Ports

- Analog-to-Digital Converter (ADC)

- Capture/Compare Unit 6 (CCU6)

- System Control Registers

# 3.2.4 XC866 Register Overview

The SFRs of the XC866 are organized into groups according to their functional units. The contents (bits) of the SFRs are summarized in **Table 7** to **Table 15**, with the addresses of the bitaddressable SFRs appearing in bold typeface.

The CPU SFRs can be accessed in both the standard and mapped memory areas (RMAP = 0 or 1).

| Addr            | Register Name                                | I                                    | Bit       | 7          | 6          | 5          | 4          | 3     | 2    | 1    | 0     |  |

|-----------------|----------------------------------------------|--------------------------------------|-----------|------------|------------|------------|------------|-------|------|------|-------|--|

| RMAP =          | 0 or 1                                       |                                      |           |            | 1          |            |            | 1     |      | 1    |       |  |

| 81 <sub>H</sub> | SP Rese                                      | t: 07 <sub>H</sub>                   | Bit Field |            |            |            | S          | P     |      |      |       |  |

|                 | Stack Pointer Register                       |                                      | Туре      |            |            |            | r          | w     |      |      |       |  |

| 82 <sub>H</sub> | DPL Rese                                     | t: 00 <sub>H</sub>                   | Bit Field | DPL7       | DPL6       | DPL5       | DPL4       | DPL3  | DPL2 | DPL1 | DPL0  |  |

|                 | Data Pointer Register Low                    |                                      | Туре      | rw         | rw         | rw         | rw         | rw    | rw   | rw   | rw    |  |

| 83 <sub>H</sub> | DPH Rese                                     | t: 00 <sub>H</sub>                   | Bit Field | DPH7       | DPH6       | DPH5       | DPH4       | DPH3  | DPH2 | DPH1 | DPH0  |  |

|                 | Data Pointer Register High                   |                                      | Туре      | rw         | rw         | rw         | rw         | rw    | rw   | rw   | rw    |  |

| 87 <sub>H</sub> |                                              | t: 00 <sub>H</sub>                   | Bit Field | SMOD       |            | 0          |            | GF1   | GF0  | 0    | IDLE  |  |

|                 | Power Control Register                       |                                      | Туре      | rw         |            | r          |            | rw    | rw   | r    | rw    |  |

| 88 <sub>H</sub> |                                              | t: 00 <sub>H</sub>                   | Bit Field | TF1        | TR1        | TF0        | TR0        | IE1   | IT1  | IE0  | IT0   |  |

|                 | Timer Control Register                       |                                      | Туре      | rwh        | rw         | rwh        | rw         | rwh   | rw   | rwh  | rw    |  |

| 89 <sub>H</sub> |                                              | t: 00 <sub>H</sub>                   | Bit Field | GATE1      | 0          | Τ          | 1M         | GATE0 | 0    | T    | M     |  |

|                 | Timer Mode Register                          |                                      | Туре      | rw         | r          | r          | w          | rw    | r    | r    | w     |  |

| 8A <sub>H</sub> |                                              | Reset: 00 <sub>H</sub> Bit Field VAL |           |            |            |            |            |       |      |      |       |  |

|                 | Timer 0 Register Low                         |                                      | Туре      |            |            |            | rv         | vh    |      |      |       |  |

| 8B <sub>H</sub> |                                              | t: 00 <sub>H</sub>                   | Bit Field |            |            |            | V          | AL    |      |      |       |  |

|                 | Timer 1 Register Low                         |                                      | Туре      |            |            |            | rv         | vh    |      |      |       |  |

| 8C <sub>H</sub> |                                              | t: 00 <sub>H</sub>                   | Bit Field | VAL rwh    |            |            |            |       |      |      |       |  |

|                 | Timer 0 Register High                        |                                      | Туре      |            |            |            |            |       |      |      |       |  |

| 8D <sub>H</sub> |                                              | t: 00 <sub>H</sub>                   | Bit Field | VAL        |            |            |            |       |      |      |       |  |

|                 | Timer 1 Register High                        |                                      | Туре      |            |            |            | rv         | vh    |      |      |       |  |

| 98 <sub>H</sub> |                                              |                                      | Bit Field | SM0        | SM1        | SM2        | REN        | TB8   | RB8  | TI   | RI    |  |

|                 | Serial Channel Control Register              |                                      | Туре      | rw         | rw         | rw         | rw         | rw    | rwh  | rwh  | rwh   |  |

| 99 <sub>H</sub> |                                              | t: 00 <sub>H</sub>                   | Bit Field |            |            |            | V          | AL    |      |      |       |  |

|                 | Serial Data Buffer Register                  |                                      | Туре      | rwh        |            |            |            |       |      |      |       |  |

| A2 <sub>H</sub> |                                              | t: 00 <sub>H</sub>                   | Bit Field |            | 0          |            | TRAP_      |       | 0    |      | DPSEL |  |

|                 | Extended Operation Register                  |                                      | _         |            |            |            | EN         |       |      |      | 0     |  |

|                 |                                              |                                      | Туре      |            | r          |            | rw         |       | r    |      | rw    |  |

| A8 <sub>H</sub> | IEN0 Rese<br>Interrupt Enable Register 0     |                                      | Bit Field | EA         | 0          | ET2        | ES         | ET1   | EX1  | ET0  | EX0   |  |

|                 |                                              |                                      | Туре      | rw         | r          | rw         | rw         | rw    | rw   | rw   | rw    |  |

| B8 <sub>H</sub> | IP Rese<br>Interrupt Priority Register       |                                      | Bit Field |            | )          | PT2        | PS         | PT1   | PX1  | PT0  | PX0   |  |

|                 | . , .                                        |                                      | Туре      |            | r          | rw         | rw         | rw    | rw   | rw   | rw    |  |

| B9 <sub>H</sub> | IPH Rese<br>Interrupt Priority Register High |                                      | Bit Field |            | )          | PT2H       | PSH        | PT1H  | PX1H | PT0H | PX0H  |  |

|                 | , , , , ,                                    |                                      | Туре      |            | r          | rw         | rw         | rw    | rw   | rw   | rw    |  |

| D0 <sub>H</sub> | PSW Rese<br>Program Status Word Register     |                                      | Bit Field | CY         | AC         | F0         | RS1        | RS0   | OV   | F1   | P     |  |

| 50              | · ·                                          |                                      | Туре      | rw         | rwh        | rwh        | rw         | rw    | rwh  | rwh  | rh    |  |

| E0 <sub>H</sub> | ACC Rese<br>Accumulator Register             | · · · · · ·                          | Bit Field | ACC7       | ACC6       | ACC5       | ACC4       | ACC3  | ACC2 | ACC1 | ACC0  |  |

| =0              | ÷                                            |                                      | Туре      | rw         | rw         | rw         | rw         | rw    | rw   | rw   | rw    |  |

| E8 <sub>H</sub> | IEN1 Rese<br>Interrupt Enable Register 1     | t: 00 <sub>H</sub>                   | Bit Field | ECCIP<br>3 | ECCIP<br>2 | ECCIP<br>1 | ECCIP<br>0 | EXM   | EX2  | ESSC | EADC  |  |

|                 |                                              |                                      | Туре      | rw         | rw         | rw         | rw         | rw    | rw   | rw   | rw    |  |

### Table 7 CPU Register Overview

# Table 7CPU Register Overview (cont'd)

| Addr            | Register Name                    |                                      | Bit       | 7           | 6           | 5           | 4           | 3    | 2    | 1     | 0         |

|-----------------|----------------------------------|--------------------------------------|-----------|-------------|-------------|-------------|-------------|------|------|-------|-----------|

| F0 <sub>H</sub> | В                                | Reset: 00 <sub>H</sub>               | Bit Field | B7          | B6          | B5          | B4          | B3   | B2   | B1    | B0        |

|                 | B Register                       |                                      | Туре      | rw          | rw          | rw          | rw          | rw   | rw   | rw    | rw        |

| F8 <sub>H</sub> | IP1<br>Interrupt Priority Regis  | Reset: 00 <sub>H</sub><br>iter 1     | Bit Field | PCCIP<br>3  | PCCIP<br>2  | PCCIP<br>1  | PCCIP<br>0  | PXM  | PX2  | PSSC  | PADC      |

|                 |                                  |                                      | Туре      | rw          | rw          | rw          | rw          | rw   | rw   | rw    | rw        |

| F9 <sub>H</sub> | IPH1<br>Interrupt Priority Regis | Reset: 00 <sub>H</sub><br>ter 1 High | Bit Field | PCCIP<br>3H | PCCIP<br>2H | PCCIP<br>1H | PCCIP<br>0H | PXMH | PX2H | PSSCH | PADC<br>H |

|                 |                                  |                                      | Туре      | rw          | rw          | rw          | rw          | rw   | rw   | rw    | rw        |

The system control SFRs can be accessed in the standard memory area (RMAP = 0).

## Table 8 System Control Register Overview

| Addr            | Register Name                                                       | Bit       | 7             | 6           | 5            | 4            | 3            | 2             | 1            | 0           |  |

|-----------------|---------------------------------------------------------------------|-----------|---------------|-------------|--------------|--------------|--------------|---------------|--------------|-------------|--|

| RMAP =          | 0 or 1                                                              |           | 1             |             |              | 1            |              |               | 1            |             |  |

| 8F <sub>H</sub> | SYSCON0 Reset: 00 <sub>H</sub>                                      | Bit Field |               |             |              | 0            |              |               |              | RMAP        |  |

|                 | System Control Register 0                                           | Туре      |               |             |              | r            |              |               |              |             |  |

| RMAP =          | 0                                                                   |           | 1             |             |              |              |              |               |              |             |  |

| BF <sub>H</sub> | SCU_PAGE Reset: 00 <sub>H</sub>                                     | Bit Field | C             | )P          | ST           | STNR 0       |              |               | PAGE         |             |  |

|                 | Page Register for System Control                                    | Туре      | 1             | N           | ١            | v            | r            |               | rwh          |             |  |

| RMAP =          | 0, Page 0                                                           |           |               |             |              |              |              |               |              |             |  |

| B3 <sub>H</sub> | MODPISEL Reset: 00 <sub>H</sub><br>Peripheral Input Select Register | Bit Field |               | 0           | JTAG<br>TDIS | JTAG<br>TCKS | (            | 0             | EXINT<br>0IS | URRIS       |  |

|                 |                                                                     | Туре      |               | r           | rw           | rw           |              | r             | rw           | rw          |  |

| B4 <sub>H</sub> | IRCON0 Reset: 00 <sub>H</sub><br>Interrupt Request Register 0       | Bit Field | 0             | EXINT<br>6  | EXINT<br>5   | EXINT<br>4   | EXINT<br>3   | EXINT<br>2    | EXINT<br>1   | EXINT<br>0  |  |

|                 |                                                                     | Туре      | r             | rwh         | rwh          | rwh          | rwh          | rwh           | rwh          | rwh         |  |

| B5 <sub>H</sub> | IRCON1 Reset: 00 <sub>H</sub><br>Interrupt Request Register 1       | Bit Field | 0 ADCS<br>RC1 |             | ADCS<br>RC1  | ADCS<br>RC0  | RIR          | TIR           | EIR          |             |  |

|                 |                                                                     | Туре      |               | r           | rwh          |              | rwh rwh      |               | rwh          | rwh         |  |

| B7 <sub>H</sub> | EXICON0 Reset: 00 <sub>H</sub>                                      | Bit Field | EXI           | NT3         | EXINT2       |              | EXINT1       |               | EXI          | NT0         |  |

|                 | External Interrupt Control Register 0                               | Туре      | r             | w           |              | w            | rw           |               |              | w           |  |

| BA <sub>H</sub> | EXICON1 Reset: 00 <sub>H</sub>                                      | Bit Field |               | 0           |              | NT6          | EXINT5       |               | EXI          | NT4         |  |

|                 | External Interrupt Control Register 1                               | Туре      | r             |             | rw           |              | rw           |               | rw           |             |  |

| BB <sub>H</sub> | NMICON Reset: 00 <sub>H</sub><br>NMI Control Register               | Bit Field | 0             | NMI<br>ECC  | NMI<br>VDDP  | NMI<br>VDD   | NMI<br>OCDS  | NMI<br>FLASH  | NMI<br>PLL   | NMI<br>WDT  |  |

|                 |                                                                     | Туре      | r             | rw          | rw           | rw           | rw           | rw            | rw           | rw          |  |

| BC <sub>H</sub> | NMISR Reset: 00 <sub>H</sub><br>NMI Status Register                 | Bit Field | 0             | FNMI<br>ECC | FNMI<br>VDDP | FNMI<br>VDD  | FNMI<br>OCDS | FNMI<br>FLASH | FNMI<br>PLL  | FNMI<br>WDT |  |

|                 |                                                                     | Туре      | r             | rwh         | rwh          | rwh          | rwh          | rwh           | rwh          | rwh         |  |

| BD <sub>H</sub> | BCON Reset: 00 <sub>H</sub>                                         | Bit Field | BG            | SEL         | 0            | BREN         |              | BRPRE         |              | R           |  |

|                 | Baud Rate Control Register                                          | Туре      | r             | w           | r            | rw           |              | rw            |              | rw          |  |

| BE <sub>H</sub> | BG Reset: 00 <sub>H</sub>                                           | Bit Field |               |             |              | BR_V         | ALUE         |               |              |             |  |

|                 | Baud Rate Timer/Reload Register                                     | Туре      |               |             |              |              | N            |               |              |             |  |

| E9 <sub>H</sub> | FDCON Reset: 00 <sub>H</sub><br>Fractional Divider Control Register | Bit Field | BGS           | SYNEN       | ERRSY<br>N   | EOFSY<br>N   | BRK          | NDOV          | FDM          | FDEN        |  |

|                 | Туре                                                                |           | rw            | rw          | rwh          | rwh          | rwh          | rwh           | rw           | rw          |  |

| EA <sub>H</sub> | FDSTEP Reset: 00 <sub>H</sub>                                       | Bit Field | ld STEP       |             |              |              |              |               |              |             |  |

|                 | Fractional Divider Reload Register                                  | Туре гw   |               |             |              |              |              |               |              |             |  |

| EB <sub>H</sub> | FDRES Reset: 00 <sub>H</sub>                                        | Bit Field | d RESULT      |             |              |              |              |               |              |             |  |

|                 | Fractional Divider Result Register                                  | Туре      | rh            |             |              |              |              |               |              |             |  |

### Table 11 ADC Register Overview (cont'd)

| Addr            | Register Name                                                              | Bit       | 7          | 6          | 5          | 4          | 3          | 2          | 1          | 0          |            |            |

|-----------------|----------------------------------------------------------------------------|-----------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|

| CA <sub>H</sub> | ADC_CHINFR Reset: 00 <sub>H</sub>                                          | Bit Field | CHINF      |            |            |

|                 | Channel Interrupt Flag Register                                            | _         | 7          | 6          | 5          | 4          | 3          | 2          | 1          | 0          |            |            |

|                 |                                                                            | Туре      | rh         |            |            |

| CBH             | ADC_CHINCR Reset: 00 <sub>H</sub>                                          | Bit Field | CHINC      | CHINC      | CHINC      |            | CHINC      | CHINC<br>2 | CHINC<br>1 | CHINC<br>0 |            |            |

|                 | Channel Interrupt Clear Register                                           | Turne     | 7          | 6          | 5          | 4          | 3          |            |            | -          |            |            |

| 00              |                                                                            | Type      | W          | W          | W          | W          | W          | W          | W          | W          |            |            |

| CCH             | ADC_CHINSR Reset: 00 <sub>H</sub><br>Channel Interrupt Set Register        | Bit Field | CHINS<br>7 | CHINS<br>6 | CHINS<br>5 | CHINS<br>4 | CHINS<br>3 | CHINS<br>2 | CHINS<br>1 | CHINS<br>0 |            |            |

|                 |                                                                            | Туре      | w          | w          | w          | w          | w          | w          | w          | w          |            |            |

| CD <sub>H</sub> | ADC_CHINPR Reset: 00 <sub>H</sub><br>Channel Interrupt Node Pointer        | Bit Field | CHINP<br>7 | CHINP<br>6 | CHINP<br>5 | CHINP<br>4 | CHINP<br>3 | CHINP<br>2 | CHINP<br>1 | CHINP<br>0 |            |            |

|                 | Register                                                                   | Туре      | rw         |            |            |

| CEH             | ADC_EVINFR Reset: 00 <sub>H</sub><br>Event Interrupt Flag Register         | Bit Field | EVINF<br>7 | EVINF<br>6 | EVINF<br>5 | EVINF<br>4 | (          | )          | EVINF<br>1 | EVINF<br>0 |            |            |

|                 |                                                                            | Туре      | rh         | rh         | rh         | rh         | 1          | r          | rh         | rh         |            |            |

| CF <sub>H</sub> | ADC_EVINCR Reset: 00 <sub>H</sub><br>Event Interrupt Clear Flag Register   | Bit Field | EVINC<br>7 | EVINC<br>6 | EVINC<br>5 | EVINC<br>4 | -          |            | 0          |            | EVINC<br>1 | EVINC<br>0 |

|                 |                                                                            | Туре      | w          | w          | w          | w          | r          |            | w          | w          |            |            |

| D2 <sub>H</sub> | ADC_EVINSR Reset: 00 <sub>H</sub><br>Event Interrupt Set Flag Register     | Bit Field | EVINS<br>7 | EVINS<br>6 | EVINS<br>5 | EVINS<br>4 | (          | 0          |            | EVINS<br>0 |            |            |

|                 |                                                                            | Туре      | w          | w          | w          | w          | _          | r          | w          | w          |            |            |

| D3 <sub>H</sub> | ADC_EVINPR Reset: 00 <sub>H</sub><br>Event Interrupt Node Pointer Register | Bit Field | EVINP<br>7 | EVINP<br>6 | EVINP<br>5 | EVINP<br>4 | (          | )          | EVINP<br>1 | EVINP<br>0 |            |            |

|                 |                                                                            | Туре      | rw         | rw         | rw         | rw         | _          | r          | rw         | rw         |            |            |

| RMAP =          | 0, Page 6                                                                  |           |            |            |            |            |            |            |            |            |            |            |

| CA <sub>H</sub> | ADC_CRCR1 Reset: 00 <sub>H</sub><br>Conversion Request Control Register 1  | Bit Field | CH7        | CH6        | CH5        | CH4        |            | (          | 0          |            |            |            |

|                 |                                                                            | Туре      | rwh        | rwh        | rwh        | rwh        |            |            | r          |            |            |            |

| CB <sub>H</sub> | ADC_CRPR1 Reset: 00 <sub>H</sub><br>Conversion Request Pending             | Bit Field | CHP7       | CHP6       | CHP5       | CHP4       |            | (          | 0          |            |            |            |

|                 | Register 1                                                                 | Туре      | rwh        | rwh        | rwh        | rwh        |            |            | r          |            |            |            |

| CCH             | ADC_CRMR1 Reset: 00 <sub>H</sub><br>Conversion Request Mode Register 1     | Bit Field | Rsv        | LDEV       | CLR<br>PND | SCAN       | ENSI       | ENTR       | EN         | GT         |            |            |

|                 |                                                                            | Туре      | r          | w          | w          | rw         | rw         | rw         | r          | w          |            |            |

| CD <sub>H</sub> | ADC_QMR0 Reset: 00 <sub>H</sub>                                            | Bit Field | CEV        | TREV       | FLUSH      | CLRV       | TRMD       | ENTR       | EN         | GT         |            |            |

|                 | Queue Mode Register 0                                                      | Туре      | w          | w          | w          | w          | rw         | rw         | r          | w          |            |            |

| CEH             | ADC_QSR0 Reset: 20 <sub>H</sub><br>Queue Status Register 0                 | Bit Field | Rsv        | 0          | EMPTY      | EV         |            |            | 0          |            |            |            |

|                 |                                                                            | Туре      | r          | r          | rh         | rh         |            |            | r          | _          |            |            |

| CF <sub>H</sub> | ADC_Q0R0 Reset: 00 <sub>H</sub><br>Queue 0 Register 0                      | Bit Field | EXTR       | ENSI       | RF         | V          |            |            | REQCHN     | к          |            |            |

| <b>D</b> 0      | -                                                                          | Type      | rh         | rh         | rh         | rh         | r          |            | rh         |            |            |            |

| D2 <sub>H</sub> | ADC_QBUR0 Reset: 00 <sub>H</sub><br>Queue Backup Register 0                | Bit Field | EXTR       | ENSI       | RF         | V          | 0          | F          | REQCHN     | к          |            |            |

|                 |                                                                            | Туре      | rh         | rh         | rh         | rh         | r          | _          | rh         | _          |            |            |

| D2 <sub>H</sub> | ADC_QINR0 Reset: 00 <sub>H</sub><br>Queue Input Register 0                 | Bit Field | EXTR       | ENSI       | RF         |            | )          | F          | REQCHN     | к          |            |            |

|                 | Queue input register o                                                     | Туре      | w          | w          | w          |            | r          |            | w          |            |            |            |

The Timer 2 SFRs can be accessed in the standard memory area (RMAP = 0).

## Table 12Timer 2 Register Overview

| Addr            | Register Name                        |                        | Bit       | 7   | 6    | 5 | 4 | 3     | 2   | 1 | 0          |

|-----------------|--------------------------------------|------------------------|-----------|-----|------|---|---|-------|-----|---|------------|

| C0 <sub>H</sub> | T2_T2CON<br>Timer 2 Control Register | Reset: 00 <sub>H</sub> | Bit Field | TF2 | EXF2 | ( | ) | EXEN2 | TR2 | 0 | CP/<br>RL2 |

|                 |                                      |                        | Туре      | rwh | rwh  |   | r | rw    | rwh | r | rw         |

### Table 13 CCU6 Register Overview (cont'd)

| Addr            | Register Name                                                             | Bit       | 7     | 6            | 5            | 4          | 3            | 2          | 1            | 0          |  |

|-----------------|---------------------------------------------------------------------------|-----------|-------|--------------|--------------|------------|--------------|------------|--------------|------------|--|

| FF <sub>H</sub> | CCU6_TRPCTRH Reset: 00 <sub>H</sub>                                       | Bit Field |       | TRPEN        |              |            | TR           | PEN        |              |            |  |

|                 | Trap Control Register High                                                |           | N     | 13           |              |            |              |            |              |            |  |

|                 |                                                                           | Туре      | rw    | rw           |              |            | r            | w          |              |            |  |

| RMAP =          | 0, Page 3                                                                 |           |       |              |              |            |              |            |              |            |  |

| 9A <sub>H</sub> | CCU6_MCMOUTL Reset: 00 <sub>H</sub><br>Multi-Channel Mode Output Register | Bit Field | 0     | R            |              |            |              |            |              |            |  |

|                 | Low                                                                       | Туре      | r     | rh           |              |            | h            |            |              |            |  |

| 9B <sub>H</sub> | CCU6_MCMOUTH Reset: 00 <sub>H</sub><br>Multi-Channel Mode Output Register |           |       |              |              | EXPH       |              |            |              |            |  |

|                 | High                                                                      | Туре      | 1     | r            |              | rh         |              |            | rh           |            |  |

| 9C <sub>H</sub> | CCU6_ISL Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Status       | Bit Field | T12PM | T12OM        | ICC62F       | R          | ICC61F       | R          | ICC60F       | ICC60<br>R |  |

|                 | Register Low                                                              | Туре      | rh    | rh           | rh           | rh         | rh           | rh         | rh           | rh         |  |

| 9D <sub>H</sub> | CCU6_ISH Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Status       | Bit Field | STR   | IDLE         | WHE          | CHE        | TRPS         | TRPF       | T13PM        | T13CM      |  |

|                 | Register High                                                             | Туре      | rh    | rh           | rh           | rh         | rh           | rh         | rh           | rh         |  |

| 9E <sub>H</sub> | CCU6_PISEL0L Reset: 00 <sub>H</sub>                                       | Bit Field | IST   | ISTRP        |              | ISCC62 IS  |              | C61        | ISC          | C60        |  |

|                 | Port Input Select Register 0 Low                                          | Туре      | rw    |              | rw           |            | r            | w          | r            | w          |  |

| 9F <sub>H</sub> | CCU6_PISEL0H Reset: 00 <sub>H</sub><br>Port Input Select Register 0 High  | Bit Field | IST1  | 2HR          | ISP          | OS2        | ISP          | OS1        | ISPOS        |            |  |

|                 |                                                                           | Туре      | n     | w            | rw           |            | rw           |            | rw           |            |  |

| A4 <sub>H</sub> | CCU6_PISEL2 Reset: 00 <sub>H</sub>                                        | Bit Field |       |              | (            | C          |              |            | IST1         | 3HR        |  |

|                 | Port Input Select Register 2                                              | Туре      |       |              |              | r          |              |            | n            | w          |  |

| FA <sub>H</sub> | CCU6_T12L Reset: 00 <sub>H</sub>                                          | Bit Field |       |              |              | T12        | CVL          |            |              |            |  |

|                 | Timer T12 Counter Register Low                                            | Туре      |       |              |              | n          | vh           |            |              |            |  |

| FB <sub>H</sub> | CCU6_T12H Reset: 00 <sub>H</sub>                                          | Bit Field |       |              |              | T12        | CVH          |            |              |            |  |

|                 | Timer T12 Counter Register High                                           | Туре      |       |              |              | n          | vh           |            |              |            |  |

| FC <sub>H</sub> | CCU6_T13L Reset: 00 <sub>H</sub>                                          | Bit Field |       |              |              | T13        | CVL          |            |              |            |  |

|                 | Timer T13 Counter Register Low                                            | Туре      |       |              |              | n          | vh           |            |              |            |  |

| FD <sub>H</sub> | CCU6_T13H Reset: 00 <sub>H</sub>                                          | Bit Field |       |              |              | T13        | CVH          |            |              |            |  |

|                 | Timer T13 Counter Register High                                           | Туре      |       |              |              | n          | vh           |            |              |            |  |

| FE <sub>H</sub> | CCU6_CMPSTATL Reset: 00 <sub>H</sub><br>Compare State Register Low        | Bit Field | 0     | CC63<br>ST   | CCPO<br>S2   | CCPO<br>S1 | CCPO<br>S0   | CC62<br>ST | CC61<br>ST   | CC60<br>ST |  |

|                 |                                                                           | Туре      | r     | rh           | rh           | rh         | rh           | rh         | rh           | rh         |  |

| FF <sub>H</sub> | CCU6_CMPSTATH Reset: 00 <sub>H</sub><br>Compare State Register High       | Bit Field | T13IM | COUT<br>63PS | COUT<br>62PS | CC62<br>PS | COUT<br>61PS | CC61<br>PS | COUT<br>60PS | CC60<br>PS |  |

|                 |                                                                           | Туре      | rwh   | rwh          | rwh          | rwh        | rwh          | rwh        | rwh          | rwh        |  |

The SSC SFRs can be accessed in the standard memory area (RMAP = 0).

# Table 14SSC Register Overview

| Addr            | Register Name                                                               |                        | Bit       | 7  | 6  | 5  | 4  | 3  | 2   | 1   | 0   |

|-----------------|-----------------------------------------------------------------------------|------------------------|-----------|----|----|----|----|----|-----|-----|-----|

| RMAP =          | 0                                                                           |                        | •         |    |    |    |    |    |     |     |     |

| A9 <sub>H</sub> |                                                                             |                        | Bit Field |    |    | 0  |    |    | CIS | SIS | MIS |

|                 | Port Input Select Register                                                  | Туре                   |           |    | r  | rw | rw | rw |     |     |     |

| AA <sub>H</sub> | SSC_CONL Reset: 00 <sub>H</sub><br>Control Register Low<br>Programming Mode | Reset: 00 <sub>H</sub> | Bit Field | LB | PO | PH | HB |    | BM  |     |     |

|                 |                                                                             | Туре                   | rw        | rw | rw | rw | rw |    |     |     |     |

|                 | Operating Mode                                                              |                        | Bit Field | 0  |    |    |    |    | BC  |     |     |

|                 |                                                                             |                        | Туре      | r  |    |    |    | rh |     |     |     |

|                 | SSC_CONH Reset: 00<br>Control Register High | H Bit Field       | EN       | MS | 0 | AREN   | BEN      | PEN | REN | TEN |  |

|-----------------|---------------------------------------------|-------------------|----------|----|---|--------|----------|-----|-----|-----|--|

|                 | Programming Mode                            | Туре              | rw       | rw | r | rw     | rw       | rw  | rw  | rw  |  |

|                 | Operating Mode                              | Bit Field         | EN       | MS | 0 | BSY    | BE       | PE  | RE  | TE  |  |

|                 |                                             | Туре              | rw       | rw | r | rh     | rwh      | rwh | rwh | rwh |  |

| AC <sub>H</sub> | SSC_TBL Reset: 00                           | H Bit Field       |          |    |   | TB_V   | ALUE     |     |     |     |  |

|                 | Transmitter Buffer Register Low             | Туре              | rw       |    |   |        |          |     |     |     |  |

| AD <sub>H</sub> | SSC_RBL Reset: 00                           | H Bit Field       | RB_VALUE |    |   |        |          |     |     |     |  |

|                 | Receiver Buffer Register Low                | Туре              |          |    |   | r      | h        |     |     |     |  |

| AE <sub>H</sub> | SSC_BRL Reset: 00                           |                   |          |    |   | BR_VA  | _UE[7:0] |     |     |     |  |

|                 | Baudrate Timer Reload Register Lo           | <sup>w</sup> Туре |          |    |   | r      | N        |     |     |     |  |

| AF <sub>H</sub> | SSC_BRH Reset: 00                           |                   |          |    |   | BR_VAL | UE[15:8] |     |     |     |  |

|                 | Baudrate Timer Reload Register Hig          | Ih Type           |          |    |   | r      | N        |     |     |     |  |

## Table 14 SSC Register Overview

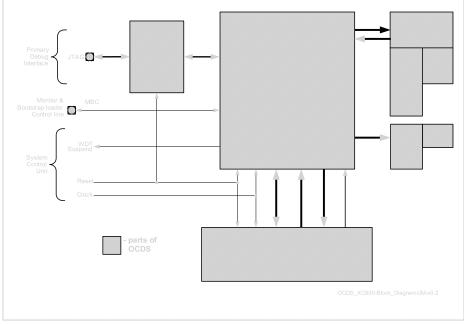

The OCDS SFRs can be accessed in the mapped memory area (RMAP = 1).

# Table 15OCDS Register Overview

| Addr                                       | Register Name                                                                | Bit       | 7           | 6             | 5           | 4             | 3           | 2         | 1          | 0         |  |

|--------------------------------------------|------------------------------------------------------------------------------|-----------|-------------|---------------|-------------|---------------|-------------|-----------|------------|-----------|--|

| RMAP =                                     | 1                                                                            |           | I.          |               |             |               |             |           |            |           |  |

| E9 <sub>H</sub> MMCR2<br>Monitor Mode Cont | MMCR2 Reset: 0U <sub>H</sub><br>Monitor Mode Control Register 2              | Bit Field | EXBC_<br>P  | EXBC          | MBCO<br>N_P | MBCO<br>N     | MMEP<br>_P  | MMEP      | MMOD<br>E  | JENA      |  |

|                                            |                                                                              | Туре      | w           | rw            | w           | rwh           | w           | rwh       | rh         | rh        |  |

| F1 <sub>H</sub>                            | 1 <sub>H</sub> MMCR Reset: 00 <sub>H</sub><br>Monitor Mode Control Register  |           | MEXIT<br>_P | MEXIT         | MSTEP<br>_P | MSTEP         | MRAM<br>S_P | MRAM<br>S | TRF        | RRF       |  |

|                                            |                                                                              | Туре      | w           | rwh           | w           | rw            | w           | rwh       | rh         | rh        |  |

| F2 <sub>H</sub>                            | P <sub>H</sub> MMSR Reset: 00 <sub>H</sub><br>Monitor Mode Status Register   |           | MBCA<br>M   | MBCIN         | EXBF        | SWBF          | HWB3<br>F   | HWB2<br>F | HWB1<br>F  | HWB0<br>F |  |

|                                            |                                                                              | Туре      | rw          | rh            | rwh         | rwh           | rwh         | rwh       | rwh        | rwh       |  |

| F3 <sub>H</sub>                            | 3 <sub>H</sub> MMBPCR Reset: 00 <sub>H</sub><br>BreakPoints Control Register |           | SWBC        | HWB3C HW      |             | B2C HWB1<br>C |             | HWB0C     |            |           |  |

|                                            |                                                                              | Туре      | rw          | r             | rw r        |               | w           | rw        | r          | w         |  |

| F4 <sub>H</sub>                            | MMICR Reset: 00 <sub>H</sub><br>Monitor Mode Interrupt Control Register      | Bit Field | DVECT       | DRETR         | (           | Ċ             | MMUIE<br>_P | MMUIE     | RRIE_<br>P | RRIE      |  |

|                                            |                                                                              | Туре      | rwh         | rwh           |             | r             | w           | rw        | w          | rw        |  |

| F5 <sub>H</sub>                            | MMDR Reset: 00 <sub>H</sub><br>Monitor Mode Data Register                    | Bit Field | MMRR        |               |             |               |             |           |            |           |  |

|                                            | Receive                                                                      | Туре      | rh          |               |             |               |             |           |            |           |  |

|                                            | Transmit                                                                     | Bit Field | MMTR        |               |             |               |             |           |            |           |  |

|                                            |                                                                              | Туре      | w           |               |             |               |             |           |            |           |  |

| F6 <sub>H</sub>                            | HWBPSR Reset: 00 <sub>H</sub><br>Hardware Breakpoints Select Register        | Bit Field |             | 0 BPSEL<br>_P |             |               | BPSEL       |           |            |           |  |

|                                            |                                                                              | Туре      | r w         |               |             |               |             | rw        |            |           |  |

| F7 <sub>H</sub>                            | HWBPDR Reset: 00 <sub>H</sub>                                                | Bit Field |             |               |             | HW            | BPxx        |           |            |           |  |

|                                            | Hardware Breakpoints Data Register                                           | Туре      | rw          |               |             |               |             |           |            |           |  |

# XC866

# **Functional Description**

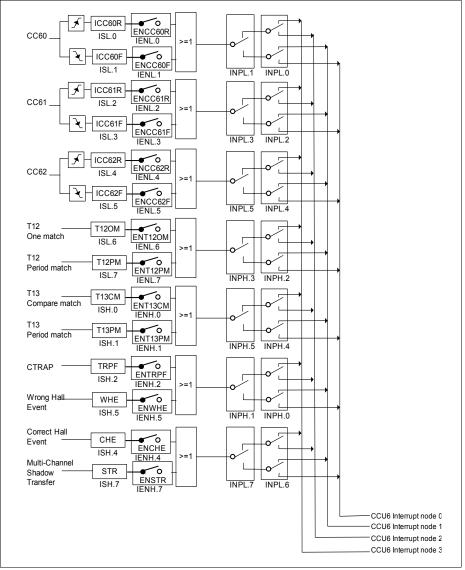

## Figure 17 Interrupt Request Sources (Part 4)

# 3.4.3 Interrupt Priority

Each interrupt source, except for NMI, can be individually programmed to one of the four possible priority levels. The NMI has the highest priority and supersedes all other interrupts. Two pairs of interrupt priority registers (IP and IPH, IP1 and IPH1) are available to program the priority level of each non-NMI interrupt vector.

A low-priority interrupt can be interrupted by a high-priority interrupt, but not by another interrupt of the same or lower priority. Further, an interrupt of the highest priority cannot be interrupted by any other interrupt source.

If two or more requests of different priority levels are received simultaneously, the request of the highest priority is serviced first. If requests of the same priority are received simultaneously, then an internal polling sequence determines which request is serviced first. Thus, within each priority level, there is a second priority structure determined by the polling sequence shown in **Table 18**.

| Source                                      | Level     |

|---------------------------------------------|-----------|

| Non-Maskable Interrupt (NMI)                | (highest) |

| External Interrupt 0                        | 1         |

| Timer 0 Interrupt                           | 2         |

| External Interrupt 1                        | 3         |

| Timer 1 Interrupt                           | 4         |

| UART Interrupt                              | 5         |

| Timer 2, Fractional Divider, LIN Interrupts | 6         |

| ADC Interrupt                               | 7         |

| SSC Interrupt                               | 8         |

| External Interrupt 2                        | 9         |

| External Interrupt [6:3]                    | 10        |

| CCU6 Interrupt Node Pointer 0               | 11        |

| CCU6 Interrupt Node Pointer 1               | 12        |

| CCU6 Interrupt Node Pointer 2               | 13        |

| CCU6 Interrupt Node Pointer 3               | 14        |

Table 18

Priority Structure within Interrupt Level

# 3.7 Reset Control

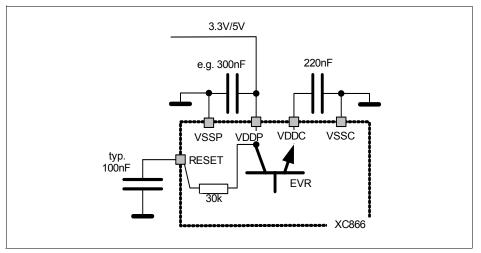

The XC866 has five types of reset: power-on reset, hardware reset, watchdog timer reset, power-down wake-up reset, and brownout reset.

When the XC866 is first powered up, the status of certain pins (see **Table 20**) must be defined to ensure proper start operation of the device. At the end of a reset sequence, the sampled values are latched to select the desired boot option, which cannot be modified until the next power-on reset or hardware reset. This guarantees stable conditions during the normal operation of the device.

In order to power up the system properly, the external reset pin  $\overrightarrow{\text{RESET}}$  must be asserted until  $V_{\text{DDC}}$  reaches  $0.9^* V_{\text{DDC}}$ . The delay of external reset can be realized by an external capacitor at  $\overrightarrow{\text{RESET}}$  pin. This capacitor value must be selected so that  $V_{\text{RESET}}$  reaches 0.4 V, but not before  $V_{\text{DDC}}$  reaches 0.9\*  $V_{\text{DDC}}$ .

A typical application example is shown in **Figure 21**.  $V_{DDP}$  capacitor value is 300 nF.  $V_{DDC}$  capacitor value is 220 nF. The capacitor connected to RESET pin is 100 nF.

Typically, the time taken for  $V_{DDC}$  to reach  $0.9^*V_{DDC}$  is less than 50 µs once  $V_{DDP}$  reaches 2.3V. Hence, based on the condition that 10% to 90%  $V_{DDP}$  (slew rate) is less than 500 µs, the RESET pin should be held low for 500 µs typically. See **Figure 22**.

XC866

# 3.11.1 Baud-Rate Generator

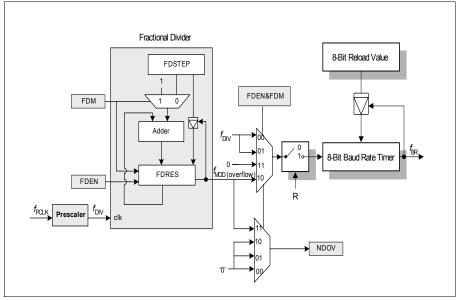

The baud-rate generator is based on a programmable 8-bit reload value, and includes divider stages (i.e., prescaler and fractional divider) for generating a wide range of baud rates based on its input clock  $f_{PCLK}$ , see **Figure 29**.

#### Figure 29 Baud-rate Generator Circuitry

The baud rate timer is a count-down timer and is clocked by either the output of the fractional divider ( $f_{MOD}$ ) if the fractional divider is enabled (FDCON.FDEN = 1), or the output of the prescaler ( $f_{DIV}$ ) if the fractional divider is disabled (FDEN = 0). For baud rate generation, the fractional divider must be configured to fractional divider mode (FDCON.FDM = 0). This allows the baud rate control run bit BCON.R to be used to start or stop the baud rate timer. At each timer underflow, the timer is reloaded with the 8-bit reload value in register BG and one clock pulse is generated for the serial channel.

Enabling the fractional divider in normal divider mode (FDEN = 1 and FDM = 1) stops the baud rate timer and nullifies the effect of bit BCON.R. See **Section 3.12**.

The baud rate  $(f_{BR})$  value is dependent on the following parameters:

- Input clock f<sub>PCLK</sub>

- Prescaling factor (2<sup>BRPRE</sup>) defined by bit field BRPRE in register BCON

- Fractional divider (STEP/256) defined by register FDSTEP (to be considered only if fractional divider is enabled and operating in fractional divider mode)

# 3.16 Timer 2

Timer 2 Modes

Table 29

Timer 2 is a 16-bit general purpose timer (THL2) that has two modes of operation, a 16-bit auto-reload mode and a 16-bit one channel capture mode. If the prescalar is disabled, Timer 2 counts with an input clock of PCLK/12. Timer 2 continues counting as long as it is enabled.

| Table 29           | Timer 2 wodes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mode               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Auto-reload        | <ul> <li>Up/Down Count Disabled</li> <li>Count up only</li> <li>Start counting from 16-bit reload value, overflow at FFFF<sub>H</sub></li> <li>Reload event configurable for trigger by overflow condition only, or by negative/positive edge at input pin T2EX as well</li> <li>Programmble reload value in register RC2</li> <li>Interrupt is generated with reload event</li> </ul>                                                                                                                                                                                                                                       |

|                    | <ul> <li>Up/Down Count Enabled</li> <li>Count up or down, direction determined by level at input pin T2EX</li> <li>No interrupt is generated</li> <li>Count up <ul> <li>Start counting from 16-bit reload value, overflow at FFF<sub>H</sub></li> <li>Reload event triggered by overflow condition</li> <li>Programmble reload value in register RC2</li> </ul> </li> <li>Count down <ul> <li>Start counting from FFF<sub>H</sub>, underflow at value defined in register RC2</li> <li>Reload event triggered by underflow condition <ul> <li>Reload event triggered by underflow condition</li> </ul> </li> </ul></li></ul> |

| Channel<br>capture | <ul> <li>Count up only</li> <li>Start counting from 0000<sub>H</sub>, overflow at FFFF<sub>H</sub></li> <li>Reload event triggered by overflow condition</li> <li>Reload value fixed at 0000<sub>H</sub></li> <li>Capture event triggered by falling/rising edge at pin T2EX</li> <li>Captured timer value stored in register RC2</li> <li>Interrupt is generated with reload or capture event</li> </ul>                                                                                                                                                                                                                    |

# 3.19.1 JTAG ID Register

This is a read-only register located inside the JTAG module, and is used to recognize the device(s) connected to the JTAG interface. Its content is shifted out when INSTRUCTION register contains the IDCODE command (opcode  $04_H$ ), and the same is also true immediately after reset.

The JTAG ID register contents for the XC866 devices are given in Table 31.

| Device Type | Device Name | JTAG ID                |  |

|-------------|-------------|------------------------|--|

| Flash       | XC866L-4FR  | 1010 0083 <sub>H</sub> |  |

|             | XC866-4FR   | 100F 5083 <sub>H</sub> |  |

|             | XC866L-2FR  | 1010 2083 <sub>H</sub> |  |

|             | XC866-2FR   | 1010 1083 <sub>H</sub> |  |

|             | XC866L-1FR  | 1013 8083 <sub>H</sub> |  |

|             | XC866-1FR   | 1013 8083 <sub>H</sub> |  |

### Table 31JTAG ID Summary

| ROM | XC866L-4RR | 1013 9083 <sub>H</sub> |

|-----|------------|------------------------|

|     | XC866-4RR  | 1013 9083 <sub>H</sub> |

|     | XC866L-2RR | 1013 9083 <sub>H</sub> |

|     | XC866-2RR  | 1013 9083 <sub>H</sub> |

# 3.20 Identification Register

The XC866 identity register is located at Page 1 of address B3<sub>H</sub>.

# ID

# **Identity Register**

### Reset Value: 0000 0010<sub>B</sub>

| 7 | 6 | 5      | 4 | 3 | 2 | 1     | 0 |

|---|---|--------|---|---|---|-------|---|

|   | Ι | PRODID | I | I |   | VERID | I |

|   | 1 | r      | 1 | I |   | r     | L |

| Field  | Bits  | Туре | Description                      |

|--------|-------|------|----------------------------------|

| VERID  | [2:0] | r    | Version ID<br>010 <sub>B</sub>   |

| PRODID | [7:3] | r    | Product ID<br>00000 <sub>B</sub> |

### **Electrical Parameters**

# Table 36ADC Characteristics (Operating Conditions apply; $V_{DDP}$ = 5V Range)

| Parameter                                                  | Symbol                   | Li   | mit Valu | es   | Unit | Test Conditions/ |  |

|------------------------------------------------------------|--------------------------|------|----------|------|------|------------------|--|

|                                                            |                          | min. | typ.     | max. |      | Remarks          |  |

| Switched<br>capacitance at the<br>analog voltage<br>inputs | C <sub>AINSW</sub><br>CC | _    | 5        | 7    | pF   | 2)4)             |  |

| Input resistance of the reference input                    | R <sub>AREF</sub> CC     | -    | 1        | 2    | kΩ   | 2)               |  |

| Input resistance of the selected analog channel            | R <sub>AIN</sub> CC      | -    | 1        | 1.5  | kΩ   | 2)               |  |

<sup>1)</sup> TUE is tested at  $V_{AREF}$  = 5.0 V,  $V_{AGND}$  = 0 V ,  $V_{DDP}$  = 5.0 V.

<sup>2)</sup> Not subject to production test, verified by design/characterization.

<sup>&</sup>lt;sup>3)</sup> This represents an equivalent switched capacitance. This capacitance is not switched to the reference voltage at once. Instead of this, smaller capacitances are successively switched to the reference voltage.

<sup>&</sup>lt;sup>4)</sup> The sampling capacity of the conversion C-Network is pre-charged to V<sub>AREF</sub>/2 before connecting the input to the C-Network. Because of the parasitic elements, the voltage measured at ANx is lower than V<sub>AREF</sub>/2.

### **Electrical Parameters**

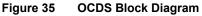

# 4.3.2 Output Rise/Fall Times

# Table 41 Output Rise/Fall Times Parameters (Operating Conditions apply)

| Parameter                     | Symbol                          | Limit<br>Values |           | Unit | Test Conditions      |  |

|-------------------------------|---------------------------------|-----------------|-----------|------|----------------------|--|

|                               |                                 | min.            | nin. max. |      |                      |  |

| V <sub>DDP</sub> = 5V Range   |                                 |                 |           |      |                      |  |

| Rise/fall times 1) 2)         | t <sub>R</sub> , t <sub>F</sub> | -               | 10        | ns   | 20 pF. <sup>3)</sup> |  |

| V <sub>DDP</sub> = 3.3V Range |                                 |                 |           |      |                      |  |

| Rise/fall times 1) 2)         | t <sub>R</sub> , t <sub>F</sub> | -               | 10        | ns   | 20 pF. <sup>4)</sup> |  |

<sup>1)</sup> Rise/Fall time measurements are taken with 10% - 90% of the pad supply.

<sup>2)</sup> Not all parameters are 100% tested, but are verified by design/characterization and test correlation.

<sup>3)</sup> Additional rise/fall time valid for  $C_L = 20pF - 100pF @ 0.125 ns/pF$ .

<sup>4)</sup> Additional rise/fall time valid for  $C_L = 20pF - 100pF @ 0.225 ns/pF$ .

Figure 41 Rise/Fall Times Parameters

### **Electrical Parameters**

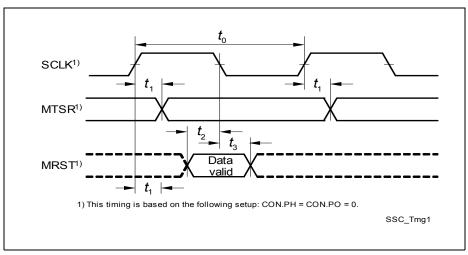

# 4.3.6 SSC Master Mode Timing

# Table 46 SSC Master Mode Timing (Operating Conditions apply; C<sub>L</sub> = 50 pF)

| Parameter              | Syn                   | nbol | Limit                 | Unit |    |

|------------------------|-----------------------|------|-----------------------|------|----|

|                        |                       |      | min.                  | max. |    |

| SCLK clock period      | <i>t</i> <sub>0</sub> | CC   | 2*T <sub>SSC</sub> 1) | _    | ns |

| MTSR delay from SCLK _ | <i>t</i> <sub>1</sub> | CC   | 0                     | 8    | ns |

| MRST setup to SCLK ٦   | <i>t</i> <sub>2</sub> | SR   | 22                    | _    | ns |

| MRST hold from SCLK ٦  | $t_3$                 | SR   | 0                     | -    | ns |

<sup>1)</sup>  $T_{SSCmin} = T_{CPU} = 1/f_{CPU}$ . When  $f_{CPU} = 26.7$ MHz,  $t_0 = 74.9$ ns.  $T_{CPU}$  is the CPU clock period.

Figure 45 SSC Master Mode Timing