Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xc8662fribekxuma1 |

|----------------------------|------------------------------------------------------------------------------|

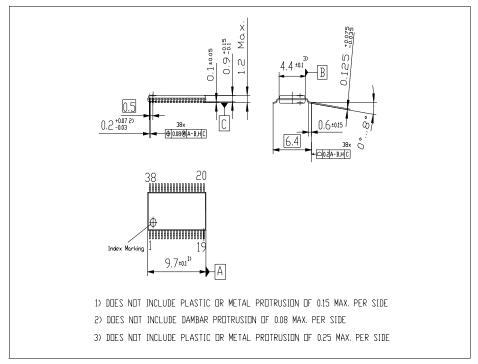

| Supplier Device Package    | PG-TSSOP-38                                                                  |

| Package / Case             | 38-TFSOP (0.173", 4.40mm Width)                                              |

| Mounting Type              | Surface Mount                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                           |

| Oscillator Type            | Internal                                                                     |

| Data Converters            | A/D 8x10b                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                  |

| RAM Size                   | 768 x 8                                                                      |

| EEPROM Size                | -                                                                            |

| Program Memory Type        | FLASH                                                                        |

| Program Memory Size        | 8KB (8K x 8)                                                                 |

| Number of I/O              | 19                                                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Connectivity               | SSI, UART/USART                                                              |

| Speed                      | 86MHz                                                                        |

| Core Size                  | 8-Bit                                                                        |

| Core Processor             | XC800                                                                        |

| Product Status             | Last Time Buy                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

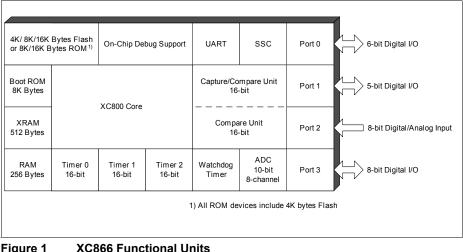

## 8-Bit Single-Chip Microcontroller XC800 Family

#### 1 **Summary of Features**

- High-performance XC800 Core •

- compatible with standard 8051 processor

- two clocks per machine cycle architecture (for memory access without wait state)

- two data pointers

- On-chip memory

- 8 Kbytes of Boot ROM

- 256 bytes of RAM

- 512 bytes of XRAM

- 4/8/16 Kbytes of Flash; or 8/16 Kbytes of ROM, with additional 4 Kbytes of Flash (includes memory protection strategy)

- I/O port supply at 3.3 V/5.0 V and core logic supply at 2.5 V (generated by embedded voltage regulator)

(further features are on next page)

# **General Device Information**

# 2.4 Pin Definitions and Functions

İnfineon

## Table 3 Pin Definitions and Functions

| Symbol | Pin<br>Number | Туре | Reset<br>State | Function                            |                                                                                                                            |

|--------|---------------|------|----------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| P0     |               | I/O  |                | port. It can b                      | -bit bidirectional general purpose I/O<br>be used as alternate functions for the<br>6, UART, and the SSC.                  |

| P0.0   | 12            |      | Hi-Z           | TCK_0<br>T12HR_1                    | JTAG Clock Input<br>CCU6 Timer 12 Hardware Run<br>Input                                                                    |

|        |               |      |                | CC61_1<br>CLKOUT<br>RXDO_1          | Input/Output of Capture/Compare<br>channel 1<br>Clock Output<br>UART Transmit Data Output                                  |

| P0.1   | 14            |      | Hi-Z           | TDI_0<br>T13HR_1                    | JTAG Serial Data Input<br>CCU6 Timer 13 Hardware Run<br>Input                                                              |

|        |               |      |                | RXD_1<br>COUT61_1                   | UART Receive Data Input                                                                                                    |

| P0.2   | 13            |      | PU             | EXF2_1<br>CTRAP_2<br>TDO_0<br>TXD_1 | Timer 2 External Flag Output<br>CCU6 Trap Input<br>JTAG Serial Data Output<br>UART Transmit Data Output/<br>Clock Output   |

| P0.3   | 2             |      | Hi-Z           | SCK_1<br>COUT63_1                   | SSC Clock Input/Output<br>Output of Capture/Compare<br>channel 3                                                           |

| P0.4   | 3             |      | Hi-Z           | MTSR_1<br>CC62_1                    | SSC Master Transmit Output/<br>Slave Receive Input<br>Input/Output of Capture/Compare<br>channel 2                         |

| P0.5   | 4             |      | Hi-Z           | MRST_1<br>EXINT0_0<br>COUT62_1      | SSC Master Receive Input/<br>Slave Transmit Output<br>External Interrupt Input 0<br>Output of Capture/Compare<br>channel 2 |

## 3.2.2 Special Function Register

The Special Function Registers (SFRs) occupy direct internal data memory space in the range  $80_H$  to FF<sub>H</sub>. All registers, except the program counter, reside in the SFR area. The SFRs include pointers and registers that provide an interface between the CPU and the on-chip peripherals. As the 128-SFR range is less than the total number of registers required, address extension mechanisms are required to increase the number of addressable SFRs. The address extension mechanisms include:

- Mapping

- Paging

## 3.2.2.1 Address Extension by Mapping

Address extension is performed at the system level by mapping. The SFR area is extended into two portions: the standard (non-mapped) SFR area and the mapped SFR area. Each portion supports the same address range  $80_H$  to FF<sub>H</sub>, bringing the number of addressable SFRs to 256. The extended address range is not directly controlled by the CPU instruction itself, but is derived from bit RMAP in the system control register SYSCON0 at address  $8F_H$ . To access SFRs in the mapped area, bit RMAP in SFR SYSCON0 must be set. Alternatively, the SFRs in the standard area can be accessed by clearing bit RMAP. The SFR area can be selected as shown in **Figure 8**.

#### SYSCON0 System Control Register 0 Reset Value: 00<sub>H</sub> 2 1 0 7 6 5 4 3 0 1 0 RMAP r rw r rw

| Field | Bits    | Туре | Description                                                                                                                                                               |

|-------|---------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RMAP  | 0       | rw   | <ul> <li>Special Function Register Map Control</li> <li>The access to the standard SFR area is enabled.</li> <li>The access to the mapped SFR area is enabled.</li> </ul> |

| 1     | 2       | rw   | <b>Reserved</b><br>Returns the last value if read; should be written<br>with 1.                                                                                           |

| 0     | 1,[7:3] | r    | <b>Reserved</b><br>Returns 0 if read; should be written with 0.                                                                                                           |

#### Table 13 CCU6 Register Overview (cont'd)

| Addr            | Register Name                                                                               | Bit               | 7              | 6                 | 5           | 4           | 3           | 2           | 1           | 0           |  |

|-----------------|---------------------------------------------------------------------------------------------|-------------------|----------------|-------------------|-------------|-------------|-------------|-------------|-------------|-------------|--|

| FD <sub>H</sub> | CCU6_CC61RH Reset: 00 <sub>H</sub><br>Capture/Compare Register for Channel                  | Bit Field         |                | CC61VH            |             |             |             |             |             |             |  |

|                 | CC61 High                                                                                   | Туре              | rh             |                   |             |             |             |             |             |             |  |

| FE <sub>H</sub> | CCU6_CC62RL Reset: 00 <sub>H</sub><br>Capture/Compare Register for Channel                  | Bit Field         | CC62VL         |                   |             |             |             |             |             |             |  |

|                 | CC62 Low                                                                                    | Туре              |                |                   |             | r           | 'n          |             |             |             |  |

| FF <sub>H</sub> | CCU6_CC62RH Reset: 00 <sub>H</sub><br>Capture/Compare Register for Channel                  | Bit Field         |                |                   |             | CCE         | 62VH        |             |             |             |  |

|                 | CC62 High                                                                                   | Туре              |                |                   |             | r           | 'n          |             |             |             |  |

|                 | 0, Page 2                                                                                   | 1                 |                |                   |             |             |             |             |             |             |  |

| 9A <sub>H</sub> | CCU6_T12MSELL Reset: 00 <sub>H</sub><br>T12 Capture/Compare Mode Select<br>Register Low     | Bit Field         |                |                   | EL61        |             |             |             | EL60        |             |  |

|                 | •                                                                                           | Туре              | 5510           | r                 | W           |             |             |             | W           |             |  |

| 9B <sub>H</sub> | CCU6_T12MSELH Reset: 00 <sub>H</sub><br>T12 Capture/Compare Mode Select<br>Register High    | Bit Field         | DBYP           |                   | HSYNC       |             |             |             | EL62        |             |  |

|                 |                                                                                             | Туре              | rw             | ENT 10            | rw          | FNOO        | ENICO       |             | W           | ENGO        |  |

| 9C <sub>H</sub> | CCU6_IENL Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Enable<br>Register Low        | Bit Field         | ENT12<br>PM    | ENT12<br>OM       | ENCC<br>62F | ENCC<br>62R | ENCC<br>61F | ENCC<br>61R | ENCC<br>60F | ENCC<br>60R |  |

|                 | •                                                                                           | Туре              | rw             | rw                | rw          | rw          | rw          | rw          | rw          | rw          |  |

| 9D <sub>H</sub> | CCU6_IENH Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Enable<br>Register High       | Bit Field         | ENSTR          | EN<br>IDLE        | EN<br>WHE   | EN<br>CHE   | 0           | EN<br>TRPF  | ENT13<br>PM | ENT13<br>CM |  |

| 05              |                                                                                             | Type              | rw             | rw                | rw          | rw          | r           | rw<br>CC61  | rw          | rw          |  |

| 9E <sub>H</sub> | CCU6_INPL Reset: 40 <sub>H</sub><br>Capture/Compare Interrupt Node<br>Pointer Register Low  | Bit Field         | INPCHE INPCC62 |                   |             |             | CC60        |             |             |             |  |

| 05              | ÷                                                                                           | Type<br>Bit Field |                | rw rw<br>0 INPT13 |             |             |             |             |             |             |  |

| 9F <sub>H</sub> | CCU6_INPH Reset: 39 <sub>H</sub><br>Capture/Compare Interrupt Node<br>Pointer Register High | Type              |                | r                 | INPT IS     |             | rw          |             | INPERR      |             |  |

| A4 <sub>H</sub> | CCU6_ISSL Reset: 00 <sub>H</sub>                                                            | Bit Field         | ST12P          | ST120             |             | SCC62       |             | SCC61       |             | SCC60       |  |

|                 | Capture/Compare Interrupt Status Set<br>Register Low                                        | Туре              | M              | M                 | F           | R           | F           | R           | F           | R           |  |

| A5 <sub>H</sub> | CCU6_ISSH Reset: 00 <sub>H</sub>                                                            | Bit Field         | SSTR           | SIDLE             | SWHE        | SCHE        |             |             | ST13        | ST13        |  |

| AJH             | Capture/Compare Interrupt Status Set<br>Register High                                       | Туре              | w              | W                 | w           | w           | w           | w           | PM          | CM          |  |

| A6 <sub>H</sub> | CCU6 PSLR Reset: 00 <sub>H</sub>                                                            | Bit Field         | PSL63          | 0                 | vv          | vv          |             | SL          | vv          | vv          |  |

| A0H             | Passive State Level Register                                                                | Туре              | rwh            | r                 |             |             |             | vh          |             |             |  |

| A7 <sub>H</sub> | CCU6_MCMCTR Reset: 00 <sub>H</sub>                                                          | Bit Field         |                | )                 | SW          | SYN         | 0           |             | SWSEL       |             |  |

|                 | Multi-Channel Mode Control Register                                                         | Туре              |                | r                 | r           | w           | r           |             | rw          |             |  |

| FA <sub>H</sub> | CCU6_TCTR2L Reset: 00 <sub>H</sub><br>Timer Control Register 2 Low                          | Bit Field         | 0              | T13               | TED         |             | T13TEC      | ;           | T13<br>SSC  | T12<br>SSC  |  |

|                 |                                                                                             | Туре              | r              | r                 | w           |             | rw          |             | rw          | rw          |  |

| FB <sub>H</sub> | CCU6_TCTR2H Reset: 00 <sub>H</sub>                                                          | Bit Field         |                |                   | 0           |             | T13F        | RSEL        | T12         | RSEL        |  |

|                 | Timer Control Register 2 High                                                               | Туре              |                |                   | r           |             |             | w           | r           | w           |  |

| FC <sub>H</sub> | CCU6_MODCTRL Reset: 00 <sub>H</sub><br>Modulation Control Register Low                      | Bit Field         | MC<br>MEN      | 0                 |             | T12MODEN    |             |             |             |             |  |

|                 |                                                                                             | Туре              | rw             | r                 |             |             |             | w           |             |             |  |

| FD <sub>H</sub> | CCU6_MODCTRH Reset: 00 <sub>H</sub><br>Modulation Control Register High                     | Bit Field         | ECT13<br>O     | 0                 |             |             | T13M        | ODEN        |             |             |  |

|                 |                                                                                             | Туре              | rw             | r                 |             |             |             |             |             |             |  |

| FE <sub>H</sub> | CCU6_TRPCTRL Reset: 00 <sub>H</sub><br>Trap Control Register Low                            | Bit Field         |                |                   | 0           |             |             |             | TRPM1       | -           |  |

|                 | Trap Control Register Low                                                                   | Туре              |                |                   | r           |             |             | rw          | rw          | rw          |  |

#### Table 13 CCU6 Register Overview (cont'd)

| Addr            | Register Name                                                             | Bit       | 7         | 6              | 5            | 4          | 3            | 2          | 1            | 0          |  |

|-----------------|---------------------------------------------------------------------------|-----------|-----------|----------------|--------------|------------|--------------|------------|--------------|------------|--|

| FF <sub>H</sub> | CCU6_TRPCTRH Reset: 00 <sub>H</sub>                                       | Bit Field |           | TRPEN TRPEN    |              |            |              |            |              |            |  |

|                 | Trap Control Register High                                                |           | N         | 13             |              |            |              |            |              |            |  |

|                 |                                                                           | Туре      | rw        | rw             |              |            | r            | w          |              |            |  |

| RMAP =          | 0, Page 3                                                                 |           |           |                |              |            |              |            |              |            |  |

| 9A <sub>H</sub> | CCU6_MCMOUTL Reset: 00 <sub>H</sub><br>Multi-Channel Mode Output Register | Bit Field | 0         | R              |              |            | MC           | MP         |              |            |  |

|                 | Low                                                                       | Туре      | r         | rh             |              |            | r            | h          |              |            |  |

| 9B <sub>H</sub> | CCU6_MCMOUTH Reset: 00 <sub>H</sub><br>Multi-Channel Mode Output Register | Bit Field | (         | )              |              | CURH       |              |            | EXPH         |            |  |

|                 | High                                                                      | Туре      | 1         | r              |              | rh         |              |            | rh           |            |  |

| 9C <sub>H</sub> | CCU6_ISL Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Status       | Bit Field | T12PM     | T12OM          | ICC62F       | R          | ICC61F       | R          | ICC60F       | ICC60<br>R |  |

|                 | Register Low                                                              | Туре      | rh        | rh             | rh           | rh         | rh           | rh         | rh           | rh         |  |

| 9D <sub>H</sub> | CCU6_ISH Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Status       | Bit Field | STR       | IDLE           | WHE          | CHE        | TRPS         | TRPF       | T13PM        | T13CM      |  |

|                 | Register High                                                             | Туре      | rh        | rh             | rh           | rh         | rh           | rh         | rh           | rh         |  |

| 9E <sub>H</sub> | CCU6_PISEL0L Reset: 00 <sub>H</sub>                                       | Bit Field | ISTRP     |                | ISCC62 ISC   |            | C61 ISCC60   |            | C60          |            |  |

|                 | Port Input Select Register 0 Low                                          | Туре      | rw rw     |                |              | r          | rw rw        |            |              |            |  |

| 9F <sub>H</sub> | CCU6_PISEL0H Reset: 00 <sub>H</sub><br>Port Input Select Register 0 High  | Bit Field | IST1      | IST12HR ISPOS2 |              | ISPOS1     |              | ISPOS0     |              |            |  |

|                 |                                                                           | Туре      | rw rw rw  |                |              |            |              | rw         |              |            |  |

| A4 <sub>H</sub> | CCU6_PISEL2 Reset: 00 <sub>H</sub>                                        | Bit Field | 0 IST13HF |                |              |            |              |            | 3HR          |            |  |

|                 | Port Input Select Register 2                                              | Туре      | r rw      |                |              |            |              |            |              | w          |  |

| FA <sub>H</sub> | CCU6_T12L Reset: 00 <sub>H</sub>                                          | Bit Field | T12CVL    |                |              |            |              |            |              |            |  |

|                 | Timer T12 Counter Register Low                                            | Туре      | rwh       |                |              |            |              |            |              |            |  |

| FB <sub>H</sub> | CCU6_T12H Reset: 00 <sub>H</sub>                                          | Bit Field |           |                |              | T12        | CVH          |            |              |            |  |

|                 | Timer T12 Counter Register High                                           | Туре      | rwh       |                |              |            |              |            |              |            |  |

| FC <sub>H</sub> | CCU6_T13L Reset: 00 <sub>H</sub>                                          | Bit Field |           |                |              | T13        | CVL          |            |              |            |  |

|                 | Timer T13 Counter Register Low                                            | Туре      |           |                |              | n          | vh           |            |              |            |  |

| FD <sub>H</sub> | CCU6_T13H Reset: 00 <sub>H</sub>                                          | Bit Field |           |                |              | T13        | CVH          |            |              |            |  |

|                 | Timer T13 Counter Register High                                           | Туре      |           |                |              | n          | vh           |            |              |            |  |

| FE <sub>H</sub> | CCU6_CMPSTATL Reset: 00 <sub>H</sub><br>Compare State Register Low        | Bit Field | 0         | CC63<br>ST     | CCPO<br>S2   | CCPO<br>S1 | CCPO<br>S0   | CC62<br>ST | CC61<br>ST   | CC60<br>ST |  |

|                 |                                                                           | Туре      | r         | rh             | rh           | rh         | rh           | rh         | rh           | rh         |  |

| FF <sub>H</sub> | CCU6_CMPSTATH Reset: 00 <sub>H</sub><br>Compare State Register High       | Bit Field | T13IM     | COUT<br>63PS   | COUT<br>62PS | CC62<br>PS | COUT<br>61PS | CC61<br>PS | COUT<br>60PS | CC60<br>PS |  |

|                 |                                                                           | Туре      | rwh       | rwh            | rwh          | rwh        | rwh          | rwh        | rwh          | rwh        |  |

The SSC SFRs can be accessed in the standard memory area (RMAP = 0).

## Table 14SSC Register Overview

| Addr            | Register Name                                                  |                        | Bit       | 7  | 6  | 5  | 4  | 3  | 2   | 1   | 0   |

|-----------------|----------------------------------------------------------------|------------------------|-----------|----|----|----|----|----|-----|-----|-----|

| RMAP =          | 0                                                              |                        | •         |    |    |    |    |    |     |     |     |

| A9 <sub>H</sub> | SSC_PISEL Reset: 00 <sub>H</sub><br>Port Input Select Register |                        | Bit Field |    |    | 0  |    |    | CIS | SIS | MIS |

|                 |                                                                |                        | Туре      |    |    | r  |    |    | rw  | rw  | rw  |

| AA <sub>H</sub> | SSC_CONL                                                       | Reset: 00 <sub>H</sub> | Bit Field | LB | PO | PH | HB |    | В   | М   |     |

|                 | Control Register Low<br>Programming Mode                       |                        | Туре      | rw | rw | rw | rw |    | r   | w   |     |

| Operating Mode  |                                                                |                        | Bit Field |    | 0  |    |    | BC |     |     |     |

|                 |                                                                |                        | Туре      |    |    | r  |    |    | r   | h   |     |

## 3.4.2 Interrupt Source and Vector

Each interrupt source has an associated interrupt vector address. This vector is accessed to service the corresponding interrupt source request. The interrupt service of each interrupt source can be individually enabled or disabled via an enable bit. The assignment of the XC866 interrupt sources to the interrupt vector addresses and the corresponding interrupt source enable bits are summarized in **Table 17**.

| Interrupt<br>Source |                   |                                                 | Enable Bit | SFR    |

|---------------------|-------------------|-------------------------------------------------|------------|--------|

| NMI                 | 0073 <sub>H</sub> | 073 <sub>H</sub> Watchdog Timer NMI             |            | NMICON |

|                     |                   | PLL NMI                                         | NMIPLL     |        |

|                     |                   | Flash NMI                                       | NMIFLASH   |        |

|                     |                   | VDDC Prewarning NMI                             | NMIVDD     |        |

|                     |                   | VDDP Prewarning NMI                             | NMIVDDP    |        |

|                     |                   | Flash ECC NMI                                   | NMIECC     |        |

| XINTR0              | 0003 <sub>H</sub> | External Interrupt 0                            | EX0        | IEN0   |

| XINTR1              | 000B <sub>H</sub> | Timer 0                                         | ET0        |        |

| XINTR2              | 0013 <sub>H</sub> | External Interrupt 1                            | EX1        |        |

| XINTR3              | 001B <sub>H</sub> | Timer 1                                         | ET1        |        |

| XINTR4              | 0023 <sub>H</sub> | UART                                            | ES         |        |

| XINTR5              | 002B <sub>H</sub> | T2                                              | ET2        |        |

|                     |                   | Fractional Divider<br>(Normal Divider Overflow) |            |        |

|                     |                   | LIN                                             |            |        |

#### Table 17 Interrupt Vector Addresses

| XINTR6  | 0033 <sub>H</sub> | ADC                  | EADC   | IEN1 |

|---------|-------------------|----------------------|--------|------|

| XINTR7  | 003B <sub>H</sub> | SSC                  | ESSC   |      |

| XINTR8  | 0043 <sub>H</sub> | External Interrupt 2 | EX2    |      |

| XINTR9  | 004B <sub>H</sub> | External Interrupt 3 | EXM    |      |

|         |                   | External Interrupt 4 |        |      |

|         |                   | External Interrupt 5 |        |      |

|         |                   | External Interrupt 6 |        |      |

| XINTR10 | 0053 <sub>H</sub> | CCU6 INP0            | ECCIP0 |      |

| XINTR11 | 005B <sub>H</sub> | CCU6 INP1            | ECCIP1 |      |

| XINTR12 | 0063 <sub>H</sub> | CCU6 INP2            | ECCIP2 |      |

| XINTR13 | 006B <sub>H</sub> | CCU6 INP3            | ECCIP3 |      |

## Table 17 Interrupt Vector Addresses (cont'd)

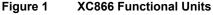

## 3.6 Power Supply System with Embedded Voltage Regulator

The XC866 microcontroller requires two different levels of power supply:

- 3.3 V or 5.0 V for the Embedded Voltage Regulator (EVR) and Ports

- · 2.5 V for the core, memory, on-chip oscillator, and peripherals

**Figure 20** shows the XC866 power supply system. A power supply of 3.3 V or 5.0 V must be provided from the external power supply pin. The 2.5 V power supply for the logic is generated by the EVR. The EVR helps to reduce the power consumption of the whole chip and the complexity of the application board design.

The EVR consists of a main voltage regulator and a low power voltage regulator. In active mode, both voltage regulators are enabled. In power-down mode, the main voltage regulator is switched off, while the low power voltage regulator continues to function and provide power supply to the system with low power consumption.

Figure 20 XC866 Power Supply System

## EVR Features:

- Input voltage (V<sub>DDP</sub>): 3.3 V/5.0 V

- Output voltage (V<sub>DDC</sub>): 2.5 V ± 7.5%

- · Low power voltage regulator provided in power-down mode

- V<sub>DDC</sub> and V<sub>DDP</sub> prewarning detection

- V<sub>DDC</sub> brownout detection

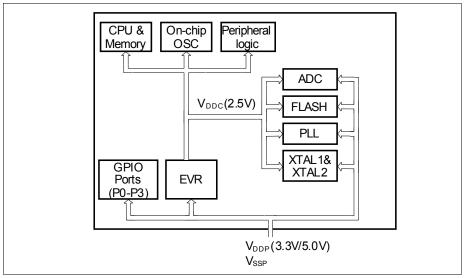

The clock system provides three ways to generate the system clock:

#### PLL Base Mode

The system clock is derived from the VCO base (free running) frequency clock divided by the K factor.

$$f_{SYS} = f_{VCObase} \times \frac{1}{K}$$

#### Prescaler Mode (VCO Bypass Operation)

In VCO bypass operation, the system clock is derived from the oscillator clock, divided by the P and K factors.

$$f_{SYS} = f_{OSC} \times \frac{1}{P \times K}$$

#### PLL Mode

The system clock is derived from the oscillator clock, multiplied by the N factor, and divided by the P and K factors. Both VCO bypass and PLL bypass must be inactive for this PLL mode. The PLL mode is used during normal system operation.

$$f_{SYS} = f_{OSC} \times \frac{N}{P \times K}$$

**Table 3-1** shows the settings of bits OSCDISC and VCOBYP for different clock mode selection.

| OSCDISC | VCOBYP | Clock Working Modes |  |

|---------|--------|---------------------|--|

| 0       | 0      | PLL Mode            |  |

| 0       | 1      | Prescaler Mode      |  |

| 1       | 0      | PLL Base Mode       |  |

| 1       | 1      | PLL Base Mode       |  |

## Table 3-1 Clock Mode Selection

Note: When oscillator clock is disconnected from PLL, the clock mode is PLL Base mode regardless of the setting of VCOBYP bit.

#### **System Frequency Selection**

For the XC866, the values of P and K are fixed to "1" and "2", respectively. In order to obtain the required system frequency,  $f_{sys}$ , the value of N can be selected by bit NDIV for different oscillator inputs. **Table 21** provides examples on how  $f_{sys}$  = 80 MHz can be obtained for the different oscillator sources.

## 3.8.2 Clock Management

The CGU generates all clock signals required within the microcontroller from a single clock,  $f_{sys}$ . During normal system operation, the typical frequencies of the different modules are as follow:

- CPU clock: CCLK, SCLK = 26.7 MHz

- CCU6 clock: FCLK = 26.7 MHz

- Other peripherals: PCLK = 26.7 MHz

- Flash Interface clock: CCLK3 = 80 MHz and CCLK = 26.7 MHz

In addition, different clock frequency can output to pin CLKOUT(P0.0). The clock output frequency can further be divided by 2 using toggle latch (bit TLEN is set to 1), the resulting output frequency has 50% duty cycle. **Figure 25** shows the clock distribution of the XC866.

Figure 25 Clock Generation from f<sub>svs</sub>

XC866

## 3.11.1 Baud-Rate Generator

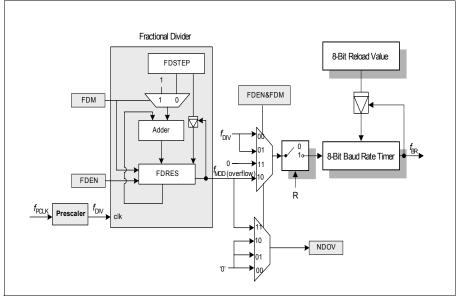

The baud-rate generator is based on a programmable 8-bit reload value, and includes divider stages (i.e., prescaler and fractional divider) for generating a wide range of baud rates based on its input clock  $f_{PCLK}$ , see **Figure 29**.

#### Figure 29 Baud-rate Generator Circuitry

The baud rate timer is a count-down timer and is clocked by either the output of the fractional divider ( $f_{MOD}$ ) if the fractional divider is enabled (FDCON.FDEN = 1), or the output of the prescaler ( $f_{DIV}$ ) if the fractional divider is disabled (FDEN = 0). For baud rate generation, the fractional divider must be configured to fractional divider mode (FDCON.FDM = 0). This allows the baud rate control run bit BCON.R to be used to start or stop the baud rate timer. At each timer underflow, the timer is reloaded with the 8-bit reload value in register BG and one clock pulse is generated for the serial channel.

Enabling the fractional divider in normal divider mode (FDEN = 1 and FDM = 1) stops the baud rate timer and nullifies the effect of bit BCON.R. See **Section 3.12**.

The baud rate  $(f_{BR})$  value is dependent on the following parameters:

- Input clock f<sub>PCLK</sub>

- Prescaling factor (2<sup>BRPRE</sup>) defined by bit field BRPRE in register BCON

- Fractional divider (STEP/256) defined by register FDSTEP (to be considered only if fractional divider is enabled and operating in fractional divider mode)

• 8-bit reload value (BR\_VALUE) for the baud rate timer defined by register BG The following formulas calculate the final baud rate without and with the fractional divider respectively:

baud rate =

$$\frac{f_{PCLK}}{16 \times 2^{BRPRE} \times (BR_VALUE + 1)}$$

where  $2^{BRPRE} \times (BR_VALUE + 1) > 1$

baud rate =

$$\frac{f_{PCLK}}{16 \times 2^{BRPRE} \times (BR VALUE + 1)} \times \frac{STEP}{256}$$

The maximum baud rate that can be generated is limited to  $f_{PCLK}/32$ . Hence, for a module clock of 26.7 MHz, the maximum achievable baud rate is 0.83 MBaud.

Standard LIN protocal can support a maximum baud rate of 20kHz, the baud rate accuracy is not critical and the fractional divider can be disabled. Only the prescaler is used for auto baud rate calculation. For LIN fast mode, which supports the baud rate of 20kHz to 115.2kHz, the higher baud rates require the use of the fractional divider for greater accuracy.

**Table 26** lists the various commonly used baud rates with their corresponding parameter settings and deviation errors. The fractional divider is disabled and a module clock of 26.7 MHz is used.

| Baud rate  | Prescaling Factor<br>(2 <sup>BRPRE</sup> ) | Reload Value<br>(BR_VALUE + 1) | Deviation Error |  |  |

|------------|--------------------------------------------|--------------------------------|-----------------|--|--|

| 19.2 kBaud | 1 (BRPRE=000 <sub>B</sub> )                | 87 (57 <sub>H</sub> )          | -0.22 %         |  |  |

| 9600 Baud  | 1 (BRPRE=000 <sub>B</sub> )                | 174 (AE <sub>H</sub> )         | -0.22 %         |  |  |

| 4800 Baud  | 2 (BRPRE=001 <sub>B</sub> )                | 174 (AE <sub>H</sub> )         | -0.22 %         |  |  |

| 2400 Baud  | 4 (BRPRE=010 <sub>B</sub> )                | 174 (AE <sub>H</sub> )         | -0.22 %         |  |  |

Table 26

Typical Baud rates for UART with Fractional Divider disabled

The fractional divider allows baud rates of higher accuracy (lower deviation error) to be generated. **Table 27** lists the resulting deviation errors from generating a baud rate of

## 3.11.2 Baud Rate Generation using Timer 1

In UART modes 1 and 3, Timer 1 can be used for generating the variable baud rates. In theory, this timer could be used in any of its modes. But in practice, it should be set into auto-reload mode (Timer 1 mode 2), with its high byte set to the appropriate value for the required baud rate. The baud rate is determined by the Timer 1 overflow rate and the value of SMOD as follows:

[3.1]

Mode 1, 3 baud rate=  $\frac{2^{\text{SMOD}} \times f_{\text{PCLK}}}{32 \times 2 \times (256 - \text{TH1})}$

## 3.12 Normal Divider Mode (8-bit Auto-reload Timer)

Setting bit FDM in register FDCON to 1 configures the fractional divider to normal divider mode, while at the same time disables baud rate generation (see **Figure 29**). Once the fractional divider is enabled (FDEN = 1), it functions as an 8-bit auto-reload timer (with no relation to baud rate generation) and counts up from the reload value with each input clock pulse. Bit field RESULT in register FDRES represents the timer value, while bit field STEP in register FDSTEP defines the reload value. At each timer overflow, an overflow flag (FDCON.NDOV) will be set and an interrupt request generated. This gives an output clock  $f_{MOD}$  that is 1/n of the input clock  $f_{DIV}$ , where n is defined by 256 - STEP.

The output frequency in normal divider mode is derived as follows:

$f_{MOD} = f_{DIV} \times \frac{1}{256 - STEP}$ [3.2]

## 3.16 Timer 2

Timer 2 Modes

Table 29

Timer 2 is a 16-bit general purpose timer (THL2) that has two modes of operation, a 16-bit auto-reload mode and a 16-bit one channel capture mode. If the prescalar is disabled, Timer 2 counts with an input clock of PCLK/12. Timer 2 continues counting as long as it is enabled.

| Table 29           | Timer 2 wodes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mode               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Auto-reload        | <ul> <li>Up/Down Count Disabled</li> <li>Count up only</li> <li>Start counting from 16-bit reload value, overflow at FFFF<sub>H</sub></li> <li>Reload event configurable for trigger by overflow condition only, or by negative/positive edge at input pin T2EX as well</li> <li>Programmble reload value in register RC2</li> <li>Interrupt is generated with reload event</li> </ul>                                                                                                                                                                                                                                       |

|                    | <ul> <li>Up/Down Count Enabled</li> <li>Count up or down, direction determined by level at input pin T2EX</li> <li>No interrupt is generated</li> <li>Count up <ul> <li>Start counting from 16-bit reload value, overflow at FFF<sub>H</sub></li> <li>Reload event triggered by overflow condition</li> <li>Programmble reload value in register RC2</li> </ul> </li> <li>Count down <ul> <li>Start counting from FFF<sub>H</sub>, underflow at value defined in register RC2</li> <li>Reload event triggered by underflow condition <ul> <li>Reload event triggered by underflow condition</li> </ul> </li> </ul></li></ul> |

| Channel<br>capture | <ul> <li>Count up only</li> <li>Start counting from 0000<sub>H</sub>, overflow at FFFF<sub>H</sub></li> <li>Reload event triggered by overflow condition</li> <li>Reload value fixed at 0000<sub>H</sub></li> <li>Capture event triggered by falling/rising edge at pin T2EX</li> <li>Captured timer value stored in register RC2</li> <li>Interrupt is generated with reload or capture event</li> </ul>                                                                                                                                                                                                                    |

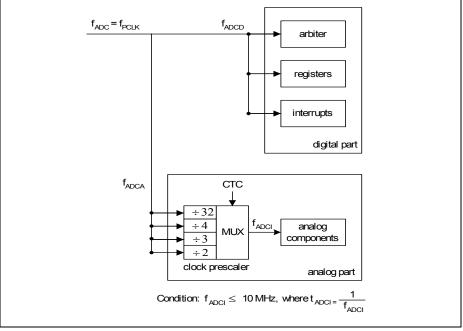

## 3.18.1 ADC Clocking Scheme

A common module clock  $f_{ADC}$  generates the various clock signals used by the analog and digital parts of the ADC module:

- f<sub>ADCA</sub> is input clock for the analog part.

- $f_{ADCI}$  is internal clock for the analog part (defines the time base for conversion length and the sample time). This clock is generated internally in the analog part, based on the input clock  $f_{ADCA}$  to generate a correct duty cycle for the analog components.

- f<sub>ADCD</sub> is input clock for the digital part.

The internal clock for the analog part  $f_{ADCI}$  is limited to a maximum frequency of 10 MHz. Therefore, the ADC clock prescaler must be programmed to a value that ensures  $f_{ADCI}$  does not exceed 10 MHz. The prescaler ratio is selected by bit field CTC in register GLOBCTR. A prescaling ratio of 32 can be selected when the maximum performance of the ADC is not required.

Figure 33 ADC Clocking Scheme

## 3.19 On-Chip Debug Support

The On-Chip Debug Support (OCDS) provides the basic functionality required for the software development and debugging of XC800-based systems.

The OCDS design is based on these principles:

- · use the built-in debug functionality of the XC800 Core

- · add a minimum of hardware overhead

- provide support for most of the operations by a Monitor Program

- use standard interfaces to communicate with the Host (a Debugger)

#### Features:

- · Set breakpoints on instruction address and within a specified address range

- Set breakpoints on internal RAM address

- · Support unlimited software breakpoints in Flash/RAM code region

- Process external breaks

- Step through the program code

The OCDS functional blocks are shown in **Figure 35**. The Monitor Mode Control (MMC) block at the center of OCDS system brings together control signals and supports the overall functionality. The MMC communicates with the XC800 Core, primarily via the Debug Interface, and also receives reset and clock signals. After processing memory address and control signals from the core, the MMC provides proper access to the dedicated extra-memories: a Monitor ROM (holding the code) and a Monitor RAM (for work-data and Monitor-stack). The OCDS system is accessed through the JTAG<sup>1</sup>, which is an interface dedicated exclusively for testing and debugging activities and is not normally used in an application. The dedicated MBC pin is used for external configuration and debugging control.

Note: All the debug functionality described here can normally be used only after XC866 has been started in OCDS mode.

<sup>&</sup>lt;sup>1)</sup> The pins of the JTAG port can be assigned to either Port 0 (primary) or Ports 1 and 2 (secondary). User must set the JTAG pins (TCK and TDI) as input during connection with the OCDS system.

#### **Electrical Parameters**

#### Table 34 Input/Output Characteristics (Operating Conditions apply)

| Parameter                                                                | Sym               | bol      | Limit | Values | Unit |                                                                                |  |

|--------------------------------------------------------------------------|-------------------|----------|-------|--------|------|--------------------------------------------------------------------------------|--|

|                                                                          |                   |          | min.  | max.   |      | Remarks                                                                        |  |

| Pull-up current                                                          | $I_{PU}$          | SR       | -     | -5     | μA   | V <sub>IH,min</sub>                                                            |  |

|                                                                          |                   |          | -50   | -      | μA   | V <sub>IL,max</sub>                                                            |  |

| Pull-down current                                                        | $I_{PD}$          | SR       | -     | 5      | μA   | V <sub>IL,max</sub>                                                            |  |

|                                                                          |                   |          | 50    | -      | μA   | V <sub>IH,min</sub>                                                            |  |

| Input leakage current <sup>2)</sup>                                      | I <sub>OZ1</sub>  | CC       | -1    | 1      | μA   | $0 < V_{IN} < V_{DDP},$<br>$T_A \le 125^{\circ}C$ , XC866-4FR<br>and XC866-2FR |  |

|                                                                          |                   |          | -2.5  | 1      | μA   | $0 < V_{IN} < V_{DDP},$<br>$T_A \le 125^{\circ}C, XC866-1FR$<br>and ROM device |  |

| Input current at XTAL1                                                   | $I_{ILX}$         | CC       | - 10  | 10     | μA   |                                                                                |  |

| Overload current on any pin                                              | I <sub>OV</sub>   | SR       | -5    | 5      | mA   |                                                                                |  |

| Absolute sum of overload currents                                        | $\Sigma   I_{OV}$ | <br>SR   | -     | 25     | mA   | 3)                                                                             |  |

| Voltage on any pin during $V_{\text{DDP}}$ power off                     | V <sub>PO</sub>   | SR       | -     | 0.3    | V    | 4)                                                                             |  |

| Maximum current per pin (excluding $V_{\rm DDP}$ and $V_{\rm SS}$ )      | I <sub>M</sub>    | SR       | -     | 15     | mA   |                                                                                |  |

| Maximum current for all pins (excluding $V_{\rm DDP}$ and $V_{\rm SS}$ ) | $\Sigma  I_{M} $  | SR       | -     | 60     | mA   |                                                                                |  |

| Maximum current into $V_{\text{DDP}}$                                    | I <sub>MVDI</sub> | DP<br>SR | -     | 80     | mA   |                                                                                |  |

| $\overline{ \mbox{Maximum current out of } }_{V_{\rm SS}}$               | I <sub>MVS</sub>  | sr<br>Sr | -     | 80     | mA   |                                                                                |  |

<sup>1)</sup> Not subjected to production test, verified by design/characterization. Hysteresis is implemented to avoid meta stable states and switching due to internal ground bounce. It cannot be guaranteed that it suppresses switching due to external system noise.

<sup>2)</sup> <u>An additional error current ( $l_{INJ}$ ) will flow if an overload current flows through an adjacent pin. TMS pin and RESET pin have internal pull devices and are not included in the input leakage current characteristic.</u>

<sup>3)</sup> Not subjected to production test, verified by design/characterization.

#### **Electrical Parameters**

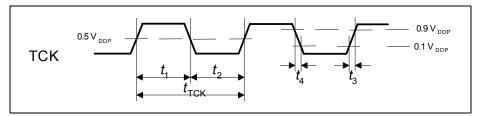

## 4.3.5 JTAG Timing

## Table 44TCK Clock Timing (Operating Conditions apply; $C_L = 50 \text{ pF}$ )

| Parameter           | Symbol              | Limits |     | Unit |

|---------------------|---------------------|--------|-----|------|

|                     |                     | min    | max |      |

| TCK clock period    | t <sub>TCK</sub> SR | 50     | -   | ns   |

| TCK high time       | t <sub>1</sub> SR   | 20     | -   | ns   |

| TCK low time        | t <sub>2</sub> SR   | 20     | -   | ns   |

| TCK clock rise time | t <sub>3</sub> SR   | -      | 4   | ns   |

| TCK clock fall time | t <sub>4</sub> SR   | -      | 4   | ns   |

Figure 43 TCK Clock Timing

#### **Electrical Parameters**

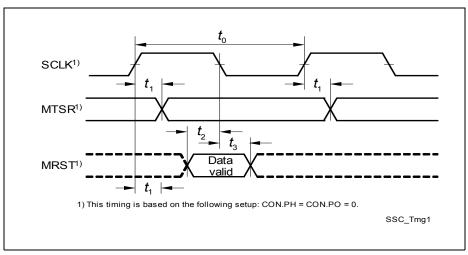

## 4.3.6 SSC Master Mode Timing

## Table 46 SSC Master Mode Timing (Operating Conditions apply; C<sub>L</sub> = 50 pF)

| Parameter              | Symbol                |    | Limit Values          |      | Unit |

|------------------------|-----------------------|----|-----------------------|------|------|

|                        |                       |    | min.                  | max. |      |

| SCLK clock period      | <i>t</i> <sub>0</sub> | CC | 2*T <sub>SSC</sub> 1) | _    | ns   |

| MTSR delay from SCLK _ | <i>t</i> <sub>1</sub> | CC | 0                     | 8    | ns   |

| MRST setup to SCLK ٦   | <i>t</i> <sub>2</sub> | SR | 22                    | _    | ns   |

| MRST hold from SCLK ٦  | $t_3$                 | SR | 0                     | -    | ns   |

<sup>1)</sup>  $T_{SSCmin} = T_{CPU} = 1/f_{CPU}$ . When  $f_{CPU} = 26.7$ MHz,  $t_0 = 74.9$ ns.  $T_{CPU}$  is the CPU clock period.

Figure 45 SSC Master Mode Timing

#### Package and Reliability

## 5.2 Package Outline

Figure 46 PG-TSSOP-38-4 Package Outline