Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Last Time Buy                                                                |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | XC800                                                                        |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 86MHz                                                                        |

| Connectivity               | SSI, UART/USART                                                              |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 19                                                                           |

| Program Memory Size        | 16KB (16K x 8)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 768 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                  |

| Data Converters            | A/D 8x10b                                                                    |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 38-TFSOP (0.173", 4.40mm Width)                                              |

| Supplier Device Package    | PG-TSSOP-38-4                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xc8664frabefxuma1 |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **General Device Information**

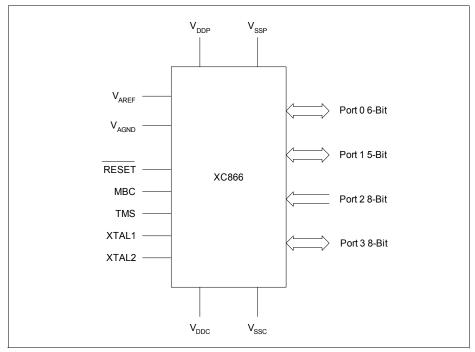

# 2.2 Logic Symbol

Figure 3 XC866 Logic Symbol

# XC866

# **General Device Information**

| Symbol | Pin<br>Number | Туре | Reset<br>State | Function           |                                                                               |

|--------|---------------|------|----------------|--------------------|-------------------------------------------------------------------------------|

| P3     |               | I    |                |                    | directional general purpose I/O port. It as alternate functions for the CCU6. |

| P3.0   | 32            |      | Hi-Z           | CCPOS1_2<br>CC60_0 | CCU6 Hall Input 1<br>Input/Output of Capture/Compare<br>channel 0             |

| P3.1   | 33            |      | Hi-Z           | CCPOS0_2<br>CC61_2 | CCU6 Hall Input 0<br>Input/Output of Capture/Compare<br>channel 1             |

|        |               |      |                | COUT60_0           | Output of Capture/Compare<br>channel 0                                        |

| P3.2   | 34            |      | Hi-Z           | CCPOS2_2<br>CC61_0 | CCU6 Hall Input 2<br>Input/Output of Capture/Compare<br>channel 1             |

| P3.3   | 35            |      | Hi-Z           | COUT61_0           | Output of Capture/Compare<br>channel 1                                        |

| P3.4   | 36            |      | Hi-Z           | CC62_0             | Input/Output of Capture/Compare<br>channel 2                                  |

| P3.5   | 37            |      | Hi-Z           | COUT62_0           | Output of Capture/Compare<br>channel 2                                        |

| P3.6   | 30            |      | PD             | CTRAP_0            | CCU6 Trap Input                                                               |

| P3.7   | 31            |      | Hi-Z           | EXINT4<br>COUT63_0 | External Interrupt Input 4<br>Output of Capture/Compare<br>channel 3          |

#### Table 3Pin Definitions and Functions (cont'd)

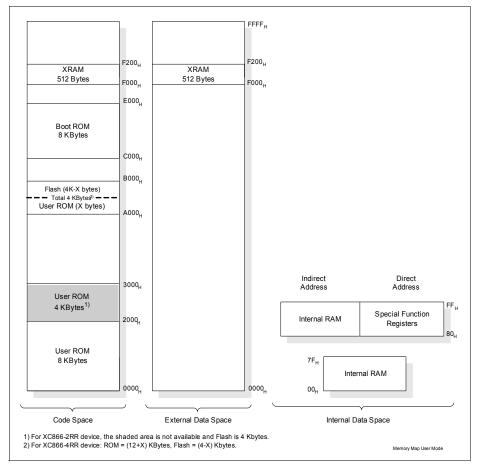

# Figure 7 illustrates the memory address spaces of the XC866-4RR device.

Figure 7 Memory Map of XC866 ROM Devices

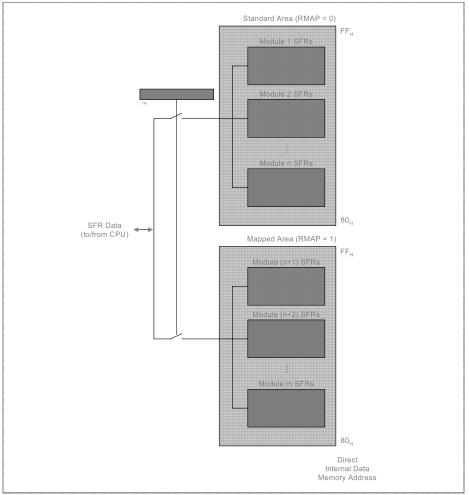

# 3.2.2 Special Function Register

The Special Function Registers (SFRs) occupy direct internal data memory space in the range  $80_H$  to FF<sub>H</sub>. All registers, except the program counter, reside in the SFR area. The SFRs include pointers and registers that provide an interface between the CPU and the on-chip peripherals. As the 128-SFR range is less than the total number of registers required, address extension mechanisms are required to increase the number of addressable SFRs. The address extension mechanisms include:

- Mapping

- Paging

# 3.2.2.1 Address Extension by Mapping

Address extension is performed at the system level by mapping. The SFR area is extended into two portions: the standard (non-mapped) SFR area and the mapped SFR area. Each portion supports the same address range  $80_H$  to FF<sub>H</sub>, bringing the number of addressable SFRs to 256. The extended address range is not directly controlled by the CPU instruction itself, but is derived from bit RMAP in the system control register SYSCON0 at address  $8F_H$ . To access SFRs in the mapped area, bit RMAP in SFR SYSCON0 must be set. Alternatively, the SFRs in the standard area can be accessed by clearing bit RMAP. The SFR area can be selected as shown in **Figure 8**.

#### SYSCON0 System Control Register 0 Reset Value: 00<sub>H</sub> 2 1 0 7 6 5 4 3 0 1 0 RMAP r rw r rw

| Field | Bits    | Туре | Description                                                                                                                                                               |

|-------|---------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RMAP  | 0       | rw   | <ul> <li>Special Function Register Map Control</li> <li>The access to the standard SFR area is enabled.</li> <li>The access to the mapped SFR area is enabled.</li> </ul> |

| 1     | 2       | rw   | <b>Reserved</b><br>Returns the last value if read; should be written<br>with 1.                                                                                           |

| 0     | 1,[7:3] | r    | <b>Reserved</b><br>Returns 0 if read; should be written with 0.                                                                                                           |

# Note: The RMAP bit must be cleared/set by ANL or ORL instructions. The rest bits of SYSCON0 should not be modified.

As long as bit RMAP is set, the mapped SFR area can be accessed. This bit is not cleared automatically by hardware. Thus, before standard/mapped registers are accessed, bit RMAP must be cleared/set, respectively, by software.

Figure 8 Address Extension by Mapping

| Field | Bits  | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------|-------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OP    | [7:6] | w    | <ul> <li>Operation</li> <li>OX Manual page mode. The value of STNR is ignored and PAGE is directly written.</li> <li>10 New page programming with automatic page saving. The value written to the bit positions of PAGE is stored. In parallel, the previous contents of PAGE are saved in the storage bit field STx indicated by STNR.</li> <li>11 Automatic restore page action. The value written to the bit positions PAGE is ignored and instead, PAGE is overwritten by the contents of the storage bit field STx indicated by STNR.</li> </ul> |

| 0     | 3     | r    | <b>Reserved</b><br>Returns 0 if read; should be written with 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

### Table 7CPU Register Overview (cont'd)

| Addr            | Register Name                    |                                      | Bit       | 7           | 6           | 5           | 4           | 3    | 2    | 1     | 0         |

|-----------------|----------------------------------|--------------------------------------|-----------|-------------|-------------|-------------|-------------|------|------|-------|-----------|

| F0 <sub>H</sub> | В                                | Reset: 00 <sub>H</sub>               | Bit Field | B7          | B6          | B5          | B4          | B3   | B2   | B1    | B0        |

|                 | B Register                       |                                      | Туре      | rw          | rw          | rw          | rw          | rw   | rw   | rw    | rw        |

| F8 <sub>H</sub> | IP1<br>Interrupt Priority Regis  | Reset: 00 <sub>H</sub><br>iter 1     | Bit Field | PCCIP<br>3  | PCCIP<br>2  | PCCIP<br>1  | PCCIP<br>0  | PXM  | PX2  | PSSC  | PADC      |

|                 |                                  |                                      | Туре      | rw          | rw          | rw          | rw          | rw   | rw   | rw    | rw        |

| F9 <sub>H</sub> | IPH1<br>Interrupt Priority Regis | Reset: 00 <sub>H</sub><br>ter 1 High | Bit Field | PCCIP<br>3H | PCCIP<br>2H | PCCIP<br>1H | PCCIP<br>0H | PXMH | PX2H | PSSCH | PADC<br>H |

|                 |                                  |                                      | Туре      | rw          | rw          | rw          | rw          | rw   | rw   | rw    | rw        |

The system control SFRs can be accessed in the standard memory area (RMAP = 0).

#### Table 8 System Control Register Overview

| Addr            | Register Name                                                       | Bit       | 7   | 6           | 5            | 4            | 3            | 2             | 1            | 0           |  |

|-----------------|---------------------------------------------------------------------|-----------|-----|-------------|--------------|--------------|--------------|---------------|--------------|-------------|--|

| RMAP =          | 0 or 1                                                              |           | 1   |             |              | 1            |              |               | 1            |             |  |

| 8F <sub>H</sub> | SYSCON0 Reset: 00 <sub>H</sub>                                      | Bit Field |     |             |              | 0            |              |               | RMAP         |             |  |

|                 | System Control Register 0                                           | Туре      |     |             |              | r            |              |               |              | rw          |  |

| RMAP =          | 0                                                                   |           | 1   |             |              |              |              |               |              |             |  |

| BF <sub>H</sub> | SCU_PAGE Reset: 00 <sub>H</sub>                                     | Bit Field | C   | )P          | ST           | NR           | 0            |               | PAGE         |             |  |

|                 | Page Register for System Control                                    | Туре      | 1   | N           | ١            | v            | r            |               | rwh          |             |  |

| RMAP =          | 0, Page 0                                                           |           |     |             |              |              |              |               |              |             |  |

| B3 <sub>H</sub> | MODPISEL Reset: 00 <sub>H</sub><br>Peripheral Input Select Register | Bit Field |     | 0           | JTAG<br>TDIS | JTAG<br>TCKS | (            | 0             | EXINT<br>0IS | URRIS       |  |

|                 |                                                                     | Туре      |     | r           | rw           | rw           |              | r             | rw           | rw          |  |

| B4 <sub>H</sub> | IRCON0 Reset: 00 <sub>H</sub><br>Interrupt Request Register 0       | Bit Field | 0   | EXINT<br>6  | EXINT<br>5   | EXINT<br>4   | EXINT<br>3   | EXINT<br>2    | EXINT<br>1   | EXINT<br>0  |  |

|                 |                                                                     | Туре      | r   | rwh         | rwh          | rwh          | rwh          | rwh           | rwh          | rwh         |  |

| B5 <sub>H</sub> | IRCON1 Reset: 00 <sub>H</sub><br>Interrupt Request Register 1       | Bit Field |     | 0           |              | ADCS<br>RC1  | ADCS<br>RC0  | RIR           | TIR          | EIR         |  |

|                 |                                                                     | Туре      |     | r           |              | rwh          | rwh          | rwh           | rwh rwh      |             |  |

| B7 <sub>H</sub> | EXICON0 Reset: 00 <sub>H</sub>                                      | Bit Field | EXI | NT3         | EXI          | NT2          | EXI          | NT1           | EXI          | NT0         |  |

|                 | External Interrupt Control Register 0                               | Туре      | r   | w           |              | w            |              | w             |              | w           |  |

| BA <sub>H</sub> | EXICON1 Reset: 00 <sub>H</sub>                                      | Bit Field |     | 0           | EXI          | NT6          | EXI          | NT5           | EXI          | NT4         |  |

|                 | External Interrupt Control Register 1                               | Туре      |     | r           | r            | w            | r            | w             | r            | w           |  |

| BB <sub>H</sub> | NMICON Reset: 00 <sub>H</sub><br>NMI Control Register               | Bit Field | 0   | NMI<br>ECC  | NMI<br>VDDP  | NMI<br>VDD   | NMI<br>OCDS  | NMI<br>FLASH  | NMI<br>PLL   | NMI<br>WDT  |  |

|                 |                                                                     | Туре      | r   | rw          | rw           | rw           | rw           | rw            | rw           | rw          |  |

| BC <sub>H</sub> | NMISR Reset: 00 <sub>H</sub><br>NMI Status Register                 | Bit Field | 0   | FNMI<br>ECC | FNMI<br>VDDP | FNMI<br>VDD  | FNMI<br>OCDS | FNMI<br>FLASH | FNMI<br>PLL  | FNMI<br>WDT |  |

|                 |                                                                     | Туре      | r   | rwh         | rwh          | rwh          | rwh          | rwh           | rwh          | rwh         |  |

| BD <sub>H</sub> | BCON Reset: 00 <sub>H</sub>                                         | Bit Field | BG  | SEL         | 0            | BREN         |              | BRPRE         |              | R           |  |

|                 | Baud Rate Control Register                                          | Туре      | r   | w           | r            | rw           |              | rw            |              | rw          |  |

| BE <sub>H</sub> | BG Reset: 00 <sub>H</sub>                                           | Bit Field |     |             |              | BR_V         | ALUE         |               |              |             |  |

|                 | Baud Rate Timer/Reload Register                                     | Туре      |     |             |              |              | N            |               |              |             |  |

| E9 <sub>H</sub> | FDCON Reset: 00 <sub>H</sub><br>Fractional Divider Control Register | Bit Field | BGS | SYNEN       | ERRSY<br>N   | EOFSY<br>N   | BRK          | NDOV          | FDM          | FDEN        |  |

|                 |                                                                     | Туре      | rw  | rw          | rwh          | rwh          | rwh          | rwh           | rw           | rw          |  |

| EA <sub>H</sub> | FDSTEP Reset: 00 <sub>H</sub>                                       | Bit Field |     |             |              | ST           | EP           |               |              |             |  |

|                 | Fractional Divider Reload Register                                  | Туре      |     |             |              |              | N            |               |              |             |  |

| EB <sub>H</sub> | FDRES Reset: 00 <sub>H</sub>                                        | Bit Field |     |             |              | RES          | ULT          |               |              |             |  |

|                 | Fractional Divider Result Register                                  | Туре      | 1   |             |              | r            | h            |               |              |             |  |

| C1 <sub>H</sub> | T2_T2MOD<br>Timer 2 Mode Register | Reset: 00 <sub>H</sub>                     | Bit Field | T2<br>REGS | T2<br>RHEN | EDGE<br>SEL | PREN | T2PRE  | DCEN |  |  |

|-----------------|-----------------------------------|--------------------------------------------|-----------|------------|------------|-------------|------|--------|------|--|--|

|                 |                                   |                                            | Туре      | rw         | rw         | rw          | rw   | rw     | rw   |  |  |

| C2 <sub>H</sub> | T2_RC2L                           | Reset: 00 <sub>H</sub>                     | Bit Field |            |            |             | RC2  | [7:0]  |      |  |  |

|                 | Timer 2 Reload/Capture            | Туре                                       | rwh       |            |            |             |      |        |      |  |  |

| C3 <sub>H</sub> | T2_RC2H                           | Reset: 00 <sub>H</sub> Bit Field RC2[15:8] |           |            |            |             |      |        |      |  |  |

|                 | Timer 2 Reload/Capture            | Register High                              | Туре      |            |            |             | rv   | /h     |      |  |  |

| C4 <sub>H</sub> | T2_T2L                            | Reset: 00 <sub>H</sub>                     | Bit Field |            |            |             | THL  | 2[7:0] |      |  |  |

|                 | Timer 2 Register Low              |                                            | Туре      |            |            |             | rv   | /h     |      |  |  |

| C5 <sub>H</sub> | T2_T2H                            | Reset: 00 <sub>H</sub>                     | Bit Field |            |            |             | THL2 | [15:8] |      |  |  |

|                 | Timer 2 Register High             |                                            | Туре      |            |            |             | rv   | vh     |      |  |  |

The CCU6 SFRs can be accessed in the standard memory area (RMAP = 0).

# Table 13 CCU6 Register Overview

| Addr            | Register Name                                                                | Bit       | 7          | 6          | 5          | 4          | 3          | 2          | 1          | 0          |  |

|-----------------|------------------------------------------------------------------------------|-----------|------------|------------|------------|------------|------------|------------|------------|------------|--|

| RMAP =          | 0                                                                            |           |            | 1          |            |            |            |            |            | 1          |  |

| A3 <sub>H</sub> | CCU6_PAGE Reset: 00 <sub>H</sub>                                             | Bit Field | C          | P          | ST         | NR         | 0          | PAGE       |            |            |  |

|                 | Page Register for CCU6                                                       | Туре      | ١          | v          | ١          | N          | r          |            | rwh        |            |  |

| RMAP =          | 0, Page 0                                                                    |           |            |            |            |            |            |            |            |            |  |

| 9A <sub>H</sub> | CCU6_CC63SRL Reset: 00 <sub>H</sub><br>Capture/Compare Shadow Register for   | Bit Field |            |            |            | CC         | 63SL       |            |            |            |  |

|                 | Channel CC63 Low                                                             | Туре      |            |            |            | r          | w          |            |            |            |  |

| 9B <sub>H</sub> | CCU6_CC63SRH Reset: 00 <sub>H</sub><br>Capture/Compare Shadow Register for   | Bit Field |            |            |            | CC6        | 63SH       |            |            |            |  |

|                 | Channel CC63 High                                                            | Туре      |            |            |            | r          | w          |            |            |            |  |

| 9C <sub>H</sub> | CCU6_TCTR4L Reset: 00 <sub>H</sub><br>Timer Control Register 4 Low           | Bit Field | T12<br>STD | T12<br>STR | (          | 0          | DTRES      | T12<br>RES | T12RS      | T12RR      |  |

|                 |                                                                              | Туре      | w          | w          |            | r          | w          | w          | w          | w          |  |

| 9D <sub>H</sub> | CCU6_TCTR4H Reset: 00 <sub>H</sub><br>Timer Control Register 4 High          | Bit Field | T13<br>STD | T13<br>STR |            | 0          |            | T13<br>RES | T13RS      | T13RR      |  |

|                 |                                                                              | Туре      | w          | w          |            | r          |            | w          | w          | w          |  |

| 9E <sub>H</sub> | CCU6_MCMOUTSL Reset: 00 <sub>H</sub><br>Multi-Channel Mode Output Shadow     | Bit Field | STRM<br>CM | 0          |            |            | MCI        | MPS        |            |            |  |

|                 | Register Low                                                                 | Туре      | w          | r          |            |            | r          | w          |            |            |  |

| 9F <sub>H</sub> | CCU6_MCMOUTSH Reset: 00 <sub>H</sub>                                         | Bit Field | STRHP      | 0          |            | CURHS      | ;          |            | EXPHS      |            |  |

|                 | Multi-Channel Mode Output Shadow<br>Register High                            | Туре      | w          | r          |            | rw         |            |            | rw         |            |  |

| A4 <sub>H</sub> | CCU6_ISRL Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Status         | Bit Field | RT12P<br>M | RT12O<br>M | RCC62<br>F | RCC62<br>R | RCC61<br>F | RCC61<br>R | RCC60<br>F | RCC60<br>R |  |

|                 | Reset Register Low                                                           | Туре      | w          | w          | w          | w          | w          | w          | w          | w          |  |

| A5 <sub>H</sub> | CCU6_ISRH Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Status         | Bit Field | RSTR       | RIDLE      | RWHE       | RCHE       | 0          | RTRPF      | RT13<br>PM | RT13<br>CM |  |

|                 | Reset Register High                                                          | Туре      | w          | w          | w          | w          | r          | w          | w          | w          |  |

| A6 <sub>H</sub> | CCU6_CMPMODIFL Reset: 00 <sub>H</sub><br>Compare State Modification Register | Bit Field | 0          | MCC63<br>S |            | 0          |            | MCC62<br>S | MCC61<br>S | MCC60<br>S |  |

|                 | Low                                                                          | Туре      | r          | w          |            | r          |            | w          | w          | w          |  |

| A7 <sub>H</sub> | CCU6_CMPMODIFH Reset: 00 <sub>H</sub><br>Compare State Modification Register | Bit Field | 0          | MCC63<br>R |            | 0          |            | MCC62<br>R | MCC61<br>R | MCC60<br>R |  |

|                 | High                                                                         | Туре      | r          | w          |            | r          |            | w          | w          | w          |  |

| FA <sub>H</sub> | CCU6_CC60SRL Reset: 00 <sub>H</sub><br>Capture/Compare Shadow Register for   | Bit Field |            |            |            | CC         | 60SL       |            |            |            |  |

|                 | Channel CC60 Low                                                             | Туре      |            |            |            | n          | wh         |            |            |            |  |

#### Table 13 CCU6 Register Overview (cont'd)

| Addr            | Register Name                                                             | Bit       | 7      | 6            | 5            | 4          | 3            | 2          | 1            | 0          |

|-----------------|---------------------------------------------------------------------------|-----------|--------|--------------|--------------|------------|--------------|------------|--------------|------------|

| FF <sub>H</sub> | CCU6_TRPCTRH Reset: 00 <sub>H</sub>                                       | Bit Field |        | TRPEN        |              |            | TR           | PEN        |              |            |

|                 | Trap Control Register High                                                |           | N      | 13           |              |            |              |            |              |            |

|                 |                                                                           | Туре      | rw     | rw           |              |            | r            | w          |              |            |

| RMAP =          | 0, Page 3                                                                 |           |        |              |              |            |              |            |              |            |

| 9A <sub>H</sub> | CCU6_MCMOUTL Reset: 00 <sub>H</sub><br>Multi-Channel Mode Output Register | Bit Field | 0      | R            |              |            | MC           | MP         |              |            |

|                 | Low                                                                       | Туре      | r      | rh           |              |            | r            | h          |              |            |

| 9B <sub>H</sub> | CCU6_MCMOUTH Reset: 00 <sub>H</sub><br>Multi-Channel Mode Output Register | Bit Field | (      | )            |              | CURH       |              |            | EXPH         |            |

|                 | High                                                                      | Туре      | 1      | r            |              | rh         |              |            | rh           |            |

| 9C <sub>H</sub> | CCU6_ISL Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Status       | Bit Field | T12PM  | T12OM        | ICC62F       | R          | ICC61F       | R          | ICC60F       | ICC60<br>R |

|                 | Register Low                                                              | Туре      | rh     | rh           | rh           | rh         | rh           | rh         | rh           | rh         |

| 9D <sub>H</sub> | CCU6_ISH Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Status       | Bit Field | STR    | IDLE         | WHE          | CHE        | TRPS         | TRPF       | T13PM        | T13CM      |

|                 | Register High                                                             | Туре      | rh     | rh           | rh           | rh         | rh           | rh         | rh           | rh         |

| 9E <sub>H</sub> | CCU6_PISEL0L Reset: 00 <sub>H</sub>                                       | Bit Field | IST    | RP           | ISC          | C62        | ISC          | C61        | C61 ISCC60   |            |

|                 | Port Input Select Register 0 Low                                          | Туре      | r      | w            | r            | w          | r            | w          | rw           |            |

| 9F <sub>H</sub> | CCU6_PISEL0H Reset: 00 <sub>H</sub><br>Port Input Select Register 0 High  | Bit Field | IST1   | 2HR          | ISP          | OS2        | ISP          | OS1        | ISPOS0       |            |

|                 |                                                                           | Туре      | n      | w            | r            | w          | r            | w          | n            | w          |

| A4 <sub>H</sub> | CCU6_PISEL2 Reset: 00 <sub>H</sub>                                        | Bit Field |        |              | (            | C          |              |            | IST1         | 3HR        |

|                 | Port Input Select Register 2                                              | Туре      |        |              |              | r          |              |            | n            | w          |

| FA <sub>H</sub> | CCU6_T12L Reset: 00 <sub>H</sub>                                          | Bit Field |        |              |              | T12        | CVL          |            |              |            |

|                 | Timer T12 Counter Register Low                                            | Туре      |        |              |              | n          | vh           |            |              |            |

| FB <sub>H</sub> | CCU6_T12H Reset: 00 <sub>H</sub>                                          | Bit Field | T12CVH |              |              |            |              |            |              |            |

|                 | Timer T12 Counter Register High                                           | Туре      |        |              |              | n          | vh           |            |              |            |

| FC <sub>H</sub> | CCU6_T13L Reset: 00 <sub>H</sub>                                          | Bit Field |        |              |              | T13        | CVL          |            |              |            |

|                 | Timer T13 Counter Register Low                                            | Туре      |        |              |              | n          | vh           |            |              |            |

| FD <sub>H</sub> | CCU6_T13H Reset: 00 <sub>H</sub>                                          | Bit Field |        |              |              | T13        | CVH          |            |              |            |

|                 | Timer T13 Counter Register High                                           | Туре      |        |              |              | n          | vh           |            |              |            |

| FE <sub>H</sub> | CCU6_CMPSTATL Reset: 00 <sub>H</sub><br>Compare State Register Low        | Bit Field | 0      | CC63<br>ST   | CCPO<br>S2   | CCPO<br>S1 | CCPO<br>S0   | CC62<br>ST | CC61<br>ST   | CC60<br>ST |

|                 |                                                                           | Туре      | r      | rh           | rh           | rh         | rh           | rh         | rh           | rh         |

| FF <sub>H</sub> | CCU6_CMPSTATH Reset: 00 <sub>H</sub><br>Compare State Register High       | Bit Field | T13IM  | COUT<br>63PS | COUT<br>62PS | CC62<br>PS | COUT<br>61PS | CC61<br>PS | COUT<br>60PS | CC60<br>PS |

|                 |                                                                           | Туре      | rwh    | rwh          | rwh          | rwh        | rwh          | rwh        | rwh          | rwh        |

The SSC SFRs can be accessed in the standard memory area (RMAP = 0).

# Table 14SSC Register Overview

| Addr            | Register Name                            |                        | Bit       | 7  | 6  | 5  | 4  | 3 | 2   | 1   | 0   |

|-----------------|------------------------------------------|------------------------|-----------|----|----|----|----|---|-----|-----|-----|

| RMAP =          | 0                                        |                        | •         |    |    |    |    |   |     |     |     |

| A9 <sub>H</sub> | SSC_PISEL                                | Reset: 00 <sub>H</sub> | Bit Field |    |    | 0  |    |   | CIS | SIS | MIS |

|                 | Port Input Select Regist                 | er                     | Туре      |    |    | r  |    |   | rw  | rw  | rw  |

| AA <sub>H</sub> | SSC_CONL                                 | Reset: 00 <sub>H</sub> | Bit Field | LB | PO | PH | HB |   | В   | М   |     |

|                 | Control Register Low<br>Programming Mode |                        | Туре      | rw | rw | rw | rw |   | r   | w   |     |

|                 | Operating Mode                           |                        | Bit Field |    |    | 0  |    |   | B   | С   |     |

|                 |                                          |                        | Туре      |    |    | r  |    |   | r   | h   |     |

| P-Flash              | D-Flash            |

|----------------------|--------------------|

|                      | Sector 0: 1-Kbyte  |

|                      | Sector 1: 1-Kbyte  |

| Sector 0: 3.75-Kbyte | Sector 2: 512-byte |

|                      | Sector 3: 512-byte |

|                      | Sector 4: 256-byte |

|                      | Sector 5: 256-byte |

|                      | Sector 6: 128-byte |

|                      | Sector 7: 128-byte |

| Sector 1: 128-byte   | Sector 8: 128-byte |

| Sector 2: 128-byte   | Sector 9: 128-byte |

#### Figure 11 Flash Bank Sectorization

İnfineon

The internal structure of each Flash bank represents a sector architecture for flexible erase capability. The minimum erase width is always a complete sector, and sectors can be erased separately or in parallel. Contrary to standard EPROMs, erased Flash memory cells contain 0s.

The D-Flash bank is divided into more physical sectors for extended erasing and reprogramming capability; even numbers for each sector size are provided to allow greater flexibility and the ability to adapt to a wide range of application requirements.

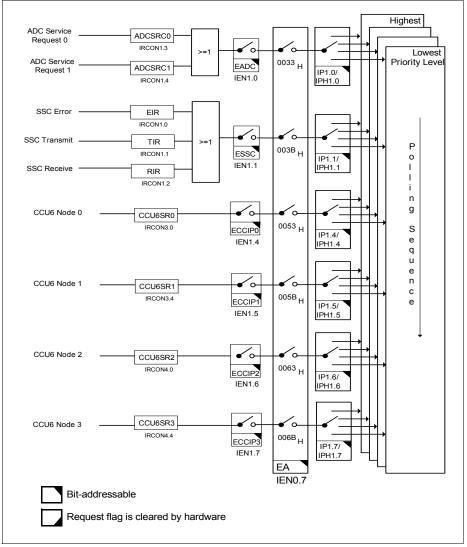

Figure 16 Interrupt Request Sources (Part 3)

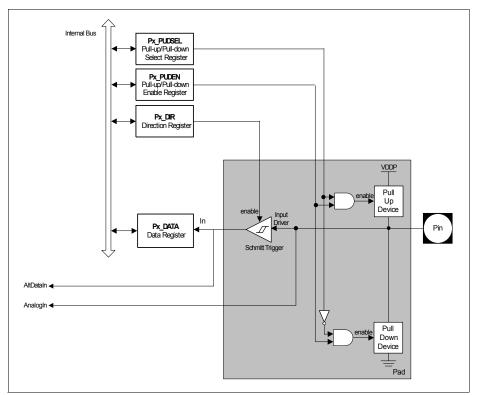

Figure 19 General Structure of Input Port

# 3.7.1 Module Reset Behavior

**Table 19** shows how the functions of the XC866 are affected by the various reset types. A "∎" means that this function is reset to its default state.

| Module/<br>Function                            | Wake-Up<br>Reset       | Watchdog<br>Reset      | Hardware<br>Reset | Power-On<br>Reset | Brownout<br>Reset         |  |

|------------------------------------------------|------------------------|------------------------|-------------------|-------------------|---------------------------|--|

| CPU Core                                       |                        |                        |                   |                   |                           |  |

| Peripherals                                    |                        |                        |                   |                   |                           |  |

| On-Chip<br>Static RAM                          | Not affected, reliable | Not affected, reliable |                   |                   | Affected, un-<br>reliable |  |

| Oscillator,<br>PLL                             |                        | Not affected           |                   |                   |                           |  |

| Port Pins                                      |                        |                        |                   |                   |                           |  |

| EVR The voltage<br>regulator is<br>switched or |                        | Not affected           |                   |                   |                           |  |

| FLASH                                          |                        |                        |                   |                   |                           |  |

| NMI                                            | Disabled               | Disabled               |                   |                   |                           |  |

Table 19 Effect of Reset on Device Functions

# 3.7.2 Booting Scheme

When the XC866 is reset, it must identify the type of configuration with which to start the different modes once the reset sequence is complete. Thus, boot configuration information that is required for activation of special modes and conditions needs to be applied by the external world through input pins. After power-on reset or hardware reset, the pins MBC, TMS and P0.0 collectively select the different boot options. **Table 20** shows the available boot options in the XC866.

| MBC | TMS | P0.0                                      | PC Start Value                                                                    |                   |  |

|-----|-----|-------------------------------------------|-----------------------------------------------------------------------------------|-------------------|--|

| 1   | 0   | x User Mode; on-chip OSC/PLL non-bypassed |                                                                                   | 0000 <sub>H</sub> |  |

| 0   | 0   | х                                         | BSL Mode; on-chip OSC/PLL non-bypassed                                            | 0000 <sub>H</sub> |  |

| 0   | 1   | 0                                         | OCDS Mode <sup>1)</sup> ; on-chip OSC/PLL non-<br>bypassed                        | 0000 <sub>H</sub> |  |

| 1   | 1   | 0                                         | Standalone User (JTAG) Mode <sup>2)</sup> ; on-chip OSC/PLL non-bypassed (normal) | 0000 <sub>H</sub> |  |

Table 20 XC866 Boot Selection

<sup>1)</sup> The OCDS mode is not accessible if Flash is protected.

<sup>2)</sup> Normal user mode with standard JTAG (TCK,TDI,TDO) pins for hot-attach purpose.

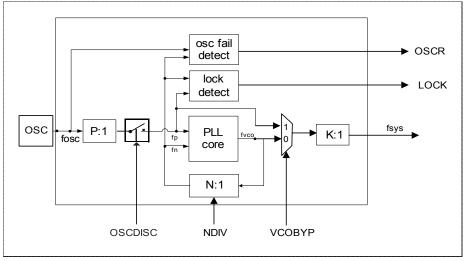

# 3.8 Clock Generation Unit

The Clock Generation Unit (CGU) allows great flexibility in the clock generation for the XC866. The power consumption is indirectly proportional to the frequency, whereas the performance of the microcontroller is directly proportional to the frequency. During user program execution, the frequency can be programmed for an optimal ratio between performance and power consumption. Therefore the power consumption can be adapted to the actual application state.

### Features:

- · Phase-Locked Loop (PLL) for multiplying clock source by different factors

- PLL Base Mode

- Prescaler Mode

- PLL Mode

- Power-down mode support

The CGU consists of an oscillator circuit and a PLL.In the XC866, the oscillator can be from either of these two sources: the on-chip oscillator (10 MHz) or the external oscillator (4 MHz to 12 MHz). The term "oscillator" is used to refer to both on-chip oscillator and external oscillator, unless otherwise stated. After the reset, the on-chip oscillator will be used by default. The external oscillator can be selected via software. In addition, the PLL provides a fail-safe logic to perform oscillator run and loss-of-lock detection. This allows emergency routines to be executed for system recovery or to perform system shut down.

Figure 23 CGU Block Diagram

# 3.11.2 Baud Rate Generation using Timer 1

In UART modes 1 and 3, Timer 1 can be used for generating the variable baud rates. In theory, this timer could be used in any of its modes. But in practice, it should be set into auto-reload mode (Timer 1 mode 2), with its high byte set to the appropriate value for the required baud rate. The baud rate is determined by the Timer 1 overflow rate and the value of SMOD as follows:

[3.1]

Mode 1, 3 baud rate=  $\frac{2^{\text{SMOD}} \times f_{\text{PCLK}}}{32 \times 2 \times (256 - \text{TH1})}$

# 3.12 Normal Divider Mode (8-bit Auto-reload Timer)

Setting bit FDM in register FDCON to 1 configures the fractional divider to normal divider mode, while at the same time disables baud rate generation (see **Figure 29**). Once the fractional divider is enabled (FDEN = 1), it functions as an 8-bit auto-reload timer (with no relation to baud rate generation) and counts up from the reload value with each input clock pulse. Bit field RESULT in register FDRES represents the timer value, while bit field STEP in register FDSTEP defines the reload value. At each timer overflow, an overflow flag (FDCON.NDOV) will be set and an interrupt request generated. This gives an output clock  $f_{MOD}$  that is 1/n of the input clock  $f_{DIV}$ , where n is defined by 256 - STEP.

The output frequency in normal divider mode is derived as follows:

$f_{MOD} = f_{DIV} \times \frac{1}{256 - STEP}$ [3.2]

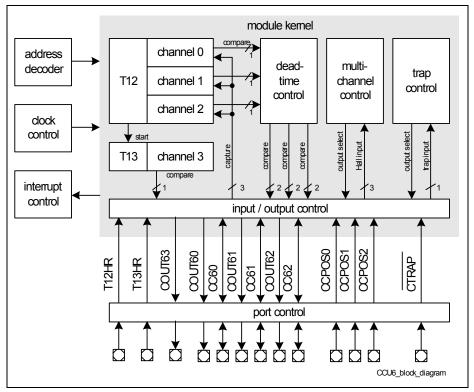

The block diagram of the CCU6 module is shown in Figure 32.

Figure 32 CCU6 Block Diagram

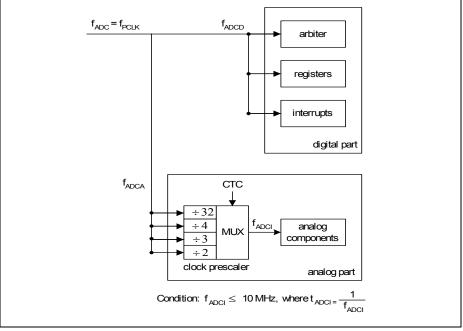

# 3.18.1 ADC Clocking Scheme

A common module clock  $f_{ADC}$  generates the various clock signals used by the analog and digital parts of the ADC module:

- f<sub>ADCA</sub> is input clock for the analog part.

- $f_{ADCI}$  is internal clock for the analog part (defines the time base for conversion length and the sample time). This clock is generated internally in the analog part, based on the input clock  $f_{ADCA}$  to generate a correct duty cycle for the analog components.

- f<sub>ADCD</sub> is input clock for the digital part.

The internal clock for the analog part  $f_{ADCI}$  is limited to a maximum frequency of 10 MHz. Therefore, the ADC clock prescaler must be programmed to a value that ensures  $f_{ADCI}$  does not exceed 10 MHz. The prescaler ratio is selected by bit field CTC in register GLOBCTR. A prescaling ratio of 32 can be selected when the maximum performance of the ADC is not required.

Figure 33 ADC Clocking Scheme

#### **Electrical Parameters**

# 4.2.3 ADC Characteristics

The values in the table below are given for an analog power supply between 4.5 V to 5.5 V. The ADC can be used with an analog power supply down to 3 V. But in this case, the analog parameters may show a reduced performance. All ground pins ( $V_{SS}$ ) must be externally connected to one single star point in the system. The voltage difference between the ground pins must not exceed 200mV.

| Parameter                                                    | Symbol            |           | Limit Values                            |                  |                            | Unit | Test Conditions/                       |

|--------------------------------------------------------------|-------------------|-----------|-----------------------------------------|------------------|----------------------------|------|----------------------------------------|

|                                                              |                   |           | min.                                    | typ .            | max.                       |      | Remarks                                |

| Analog reference voltage                                     | VARE              | -<br>SR   | V <sub>AGND</sub><br>+ 1                | V <sub>DDP</sub> | V <sub>DDP</sub><br>+ 0.05 | V    |                                        |

| Analog reference ground                                      | V <sub>AGN</sub>  | D<br>SR   | V <sub>SS</sub><br>- 0.05               | V <sub>SS</sub>  | V <sub>AREF</sub><br>- 1   | V    |                                        |

| Analog input<br>voltage range                                | V <sub>AIN</sub>  | SR        | V <sub>AGND</sub>                       | -                | V <sub>AREF</sub>          | V    |                                        |

| ADC clocks                                                   | f <sub>ADC</sub>  |           | -                                       | 20               | 40                         | MHz  | module clock                           |

|                                                              | f <sub>ADCI</sub> |           | -                                       | -                | 10                         | MHz  | internal analog clock<br>See Figure 33 |

| Sample time                                                  | t <sub>S</sub>    | СС        | (2 + INPCR0.STC) ×<br>t <sub>ADCI</sub> |                  |                            | μs   |                                        |

| Conversion time                                              | t <sub>C</sub>    | СС        | See Se                                  | ction 4.         | 2.3.1                      | μs   |                                        |

| Total unadjusted                                             | TUE <sup>1</sup>  | )CC       | -                                       | -                | ±1                         | LSB  | 8-bit conversion. <sup>2)</sup>        |

| error                                                        |                   |           | -                                       | -                | ±2                         | LSB  | 10-bit conversion.                     |

| Differential<br>Nonlinearity                                 | DNL               | СС        | -                                       | ±1               | -                          | LSB  | 10-bit conversion <sup>2)</sup>        |

| Integral<br>Nonlinearity                                     | INL               | СС        | -                                       | ±1               | -                          | LSB  | 10-bit conversion <sup>2)</sup>        |

| Offset                                                       | OFF               | СС        | -                                       | ±1               | -                          | LSB  | 10-bit conversion <sup>2)</sup>        |

| Gain                                                         | GAIN              | СС        | -                                       | ±1               | -                          | LSB  | 10-bit conversion <sup>2)</sup>        |

| Switched<br>capacitance at the<br>reference voltage<br>input | C <sub>ARE</sub>  | FSW<br>CC | -                                       | 10               | 20                         | pF   | 2)3)                                   |

#### Table 36ADC Characteristics (Operating Conditions apply; $V_{DDP}$ = 5V Range)

#### **Electrical Parameters**

# Table 40Power Down Current (Operating Conditions apply; $V_{\text{DDP}}$ = 3.3Vrange )

| Parameter                     | Symbol    | Limit Values                          |    | Unit | Test Condition<br>Remarks                                          |

|-------------------------------|-----------|---------------------------------------|----|------|--------------------------------------------------------------------|

|                               |           | typ. <sup>1)</sup> max. <sup>2)</sup> |    | -    |                                                                    |

| V <sub>DDP</sub> = 3.3V Range |           | -1                                    | 1  | 1    |                                                                    |

| Power-Down Mode <sup>3)</sup> | $I_{PDP}$ | 1                                     | 10 | μA   | $T_{\rm A}$ = + 25 °C. <sup>4</sup> )                              |

|                               |           | -                                     | 30 | μA   | T <sub>A</sub> = + 85 °C, XC866-<br>4FR, XC866-2FR <sup>4)5)</sup> |

|                               |           | -                                     | 35 | μA   | $T_{A}$ = + 85 °C, XC866-<br>1FR, ROM device <sup>4)5)</sup>       |

<sup>1)</sup> The typical  $I_{PDP}$  values are measured at  $V_{DDP}$  = 3.3 V.

$^{2)}\,$  The maximum  $I_{\rm PDP}$  values are measured at  $V_{\rm DDP}$  = 3.6 V.

<sup>3)</sup> I<sub>PDP</sub> (power-down mode) has a maximum value of 200  $\mu$ A at  $T_A$  = + 125 °C.

<sup>4)</sup> I<sub>PDP</sub> (power-down mode) is measured with: RESET = V<sub>DDP</sub>, V<sub>AGND</sub>= V<sub>SS</sub>, RXD/INT0= V<sub>DDP</sub>; rest of the ports are programmed to be input with either internal pull devices enabled or driven externally to ensure no floating inputs.

<sup>5)</sup> Not subject to production test, verified by design/characterization.

#### Package and Reliability

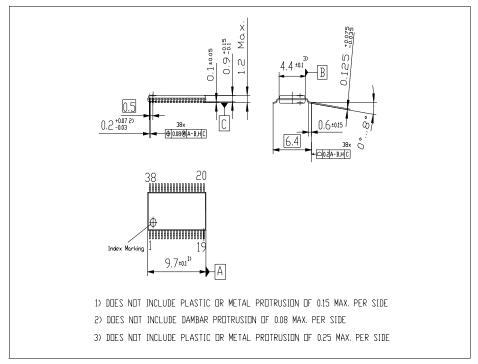

# 5.2 Package Outline

Figure 46 PG-TSSOP-38-4 Package Outline