Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Last Time Buy                                                                |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | XC800                                                                        |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 86MHz                                                                        |

| Connectivity               | SSI, UART/USART                                                              |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 19                                                                           |

| Program Memory Size        | 16KB (16K x 8)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 768 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                  |

| Data Converters            | A/D 8x10b                                                                    |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 38-TFSOP (0.173", 4.40mm Width)                                              |

| Supplier Device Package    | PG-TSSOP-38-4                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xc8664frabekxuma1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

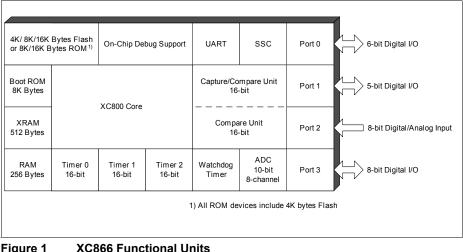

# 8-Bit Single-Chip Microcontroller XC800 Family

#### 1 **Summary of Features**

- High-performance XC800 Core •

- compatible with standard 8051 processor

- two clocks per machine cycle architecture (for memory access without wait state)

- two data pointers

- On-chip memory

- 8 Kbytes of Boot ROM

- 256 bytes of RAM

- 512 bytes of XRAM

- 4/8/16 Kbytes of Flash; or 8/16 Kbytes of ROM, with additional 4 Kbytes of Flash (includes memory protection strategy)

- I/O port supply at 3.3 V/5.0 V and core logic supply at 2.5 V (generated by embedded voltage regulator)

(further features are on next page)

#### Summary of Features

Features (continued):

infineon

- Reset generation

- Power-On reset

- Hardware reset

- Brownout reset for core logic supply

- Watchdog timer reset

- Power-Down Wake-up reset

- On-chip OSC and PLL for clock generation

- PLL loss-of-lock detection

- Power saving modes

- slow-down mode

- idle mode

- power-down mode with wake-up capability via RXD or EXINT0

- clock gating control to each peripheral

- Programmable 16-bit Watchdog Timer (WDT)

- Four ports

- 19 pins as digital I/O

- 8 pins as digital/analog input

- 8-channel, 10-bit ADC

- Three 16-bit timers

- Timer 0 and Timer 1 (T0 and T1)

- Timer 2

- · Capture/compare unit for PWM signal generation (CCU6)

- Full-duplex serial interface (UART)

- Synchronous serial channel (SSC)

- · On-chip debug support

- 1 Kbyte of monitor ROM (part of the 8-Kbyte Boot ROM)

- 64 bytes of monitor RAM

- PG-TSSOP-38 pin package

- Temperature range T<sub>A</sub>:

- SAF (-40 to 85 °C)

- SAK (-40 to 125 °C)

# infineon

# **Summary of Features**

#### Table 2Device Summary

|     | -                  |     |    |   |    |            |

|-----|--------------------|-----|----|---|----|------------|

|     | SAK-XC866*-1FRI 3V | 3.3 | -  | 4 | -  | Industrial |

|     | SAF-XC866*-4FRA 3V | 3.3 | 12 | 4 | _  | Automotive |

|     | SAF-XC866*-4FRI 3V | 3.3 | 12 | 4 | _  | Industrial |

|     | SAF-XC866*-2FRA 3V | 3.3 | 4  | 4 | _  | Automotive |

|     | SAF-XC866*-2FRI 3V | 3.3 | 4  | 4 | -  | Industrial |

|     | SAF-XC866*-1FRA 3V | 3.3 | -  | 4 | -  | Automotive |

|     | SAF-XC866*-1FRI 3V | 3.3 | -  | 4 | -  | Industrial |

| ROM | SAK-XC866*-4RRA    | 5.0 | -  | 4 | 16 | Automotive |

|     | SAK-XC866*-4RRI    | 5.0 | -  | 4 | 16 | Industrial |

|     | SAK-XC866*-2RRA    | 5.0 | -  | 4 | 8  | Automotive |

|     | SAK-XC866*-2RRI    | 5.0 | -  | 4 | 8  | Industrial |

|     | SAF-XC866*-4RRA    | 5.0 | -  | 4 | 16 | Automotive |

|     | SAF-XC866*-4RRI    | 5.0 | -  | 4 | 16 | Industrial |

|     | SAF-XC866*-2RRA    | 5.0 | _  | 4 | 8  | Automotive |

|     | SAF-XC866*-2RRI    | 5.0 | -  | 4 | 8  | Industrial |

|     | SAK-XC866*-4RRA 3V | 3.3 | -  | 4 | 16 | Automotive |

|     | SAK-XC866*-4RRI 3V | 3.3 | -  | 4 | 16 | Industrial |

|     | SAK-XC866*-2RRA 3V | 3.3 | -  | 4 | 8  | Automotive |

|     | SAK-XC866*-2RRI 3V | 3.3 | _  | 4 | 8  | Industrial |

|     | SAF-XC866*-4RRA 3V | 3.3 | -  | 4 | 16 | Automotive |

|     | SAF-XC866*-4RRI 3V | 3.3 | -  | 4 | 16 | Industrial |

|     | SAF-XC866*-2RRA 3V | 3.3 | -  | 4 | 8  | Automotive |

|     | SAF-XC866*-2RRI 3V | 3.3 | -  | 4 | 8  | Industrial |

1) Industrial is not for Automotive usage

<sup>2)</sup> The flash memory (P-Flash and D-Flash) can be used for code or data.

Note: The asterisk (\*) above denotes the device configuration letters from Table 1.

# XC866

# **General Device Information**

| Symbol | Pin<br>Number | Туре | Reset<br>State | Function                               |                                                                                                              |

|--------|---------------|------|----------------|----------------------------------------|--------------------------------------------------------------------------------------------------------------|

| P1     |               | I/O  |                | port. It can b                         | -bit bidirectional general purpose I/O<br>e used as alternate functions for the<br>5, UART, and the SSC.     |

| P1.0   | 27            |      | PU             | RXD_0<br>T2EX                          | UART Receive Data Input<br>Timer 2 External Trigger Input                                                    |

| P1.1   | 28            |      | PU             | EXINT3<br>TDO_1<br>TXD_0               | External Interrupt Input 3<br>JTAG Serial Data Output<br>UART Transmit Data Output/<br>Clock Output          |

| P1.5   | 29            |      | PU             | CCPOS0_1<br>EXINT5<br>EXF2_0<br>RXDO_0 | CCU6 Hall Input 0<br>External Interrupt Input 5<br>TImer 2 External Flag Output<br>UART Transmit Data Output |

| P1.6   | 9             |      | PU             | CCPOS1_1<br>T12HR_0<br>EXINT6          | CCU6 Hall Input 1<br>CCU6 Timer 12 Hardware Run<br>Input<br>External Interrupt Input 6                       |

| P1.7   | 10            |      | PU             | CCPOS2_1<br>T13HR_0                    | CCU6 Hall Input 2<br>CCU6 Timer 13 Hardware Run<br>Input                                                     |

| _      |               |      |                |                                        | .6 can be used as a software chip<br>t for the SSC.                                                          |

# Table 3Pin Definitions and Functions (cont'd)

# 3.2.2 Special Function Register

The Special Function Registers (SFRs) occupy direct internal data memory space in the range  $80_H$  to FF<sub>H</sub>. All registers, except the program counter, reside in the SFR area. The SFRs include pointers and registers that provide an interface between the CPU and the on-chip peripherals. As the 128-SFR range is less than the total number of registers required, address extension mechanisms are required to increase the number of addressable SFRs. The address extension mechanisms include:

- Mapping

- Paging

# 3.2.2.1 Address Extension by Mapping

Address extension is performed at the system level by mapping. The SFR area is extended into two portions: the standard (non-mapped) SFR area and the mapped SFR area. Each portion supports the same address range  $80_H$  to FF<sub>H</sub>, bringing the number of addressable SFRs to 256. The extended address range is not directly controlled by the CPU instruction itself, but is derived from bit RMAP in the system control register SYSCON0 at address  $8F_H$ . To access SFRs in the mapped area, bit RMAP in SFR SYSCON0 must be set. Alternatively, the SFRs in the standard area can be accessed by clearing bit RMAP. The SFR area can be selected as shown in **Figure 8**.

#### SYSCON0 System Control Register 0 Reset Value: 00<sub>H</sub> 2 1 0 7 6 5 4 3 0 1 0 RMAP r rw r rw

| Field | Bits    | Туре | Description                                                                                                                                                               |

|-------|---------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RMAP  | 0       | rw   | <ul> <li>Special Function Register Map Control</li> <li>The access to the standard SFR area is enabled.</li> <li>The access to the mapped SFR area is enabled.</li> </ul> |

| 1     | 2       | rw   | <b>Reserved</b><br>Returns the last value if read; should be written<br>with 1.                                                                                           |

| 0     | 1,[7:3] | r    | <b>Reserved</b><br>Returns 0 if read; should be written with 0.                                                                                                           |

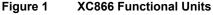

In order to access a register located in a page different from the actual one, the current page must be left. This is done by reprogramming the bit field PAGE in the page register. Only then can the desired access be performed.

If an interrupt routine is initiated between the page register access and the module register access, and the interrupt needs to access a register located in another page, the current page setting can be saved, the new one programmed and finally, the old page setting restored. This is possible with the storage fields STx (x = 0 - 3) for the save and restore action of the current page setting. By indicating which storage bit field should be used in parallel with the new page value, a single write operation can:

- Save the contents of PAGE in STx before overwriting with the new value (this is done in the beginning of the interrupt routine to save the current page setting and program the new page number); or

- Overwrite the contents of PAGE with the contents of STx, ignoring the value written to the bit positions of PAGE

(this is done at the end of the interrupt routine to restore the previous page setting before the interrupt occurred)

## Figure 10 Storage Elements for Paging

With this mechanism, a certain number of interrupt routines (or other routines) can perform page changes without reading and storing the previously used page information. The use of only write operations makes the system simpler and faster. Consequently, this mechanism significantly improves the performance of short interrupt routines.

The XC866 supports local address extension for:

- Parallel Ports

- Analog-to-Digital Converter (ADC)

- Capture/Compare Unit 6 (CCU6)

- System Control Registers

| C1 <sub>H</sub> | T2_T2MOD<br>Timer 2 Mode Register | Reset: 00 <sub>H</sub> | Bit Field | T2<br>REGS | T2<br>RHEN | EDGE<br>SEL | PREN | T2PRE  | DCEN |  |

|-----------------|-----------------------------------|------------------------|-----------|------------|------------|-------------|------|--------|------|--|

|                 |                                   |                        | Туре      | rw         | rw         | rw          | rw   | rw     | rw   |  |

| C2 <sub>H</sub> | T2_RC2L                           | Reset: 00 <sub>H</sub> | Bit Field |            |            |             | RC2  | [7:0]  |      |  |

|                 | Timer 2 Reload/Capture            | Register Low           | Туре      | rwh        |            |             |      |        |      |  |

| C3 <sub>H</sub> | T2_RC2H                           | Reset: 00 <sub>H</sub> | Bit Field | RC2[15:8]  |            |             |      |        |      |  |

|                 | Timer 2 Reload/Capture            | Register High          | Туре      | rwh        |            |             |      |        |      |  |

| C4 <sub>H</sub> | T2_T2L                            | Reset: 00 <sub>H</sub> | Bit Field |            |            |             | THL  | 2[7:0] |      |  |

|                 | Timer 2 Register Low              |                        | Туре      | rwh        |            |             |      |        |      |  |

| C5 <sub>H</sub> | T2_T2H Reset: 00 <sub>H</sub>     |                        | Bit Field | THL2[15:8] |            |             |      |        |      |  |

|                 | Timer 2 Register High             |                        | Туре      |            |            |             | rv   | vh     |      |  |

The CCU6 SFRs can be accessed in the standard memory area (RMAP = 0).

# Table 13 CCU6 Register Overview

| Addr            | Register Name                                                                | Bit       | 7          | 6          | 5           | 4          | 3          | 2          | 1          | 0          |  |

|-----------------|------------------------------------------------------------------------------|-----------|------------|------------|-------------|------------|------------|------------|------------|------------|--|

| RMAP =          | 0                                                                            |           |            | 1          |             |            |            |            |            | 1          |  |

| A3 <sub>H</sub> | CCU6_PAGE Reset: 00 <sub>H</sub>                                             | Bit Field | C          | P          | ST          | NR         | 0          |            | PAGE       |            |  |

|                 | Page Register for CCU6                                                       | Туре      | ١          | v          | w r rwh     |            |            |            |            |            |  |

| RMAP =          | 0, Page 0                                                                    |           |            |            |             |            |            |            |            |            |  |

| 9A <sub>H</sub> | CCU6_CC63SRL Reset: 00 <sub>H</sub><br>Capture/Compare Shadow Register for   | Bit Field | eld CC63SL |            |             |            |            |            |            |            |  |

|                 | Channel CC63 Low                                                             | Туре      |            |            |             | r          | w          |            |            |            |  |

| 9B <sub>H</sub> | CCU6_CC63SRH Reset: 00 <sub>H</sub><br>Capture/Compare Shadow Register for   | Bit Field |            |            |             | CC6        | 3SH        |            |            |            |  |

|                 | Channel CC63 High                                                            | Туре      |            |            |             | r          | w          |            |            |            |  |

| 9C <sub>H</sub> | CCU6_TCTR4L Reset: 00 <sub>H</sub><br>Timer Control Register 4 Low           | Bit Field | T12<br>STD | T12<br>STR | (           | 0          | DTRES      | T12<br>RES | T12RS      | T12RR      |  |

|                 |                                                                              | Туре      | w          | w          |             | r          | w          | w          | w          | w          |  |

| 9D <sub>H</sub> | CCU6_TCTR4H Reset: 00 <sub>H</sub><br>Timer Control Register 4 High          | Bit Field | T13<br>STD | T13<br>STR |             | 0          |            | T13<br>RES | T13RS      | T13RR      |  |

|                 |                                                                              | Туре      | w          | w          | r           |            |            | w          | w          | w          |  |

| 9E <sub>H</sub> | CCU6_MCMOUTSL Reset: 00 <sub>H</sub><br>Multi-Channel Mode Output Shadow     | Bit Field | STRM<br>CM | 0          | MCMPS       |            |            |            |            |            |  |

|                 | Register Low                                                                 | Туре      | w          | r          | rw          |            |            |            |            |            |  |

| 9F <sub>H</sub> | CCU6_MCMOUTSH Reset: 00 <sub>H</sub>                                         | Bit Field | STRHP      | 0          | CURHS EXPHS |            |            |            |            |            |  |

|                 | Multi-Channel Mode Output Shadow<br>Register High                            | Туре      | w          | r          |             | rw         |            | rw         |            |            |  |

| A4 <sub>H</sub> | CCU6_ISRL Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Status         | Bit Field | RT12P<br>M | RT12O<br>M | RCC62<br>F  | RCC62<br>R | RCC61<br>F | RCC61<br>R | RCC60<br>F | RCC60<br>R |  |

|                 | Reset Register Low                                                           | Туре      | w          | w          | w           | w          | w          | w          | w          | w          |  |

| A5 <sub>H</sub> | CCU6_ISRH Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Status         | Bit Field | RSTR       | RIDLE      | RWHE        | RCHE       | 0          | RTRPF      | RT13<br>PM | RT13<br>CM |  |

|                 | Reset Register High                                                          | Туре      | w          | w          | w           | w          | r          | w          | w          | w          |  |

| A6 <sub>H</sub> | CCU6_CMPMODIFL Reset: 00 <sub>H</sub><br>Compare State Modification Register | Bit Field | 0          | MCC63<br>S |             | 0          |            | MCC62<br>S | MCC61<br>S | MCC60<br>S |  |

|                 | Low                                                                          | Туре      | r          | w          | r           |            |            | w          | w          | w          |  |

| A7 <sub>H</sub> | CCU6_CMPMODIFH Reset: 00 <sub>H</sub><br>Compare State Modification Register | Bit Field | 0          | MCC63<br>R | 3 0         |            |            | MCC62<br>R | MCC61<br>R | MCC60<br>R |  |

|                 | High                                                                         | Туре      | r          | w          | r w v       |            |            | w          | w          |            |  |

| FA <sub>H</sub> | Capture/Compare Shadow Register for                                          |           |            |            |             | CC         | 60SL       |            |            |            |  |

|                 | Channel CC60 Low                                                             | Туре      |            |            |             | n          | wh         |            |            |            |  |

# Table 13 CCU6 Register Overview (cont'd)

| Addr            | Register Name                                                             | Bit       | 7        | 6              | 5            | 4          | 3            | 2          | 1            | 0          |  |

|-----------------|---------------------------------------------------------------------------|-----------|----------|----------------|--------------|------------|--------------|------------|--------------|------------|--|

| FF <sub>H</sub> | CCU6_TRPCTRH Reset: 00 <sub>H</sub>                                       | Bit Field |          | TRPEN          |              | 1          | TR           | PEN        |              | 1          |  |

|                 | Trap Control Register High                                                |           | N        | 13             |              |            |              |            |              |            |  |

|                 |                                                                           | Туре      | rw       | rw             |              |            | r            | w          |              |            |  |

| RMAP =          | 0, Page 3                                                                 |           |          |                |              |            |              |            |              |            |  |

| 9A <sub>H</sub> | CCU6_MCMOUTL Reset: 00 <sub>H</sub><br>Multi-Channel Mode Output Register | Bit Field | 0        | R              |              |            | MC           | MP         |              |            |  |

|                 | Low                                                                       | Туре      | r        | rh             |              |            | r            | h          |              |            |  |

| 9B <sub>H</sub> | CCU6_MCMOUTH Reset: 00 <sub>H</sub><br>Multi-Channel Mode Output Register | Bit Field | (        | )              |              | CURH       |              |            | EXPH         |            |  |

|                 | High                                                                      | Туре      | 1        | r              |              | rh         |              |            | rh           |            |  |

| 9C <sub>H</sub> | CCU6_ISL Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Status       | Bit Field | T12PM    | T12OM          | ICC62F       | R          | ICC61F       | R          | ICC60F       | ICC60<br>R |  |

|                 | Register Low                                                              | Туре      | rh       | rh             | rh           | rh         | rh           | rh         | rh           | rh         |  |

| 9D <sub>H</sub> | CCU6_ISH Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Status       | Bit Field | STR      | IDLE           | WHE          | CHE        | TRPS         | TRPF       | T13PM        | T13CM      |  |

|                 | Register High                                                             | Туре      | rh       | rh             | rh           | rh         | rh           | rh         | rh           | rh         |  |

| 9E <sub>H</sub> | CCU6_PISEL0L Reset: 00 <sub>H</sub>                                       | Bit Field | IST      | RP             | ISC          | C62        | ISC          | C61        | ISC          | C60        |  |

|                 | Port Input Select Register 0 Low                                          | Туре      | rw rw rw |                |              |            |              |            |              |            |  |

| 9F <sub>H</sub> | CCU6_PISEL0H Reset: 00 <sub>H</sub><br>Port Input Select Register 0 High  | Bit Field | IST1     | IST12HR ISPOS2 |              | OS2        | ISPOS1       |            | ISPOS0       |            |  |

|                 |                                                                           | Туре      | rw rw rw |                |              |            |              | w          | rw           |            |  |

| A4 <sub>H</sub> | CCU6_PISEL2 Reset: 00 <sub>H</sub>                                        | Bit Field |          |                | (            | C          |              |            | IST1         | IST13HR    |  |

|                 | Port Input Select Register 2                                              | Туре      |          |                |              | r          |              |            | n            | w          |  |

| FA <sub>H</sub> | CCU6_T12L Reset: 00 <sub>H</sub>                                          | Bit Field |          |                |              | T12        | CVL          |            |              |            |  |

|                 | Timer T12 Counter Register Low                                            | Туре      |          |                |              | n          | vh           |            |              |            |  |

| FB <sub>H</sub> | CCU6_T12H Reset: 00 <sub>H</sub>                                          | Bit Field |          |                |              | T12        | CVH          |            |              |            |  |

|                 | Timer T12 Counter Register High                                           | Туре      |          |                |              | n          | vh           |            |              |            |  |

| FC <sub>H</sub> | CCU6_T13L Reset: 00 <sub>H</sub>                                          | Bit Field |          |                |              | T13        | CVL          |            |              |            |  |

|                 | Timer T13 Counter Register Low                                            | Туре      |          |                |              | n          | vh           |            |              |            |  |

| FD <sub>H</sub> | CCU6_T13H Reset: 00 <sub>H</sub>                                          | Bit Field |          |                |              | T13        | CVH          |            |              |            |  |

|                 | Timer T13 Counter Register High                                           | Туре      |          |                |              | n          | vh           |            |              |            |  |

| FE <sub>H</sub> | CCU6_CMPSTATL Reset: 00 <sub>H</sub><br>Compare State Register Low        | Bit Field | 0        | CC63<br>ST     | CCPO<br>S2   | CCPO<br>S1 | CCPO<br>S0   | CC62<br>ST | CC61<br>ST   | CC60<br>ST |  |

|                 |                                                                           | Туре      | r        | rh             | rh           | rh         | rh           | rh         | rh           | rh         |  |

| FF <sub>H</sub> | CCU6_CMPSTATH Reset: 00 <sub>H</sub><br>Compare State Register High       | Bit Field | T13IM    | COUT<br>63PS   | COUT<br>62PS | CC62<br>PS | COUT<br>61PS | CC61<br>PS | COUT<br>60PS | CC60<br>PS |  |

|                 |                                                                           | Туре      | rwh      | rwh            | rwh          | rwh        | rwh          | rwh        | rwh          | rwh        |  |

The SSC SFRs can be accessed in the standard memory area (RMAP = 0).

# Table 14SSC Register Overview

| Addr            | Register Name                            |                        | Bit       | 7  | 6  | 5  | 4  | 3 | 2   | 1   | 0   |  |

|-----------------|------------------------------------------|------------------------|-----------|----|----|----|----|---|-----|-----|-----|--|

| RMAP =          | 0                                        |                        | •         |    |    |    |    |   |     |     |     |  |

| A9 <sub>H</sub> | SSC_PISEL                                | Reset: 00 <sub>H</sub> | Bit Field |    |    | 0  |    |   | CIS | SIS | MIS |  |

|                 | Port Input Select Regist                 | er                     | Туре      |    |    | r  |    |   | rw  | rw  | rw  |  |

| AA <sub>H</sub> | SSC_CONL                                 | Reset: 00 <sub>H</sub> | Bit Field | LB | PO | PH | HB |   | В   | М   |     |  |

|                 | Control Register Low<br>Programming Mode |                        | Туре      | rw | rw | rw | rw |   | r   | w   |     |  |

|                 | Operating Mode                           |                        | Bit Field |    | 0  |    |    |   | BC  |     |     |  |

|                 |                                          |                        | Туре      |    |    | r  |    |   | r   | h   |     |  |

# 3.7 Reset Control

The XC866 has five types of reset: power-on reset, hardware reset, watchdog timer reset, power-down wake-up reset, and brownout reset.

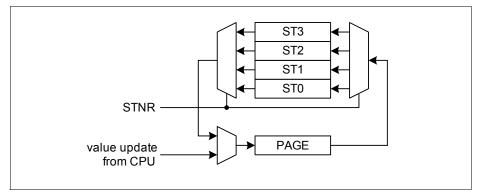

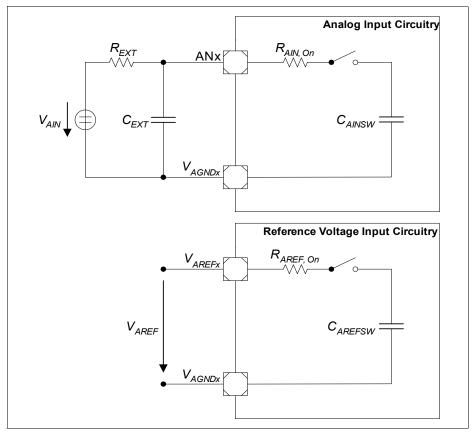

When the XC866 is first powered up, the status of certain pins (see **Table 20**) must be defined to ensure proper start operation of the device. At the end of a reset sequence, the sampled values are latched to select the desired boot option, which cannot be modified until the next power-on reset or hardware reset. This guarantees stable conditions during the normal operation of the device.

In order to power up the system properly, the external reset pin  $\overrightarrow{\text{RESET}}$  must be asserted until  $V_{\text{DDC}}$  reaches  $0.9^* V_{\text{DDC}}$ . The delay of external reset can be realized by an external capacitor at  $\overrightarrow{\text{RESET}}$  pin. This capacitor value must be selected so that  $V_{\text{RESET}}$  reaches 0.4 V, but not before  $V_{\text{DDC}}$  reaches 0.9\*  $V_{\text{DDC}}$ .

A typical application example is shown in **Figure 21**.  $V_{DDP}$  capacitor value is 300 nF.  $V_{DDC}$  capacitor value is 220 nF. The capacitor connected to RESET pin is 100 nF.

Typically, the time taken for  $V_{DDC}$  to reach  $0.9^*V_{DDC}$  is less than 50 µs once  $V_{DDP}$  reaches 2.3V. Hence, based on the condition that 10% to 90%  $V_{DDP}$  (slew rate) is less than 500 µs, the RESET pin should be held low for 500 µs typically. See **Figure 22**.

The clock system provides three ways to generate the system clock:

## PLL Base Mode

The system clock is derived from the VCO base (free running) frequency clock divided by the K factor.

$$f_{SYS} = f_{VCObase} \times \frac{1}{K}$$

## Prescaler Mode (VCO Bypass Operation)

In VCO bypass operation, the system clock is derived from the oscillator clock, divided by the P and K factors.

$$f_{SYS} = f_{OSC} \times \frac{1}{P \times K}$$

#### PLL Mode

The system clock is derived from the oscillator clock, multiplied by the N factor, and divided by the P and K factors. Both VCO bypass and PLL bypass must be inactive for this PLL mode. The PLL mode is used during normal system operation.

$$f_{SYS} = f_{OSC} \times \frac{N}{P \times K}$$

**Table 3-1** shows the settings of bits OSCDISC and VCOBYP for different clock mode selection.

| OSCDISC | VCOBYP | Clock Working Modes |  |

|---------|--------|---------------------|--|

| 0       | 0      | PLL Mode            |  |

| 0       | 1      | Prescaler Mode      |  |

| 1       | 0      | PLL Base Mode       |  |

| 1       | 1      | PLL Base Mode       |  |

# Table 3-1 Clock Mode Selection

Note: When oscillator clock is disconnected from PLL, the clock mode is PLL Base mode regardless of the setting of VCOBYP bit.

## **System Frequency Selection**

For the XC866, the values of P and K are fixed to "1" and "2", respectively. In order to obtain the required system frequency,  $f_{sys}$ , the value of N can be selected by bit NDIV for different oscillator inputs. **Table 21** provides examples on how  $f_{sys}$  = 80 MHz can be obtained for the different oscillator sources.

XC866

# 3.11.1 Baud-Rate Generator

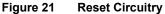

The baud-rate generator is based on a programmable 8-bit reload value, and includes divider stages (i.e., prescaler and fractional divider) for generating a wide range of baud rates based on its input clock  $f_{PCLK}$ , see **Figure 29**.

#### Figure 29 Baud-rate Generator Circuitry

The baud rate timer is a count-down timer and is clocked by either the output of the fractional divider ( $f_{MOD}$ ) if the fractional divider is enabled (FDCON.FDEN = 1), or the output of the prescaler ( $f_{DIV}$ ) if the fractional divider is disabled (FDEN = 0). For baud rate generation, the fractional divider must be configured to fractional divider mode (FDCON.FDM = 0). This allows the baud rate control run bit BCON.R to be used to start or stop the baud rate timer. At each timer underflow, the timer is reloaded with the 8-bit reload value in register BG and one clock pulse is generated for the serial channel.

Enabling the fractional divider in normal divider mode (FDEN = 1 and FDM = 1) stops the baud rate timer and nullifies the effect of bit BCON.R. See **Section 3.12**.

The baud rate  $(f_{BR})$  value is dependent on the following parameters:

- Input clock f<sub>PCLK</sub>

- Prescaling factor (2<sup>BRPRE</sup>) defined by bit field BRPRE in register BCON

- Fractional divider (STEP/256) defined by register FDSTEP (to be considered only if fractional divider is enabled and operating in fractional divider mode)

115.2 kHz, using different module clock frequencies. The fractional divider is enabled (fractional divider mode) and the corresponding parameter settings are shown.

# Table 27 Deviation Error for UART with Fractional Divider enabled

| f <sub>PCLK</sub> | Prescaling Factor<br>(2 <sup>BRPRE</sup> ) | Reload Value<br>(BR_VALUE + 1) | STEP                   | Deviation<br>Error |

|-------------------|--------------------------------------------|--------------------------------|------------------------|--------------------|

| 26.67 MHz         | 1                                          | 10 (A <sub>H</sub> )           | 177 (B1 <sub>H</sub> ) | +0.03 %            |

| 13.33 MHz         | 1                                          | 7 (7 <sub>H</sub> )            | 248 (F8 <sub>H</sub> ) | +0.11 %            |

| 6.67 MHz          | 1                                          | 3 (3 <sub>H</sub> )            | 212 (D4 <sub>H</sub> ) | -0.16 %            |

# 3.17 Capture/Compare Unit 6

The Capture/Compare Unit 6 (CCU6) provides two independent timers (T12, T13), which can be used for Pulse Width Modulation (PWM) generation, especially for AC-motor control. The CCU6 also supports special control modes for block commutation and multi-phase machines.

The timer T12 can function in capture and/or compare mode for its three channels. The timer T13 can work in compare mode only.

The multi-channel control unit generates output patterns, which can be modulated by T12 and/or T13. The modulation sources can be selected and combined for the signal modulation.

## Timer T12 Features:

- Three capture/compare channels, each channel can be used either as a capture or as a compare channel

- Supports generation of a three-phase PWM (six outputs, individual signals for highside and lowside switches)

- 16-bit resolution, maximum count frequency = peripheral clock frequency

- · Dead-time control for each channel to avoid short-circuits in the power stage

- Concurrent update of the required T12/13 registers

- · Generation of center-aligned and edge-aligned PWM

- · Supports single-shot mode

- · Supports many interrupt request sources

- · Hysteresis-like control mode

## Timer T13 Features:

- · One independent compare channel with one output

- 16-bit resolution, maximum count frequency = peripheral clock frequency

- Can be synchronized to T12

- · Interrupt generation at period-match and compare-match

- Supports single-shot mode

## Additional Features:

- · Implements block commutation for Brushless DC-drives

- Position detection via Hall-sensor pattern

- · Automatic rotational speed measurement for block commutation

- Integrated error handling

- Fast emergency stop without CPU load via external signal (CTRAP)

- · Control modes for multi-channel AC-drives

- · Output levels can be selected and adapted to the power stage

# 3.19 On-Chip Debug Support

The On-Chip Debug Support (OCDS) provides the basic functionality required for the software development and debugging of XC800-based systems.

The OCDS design is based on these principles:

- · use the built-in debug functionality of the XC800 Core

- · add a minimum of hardware overhead

- provide support for most of the operations by a Monitor Program

- use standard interfaces to communicate with the Host (a Debugger)

## Features:

- · Set breakpoints on instruction address and within a specified address range

- Set breakpoints on internal RAM address

- · Support unlimited software breakpoints in Flash/RAM code region

- Process external breaks

- Step through the program code

The OCDS functional blocks are shown in **Figure 35**. The Monitor Mode Control (MMC) block at the center of OCDS system brings together control signals and supports the overall functionality. The MMC communicates with the XC800 Core, primarily via the Debug Interface, and also receives reset and clock signals. After processing memory address and control signals from the core, the MMC provides proper access to the dedicated extra-memories: a Monitor ROM (holding the code) and a Monitor RAM (for work-data and Monitor-stack). The OCDS system is accessed through the JTAG<sup>1</sup>, which is an interface dedicated exclusively for testing and debugging activities and is not normally used in an application. The dedicated MBC pin is used for external configuration and debugging control.

Note: All the debug functionality described here can normally be used only after XC866 has been started in OCDS mode.

<sup>&</sup>lt;sup>1)</sup> The pins of the JTAG port can be assigned to either Port 0 (primary) or Ports 1 and 2 (secondary). User must set the JTAG pins (TCK and TDI) as input during connection with the OCDS system.

<sup>4)</sup> Not subjected to production test, verified by design/characterization. However, for applications with strict low power-down current requirements, it is mandatory that no active voltage source is supplied at any GPIO pin when VDDP is powered off.

# 4.2.3.1 ADC Conversion Timing

Conversion time,  $t_C = t_{ADC} \times (1 + r \times (3 + n + STC))$ , where r = CTC + 2 for CTC =  $00_B$ ,  $01_B$  or  $10_B$ , r = 32 for CTC =  $11_B$ , CTC = Conversion Time Control (GLOBCTR.CTC), STC = Sample Time Control (INPCR0.STC), n = 8 or 10 (for 8-bit and 10-bit conversion respectively),  $t_{ADC} = 1 / f_{ADC}$

# 4.2.4 Power Supply Current

# Table 37Power Supply Current Parameters (Operating Conditions apply; $V_{\text{DDP}}$ = 5V range )

| Parameter                          | Symbol           | Limit              | Values             | Unit | <b>Test Condition</b>                  |  |

|------------------------------------|------------------|--------------------|--------------------|------|----------------------------------------|--|

|                                    |                  | typ. <sup>1)</sup> | max. <sup>2)</sup> | 1    | Remarks                                |  |

| V <sub>DDP</sub> = 5V Range        |                  |                    |                    | 1    | I                                      |  |

| Active Mode                        | I <sub>DDP</sub> | 22.6               | 24.5               | mA   | 3)                                     |  |

| Idle Mode                          | I <sub>DDP</sub> | 17.2               | 19.7               | mA   | XC866-4FR,<br>XC866-2FR <sup>4)</sup>  |  |

|                                    |                  | 12.5               | 14                 | mA   | XC866-1FR,<br>ROM device <sup>4)</sup> |  |

| Active Mode with slow-down enabled | I <sub>DDP</sub> | 7.2                | 8.2                | mA   | XC866-4FR,<br>XC866-2FR <sup>5)</sup>  |  |

|                                    |                  | 5.6                | 7.5                | mA   | XC866-1FR,<br>ROM device <sup>5)</sup> |  |

| Idle Mode with slow-down enabled   | I <sub>DDP</sub> | 7.1                | 8                  | mA   | XC866-4FR,<br>XC866-2FR <sup>6)</sup>  |  |

|                                    |                  | 5.1                | 7.2                | mA   | XC866-1FR,<br>ROM device <sup>6)</sup> |  |

<sup>1)</sup> The typical  $I_{\text{DDP}}$  values are periodically measured at  $T_{\text{A}}$  = + 25 °C and  $V_{\text{DDP}}$  = 5.0 V.

<sup>2)</sup> The maximum  $I_{\text{DDP}}$  values are measured under worst case conditions ( $T_{\text{A}}$  = + 125 °C and  $V_{\text{DDP}}$  = 5.5 V).

- <sup>3)</sup> I<sub>DDP</sub> (active mode) is measured with: CPU clock and input clock to all peripherals running at 26.7 MHz(set by on-chip oscillator of 10 MHz and NDIV in PLL\_CON to 0010<sub>B</sub>), RESET =  $V_{DDP}$ , no load on ports.

- <sup>4)</sup> I<sub>DDP</sub> (idle mode) is measured with: <u>CPU clock disabled</u>, watchdog timer disabled, input clock to all peripherals enabled and running at 26.7 MHz, <u>RESET</u> = V<sub>DDP</sub>, no load on ports.

- <sup>5)</sup> I<sub>DDP</sub> (active mode with slow-down mode) is measured with: CPU clock and input clock to all peripherals running at 833 KHz by setting CLKREL in CMCON to 0101<sub>B</sub>, RESET = V<sub>DDP</sub>, no load on ports.

- <sup>6)</sup> I<sub>DDP</sub> (idle mode with slow-down mode) is measured with: CPU clock disabled, watchdog timer disabled, input <u>clock to all peripherals enabled and running at 833 KHz by setting CLKREL in CMCON to 0101<sub>B</sub>, RESET = V<sub>DDP</sub>, no load on ports.</u>

# 4.3.3 Power-on Reset and PLL Timing

| Table 42 | Power-On Reset and PLL Timing (Operating Conditions apply) |

|----------|------------------------------------------------------------|

|----------|------------------------------------------------------------|

| Parameter                           | Symbol                   | Limit Values |      |      | Unit | Test Conditions                                     |  |

|-------------------------------------|--------------------------|--------------|------|------|------|-----------------------------------------------------|--|

|                                     |                          | min.         | typ. | max. |      |                                                     |  |

| Pad operating voltage               | V <sub>PAD</sub> CC      | 2.3          | -    | -    | V    |                                                     |  |

| On-Chip Oscillator<br>start-up time | t <sub>OSCST</sub><br>CC | _            | -    | 500  | ns   |                                                     |  |

| Flash initialization time           | t <sub>FINIT</sub> CC    | -            | 160  | -    | μs   |                                                     |  |

| RESET hold time <sup>1)</sup>       | t <sub>RST</sub> SR      | -            | 500  | _    | μs   | $V_{\text{DDP}}$ rise time (10% – 90%) $\leq$ 500µs |  |

| PLL lock-in in time                 | t <sub>LOCK</sub> CC     | -            | -    | 200  | μs   |                                                     |  |

| PLL accumulated jitter              | D <sub>P</sub>           | -            | -    | 0.7  | ns   | 2)                                                  |  |

<sup>1)</sup> RESET signal has to be active (low) until  $V_{\text{DDC}}$  has reached 90% of its maximum value (typ. 2.5V).

<sup>2)</sup> PLL lock at 80 MHz using a 4 MHz external oscillator. The PLL Divider settings are K = 2, N = 40 and P = 1.

# Figure 42 Power-on Reset Timing

# 4.3.5 JTAG Timing

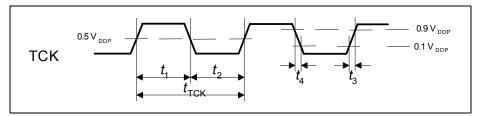

# Table 44TCK Clock Timing (Operating Conditions apply; $C_L = 50 \text{ pF}$ )

| Parameter           | Symbol              | Limits |     | Unit |

|---------------------|---------------------|--------|-----|------|

|                     |                     | min    | max |      |

| TCK clock period    | t <sub>TCK</sub> SR | 50     | -   | ns   |

| TCK high time       | t <sub>1</sub> SR   | 20     | -   | ns   |

| TCK low time        | t <sub>2</sub> SR   | 20     | -   | ns   |

| TCK clock rise time | t <sub>3</sub> SR   | -      | 4   | ns   |

| TCK clock fall time | t <sub>4</sub> SR   | -      | 4   | ns   |

Figure 43 TCK Clock Timing

# Package and Reliability

# 5 Package and Reliability

# 5.1 Package Parameters (PG-TSSOP-38)

Table 47 provides the thermal characteristics of the package.

| Parameter                                      | Symbol           |    | Limi | t Values | Unit | Notes |

|------------------------------------------------|------------------|----|------|----------|------|-------|

|                                                |                  |    | Min. | Max.     |      |       |

| Thermal resistance junction case <sup>1)</sup> | R <sub>TJC</sub> | CC | -    | 15.7     | K/W  | -     |

| Thermal resistance junction lead <sup>1)</sup> | R <sub>TJL</sub> | CC | -    | 39.2     | K/W  | -     |

<sup>)</sup> The thermal resistances between the case and the ambient (R<sub>TCA</sub>), the lead and the ambient (R<sub>TLA</sub>) are to be combined with the thermal resistances between the junction and the case (R<sub>TJC</sub>), the junction and the lead (R<sub>TJL</sub>) given above, in order to calculate the total thermal resistance between the junction and the ambient (R<sub>TJA</sub>). The thermal resistances between the case and the ambient (R<sub>TCA</sub>), the lead and the ambient (R<sub>TLA</sub>) depend on the external system (PCB, case) characteristics, and are under user responsibility.

The junction temperature can be calculated using the following equation:  $T_J=T_A + R_{TJA} \times P_D$ , where the  $R_{TJA}$  is the total thermal resistance between the junction and the ambient. This total junction ambient resistance  $R_{TJA}$  can be obtained from the upper four partial thermal resistances, by

a) simply adding only the two thermal resistances (junction lead and lead ambient), or

b) by taking all four resistances into account, depending on the precision needed.