Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Last Time Buy                                                                |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | XC800                                                                        |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 86MHz                                                                        |

| Connectivity               | SSI, UART/USART                                                              |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 19                                                                           |

| Program Memory Size        | 16KB (16K x 8)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 768 × 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                  |

| Data Converters            | A/D 8x10b                                                                    |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 38-TFSOP (0.173", 4.40mm Width)                                              |

| Supplier Device Package    | PG-TSSOP-38                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xc8664fribefxuma1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.2.1 Memory Protection Strategy

The XC866 memory protection strategy includes:

- Read-out protection: The Flash Memory can be enabled for read-out protection and ROM memory is always protected.

- Program and erase protection: The Flash memory in all devices can be enabled for program and erase protection.

Flash memory protection is available in two modes:

- Mode 0: Only the P-Flash is protected; the D-Flash is unprotected

- Mode 1: Both the P-Flash and D-Flash are protected

The selection of each protection mode and the restrictions imposed are summarized in **Table 4**.

| Mode                            | 0                                                                                                                    | 1                                              |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| Activation                      | Program a valid password via BSL m                                                                                   | node 6                                         |

| Selection                       | MSB of password = 0                                                                                                  | MSB of password = 1                            |

| P-Flash contents can be read by | Read instructions in the<br>P-Flash                                                                                  | Read instructions in the<br>P-Flash or D-Flash |

| P-Flash program and erase       | Not possible                                                                                                         | Not possible                                   |

| D-Flash contents can be read by | Read instructions in any program memory                                                                              | Read instructions in the<br>P-Flash or D-Flash |

| D-Flash program                 | Possible                                                                                                             | Not possible                                   |

| D-Flash erase                   | Possible, on the condition that bit<br>DFLASHEN in register MISC_CON<br>is set to 1 prior to each erase<br>operation | Not possible                                   |

#### Table 4 Flash Protection Modes

BSL mode 6, which is used for enabling Flash protection, can also be used for disabling Flash protection. Here, the programmed password must be provided by the user. A password match triggers an automatic erase of the read-protected Flash contents, see **Table 5** and **Table 6**, and the programmed password is erased. The Flash protection is then disabled upon the next reset.

#### For XC866-2FR and XC866-4FR devices:

The selection of protection type is summarized in Table 5.

#### Table 10Port Register Overview (cont'd)

| Addr            | Register Name                     | Bit       | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|-----------------|-----------------------------------|-----------|----|----|----|----|----|----|----|----|

| B1 <sub>H</sub> | P3_ALTSEL1 Reset: 00 <sub>H</sub> | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P3 Alternate Select 1 Register    | Туре      | rw |

| RMAP =          | 0, Page 3                         |           |    |    |    |    |    |    |    |    |

| 80 <sub>H</sub> | P0_OD Reset: 00 <sub>H</sub>      | Bit Field | 1  | C  | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P0 Open Drain Control Register    | Туре      |    | r  | rw | rw | rw | rw | rw | rw |

| 90 <sub>H</sub> | P1_OD Reset: 00 <sub>H</sub>      | Bit Field | P7 | P6 | P5 |    | 0  |    | P1 | P0 |

|                 | P1 Open Drain Control Register    | Туре      | rw | rw | rw |    | r  |    | rw | rw |

| в0 <sub>н</sub> | P3_OD Reset: 00 <sub>H</sub>      | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P3 Open Drain Control Register    | Туре      | rw |

The ADC SFRs can be accessed in the standard memory area (RMAP = 0).

# Table 11 ADC Register Overview

| Addr            | Register Name                                |                                 | Bit       | 7          | 6          | 5   | 4      | 3    | 2     | 1          | 0    |

|-----------------|----------------------------------------------|---------------------------------|-----------|------------|------------|-----|--------|------|-------|------------|------|

| RMAP =          | 0                                            |                                 |           |            |            |     |        |      |       |            |      |

| D1 <sub>H</sub> |                                              | eset: 00 <sub>H</sub>           | Bit Field | C          | P          | ST  | NR     | 0    |       | PAGE       |      |

|                 | Page Register for ADC                        |                                 | Туре      | N N        | v          | 1   | N      | r    |       | rwh        |      |

| RMAP =          | 0, Page 0                                    |                                 |           |            |            |     |        |      |       |            |      |

| CA <sub>H</sub> |                                              | eset: 30 <sub>H</sub>           | Bit Field | ANON       | DW         | C   | тс     |      |       | D          |      |

|                 | Global Control Register                      |                                 | Туре      | rw         | rw         | r   | w      |      |       | r          |      |

| CB <sub>H</sub> | ADC_GLOBSTR Register                         | eset: 00 <sub>H</sub>           | Bit Field | (          | )          |     | CHNR   |      | 0     | SAM<br>PLE | BUSY |

|                 |                                              |                                 | Туре      |            | r          |     | rh     |      | r     | rh         | rh   |

| CCH             |                                              | eset: 00 <sub>H</sub>           | Bit Field | ASEN1      | ASEN0      | 0   | ARBM   | CSM1 | PRIO1 | CSM0       | PRIO |

|                 | Priority and Arbitration Regis               | ster                            | Туре      | rw         | rw         | r   | rw     | rw   | rw    | rw         | rw   |

| CD <sub>H</sub> |                                              | eset: B7 <sub>H</sub>           | Bit Field |            | BOU        | ND1 |        |      | BOL   | IND0       |      |

|                 | Limit Check Boundary Regis                   | ster                            | Туре      |            | r          | N   |        |      | r     | w          |      |

| CEH             |                                              | eset: 00 <sub>H</sub>           | Bit Field |            |            |     | S      | ГС   |       |            |      |

|                 | Input Class Register 0                       |                                 | Туре      |            |            |     | r      | N    |       |            |      |

| CF <sub>H</sub> | ADC_ETRCR Re<br>External Trigger Control Reg | eset: 00 <sub>H</sub><br>gister | Bit Field | SYNEN<br>1 | SYNEN<br>0 |     | ETRSEL | 1    | l     | ETRSEL     | 0    |

|                 |                                              |                                 | Туре      | rw         | rw         |     | rw     |      |       | rw         |      |

| RMAP =          | 0, Page 1                                    |                                 |           |            |            |     |        |      |       |            |      |

| CA <sub>H</sub> |                                              | eset: 00 <sub>H</sub>           | Bit Field | 0          |            | LCC |        |      | D     | RES        | RSEL |

|                 | Channel Control Register 0                   |                                 | Туре      | r          |            | rw  |        |      | r     | r          | w    |

| CBH             |                                              | eset: 00 <sub>H</sub>           | Bit Field | 0          |            | LCC |        | Ţ    | 0     | RES        | RSEL |

|                 | Channel Control Register 1                   |                                 | Туре      | r          |            | rw  |        |      | r     | r          | w    |

| CCH             |                                              | eset: 00 <sub>H</sub>           | Bit Field | 0          |            | LCC |        | Ţ    | D     | RES        | RSEL |

|                 | Channel Control Register 2                   |                                 | Туре      | r          |            | rw  |        |      | r     | r          | w    |

| CD <sub>H</sub> |                                              | eset: 00 <sub>H</sub>           | Bit Field | 0          |            | LCC |        | l    | 0     | RES        | RSEL |

|                 | Channel Control Register 3                   |                                 | Туре      | r          |            | rw  |        |      | r     | r          | w    |

| CEH             |                                              | eset: 00 <sub>H</sub>           | Bit Field | 0          |            | LCC |        | Ţ    | D     | RES        | RSEL |

|                 | Channel Control Register 4                   |                                 | Туре      | r          |            | rw  |        |      | r     | r          | w    |

| CF <sub>H</sub> |                                              | eset: 00 <sub>H</sub>           | Bit Field | 0          |            | LCC |        | Ţ    | D     | RES        | RSEL |

|                 | Channel Control Register 5                   |                                 | Туре      | r          |            | rw  |        |      | r     | r          | w    |

| D2 <sub>H</sub> |                                              | eset: 00 <sub>H</sub>           | Bit Field | 0          |            | LCC |        | 1    | 0     | RES        | RSEL |

|                 | Channel Control Register 6                   |                                 | Туре      | r          |            | rw  |        |      | r     | r          | w    |

| D3 <sub>H</sub> |                                              | eset: 00 <sub>H</sub>           | Bit Field | 0          |            | LCC |        | 1    | 0     | RES        | RSEL |

|                 | Channel Control Register 7                   |                                 | Туре      | r          |            | rw  |        |      | r     | r          | w    |

| RMAP =          | 0, Page 2                                    |                                 |           |            |            |     |        |      |       |            |      |

### Table 13 CCU6 Register Overview (cont'd)

| Addr            | Register Name                                                             | Bit                              | 7      | 6            | 5            | 4          | 3            | 2          | 1            | 0          |  |

|-----------------|---------------------------------------------------------------------------|----------------------------------|--------|--------------|--------------|------------|--------------|------------|--------------|------------|--|

| FF <sub>H</sub> | CCU6_TRPCTRH Reset: 00 <sub>H</sub>                                       | Bit Field                        |        | TRPEN        |              |            | TR           | PEN        |              | 1          |  |

|                 | Trap Control Register High                                                |                                  | N      | 13           |              |            |              |            |              |            |  |

|                 |                                                                           | Туре                             | rw     | rw           |              |            | r            | w          |              |            |  |

| RMAP =          | 0, Page 3                                                                 |                                  |        |              |              |            |              |            |              |            |  |

| 9A <sub>H</sub> | CCU6_MCMOUTL Reset: 00 <sub>H</sub><br>Multi-Channel Mode Output Register | Bit Field                        | 0      | R            |              | MCMP       |              |            |              |            |  |

|                 | Low                                                                       | Туре                             | r      | rh           |              |            | r            | h          |              |            |  |

| 9B <sub>H</sub> | CCU6_MCMOUTH Reset: 00 <sub>H</sub><br>Multi-Channel Mode Output Register | Bit Field                        | (      | )            |              | CURH       |              |            | EXPH         |            |  |

|                 | High                                                                      | Туре                             | 1      | r            |              | rh         |              |            | rh           |            |  |

| 9C <sub>H</sub> | CCU6_ISL Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Status       | Bit Field                        | T12PM  | T12OM        | ICC62F       | R          | ICC61F       | R          | ICC60F       | ICC60<br>R |  |

|                 | Register Low                                                              | Туре                             | rh     | rh           | rh           | rh         | rh           | rh         | rh           | rh         |  |

| 9D <sub>H</sub> | CCU6_ISH Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Status       | Bit Field                        | STR    | IDLE         | WHE          | CHE        | TRPS         | TRPF       | T13PM        | T13CM      |  |

|                 | Register High                                                             | Туре                             | rh     | rh           | rh           | rh         | rh           | rh         | rh           | rh         |  |

| 9E <sub>H</sub> | CCU6_PISEL0L Reset: 00 <sub>H</sub>                                       |                                  |        | C62 ISCC61   |              |            | ISC          | C60        |              |            |  |

|                 | Port Input Select Register 0 Low                                          | Туре                             | r      | w            | r            | w          | rw           |            | r            | w          |  |

| 9F <sub>H</sub> | CCU6_PISEL0H Reset: 00 <sub>H</sub><br>Port Input Select Register 0 High  | Bit Field                        | IST1   | 2HR          | ISPOS2 ISP   |            | POS1 ISPOS   |            | OS0          |            |  |

|                 |                                                                           | Туре                             | n      | w            | rw n         |            |              | w rw       |              | w          |  |

| A4 <sub>H</sub> | CCU6_PISEL2 Reset: 00 <sub>H</sub>                                        | Bit Field                        |        |              | (            | C          |              |            | IST13HR      |            |  |

|                 | Port Input Select Register 2                                              | Туре                             |        |              | r            |            |              |            | rw           |            |  |

| FA <sub>H</sub> | CCU6_T12L Reset: 00 <sub>H</sub>                                          | Bit Field                        |        |              |              | T12        | CVL          |            |              |            |  |

|                 | Timer T12 Counter Register Low                                            | Туре                             |        |              |              | n          | vh           |            |              |            |  |

| FB <sub>H</sub> | CCU6_T12H Reset: 00 <sub>H</sub>                                          | Bit Field                        |        |              |              | T12        | CVH          |            |              |            |  |

|                 | Timer T12 Counter Register High                                           | Туре                             |        |              |              | n          | vh           |            |              |            |  |

| FC <sub>H</sub> | CCU6_T13L Reset: 00 <sub>H</sub>                                          | Bit Field                        |        |              |              | T13        | CVL          |            |              |            |  |

|                 | Timer T13 Counter Register Low                                            | Туре                             |        |              |              | n          | vh           |            |              |            |  |

| FD <sub>H</sub> | CCU6_T13H Reset: 00 <sub>H</sub>                                          | 00 <sub>H</sub> Bit Field T13CVH |        |              |              |            |              |            |              |            |  |

|                 | Timer T13 Counter Register High                                           | Туре                             | Гуре п |              | vh           |            |              |            |              |            |  |

| FE <sub>H</sub> | CCU6_CMPSTATL Reset: 00 <sub>H</sub><br>Compare State Register Low        | Bit Field                        | 0      | CC63<br>ST   | CCPO<br>S2   | CCPO<br>S1 | CCPO<br>S0   | CC62<br>ST | CC61<br>ST   | CC60<br>ST |  |

|                 |                                                                           | Туре                             | r      | rh           | rh           | rh         | rh           | rh         | rh           | rh         |  |

| FF <sub>H</sub> | CCU6_CMPSTATH Reset: 00 <sub>H</sub><br>Compare State Register High       | Bit Field                        | T13IM  | COUT<br>63PS | COUT<br>62PS | CC62<br>PS | COUT<br>61PS | CC61<br>PS | COUT<br>60PS | CC60<br>PS |  |

|                 |                                                                           | Туре                             | rwh    | rwh          | rwh          | rwh        | rwh          | rwh        | rwh          | rwh        |  |

The SSC SFRs can be accessed in the standard memory area (RMAP = 0).

# Table 14SSC Register Overview

| Addr            | Register Name                            |                        | Bit       | 7  | 6  | 5  | 4  | 3 | 2   | 1   | 0   |

|-----------------|------------------------------------------|------------------------|-----------|----|----|----|----|---|-----|-----|-----|

| RMAP =          | 0                                        |                        | •         |    |    |    |    |   |     |     |     |

| A9 <sub>H</sub> | SSC_PISEL                                | Reset: 00 <sub>H</sub> | Bit Field |    |    | 0  |    |   | CIS | SIS | MIS |

|                 | Port Input Select Regist                 | er                     | Туре      |    |    | r  |    |   | rw  | rw  | rw  |

| AA <sub>H</sub> | SSC_CONL                                 | Reset: 00 <sub>H</sub> | Bit Field | LB | PO | PH | HB |   | В   | М   |     |

|                 | Control Register Low<br>Programming Mode |                        | Туре      | rw | rw | rw | rw |   | r   | w   |     |

|                 | Operating Mode                           |                        | Bit Field |    |    | 0  |    |   | B   | С   |     |

|                 |                                          |                        | Туре      |    |    | r  |    |   | r   | h   |     |

# 3.4 Interrupt System

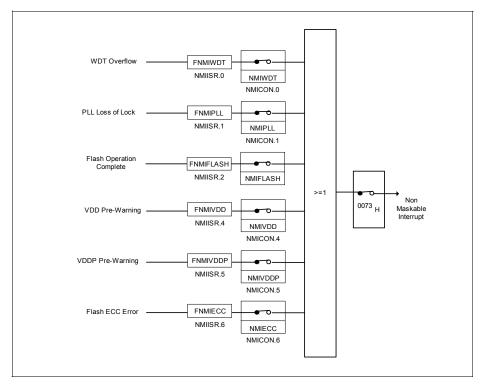

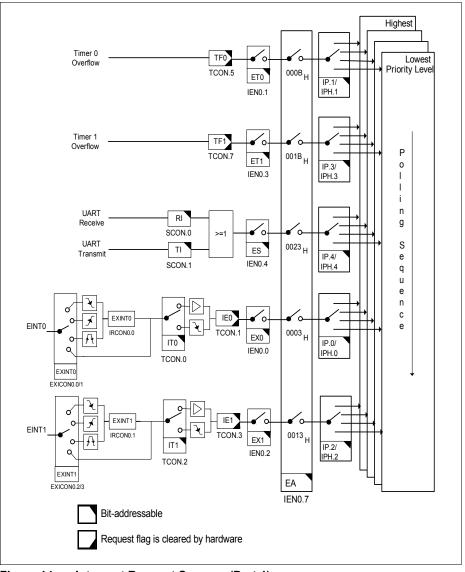

The XC800 Core supports one non-maskable interrupt (NMI) and 14 maskable interrupt requests. In addition to the standard interrupt functions supported by the core, e.g., configurable interrupt priority and interrupt masking, the XC866 interrupt system provides extended interrupt support capabilities such as the mapping of each interrupt vector to several interrupt sources to increase the number of interrupt sources supported, and additional status registers for detecting and determining the interrupt source.

# 3.4.1 Interrupt Source

Figure 13 to Figure 17 give a general overview of the interrupt sources and illustrates the request and control flags.

# Figure 13 Non-Maskable Interrupt Request Sources

Figure 14 Interrupt Request Sources (Part 1)

# 3.4.2 Interrupt Source and Vector

Each interrupt source has an associated interrupt vector address. This vector is accessed to service the corresponding interrupt source request. The interrupt service of each interrupt source can be individually enabled or disabled via an enable bit. The assignment of the XC866 interrupt sources to the interrupt vector addresses and the corresponding interrupt source enable bits are summarized in **Table 17**.

| Interrupt<br>Source | Vector<br>Address | Assignment for XC866                            | Enable Bit | SFR    |

|---------------------|-------------------|-------------------------------------------------|------------|--------|

| NMI                 | 0073 <sub>H</sub> | Watchdog Timer NMI                              | NMIWDT     | NMICON |

|                     |                   | PLL NMI                                         | NMIPLL     |        |

|                     |                   | Flash NMI                                       | NMIFLASH   |        |

|                     |                   | VDDC Prewarning NMI                             | NMIVDD     |        |

|                     |                   | VDDP Prewarning NMI                             | NMIVDDP    |        |

|                     |                   | Flash ECC NMI                                   | NMIECC     |        |

| XINTR0              | 0003 <sub>H</sub> | External Interrupt 0                            | EX0        | IEN0   |

| XINTR1              | 000B <sub>H</sub> | Timer 0                                         | ET0        |        |

| XINTR2              | 0013 <sub>H</sub> | External Interrupt 1                            | EX1        |        |

| XINTR3              | 001B <sub>H</sub> | Timer 1                                         | ET1        |        |

| XINTR4              | 0023 <sub>H</sub> | UART                                            | ES         |        |

| XINTR5              | 002B <sub>H</sub> | T2                                              | ET2        |        |

|                     |                   | Fractional Divider<br>(Normal Divider Overflow) |            |        |

|                     |                   | LIN                                             |            |        |

#### Table 17 Interrupt Vector Addresses

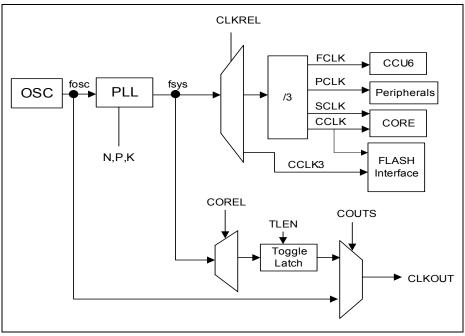

The clock system provides three ways to generate the system clock:

#### PLL Base Mode

The system clock is derived from the VCO base (free running) frequency clock divided by the K factor.

$$f_{SYS} = f_{VCObase} \times \frac{1}{K}$$

#### Prescaler Mode (VCO Bypass Operation)

In VCO bypass operation, the system clock is derived from the oscillator clock, divided by the P and K factors.

$$f_{SYS} = f_{OSC} \times \frac{1}{P \times K}$$

#### PLL Mode

The system clock is derived from the oscillator clock, multiplied by the N factor, and divided by the P and K factors. Both VCO bypass and PLL bypass must be inactive for this PLL mode. The PLL mode is used during normal system operation.

$$f_{SYS} = f_{OSC} \times \frac{N}{P \times K}$$

**Table 3-1** shows the settings of bits OSCDISC and VCOBYP for different clock mode selection.

| OSCDISC | VCOBYP | Clock Working Modes |  |

|---------|--------|---------------------|--|

| 0       | 0      | PLL Mode            |  |

| 0       | 1      | Prescaler Mode      |  |

| 1       | 0      | PLL Base Mode       |  |

| 1       | 1      | PLL Base Mode       |  |

# Table 3-1 Clock Mode Selection

Note: When oscillator clock is disconnected from PLL, the clock mode is PLL Base mode regardless of the setting of VCOBYP bit.

#### **System Frequency Selection**

For the XC866, the values of P and K are fixed to "1" and "2", respectively. In order to obtain the required system frequency,  $f_{sys}$ , the value of N can be selected by bit NDIV for different oscillator inputs. **Table 21** provides examples on how  $f_{sys}$  = 80 MHz can be obtained for the different oscillator sources.

# 3.8.2 Clock Management

The CGU generates all clock signals required within the microcontroller from a single clock,  $f_{sys}$ . During normal system operation, the typical frequencies of the different modules are as follow:

- CPU clock: CCLK, SCLK = 26.7 MHz

- CCU6 clock: FCLK = 26.7 MHz

- Other peripherals: PCLK = 26.7 MHz

- Flash Interface clock: CCLK3 = 80 MHz and CCLK = 26.7 MHz

In addition, different clock frequency can output to pin CLKOUT(P0.0). The clock output frequency can further be divided by 2 using toggle latch (bit TLEN is set to 1), the resulting output frequency has 50% duty cycle. **Figure 25** shows the clock distribution of the XC866.

Figure 25 Clock Generation from f<sub>svs</sub>

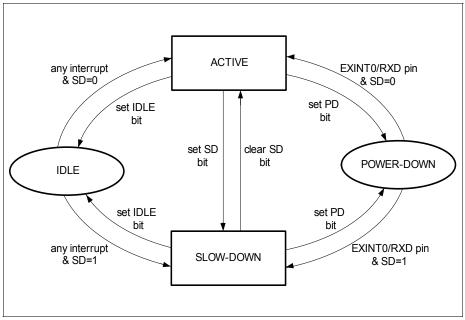

# 3.9 Power Saving Modes

The power saving modes of the XC866 provide flexible power consumption through a combination of techniques, including:

- Stopping the CPU clock

- · Stopping the clocks of individual system components

- Reducing clock speed of some peripheral components

- · Power-down of the entire system with fast restart capability

After a reset, the active mode (normal operating mode) is selected by default (see **Figure 26**) and the system runs in the main system clock frequency. From active mode, different power saving modes can be selected by software. They are:

- · Idle mode

- Slow-down mode

- Power-down mode

Figure 26 Transition between Power Saving Modes

XC866

# 3.11.1 Baud-Rate Generator

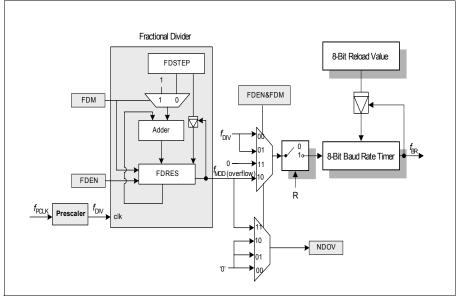

The baud-rate generator is based on a programmable 8-bit reload value, and includes divider stages (i.e., prescaler and fractional divider) for generating a wide range of baud rates based on its input clock  $f_{PCLK}$ , see **Figure 29**.

#### Figure 29 Baud-rate Generator Circuitry

The baud rate timer is a count-down timer and is clocked by either the output of the fractional divider ( $f_{MOD}$ ) if the fractional divider is enabled (FDCON.FDEN = 1), or the output of the prescaler ( $f_{DIV}$ ) if the fractional divider is disabled (FDEN = 0). For baud rate generation, the fractional divider must be configured to fractional divider mode (FDCON.FDM = 0). This allows the baud rate control run bit BCON.R to be used to start or stop the baud rate timer. At each timer underflow, the timer is reloaded with the 8-bit reload value in register BG and one clock pulse is generated for the serial channel.

Enabling the fractional divider in normal divider mode (FDEN = 1 and FDM = 1) stops the baud rate timer and nullifies the effect of bit BCON.R. See **Section 3.12**.

The baud rate  $(f_{BR})$  value is dependent on the following parameters:

- Input clock f<sub>PCLK</sub>

- Prescaling factor (2<sup>BRPRE</sup>) defined by bit field BRPRE in register BCON

- Fractional divider (STEP/256) defined by register FDSTEP (to be considered only if fractional divider is enabled and operating in fractional divider mode)

# 3.11.2 Baud Rate Generation using Timer 1

In UART modes 1 and 3, Timer 1 can be used for generating the variable baud rates. In theory, this timer could be used in any of its modes. But in practice, it should be set into auto-reload mode (Timer 1 mode 2), with its high byte set to the appropriate value for the required baud rate. The baud rate is determined by the Timer 1 overflow rate and the value of SMOD as follows:

[3.1]

Mode 1, 3 baud rate=  $\frac{2^{\text{SMOD}} \times f_{\text{PCLK}}}{32 \times 2 \times (256 - \text{TH1})}$

# 3.12 Normal Divider Mode (8-bit Auto-reload Timer)

Setting bit FDM in register FDCON to 1 configures the fractional divider to normal divider mode, while at the same time disables baud rate generation (see **Figure 29**). Once the fractional divider is enabled (FDEN = 1), it functions as an 8-bit auto-reload timer (with no relation to baud rate generation) and counts up from the reload value with each input clock pulse. Bit field RESULT in register FDRES represents the timer value, while bit field STEP in register FDSTEP defines the reload value. At each timer overflow, an overflow flag (FDCON.NDOV) will be set and an interrupt request generated. This gives an output clock  $f_{MOD}$  that is 1/n of the input clock  $f_{DIV}$ , where n is defined by 256 - STEP.

The output frequency in normal divider mode is derived as follows:

$f_{MOD} = f_{DIV} \times \frac{1}{256 - STEP}$ [3.2]

For module clock  $f_{ADC}$  = 26.7 MHz, the analog clock  $f_{ADCI}$  frequency can be selected as shown in **Table 30**.

| Module Clock f <sub>ADC</sub> | СТС                       | Prescaling Ratio | Analog Clock f <sub>ADCI</sub> |

|-------------------------------|---------------------------|------------------|--------------------------------|

| 26.7 MHz                      | 00 <sub>B</sub>           | ÷ 2              | 13.3 MHz (N.A)                 |

|                               | 01 <sub>B</sub>           | ÷ 3              | 8.9 MHz                        |

|                               | 10 <sub>B</sub>           | ÷ 4              | 6.7 MHz                        |

|                               | 11 <sub>B</sub> (default) | ÷ 32             | 833.3 kHz                      |

# Table 30f\_ADCI Frequency Selection

As  $f_{ADCI}$  cannot exceed 10 MHz, bit field CTC should not be set to  $00_B$  when  $f_{ADC}$  is 26.7 MHz. During slow-down mode where  $f_{ADC}$  may be reduced to 13.3 MHz, 6.7 MHz etc., CTC can be set to  $00_B$  as long as the divided analog clock  $f_{ADCI}$  does not exceed 10 MHz. However, it is important to note that the conversion error could increase due to loss of charges on the capacitors, if  $f_{ADC}$  becomes too low during slow-down mode.

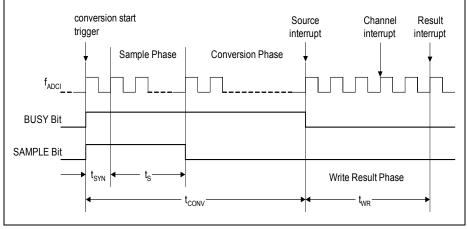

# 3.18.2 ADC Conversion Sequence

The analog-to-digital conversion procedure consists of the following phases:

- Synchronization phase (t<sub>SYN</sub>)

- Sample phase (t<sub>S</sub>)

- Conversion phase

- Write result phase (t<sub>WR</sub>)

Figure 34 ADC Conversion Timing

# 3.19.1 JTAG ID Register

This is a read-only register located inside the JTAG module, and is used to recognize the device(s) connected to the JTAG interface. Its content is shifted out when INSTRUCTION register contains the IDCODE command (opcode  $04_H$ ), and the same is also true immediately after reset.

The JTAG ID register contents for the XC866 devices are given in Table 31.

| Device Type | Device Name | JTAG ID                |  |

|-------------|-------------|------------------------|--|

| Flash       | XC866L-4FR  | 1010 0083 <sub>H</sub> |  |

|             | XC866-4FR   | 100F 5083 <sub>H</sub> |  |

|             | XC866L-2FR  | 1010 2083 <sub>H</sub> |  |

|             | XC866-2FR   | 1010 1083 <sub>H</sub> |  |

|             | XC866L-1FR  | 1013 8083 <sub>H</sub> |  |

|             | XC866-1FR   | 1013 8083 <sub>H</sub> |  |

# infineon

# **Electrical Parameters**

# Table 34 Input/Output Characteristics (Operating Conditions apply)

| Parameter                                                  | Symbol               | Limit                       | Values                      | Unit | <b>Test Conditions</b>    |  |

|------------------------------------------------------------|----------------------|-----------------------------|-----------------------------|------|---------------------------|--|

|                                                            |                      | min.                        | max.                        |      | Remarks                   |  |

| V <sub>DDP</sub> = 3.3V Range                              |                      |                             |                             |      |                           |  |

| Output low voltage                                         | V <sub>OL</sub> CC   | _                           | 1.0                         | V    | I <sub>OL</sub> = 8 mA    |  |

|                                                            |                      | _                           | 0.4                         | V    | I <sub>OL</sub> = 2.5 mA  |  |

| Output high voltage                                        | V <sub>OH</sub> CC   | V <sub>DDP</sub> -<br>1.0   | -                           | V    | I <sub>OH</sub> = -8 mA   |  |

|                                                            |                      | V <sub>DDP</sub> -<br>0.4   | -                           | V    | I <sub>OH</sub> = -2.5 mA |  |

| nput low voltage on<br>ort pins<br>all except P0.0 & P0.1) | V <sub>ILP</sub> SR  | -                           | $0.3 \times V_{\text{DDP}}$ | V    | CMOS Mode                 |  |

| nput low voltage on<br>0.0 & P0.1                          | $V_{ILP0}$ SR        | -0.2                        | $0.3 \times V_{ m DDP}$     | V    | CMOS Mode                 |  |

| i <u>put lo</u> w voltage on<br>ESET pin                   | V <sub>ILR</sub> SR  | -                           | $0.3 \times V_{\text{DDP}}$ | V    | CMOS Mode                 |  |

| iput low voltage on<br>MS pin                              | V <sub>ILT</sub> SR  | -                           | $0.3 \times V_{\text{DDP}}$ | V    | CMOS Mode                 |  |

| put high voltage on<br>ort pins<br>Il except P0.0 & P0.1)  | V <sub>IHP</sub> SR  | $0.7 \times V_{\text{DDP}}$ | -                           | V    | CMOS Mode                 |  |

| put high voltage on<br>).0 & P0.1                          | V <sub>IHP0</sub> SR | $0.7 \times V_{\text{DDP}}$ | V <sub>DDP</sub>            | V    | CMOS Mode                 |  |

| put high voltage on<br>ESET pin                            | V <sub>IHR</sub> SR  | $0.7 \times V_{\text{DDP}}$ | -                           | V    | CMOS Mode                 |  |

| put high voltage on<br>⁄IS pin                             | V <sub>IHT</sub> SR  | $0.75 \times V_{ m DDP}$    | -                           | V    | CMOS Mode                 |  |

| put Hysteresis <sup>1)</sup> on<br>ort pins                | HYS CC               | $0.03 \times V_{ m DDP}$    | -                           | V    | CMOS Mode                 |  |

| out Hysteresis <sup>1)</sup> on<br>FAL1                    | HYSXCC               |                             | -                           | V    |                           |  |

| put low voltage at<br>FAL1                                 | V <sub>ILX</sub> SR  |                             | $0.3 \times V_{ m DDC}$     | V    |                           |  |

| nput high voltage at<br>TAL1                               | V <sub>IHX</sub> SR  | $0.7 \times V_{ m DDC}$     | V <sub>DDC</sub><br>+ 0.5   | V    |                           |  |

<sup>4)</sup> Not subjected to production test, verified by design/characterization. However, for applications with strict low power-down current requirements, it is mandatory that no active voltage source is supplied at any GPIO pin when VDDP is powered off.

#### Table 38Power Down Current (Operating Conditions apply; $V_{DDP}$ = 5V range )

| Parameter                     | Symbol           | Limit              | Values             |    | Test Condition<br>Remarks                                           |

|-------------------------------|------------------|--------------------|--------------------|----|---------------------------------------------------------------------|

|                               |                  | typ. <sup>1)</sup> | max. <sup>2)</sup> |    |                                                                     |

| V <sub>DDP</sub> = 5V Range   |                  | -                  |                    |    |                                                                     |

| Power-Down Mode <sup>3)</sup> | I <sub>PDP</sub> | 1                  | 10                 | μA | $T_{A} = +25 \ ^{\circ}C.^{4)}$                                     |

|                               |                  | -                  | 30                 | μA | $T_{A}$ = + 85 °C, XC866-<br>4FR, XC866-2FR <sup>4)5)</sup>         |

|                               |                  | -                  | 35                 | μA | T <sub>A</sub> = + 85 °C, XC866-<br>1FR, ROM device <sup>4)5)</sup> |

<sup>1)</sup> The typical  $I_{PDP}$  values are measured at  $V_{DDP}$  = 5.0 V.

<sup>2)</sup> The maximum  $I_{\text{PDP}}$  values are measured at  $V_{\text{DDP}}$  = 5.5 V.

- <sup>3)</sup> I<sub>PDP</sub> (power-down mode) has a maximum value of 200  $\mu$ A at  $T_A$  = + 125 °C.

- <sup>4)</sup> I<sub>PDP</sub> (power-down mode) is measured with: RESET = V<sub>DDP</sub>, V<sub>AGND</sub>= V<sub>SS</sub>, RXD/INT0 = V<sub>DDP</sub>; rest of the ports are programmed to be input with either internal pull devices enabled or driven externally to ensure no floating inputs.

<sup>5)</sup> Not subject to production test, verified by design/characterization.

#### 4.3 AC Parameters

#### **Testing Waveforms** 4.3.1

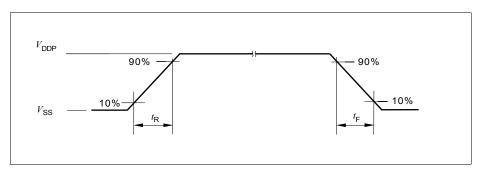

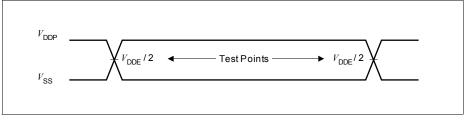

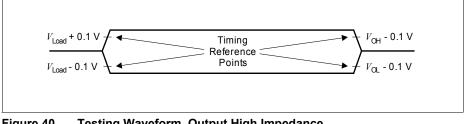

The testing waveforms for rise/fall time, output delay and output high impedance are shown in Figure 38, Figure 39 and Figure 40.

Figure 38 **Rise/Fall Time Parameters**

**Testing Waveform, Output Delay** Figure 39

Figure 40 **Testing Waveform, Output High Impedance**

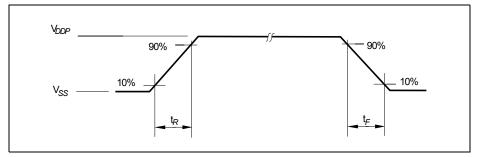

# 4.3.2 Output Rise/Fall Times

# Table 41 Output Rise/Fall Times Parameters (Operating Conditions apply)

| Parameter                     | Symbol                          | Limit<br>Values |      | Unit | Test Conditions      |

|-------------------------------|---------------------------------|-----------------|------|------|----------------------|

|                               |                                 | min.            | max. |      |                      |

| V <sub>DDP</sub> = 5V Range   |                                 |                 |      |      |                      |

| Rise/fall times 1) 2)         | t <sub>R</sub> , t <sub>F</sub> | -               | 10   | ns   | 20 pF. <sup>3)</sup> |

| V <sub>DDP</sub> = 3.3V Range |                                 |                 |      |      |                      |

| Rise/fall times 1) 2)         | t <sub>R</sub> , t <sub>F</sub> | -               | 10   | ns   | 20 pF. <sup>4)</sup> |

<sup>1)</sup> Rise/Fall time measurements are taken with 10% - 90% of the pad supply.

<sup>2)</sup> Not all parameters are 100% tested, but are verified by design/characterization and test correlation.

<sup>3)</sup> Additional rise/fall time valid for  $C_L = 20pF - 100pF @ 0.125 ns/pF$ .

<sup>4)</sup> Additional rise/fall time valid for  $C_L = 20pF - 100pF @ 0.225 ns/pF$ .

Figure 41 Rise/Fall Times Parameters

# 4.3.4 On-Chip Oscillator Characteristics

| Table 43 | On-chip Oscillator Characteristics (Operating Conditions apply) |

|----------|-----------------------------------------------------------------|

|----------|-----------------------------------------------------------------|

| Parameter                                   | Symbol              | Limit Values |      |       | Unit | Test Conditions                                                                                                     |

|---------------------------------------------|---------------------|--------------|------|-------|------|---------------------------------------------------------------------------------------------------------------------|

|                                             |                     | min.         | typ. | max.  |      |                                                                                                                     |

| Nominal frequency                           | f <sub>NOM</sub> CC | 9.75         | 10   | 10.25 | MHz  | under nominal<br>conditions <sup>1)</sup> after<br>IFX-backend trimming                                             |

| Long term frequency deviation <sup>2)</sup> | Δf <sub>LT</sub> CC | -5.0         | -    | 5.0   | %    | with respect to $f_{NOM}$ , over<br>lifetime and temperature (–<br>10°C to 125°C), for one<br>device after trimming |

|                                             |                     | -6.0         | -    | 0     | %    | with respect to $f_{NOM}$ , over<br>lifetime and temperature (–<br>40°C to -10°C), for one<br>device after trimming |

| Short term frequency deviation              | ∆f <sub>ST</sub> CC | -1.0         | -    | 1.0   | %    | with respect to <i>f<sub>NOM</sub></i> , within<br>one LIN message (<10 ms<br>100 ms)                               |

<sup>1)</sup> Nominal condition:  $V_{DDC}$  = 2.5 V,  $T_A$  = + 25°C.

<sup>2)</sup> Not all parameters are 100% tested, but are verified by design/characterization and test correlation.

### Package and Reliability

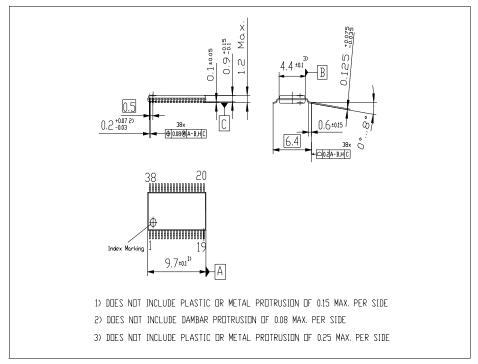

# 5.2 Package Outline

Figure 46 PG-TSSOP-38-4 Package Outline