Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Last Time Buy                                                                |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | XC800                                                                        |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 86MHz                                                                        |

| Connectivity               | SSI, UART/USART                                                              |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 19                                                                           |

| Program Memory Size        | 16KB (16K x 8)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 768 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                  |

| Data Converters            | A/D 8x10b                                                                    |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 38-TFSOP (0.173", 4.40mm Width)                                              |

| Supplier Device Package    | PG-TSSOP-38                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xc8664fribekxuma1 |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Data Sheet<br>n History: | 2007-10                                                                                                                                                                         | V1.2                               |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| V1.0                     | 2006-02                                                                                                                                                                         |                                    |

| Subjects (               | najor changes since last revision)                                                                                                                                              | )                                  |

| Device sur               | nmary table is updated for Flash                                                                                                                                                | 4-Kb and ROM variants.             |

| Footnote is              | added to MBC pin; description o                                                                                                                                                 | f $V_{\text{DDP}}$ pin is updated. |

|                          | •                                                                                                                                                                               | s type of register bit field       |

| Access typ               | e of PAGE bits of all module page                                                                                                                                               | registers are corrected to rwh.    |

| Access typ               | e of Px_DIR register bits are corr                                                                                                                                              | ected to rwh                       |

| New bullet               | point on Flash delivery state is a                                                                                                                                              | dded to the feature list.          |

| Digital pov              | er supply voltage are differentiate                                                                                                                                             | ed for 5V and 3.3V variants.       |

|                          | 5                                                                                                                                                                               | /oltage on GPIO pins during        |

| Figure on                | Power-on reset timing is updated.                                                                                                                                               |                                    |

|                          | n History:<br>S Version: V 0.1<br>V1.0,<br>V1.1,<br>Subjects (n<br>Device sum<br>Footnote is<br>Section on<br>PASSWD.F<br>Access type<br>New bullet<br>Digital pow<br>VDDP powe |                                    |

# We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to:

mcdocu.comments@infineon.com

$\ge$

## Summary of Features

## **XC866 Variant Devices**

The XC866 product family features devices with different configurations and program memory sizes, temperature and quality profiles (Automotive or Industrial), offering cost-effective solution for different application requirements.

The configuration of LIN BSL for XC866 devices are summarized in Table 1.

| Device Name | LIN BSL Support |

|-------------|-----------------|

| XC866       | No              |

| XC866L      | Yes             |

The list of XC866 devices and their differences are summarized in Table 2.

| Device<br>Type      | Device Name        | Power<br>Supply<br>(V) | P-Flash<br>Size<br>(Kbytes) | D-Flash<br>Size<br>(Kbytes) | ROM<br>Size<br>(Kbytes) | Quality<br>Profile <sup>1)</sup> |

|---------------------|--------------------|------------------------|-----------------------------|-----------------------------|-------------------------|----------------------------------|

| Flash <sup>2)</sup> | SAK-XC866*-4FRA    | 5.0                    | 12                          | 4                           | _                       | Automotive                       |

|                     | SAK-XC866*-4FRI    | 5.0                    | 12                          | 4                           | _                       | Industrial                       |

|                     | SAK-XC866*-2FRA    | 5.0                    | 4                           | 4                           | -                       | Automotive                       |

|                     | SAK-XC866*-2FRI    | 5.0                    | 4                           | 4                           | -                       | Industrial                       |

|                     | SAK-XC866*-1FRA    | 5.0                    | _                           | 4                           | -                       | Automotive                       |

|                     | SAK-XC866*-1FRI    | 5.0                    | -                           | 4                           | _                       | Industrial                       |

|                     | SAF-XC866*-4FRA    | 5.0                    | 12                          | 4                           | _                       | Automotive                       |

|                     | SAF-XC866*-4FRI    | 5.0                    | 12                          | 4                           | _                       | Industrial                       |

|                     | SAF-XC866*-2FRA    | 5.0                    | 4                           | 4                           | -                       | Automotive                       |

|                     | SAF-XC866*-2FRI    | 5.0                    | 4                           | 4                           | _                       | Industrial                       |

|                     | SAF-XC866*-1FRA    | 5.0                    | -                           | 4                           | _                       | Automotive                       |

|                     | SAF-XC866*-1FRI    | 5.0                    | -                           | 4                           | _                       | Industrial                       |

|                     | SAK-XC866*-4FRA 3V | 3.3                    | 12                          | 4                           | -                       | Automotive                       |

|                     | SAK-XC866*-4FRI 3V | 3.3                    | 12                          | 4                           | -                       | Industrial                       |

|                     | SAK-XC866*-2FRA 3V | 3.3                    | 4                           | 4                           | _                       | Automotive                       |

|                     | SAK-XC866*-2FRI 3V | 3.3                    | 4                           | 4                           | -                       | Industrial                       |

|                     | SAK-XC866*-1FRA 3V | 3.3                    | _                           | 4                           | -                       | Automotive                       |

## Table 2 Device Summary

# **Summary of Features**

### Table 2Device Summary

|     | •                  |     |    |   |    |            |

|-----|--------------------|-----|----|---|----|------------|

|     | SAK-XC866*-1FRI 3V | 3.3 | -  | 4 | _  | Industrial |

|     | SAF-XC866*-4FRA 3V | 3.3 | 12 | 4 | -  | Automotive |

|     | SAF-XC866*-4FRI 3V | 3.3 | 12 | 4 | -  | Industrial |

|     | SAF-XC866*-2FRA 3V | 3.3 | 4  | 4 | _  | Automotive |

|     | SAF-XC866*-2FRI 3V | 3.3 | 4  | 4 | _  | Industrial |

|     | SAF-XC866*-1FRA 3V | 3.3 | -  | 4 | _  | Automotive |

|     | SAF-XC866*-1FRI 3V | 3.3 | -  | 4 | -  | Industrial |

| ROM | SAK-XC866*-4RRA    | 5.0 | -  | 4 | 16 | Automotive |

|     | SAK-XC866*-4RRI    | 5.0 | -  | 4 | 16 | Industrial |

|     | SAK-XC866*-2RRA    | 5.0 | -  | 4 | 8  | Automotive |

|     | SAK-XC866*-2RRI    | 5.0 | _  | 4 | 8  | Industrial |

|     | SAF-XC866*-4RRA    | 5.0 | _  | 4 | 16 | Automotive |

|     | SAF-XC866*-4RRI    | 5.0 | _  | 4 | 16 | Industrial |

|     | SAF-XC866*-2RRA    | 5.0 | _  | 4 | 8  | Automotive |

|     | SAF-XC866*-2RRI    | 5.0 | _  | 4 | 8  | Industrial |

|     | SAK-XC866*-4RRA 3V | 3.3 | _  | 4 | 16 | Automotive |

|     | SAK-XC866*-4RRI 3V | 3.3 | _  | 4 | 16 | Industrial |

|     | SAK-XC866*-2RRA 3V | 3.3 | _  | 4 | 8  | Automotive |

|     | SAK-XC866*-2RRI 3V | 3.3 | _  | 4 | 8  | Industrial |

|     | SAF-XC866*-4RRA 3V | 3.3 | -  | 4 | 16 | Automotive |

|     | SAF-XC866*-4RRI 3V | 3.3 | -  | 4 | 16 | Industrial |

|     | SAF-XC866*-2RRA 3V | 3.3 | -  | 4 | 8  | Automotive |

|     | SAF-XC866*-2RRI 3V | 3.3 | -  | 4 | 8  | Industrial |

1) Industrial is not for Automotive usage

<sup>2)</sup> The flash memory (P-Flash and D-Flash) can be used for code or data.

Note: The asterisk (\*) above denotes the device configuration letters from Table 1.

#### **Summary of Features**

## **Ordering Information**

The ordering code for Infineon Technologies microcontrollers provides an exact reference to the required product. This ordering code identifies:

- The derivative itself, i.e. its function set, the temperature range, and the supply voltage

- the package and the type of delivery

For the available ordering codes for the XC866, please refer to your responsible sales representative or your local distributor.

As this document refers to all the derivatives, some descriptions may not apply to a specific product. For simplicity all versions are referred to by the term XC866 throughout this document.

# Note: The RMAP bit must be cleared/set by ANL or ORL instructions. The rest bits of SYSCON0 should not be modified.

As long as bit RMAP is set, the mapped SFR area can be accessed. This bit is not cleared automatically by hardware. Thus, before standard/mapped registers are accessed, bit RMAP must be cleared/set, respectively, by software.

Figure 8 Address Extension by Mapping

The Port SFRs can be accessed in the standard memory area (RMAP = 0).

## Table 10Port Register Overview

| Addr            | Register Name            |                        | Bit       | 7   | 6   | 5   | 4   | 3   | 2   | 1    | 0   |

|-----------------|--------------------------|------------------------|-----------|-----|-----|-----|-----|-----|-----|------|-----|

| RMAP =          |                          |                        |           |     |     |     |     |     |     |      |     |

| B2 <sub>H</sub> | PORT PAGE                | Reset: 00 <sub>H</sub> | Bit Field | C   | )P  | ST  | NR  | 0   |     | PAGE |     |

|                 | Page Register for PORT   |                        |           |     | r   |     | rwh |     |     |      |     |

| RMAP =          | 0, Page 0                |                        | .,,,,     |     |     |     |     |     |     |      |     |

| 80 <sub>H</sub> | P0 DATA                  | Reset: 00 <sub>H</sub> | Bit Field |     | 0   | P5  | P4  | P3  | P2  | P1   | P0  |

|                 | P0 Data Register         |                        | Туре      |     | r   | rwh | rwh | rwh | rwh | rwh  | rwh |

| 86 <sub>H</sub> | P0 DIR                   | Reset: 00 <sub>H</sub> | Bit Field |     | 0   | P5  | P4  | P3  | P2  | P1   | P0  |

|                 | P0 Direction Register    |                        | Туре      |     | r   | rw  | rw  | rw  | rw  | rw   | rw  |

| 90 <sub>H</sub> | P1 DATA                  | Reset: 00 <sub>H</sub> | Bit Field | P7  | P6  | P5  |     | 0   |     | P1   | P0  |

|                 | P1 Data Register         |                        | Туре      | rwh | rwh | rwh |     | r   |     | rwh  | rwh |

| 91 <sub>H</sub> | P1 DIR                   | Reset: 00 <sub>H</sub> | Bit Field | P7  | P6  | P5  |     | 0   |     | P1   | P0  |

|                 | P1 Direction Register    |                        | Туре      | rw  | rw  | rw  |     | r   |     | rw   | rw  |

| A0 <sub>H</sub> | P2_DATA                  | Reset: 00 <sub>H</sub> | Bit Field | P7  | P6  | P5  | P4  | P3  | P2  | P1   | P0  |

|                 | P2 Data Register         |                        | Туре      | rwh  | rwh |

| A1 <sub>H</sub> | P2_DIR                   | Reset: 00 <sub>H</sub> | Bit Field | P7  | P6  | P5  | P4  | P3  | P2  | P1   | P0  |

|                 | P2 Direction Register    |                        | Туре      | rw   | rw  |

| В0 <sub>Н</sub> | P3_DATA                  | Reset: 00 <sub>H</sub> | Bit Field | P7  | P6  | P5  | P4  | P3  | P2  | P1   | P0  |

|                 | P3 Data Register         |                        | Туре      | rwh  | rwh |

| B1 <sub>H</sub> | P3_DIR                   | Reset: 00 <sub>H</sub> | Bit Field | P7  | P6  | P5  | P4  | P3  | P2  | P1   | P0  |

|                 | P3 Direction Register    |                        | Туре      | rw   | rw  |

| RMAP =          | 0, Page 1                |                        |           |     |     |     |     |     |     |      | 1   |

| 80 <sub>H</sub> | P0_PUDSEL                | Reset: FF <sub>H</sub> | Bit Field |     | 0   | P5  | P4  | P3  | P2  | P1   | P0  |

|                 | P0 Pull-Up/Pull-Down Se  | elect Register         | Туре      |     | r   | rw  | rw  | rw  | rw  | rw   | rw  |

| 86 <sub>H</sub> | P0_PUDEN                 | Reset: C4 <sub>H</sub> | Bit Field |     | 0   | P5  | P4  | P3  | P2  | P1   | P0  |

|                 | P0 Pull-Up/Pull-Down Er  | hable Register         | Туре      |     | r   | rw  | rw  | rw  | rw  | rw   | rw  |

| 90 <sub>H</sub> | P1_PUDSEL                | Reset: FF <sub>H</sub> | Bit Field | P7  | P6  | P5  |     | 0   |     | P1   | P0  |

|                 | P1 Pull-Up/Pull-Down Se  | elect Register         | Туре      | rw  | rw  | rw  |     | r   |     | rw   | rw  |

| 91 <sub>H</sub> | P1_PUDEN                 | Reset: FF <sub>H</sub> | Bit Field | P7  | P6  | P5  |     | 0   |     | P1   | P0  |

|                 | P1 Pull-Up/Pull-Down Er  | nable Register         | Туре      | rw  | rw  | rw  |     | r   |     | rw   | rw  |

| A0 <sub>H</sub> | P2_PUDSEL                | Reset: FF <sub>H</sub> | Bit Field | P7  | P6  | P5  | P4  | P3  | P2  | P1   | P0  |

|                 | P2 Pull-Up/Pull-Down Se  | elect Register         | Туре      | rw   | rw  |

| A1 <sub>H</sub> | P2_PUDEN                 | Reset: 00 <sub>H</sub> | Bit Field | P7  | P6  | P5  | P4  | P3  | P2  | P1   | P0  |

|                 | P2 Pull-Up/Pull-Down Er  | nable Register         | Туре      | rw   | rw  |

| B0 <sub>H</sub> | P3_PUDSEL                | Reset: BF <sub>H</sub> | Bit Field | P7  | P6  | P5  | P4  | P3  | P2  | P1   | P0  |

|                 | P3 Pull-Up/Pull-Down Se  | elect Register         | Туре      | rw   | rw  |

| B1 <sub>H</sub> | P3_PUDEN                 | Reset: 40 <sub>H</sub> | Bit Field | P7  | P6  | P5  | P4  | P3  | P2  | P1   | P0  |

|                 | P3 Pull-Up/Pull-Down Er  | nable Register         | Туре      | rw   | rw  |

| RMAP =          | 0, Page 2                |                        |           |     |     |     |     |     |     |      |     |

| 80 <sub>H</sub> | P0_ALTSEL0               | Reset: 00 <sub>H</sub> | Bit Field |     | 0   | P5  | P4  | P3  | P2  | P1   | P0  |

|                 | P0 Alternate Select 0 Re | gister                 | Туре      |     | r   | rw  | rw  | rw  | rw  | rw   | rw  |

| 86 <sub>H</sub> | P0_ALTSEL1               | Reset: 00 <sub>H</sub> | Bit Field |     | 0   | P5  | P4  | P3  | P2  | P1   | P0  |

|                 | P0 Alternate Select 1 Re | gister                 | Туре      |     | r   | rw  | rw  | rw  | rw  | rw   | rw  |

| 90 <sub>H</sub> | P1_ALTSEL0               | Reset: 00 <sub>H</sub> | Bit Field | P7  | P6  | P5  |     | 0   |     | P1   | P0  |

|                 | P1 Alternate Select 0 Re | gister                 | Туре      | rw  | rw  | rw  |     | r   |     | rw   | rw  |

| 91 <sub>H</sub> | P1_ALTSEL1               | Reset: 00 <sub>H</sub> | Bit Field | P7  | P6  | P5  |     | 0   |     | P1   | P0  |

|                 | P1 Alternate Select 1 Re | gister                 | Туре      | rw  | rw  | rw  |     | r   |     | rw   | rw  |

| в0 <sub>Н</sub> | P3_ALTSEL0               | Reset: 00 <sub>H</sub> | Bit Field | P7  | P6  | P5  | P4  | P3  | P2  | P1   | P0  |

|                 | P3 Alternate Select 0 Re | gister                 | Туре      | rw   | rw  |

# Table 12Timer 2 Register Overview (cont'd)

| C1 <sub>H</sub> | T2_T2MOD<br>Timer 2 Mode Register | Reset: 00 <sub>H</sub> | Bit Field | T2<br>REGS | T2<br>RHEN | EDGE<br>SEL | PREN | T2PRE  | DCEN |

|-----------------|-----------------------------------|------------------------|-----------|------------|------------|-------------|------|--------|------|

|                 |                                   |                        | Туре      | rw         | rw         | rw          | rw   | rw     | rw   |

| C2 <sub>H</sub> | T2_RC2L                           | Reset: 00 <sub>H</sub> | Bit Field |            |            |             | RC2  | [7:0]  |      |

|                 | Timer 2 Reload/Capture            | Register Low           | Туре      |            |            |             | rv   | /h     |      |

| C3 <sub>H</sub> | T2_RC2H                           | Reset: 00 <sub>H</sub> | Bit Field |            |            |             | RC2  | [15:8] |      |

|                 | Timer 2 Reload/Capture            | Register High          | Туре      |            |            |             | rv   | /h     |      |

| C4 <sub>H</sub> | T2_T2L                            | Reset: 00 <sub>H</sub> | Bit Field |            |            |             | THL  | 2[7:0] |      |

|                 | Timer 2 Register Low              |                        | Туре      |            |            |             | rv   | /h     |      |

| C5 <sub>H</sub> | T2_T2H                            | Reset: 00 <sub>H</sub> | Bit Field |            |            |             | THL2 | [15:8] |      |

|                 | Timer 2 Register High             |                        | Туре      |            |            |             | rv   | vh     |      |

The CCU6 SFRs can be accessed in the standard memory area (RMAP = 0).

# Table 13 CCU6 Register Overview

| Addr            | Register Name                                                                | Bit       | 7          | 6          | 5          | 4          | 3          | 2          | 1          | 0          |

|-----------------|------------------------------------------------------------------------------|-----------|------------|------------|------------|------------|------------|------------|------------|------------|

| RMAP =          | 0                                                                            |           |            | 1          | 1          |            |            | 1          |            | 1          |

| A3 <sub>H</sub> | CCU6_PAGE Reset: 00 <sub>H</sub>                                             | Bit Field | C          | P          | ST         | NR         | 0          |            | PAGE       |            |

|                 | Page Register for CCU6                                                       | Туре      | ١          | N          | ١          | v          | r          |            | rwh        |            |

| RMAP =          | 0, Page 0                                                                    |           |            |            |            |            |            |            |            |            |

| 9A <sub>H</sub> | CCU6_CC63SRL Reset: 00 <sub>H</sub><br>Capture/Compare Shadow Register for   | Bit Field |            |            |            | CC         | 63SL       |            |            |            |

|                 | Channel CC63 Low                                                             | Туре      |            |            |            | r          | w          |            |            |            |

| 9B <sub>H</sub> | CCU6_CC63SRH Reset: 00 <sub>H</sub><br>Capture/Compare Shadow Register for   | Bit Field |            |            |            | CC6        | 3SH        |            |            |            |

|                 | Channel CC63 High                                                            | Туре      |            |            |            | r          | w          |            |            |            |

| 9C <sub>H</sub> | CCU6_TCTR4L Reset: 00 <sub>H</sub><br>Timer Control Register 4 Low           | Bit Field | T12<br>STD | T12<br>STR | (          | )          | DTRES      | T12<br>RES | T12RS      | T12RR      |

|                 |                                                                              | Туре      | w          | w          |            | r          | w          | w          | w          | w          |

| 9D <sub>H</sub> | CCU6_TCTR4H Reset: 00 <sub>H</sub><br>Timer Control Register 4 High          | Bit Field | T13<br>STD | T13<br>STR |            | 0          |            | T13<br>RES | T13RS      | T13RR      |

|                 |                                                                              | Туре      | w          | w          |            | r          |            | w          | w          | w          |

| 9E <sub>H</sub> | CCU6_MCMOUTSL Reset: 00 <sub>H</sub><br>Multi-Channel Mode Output Shadow     | Bit Field | STRM<br>CM | 0          |            |            | MCI        | MPS        |            |            |

|                 | Register Low                                                                 | Туре      | w          | r          |            |            | r          | w          |            |            |

| 9F <sub>H</sub> | CCU6_MCMOUTSH Reset: 00 <sub>H</sub>                                         | Bit Field | STRHP      | 0          |            | CURHS      | ;          |            | EXPHS      |            |

|                 | Multi-Channel Mode Output Shadow<br>Register High                            | Туре      | w          | r          |            | rw         |            |            | rw         |            |

| A4 <sub>H</sub> | CCU6_ISRL Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Status         | Bit Field | RT12P<br>M | RT12O<br>M | RCC62<br>F | RCC62<br>R | RCC61<br>F | RCC61<br>R | RCC60<br>F | RCC60<br>R |

|                 | Reset Register Low                                                           | Туре      | w          | w          | w          | w          | w          | w          | w          | w          |

| A5 <sub>H</sub> | CCU6_ISRH Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Status         | Bit Field | RSTR       | RIDLE      | RWHE       | RCHE       | 0          | RTRPF      | RT13<br>PM | RT13<br>CM |

|                 | Reset Register High                                                          | Туре      | w          | w          | w          | w          | r          | w          | w          | w          |

| A6 <sub>H</sub> | CCU6_CMPMODIFL Reset: 00 <sub>H</sub><br>Compare State Modification Register | Bit Field | 0          | MCC63<br>S |            | 0          |            | MCC62<br>S | MCC61<br>S | MCC60<br>S |

|                 | Low                                                                          | Туре      | r          | w          |            | r          |            | w          | w          | w          |

| A7 <sub>H</sub> | CCU6_CMPMODIFH Reset: 00 <sub>H</sub><br>Compare State Modification Register | Bit Field | 0          | MCC63<br>R |            | 0          |            | MCC62<br>R | MCC61<br>R | MCC60<br>R |

|                 | High                                                                         | Туре      | r          | w          |            | r          |            | w          | w          | w          |

| FA <sub>H</sub> | CCU6_CC60SRL Reset: 00 <sub>H</sub><br>Capture/Compare Shadow Register for   | Bit Field |            |            |            | CC         | 60SL       |            |            |            |

|                 | Channel CC60 Low                                                             | Туре      |            |            |            | n          | wh         |            |            |            |

| AB <sub>H</sub> | SSC_CONH Reset: 00 <sub>H</sub><br>Control Register High | Bit Field | EN | MS | 0 | AREN   | BEN      | PEN | REN | TEN |

|-----------------|----------------------------------------------------------|-----------|----|----|---|--------|----------|-----|-----|-----|

|                 | Programming Mode                                         | Туре      | rw | rw | r | rw     | rw       | rw  | rw  | rw  |

|                 | Operating Mode                                           | Bit Field | EN | MS | 0 | BSY    | BE       | PE  | RE  | TE  |

|                 |                                                          | Туре      | rw | rw | r | rh     | rwh      | rwh | rwh | rwh |

| ACH             | SSC_TBL Reset: 00 <sub>H</sub>                           | Bit Field |    |    |   | TB_V   | ALUE     |     |     |     |

|                 | Transmitter Buffer Register Low                          | Туре      |    |    |   | r      | w        |     |     |     |

| AD <sub>H</sub> | SSC_RBL Reset: 00 <sub>H</sub>                           | Bit Field |    |    |   | RB_V   | ALUE     |     |     |     |

|                 | Receiver Buffer Register Low                             | Туре      |    |    |   | r      | h        |     |     |     |

| AE <sub>H</sub> | SSC_BRL Reset: 00 <sub>H</sub>                           | Bit Field |    |    |   | BR_VA  | LUE[7:0] |     |     |     |

|                 | Baudrate Timer Reload Register Low                       | Туре      |    |    |   | r      | w        |     |     |     |

| AF <sub>H</sub> | SSC_BRH Reset: 00 <sub>H</sub>                           | Bit Field |    |    |   | BR_VAL | UE[15:8] |     |     |     |

|                 | Baudrate Timer Reload Register High                      | Туре      |    |    |   | r      | w        |     |     |     |

# Table 14 SSC Register Overview

The OCDS SFRs can be accessed in the mapped memory area (RMAP = 1).

# Table 15OCDS Register Overview

| Addr            | Register Name                                                           | Bit       | 7           | 6     | 5           | 4           | 3           | 2         | 1          | 0         |

|-----------------|-------------------------------------------------------------------------|-----------|-------------|-------|-------------|-------------|-------------|-----------|------------|-----------|

| RMAP =          | 1                                                                       |           |             | 1     |             |             |             |           |            |           |

| E9 <sub>H</sub> | MMCR2 Reset: 0U <sub>H</sub><br>Monitor Mode Control Register 2         | Bit Field | EXBC_<br>P  | EXBC  | MBCO<br>N_P | MBCO<br>N   | MMEP<br>_P  | MMEP      | MMOD<br>E  | JENA      |

|                 |                                                                         | Туре      | w           | rw    | w           | rwh         | w           | rwh       | rh         | rh        |

| F1 <sub>H</sub> | MMCR Reset: 00 <sub>H</sub><br>Monitor Mode Control Register            | Bit Field | MEXIT<br>_P | MEXIT | MSTEP<br>_P | MSTEP       | MRAM<br>S_P | MRAM<br>S | TRF        | RRF       |

|                 |                                                                         | Туре      | w           | rwh   | w           | rw          | w           | rwh       | rh         | rh        |

| F2 <sub>H</sub> | MMSR Reset: 00 <sub>H</sub><br>Monitor Mode Status Register             | Bit Field | MBCA<br>M   | MBCIN | EXBF        | SWBF        | HWB3<br>F   | HWB2<br>F | HWB1<br>F  | HWB0<br>F |

|                 |                                                                         | Туре      | rw          | rh    | rwh         | rwh         | rwh         | rwh       | rwh        | rwh       |

| F3 <sub>H</sub> | MMBPCR Reset: 00 <sub>H</sub><br>BreakPoints Control Register           | Bit Field | SWBC        | HW    | B3C         | HW          | B2C         | HWB1<br>C | HW         | B0C       |

|                 |                                                                         | Туре      | rw          | r     | w           | r           | w           | rw        | r          | w         |

| F4 <sub>H</sub> | MMICR Reset: 00 <sub>H</sub><br>Monitor Mode Interrupt Control Register | Bit Field | DVECT       | DRETR | (           | Ċ           | MMUIE<br>_P | MMUIE     | RRIE_<br>P | RRIE      |

|                 |                                                                         | Туре      | rwh         | rwh   | 1           | r           | w           | rw        | w          | rw        |

| F5 <sub>H</sub> | MMDR Reset: 00 <sub>H</sub><br>Monitor Mode Data Register               | Bit Field |             |       |             | MN          | IRR         |           |            |           |

|                 | Receive                                                                 | Туре      |             |       |             | r           | h           |           |            |           |

|                 | Transmit                                                                | Bit Field |             |       |             | MN          | 1TR         |           |            |           |

|                 |                                                                         | Туре      |             |       |             | ١           | N           |           |            |           |

| F6 <sub>H</sub> | HWBPSR Reset: 00 <sub>H</sub><br>Hardware Breakpoints Select Register   | Bit Field |             | 0     |             | BPSEL<br>_P |             | BP        | SEL        |           |

|                 |                                                                         | Туре      |             | r     |             | w           |             | r         | w          |           |

| F7 <sub>H</sub> | HWBPDR Reset: 00 <sub>H</sub>                                           | Bit Field |             |       |             | HW          | BPxx        |           |            |           |

|                 | Hardware Breakpoints Data Register                                      | Туре      |             |       |             | r           | w           |           |            |           |

| P-Flash              | D-Flash            |

|----------------------|--------------------|

|                      | Sector 0: 1-Kbyte  |

|                      | Sector 1: 1-Kbyte  |

| Sector 0: 3.75-Kbyte | Sector 2: 512-byte |

|                      | Sector 3: 512-byte |

|                      | Sector 4: 256-byte |

|                      | Sector 5: 256-byte |

|                      | Sector 6: 128-byte |

|                      | Sector 7: 128-byte |

| Sector 1: 128-byte   | Sector 8: 128-byte |

| Sector 2: 128-byte   | Sector 9: 128-byte |

## Figure 11 Flash Bank Sectorization

The internal structure of each Flash bank represents a sector architecture for flexible erase capability. The minimum erase width is always a complete sector, and sectors can be erased separately or in parallel. Contrary to standard EPROMs, erased Flash memory cells contain 0s.

The D-Flash bank is divided into more physical sectors for extended erasing and reprogramming capability; even numbers for each sector size are provided to allow greater flexibility and the ability to adapt to a wide range of application requirements.

# 3.3.2 Flash Programming Width

For the P-Flash banks, a programmed wordline (WL) must be erased before it can be reprogrammed as the Flash cells can only withstand one gate disturb. This means that the entire sector containing the WL must be erased since it is impossible to erase a single WL.

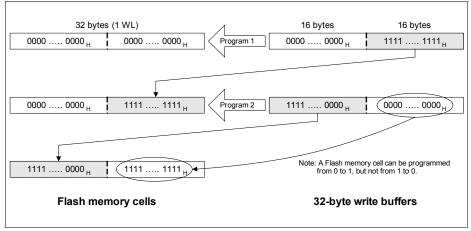

For the D-Flash bank, the same WL can be programmed twice before erasing is required as the Flash cells are able to withstand two gate disturbs. Hence, it is possible to program the same WL, for example, with 16 bytes of data in two times (see Figure 12).

## Figure 12 D-Flash Programming

Note: When programming a D-Flash WL the second time, the previously programmed Flash memory cells (whether 0s or 1s) should be reprogrammed with 0s to retain its original contents and to prevent "over-programming".

# 3.4 Interrupt System

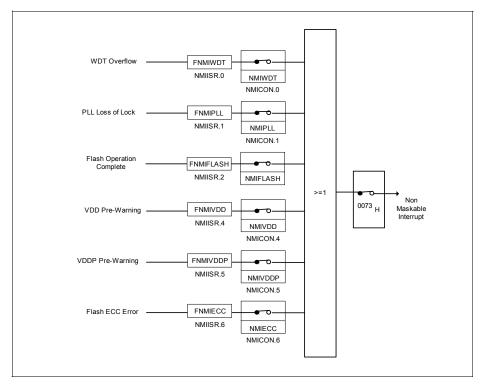

The XC800 Core supports one non-maskable interrupt (NMI) and 14 maskable interrupt requests. In addition to the standard interrupt functions supported by the core, e.g., configurable interrupt priority and interrupt masking, the XC866 interrupt system provides extended interrupt support capabilities such as the mapping of each interrupt vector to several interrupt sources to increase the number of interrupt sources supported, and additional status registers for detecting and determining the interrupt source.

# 3.4.1 Interrupt Source

Figure 13 to Figure 17 give a general overview of the interrupt sources and illustrates the request and control flags.

# Figure 13 Non-Maskable Interrupt Request Sources

# 3.5 Parallel Ports

The XC866 has 27 port pins organized into four parallel ports, Port 0 (P0) to Port 3 (P3). Each pin has a pair of internal pull-up and pull-down devices that can be individually enabled or disabled. Ports P0, P1 and P3 are bidirectional and can be used as general purpose input/output (GPIO) or to perform alternate input/output functions for the on-chip peripherals. When configured as an output, the open drain mode can be selected. Port P2 is an input-only port, providing general purpose input functions, alternate input functions for the on-chip peripherals, and also analog inputs for the Analog-to-Digital Converter (ADC).

## **Bidirectional Port Features:**

- Configurable pin direction

- Configurable pull-up/pull-down devices

- Configurable open drain mode

- Transfer of data through digital inputs and outputs (general purpose I/O)

- Alternate input/output for on-chip peripherals

## Input Port Features:

- · Configurable input driver

- Configurable pull-up/pull-down devices

- Receive of data through digital input (general purpose input)

- · Alternate input for on-chip peripherals

- Analog input for ADC module

# XC866

#### **Functional Description**

# 3.8 Clock Generation Unit

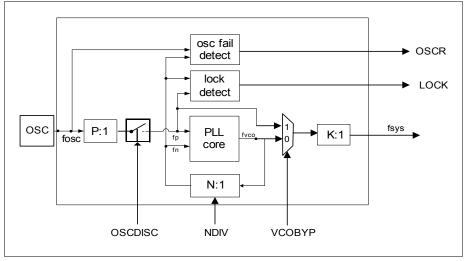

The Clock Generation Unit (CGU) allows great flexibility in the clock generation for the XC866. The power consumption is indirectly proportional to the frequency, whereas the performance of the microcontroller is directly proportional to the frequency. During user program execution, the frequency can be programmed for an optimal ratio between performance and power consumption. Therefore the power consumption can be adapted to the actual application state.

## Features:

- · Phase-Locked Loop (PLL) for multiplying clock source by different factors

- PLL Base Mode

- Prescaler Mode

- PLL Mode

- Power-down mode support

The CGU consists of an oscillator circuit and a PLL.In the XC866, the oscillator can be from either of these two sources: the on-chip oscillator (10 MHz) or the external oscillator (4 MHz to 12 MHz). The term "oscillator" is used to refer to both on-chip oscillator and external oscillator, unless otherwise stated. After the reset, the on-chip oscillator will be used by default. The external oscillator can be selected via software. In addition, the PLL provides a fail-safe logic to perform oscillator run and loss-of-lock detection. This allows emergency routines to be executed for system recovery or to perform system shut down.

Figure 23 CGU Block Diagram

Table 24 lists the possible watchdog time range that can be achieved for different module clock frequencies.

Some numbers are rounded to 3 significant digits.

| Reload value<br>in WDTREL          | Prescaler for f <sub>PCLK</sub> | Prescaler for f <sub>PCLK</sub> |  |  |  |

|------------------------------------|---------------------------------|---------------------------------|--|--|--|

|                                    | 2 (WDTIN = 0)                   | 128 (WDTIN = 1)<br>26.7 MHz     |  |  |  |

|                                    | 26.7 MHz                        |                                 |  |  |  |

| FF <sub>H</sub>                    | 19.2 μs                         | 1.23 ms                         |  |  |  |

| FF <sub>H</sub><br>7F <sub>H</sub> | 2.48 ms                         | 159 ms                          |  |  |  |

| 00 <sub>H</sub>                    | 4.92 ms                         | 315 ms                          |  |  |  |

| Table 24 | Watchdog Time Rang | jes |

|----------|--------------------|-----|

|----------|--------------------|-----|

# 3.11 Universal Asynchronous Receiver/Transmitter

The Universal Asynchronous Receiver/Transmitter (UART) provides a full-duplex asynchronous receiver/transmitter, i.e., it can transmit and receive simultaneously. It is also receive-buffered, i.e., it can commence reception of a second byte before a previously received byte has been read from the receive register. However, if the first byte still has not been read by the time reception of the second byte is complete, one of the bytes will be lost.

## Features:

- Full-duplex asynchronous modes

- 8-bit or 9-bit data frames, LSB first

- fixed or variable baud rate

- · Receive buffered

- Multiprocessor communication

- Interrupt generation on the completion of a data transmission or reception

The UART can operate in the four modes as shown in **Table 25**. Data is transmitted on TXD and received on RXD.

| Operating Mode               | Baud Rate                                      |  |  |

|------------------------------|------------------------------------------------|--|--|

| Mode 0: 8-bit shift register | f <sub>PCLK</sub> /2                           |  |  |

| Mode 1: 8-bit shift UART     | Variable                                       |  |  |

| Mode 2: 9-bit shift UART     | f <sub>PCLK</sub> /32 or f <sub>PCLK</sub> /64 |  |  |

| Mode 3: 9-bit shift UART     | Variable                                       |  |  |

There are several ways to generate the baud rate clock for the serial port, depending on the mode in which it is operating. In mode 0, the baud rate for the transfer is fixed at  $f_{PCLK}/2$ . In mode 2, the baud rate is generated internally based on the UART input clock and can be configured to either  $f_{PCLK}/32$  or  $f_{PCLK}/64$ . The variable baud rate is set by either the underflow rate on the dedicated baud-rate generator, or by the overflow rate on Timer 1.

# 3.14 High-Speed Synchronous Serial Interface

The High-Speed Synchronous Serial Interface (SSC) supports full-duplex and half-duplex synchronous communication. The serial clock signal can be generated by the SSC internally (master mode), using its own 16-bit baud-rate generator, or can be received from an external master (slave mode). Data width, shift direction, clock polarity and phase are programmable. This allows communication with SPI-compatible devices or devices using other synchronous serial interfaces.

## Features:

- · Master and slave mode operation

- Full-duplex or half-duplex operation

- Transmit and receive buffered

- Flexible data format

- Programmable number of data bits: 2 to 8 bits

- Programmable shift direction: LSB or MSB shift first

- Programmable clock polarity: idle low or high state for the shift clock

- Programmable clock/data phase: data shift with leading or trailing edge of the shift clock

- · Variable baud rate

- Compatible with Serial Peripheral Interface (SPI)

- Interrupt generation

- On a transmitter empty condition

- On a receiver full condition

- On an error condition (receive, phase, baud rate, transmit error)

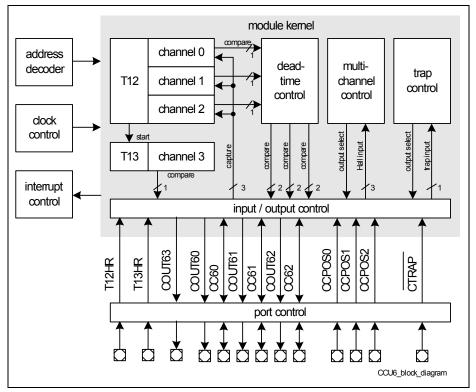

The block diagram of the CCU6 module is shown in Figure 32.

Figure 32 CCU6 Block Diagram

For module clock  $f_{ADC}$  = 26.7 MHz, the analog clock  $f_{ADCI}$  frequency can be selected as shown in **Table 30**.

| Module Clock f <sub>ADC</sub> | СТС                       | Prescaling Ratio | Analog Clock f <sub>ADCI</sub> |  |

|-------------------------------|---------------------------|------------------|--------------------------------|--|

| 26.7 MHz                      | 00 <sub>B</sub>           | ÷ 2              | 13.3 MHz (N.A)                 |  |

|                               | 01 <sub>B</sub>           | ÷ 3              | 8.9 MHz                        |  |

|                               | 10 <sub>B</sub>           | ÷ 4              | 6.7 MHz                        |  |

|                               | 11 <sub>B</sub> (default) | ÷ 32             | 833.3 kHz                      |  |

# Table 30f\_ADCIFrequency Selection

As  $f_{ADCI}$  cannot exceed 10 MHz, bit field CTC should not be set to  $00_B$  when  $f_{ADC}$  is 26.7 MHz. During slow-down mode where  $f_{ADC}$  may be reduced to 13.3 MHz, 6.7 MHz etc., CTC can be set to  $00_B$  as long as the divided analog clock  $f_{ADCI}$  does not exceed 10 MHz. However, it is important to note that the conversion error could increase due to loss of charges on the capacitors, if  $f_{ADC}$  becomes too low during slow-down mode.

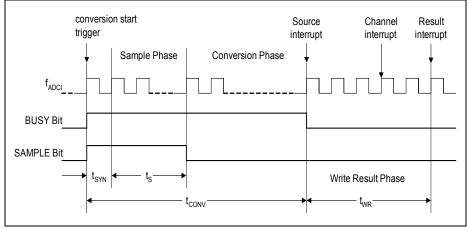

# 3.18.2 ADC Conversion Sequence

The analog-to-digital conversion procedure consists of the following phases:

- Synchronization phase (t<sub>SYN</sub>)

- Sample phase (t<sub>S</sub>)

- Conversion phase

- Write result phase (t<sub>WR</sub>)

Figure 34 ADC Conversion Timing

# Package and Reliability

# 5.3 Quality Declaration

Table 48 shows the characteristics of the quality parameters in the XC866.

# Table 48 Quality Parameters

| Parameter                                                             | Symbol           | Limit Values |      | Unit | Notes                                  |

|-----------------------------------------------------------------------|------------------|--------------|------|------|----------------------------------------|

|                                                                       |                  | Min.         | Max. |      |                                        |

| ESD susceptibility<br>according to Human Body<br>Model (HBM)          | V <sub>HBM</sub> | -            | 2000 | V    | Conforming to<br>EIA/JESD22-<br>A114-B |

| ESD susceptibility<br>according to Charged<br>Device Model (CDM) pins | V <sub>CDM</sub> | -            | 500  | V    | Conforming to<br>JESD22-C101-C         |

http://www.infineon.com