Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Discontinued at Digi-Key                                                      |

| Core Processor             | XC800                                                                         |

| Core Size                  | 8-Bit                                                                         |

| Speed                      | 86MHz                                                                         |

| Connectivity               | LINbus, SSI, UART/USART                                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                         |

| Number of I/O              | 19                                                                            |

| Program Memory Size        | 4KB (4K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 768 x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                   |

| Data Converters            | A/D 8x10b                                                                     |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 38-TFSOP (0.173", 4.40mm Width)                                               |

| Supplier Device Package    | PG-TSSOP-38                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xc866l1fraabkxuma1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

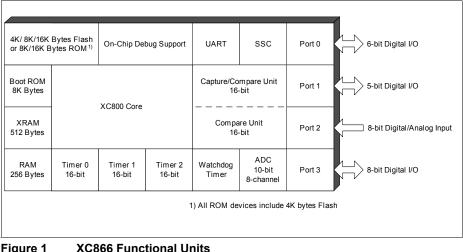

#### 8-Bit Single-Chip Microcontroller XC800 Family

#### 1 **Summary of Features**

- High-performance XC800 Core •

- compatible with standard 8051 processor

- two clocks per machine cycle architecture (for memory access without wait state)

- two data pointers

- On-chip memory

- 8 Kbytes of Boot ROM

- 256 bytes of RAM

- 512 bytes of XRAM

- 4/8/16 Kbytes of Flash; or 8/16 Kbytes of ROM, with additional 4 Kbytes of Flash (includes memory protection strategy)

- I/O port supply at 3.3 V/5.0 V and core logic supply at 2.5 V (generated by embedded voltage regulator)

(further features are on next page)

#### Summary of Features

Features (continued):

infineon

- Reset generation

- Power-On reset

- Hardware reset

- Brownout reset for core logic supply

- Watchdog timer reset

- Power-Down Wake-up reset

- On-chip OSC and PLL for clock generation

- PLL loss-of-lock detection

- Power saving modes

- slow-down mode

- idle mode

- power-down mode with wake-up capability via RXD or EXINT0

- clock gating control to each peripheral

- Programmable 16-bit Watchdog Timer (WDT)

- Four ports

- 19 pins as digital I/O

- 8 pins as digital/analog input

- 8-channel, 10-bit ADC

- Three 16-bit timers

- Timer 0 and Timer 1 (T0 and T1)

- Timer 2

- · Capture/compare unit for PWM signal generation (CCU6)

- Full-duplex serial interface (UART)

- Synchronous serial channel (SSC)

- · On-chip debug support

- 1 Kbyte of monitor ROM (part of the 8-Kbyte Boot ROM)

- 64 bytes of monitor RAM

- PG-TSSOP-38 pin package

- Temperature range T<sub>A</sub>:

- SAF (-40 to 85 °C)

- SAK (-40 to 125 °C)

## infineon

#### **Summary of Features**

#### Table 2Device Summary

|     | -                  |     |    |   |    |            |

|-----|--------------------|-----|----|---|----|------------|

|     | SAK-XC866*-1FRI 3V | 3.3 | -  | 4 | -  | Industrial |

|     | SAF-XC866*-4FRA 3V | 3.3 | 12 | 4 | _  | Automotive |

|     | SAF-XC866*-4FRI 3V | 3.3 | 12 | 4 | _  | Industrial |

|     | SAF-XC866*-2FRA 3V | 3.3 | 4  | 4 | _  | Automotive |

|     | SAF-XC866*-2FRI 3V | 3.3 | 4  | 4 | -  | Industrial |

|     | SAF-XC866*-1FRA 3V | 3.3 | -  | 4 | -  | Automotive |

|     | SAF-XC866*-1FRI 3V | 3.3 | -  | 4 | -  | Industrial |

| ROM | SAK-XC866*-4RRA    | 5.0 | -  | 4 | 16 | Automotive |

|     | SAK-XC866*-4RRI    | 5.0 | -  | 4 | 16 | Industrial |

|     | SAK-XC866*-2RRA    | 5.0 | -  | 4 | 8  | Automotive |

|     | SAK-XC866*-2RRI    | 5.0 | -  | 4 | 8  | Industrial |

|     | SAF-XC866*-4RRA    | 5.0 | -  | 4 | 16 | Automotive |

|     | SAF-XC866*-4RRI    | 5.0 | -  | 4 | 16 | Industrial |

|     | SAF-XC866*-2RRA    | 5.0 | _  | 4 | 8  | Automotive |

|     | SAF-XC866*-2RRI    | 5.0 | -  | 4 | 8  | Industrial |

|     | SAK-XC866*-4RRA 3V | 3.3 | -  | 4 | 16 | Automotive |

|     | SAK-XC866*-4RRI 3V | 3.3 | -  | 4 | 16 | Industrial |

|     | SAK-XC866*-2RRA 3V | 3.3 | -  | 4 | 8  | Automotive |

|     | SAK-XC866*-2RRI 3V | 3.3 | _  | 4 | 8  | Industrial |

|     | SAF-XC866*-4RRA 3V | 3.3 | -  | 4 | 16 | Automotive |

|     | SAF-XC866*-4RRI 3V | 3.3 | -  | 4 | 16 | Industrial |

|     | SAF-XC866*-2RRA 3V | 3.3 | -  | 4 | 8  | Automotive |

|     | SAF-XC866*-2RRI 3V | 3.3 | -  | 4 | 8  | Industrial |

1) Industrial is not for Automotive usage

<sup>2)</sup> The flash memory (P-Flash and D-Flash) can be used for code or data.

Note: The asterisk (\*) above denotes the device configuration letters from Table 1.

#### **Summary of Features**

#### **Ordering Information**

The ordering code for Infineon Technologies microcontrollers provides an exact reference to the required product. This ordering code identifies:

- The derivative itself, i.e. its function set, the temperature range, and the supply voltage

- the package and the type of delivery

For the available ordering codes for the XC866, please refer to your responsible sales representative or your local distributor.

As this document refers to all the derivatives, some descriptions may not apply to a specific product. For simplicity all versions are referred to by the term XC866 throughout this document.

#### XC866

#### **General Device Information**

| Symbol | Pin<br>Number | Туре | Reset<br>State | Function                               |                                                                                                              |

|--------|---------------|------|----------------|----------------------------------------|--------------------------------------------------------------------------------------------------------------|

| P1     |               | I/O  |                | port. It can b                         | -bit bidirectional general purpose I/O<br>e used as alternate functions for the<br>5, UART, and the SSC.     |

| P1.0   | 27            |      | PU             | RXD_0<br>T2EX                          | UART Receive Data Input<br>Timer 2 External Trigger Input                                                    |

| P1.1   | 28            |      | PU             | EXINT3<br>TDO_1<br>TXD_0               | External Interrupt Input 3<br>JTAG Serial Data Output<br>UART Transmit Data Output/<br>Clock Output          |

| P1.5   | 29            |      | PU             | CCPOS0_1<br>EXINT5<br>EXF2_0<br>RXDO_0 | CCU6 Hall Input 0<br>External Interrupt Input 5<br>TImer 2 External Flag Output<br>UART Transmit Data Output |

| P1.6   | 9             |      | PU             | CCPOS1_1<br>T12HR_0<br>EXINT6          | CCU6 Hall Input 1<br>CCU6 Timer 12 Hardware Run<br>Input<br>External Interrupt Input 6                       |

| P1.7   | 10            |      | PU             | CCPOS2_1<br>T13HR_0                    | CCU6 Hall Input 2<br>CCU6 Timer 13 Hardware Run<br>Input                                                     |

| _      |               |      |                |                                        | .6 can be used as a software chip<br>t for the SSC.                                                          |

#### Table 3Pin Definitions and Functions (cont'd)

#### XC866

#### **General Device Information**

| Symbol | Pin<br>Number | Туре | Reset<br>State | Function           |                                                                               |

|--------|---------------|------|----------------|--------------------|-------------------------------------------------------------------------------|

| P3     |               | I    |                |                    | directional general purpose I/O port. It as alternate functions for the CCU6. |

| P3.0   | 32            |      | Hi-Z           | CCPOS1_2<br>CC60_0 | CCU6 Hall Input 1<br>Input/Output of Capture/Compare<br>channel 0             |

| P3.1   | 33            |      | Hi-Z           | CCPOS0_2<br>CC61_2 | CCU6 Hall Input 0<br>Input/Output of Capture/Compare<br>channel 1             |

|        |               |      |                | COUT60_0           | Output of Capture/Compare<br>channel 0                                        |

| P3.2   | 34            |      | Hi-Z           | CCPOS2_2<br>CC61_0 | CCU6 Hall Input 2<br>Input/Output of Capture/Compare<br>channel 1             |

| P3.3   | 35            |      | Hi-Z           | COUT61_0           | Output of Capture/Compare<br>channel 1                                        |

| P3.4   | 36            |      | Hi-Z           | CC62_0             | Input/Output of Capture/Compare<br>channel 2                                  |

| P3.5   | 37            |      | Hi-Z           | COUT62_0           | Output of Capture/Compare<br>channel 2                                        |

| P3.6   | 30            |      | PD             | CTRAP_0            | CCU6 Trap Input                                                               |

| P3.7   | 31            |      | Hi-Z           | EXINT4<br>COUT63_0 | External Interrupt Input 4<br>Output of Capture/Compare<br>channel 3          |

#### Table 3Pin Definitions and Functions (cont'd)

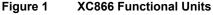

#### 3.2 Memory Organization

İnfineon

The XC866 CPU operates in the following five address spaces:

- · 8 Kbytes of Boot ROM program memory

- 256 bytes of internal RAM data memory

- 512 bytes of XRAM memory (XRAM can be read/written as program memory or external data memory)

- a 128-byte Special Function Register area

- 4/8/16 Kbytes of Flash program memory (Flash devices); or 8/16 Kbytes of ROM program memory, with additional 4 Kbytes of Flash (ROM devices)

Figure 6 illustrates the memory address spaces of the XC866-4FR device.

#### Figure 6 Memory Map of XC866 Flash Devices

# infineon

#### **Functional Description**

#### Table 8System Control Register Overview (cont'd)

| Addr            | Register Name                       |                                    | Bit       | 7                        | 6   | 5    | 4         | 3          | 2             | 1           | 0            |

|-----------------|-------------------------------------|------------------------------------|-----------|--------------------------|-----|------|-----------|------------|---------------|-------------|--------------|

| B3 <sub>H</sub> | ID                                  | Reset: 01 <sub>H</sub>             | Bit Field | PRODID                   |     |      |           | VERID      |               |             |              |

|                 | Identity Register                   |                                    | Туре      |                          |     | r    |           |            | r             |             |              |

| B4 <sub>H</sub> | PMCON0<br>Power Mode Control Re     | Reset: 00 <sub>H</sub><br>gister 0 | Bit Field | 0 WDT WKRS WK<br>RST SEL |     | SD   | PD        |            | WS            |             |              |

|                 |                                     |                                    | Туре      | r                        | rwh | rwh  | rw        | rw         | rwh           | r           | N            |

| B5 <sub>H</sub> | PMCON1<br>Power Mode Control Re     | Reset: 00 <sub>H</sub><br>gister 1 | Bit Field |                          |     | 0    |           | T2_DIS     | CCU<br>_DIS   | SSC<br>_DIS | ADC<br>_DIS  |

|                 |                                     |                                    | Туре      |                          |     | r    |           | rw         | rw            | rw          | rw           |

| B6 <sub>H</sub> | OSC_CON<br>OSC Control Register     | Reset: 08 <sub>H</sub>             | Bit Field |                          | 0   |      | OSC<br>PD | XPD        | OSC<br>SS     | ORD<br>RES  | OSCR         |

|                 |                                     |                                    | Туре      |                          | r   |      | rw        | rw         | rw            | rwh         | rh           |

| B7 <sub>H</sub> | PLL_CON<br>PLL Control Register     | Reset: 20 <sub>H</sub>             | Bit Field |                          | N   | VIC  |           | VCO<br>BYP | OSC<br>DISC   | RESLD       | LOCK         |

|                 |                                     |                                    | Туре      |                          | r   | w    |           | rw         | rw            | rwh         | rh           |

| BA <sub>H</sub> | CMCON<br>Clock Control Register     | Reset: 00 <sub>H</sub>             | Bit Field | VCO<br>SEL               |     | 0    |           | CLKREL     |               | REL         |              |

|                 |                                     |                                    | Туре      | rw                       |     | r    |           |            | r             | w           |              |

| BB <sub>H</sub> | PASSWD<br>Password Register         | Reset: 07 <sub>H</sub>             | Bit Field |                          |     | PASS |           |            | PROTE<br>CT_S | MC          | DE           |

|                 |                                     |                                    | Туре      |                          |     | w    |           |            | rh            | n           | N            |

| BC <sub>H</sub> | FEAL                                | Reset: 00 <sub>H</sub>             | Bit Field |                          |     | E    | CCERR     | ADDR[7:    | 0]            |             |              |

|                 | Flash Error Address Reg             | jister Low                         | Туре      |                          |     |      | I         | 'n         |               |             |              |

| BD <sub>H</sub> | FEAH                                | Reset: 00 <sub>H</sub>             | Bit Field |                          |     | EC   | CERRA     | ADDR[15    | :8]           |             |              |

|                 | Flash Error Address Reg             | jister High                        | Туре      |                          |     |      |           | ħ          |               |             |              |

| BE <sub>H</sub> | COCON<br>Clock Output Control Re    | Reset: 00 <sub>H</sub><br>gister   | Bit Field | (                        | )   | TLEN | COUT<br>S |            | CO            | REL         |              |

|                 |                                     |                                    | Туре      |                          | r   | rw   | rw        |            | r             | w           |              |

| E9 <sub>H</sub> | MISC_CON<br>Miscellaneous Control R | Reset: 00 <sub>H</sub><br>egister  | Bit Field |                          |     |      | 0         |            |               |             | DFLAS<br>HEN |

|                 |                                     |                                    | Туре      |                          |     |      | r         |            |               |             | rwh          |

| RMAP =          | 0, Page 3                           |                                    | -         |                          |     |      | -         |            |               |             |              |

| B3 <sub>H</sub> | XADDRH                              | Reset: F0 <sub>H</sub>             | Bit Field |                          |     |      | AD        | DRH        |               |             |              |

|                 | On-Chip XRAM Address                | Higher Order                       | Туре      |                          |     |      | r         | w          |               |             |              |

The WDT SFRs can be accessed in the mapped memory area (RMAP = 1).

#### Table 9 WDT Register Overview

| Addr            | Register Name                        |                                     | Bit       | 7  | 6 | 5          | 4         | 3      | 2         | 1         | 0         |

|-----------------|--------------------------------------|-------------------------------------|-----------|----|---|------------|-----------|--------|-----------|-----------|-----------|

| RMAP =          | 1                                    |                                     |           |    |   |            |           |        |           |           |           |

| BB <sub>H</sub> | WDTCON F<br>Watchdog Timer Control R | Reset: 00 <sub>H</sub><br>egister   | Bit Field |    | 0 | WINB<br>EN | WDT<br>PR | 0      | WDT<br>EN | WDT<br>RS | WDT<br>IN |

|                 |                                      |                                     | Туре      |    | r | rw         | rh        | r      | rw        | rwh       | rw        |

| BC <sub>H</sub> |                                      | Reset: 00 <sub>H</sub>              | Bit Field |    |   |            | WD1       | REL    |           |           |           |

|                 | Watchdog Timer Reload Re             | egister                             | Туре      | rw |   |            |           |        |           |           |           |

| BD <sub>H</sub> | Watchdog Window-Bounda               | Reset: 00 <sub>H</sub><br>ary Count | Bit Field |    |   |            | WDT       | WINB   |           |           |           |

|                 | Register                             |                                     | Туре      |    |   |            | r         | N      |           |           |           |

| BEH             |                                      | Reset: 00 <sub>H</sub>              | Bit Field |    |   |            | WDT       | [7:0]  |           |           |           |

|                 | Watchdog Timer Register L            | _ow                                 | Туре      |    |   |            | r         | h      |           |           |           |

| BF <sub>H</sub> |                                      | Reset: 00 <sub>H</sub>              | Bit Field |    |   |            | WDT       | [15:8] |           |           |           |

|                 | Watchdog Timer Register H            | ligh                                | Туре      |    |   |            | r         | h      |           |           |           |

#### XC866

#### **Functional Description**

The Port SFRs can be accessed in the standard memory area (RMAP = 0).

#### Table 10 Port Register Overview

| Addr            | Register Name                        |                        | Bit               | 7   | 6       | 5        | 4        | 3        | 2        | 1        | 0        |

|-----------------|--------------------------------------|------------------------|-------------------|-----|---------|----------|----------|----------|----------|----------|----------|

| RMAP =          | -                                    |                        |                   | -   | -       | -        | -        | -        | _        | -        | -        |

| B2 <sub>H</sub> | PORT PAGE                            | Reset: 00 <sub>H</sub> | Bit Field         | C   | P       | ST       | NR       | 0        |          | PAGE     |          |

| D-H             | Page Register for PORT               |                        | Туре              | -   | N       |          | N        | r        |          | rwh      |          |

| RMAP =          | 0, Page 0                            |                        | 1300              |     |         |          |          | •        |          |          |          |

| 80 <sub>H</sub> | P0_DATA                              | Reset: 00 <sub>H</sub> | Bit Field         |     | 0       | P5       | P4       | P3       | P2       | P1       | P0       |

| O H             | P0 Data Register                     | Hessell oog            | Туре              |     | r       | rwh      | rwh      | rwh      | rwh      | rwh      | rwh      |

| 86 <sub>H</sub> | P0 DIR                               | Reset: 00 <sub>H</sub> | Bit Field         |     | 0       | P5       | P4       | P3       | P2       | P1       | P0       |

| OOH             | P0 Direction Register                | Hessell oog            | Туре              |     | r       | rw       | rw       | rw       | rw       | rw       | rw       |

| 90 <sub>H</sub> | P1 DATA                              | Reset: 00 <sub>H</sub> | Bit Field         | P7  | P6      | P5       |          | 0        |          | P1       | P0       |

| чч              | P1 Data Register                     | Hessell oog            | Туре              | rwh | rwh     | rwh      |          | r        |          | rwh      | rwh      |

| 91 <sub>H</sub> | P1 DIR                               | Reset: 00 <sub>H</sub> | Bit Field         | P7  | P6      | P5       |          | 0        |          | P1       | P0       |

| ЧH              | P1 Direction Register                | Hessell oog            | Туре              | rw  | rw      | rw       |          | r        |          | rw       | rw       |

| А0 <sub>н</sub> | P2 DATA                              | Reset: 00 <sub>H</sub> | Bit Field         | P7  | P6      | P5       | P4       | P3       | P2       | P1       | P0       |

| AVH             | P2 Data Register                     | Reset. Oug             | Туре              | rwh | rwh     | rwh      | rwh      | rwh      | rwh      | rwh      | rwh      |

| A1 <sub>H</sub> | P2 DIR                               | Reset: 00 <sub>H</sub> | Bit Field         | P7  | P6      | P5       | P4       | P3       | P2       | P1       | P0       |

| П               | P2 Direction Register                | Neset. Oug             | Туре              | rw  | rw      | rw       | rw       | rw       | rw       | rw       | rw       |

| B0 <sub>н</sub> | P3 DATA                              | Reset: 00 <sub>H</sub> | Bit Field         | P7  | P6      | P5       | P4       | P3       | P2       | P1       | P0       |

| BOH             | P3 Data Register                     | Reset. 00H             | Туре              | rwh | rwh     | rwh      | rwh      | rwh      | rwh      | rwh      | rwh      |

| D1              | P3 DIR                               | Reset: 00 <sub>H</sub> | Bit Field         | P7  | P6      | P5       | P4       | P3       | P2       | P1       | P0       |

| B1 <sub>H</sub> | P3 Direction Register                | Reset. 00H             |                   | rw  | rw      | rw       | r4       | rs<br>rw | rv       | rw       | rw       |

|                 | 0, Page 1                            |                        | Туре              | IW  | TW      | IW       | TW       | IW       | TW       | IW       | TW       |

|                 | P0 PUDSEL                            | Booot: EE              | Bit Field         |     | 0       | P5       | P4       | P3       | P2       | P1       | P0       |

| 80 <sub>H</sub> | P0_P0D3EL<br>P0 Pull-Up/Pull-Down Se | Reset: FF <sub>H</sub> |                   |     | -       | -        |          |          |          |          |          |

| 00              | P0 PUDEN                             |                        | Type<br>Bit Field |     | r<br>D  | rw<br>P5 | rw<br>P4 | rw<br>P3 | rw<br>P2 | rw<br>P1 | rw<br>P0 |

| 86 <sub>H</sub> | P0_P0DEN<br>P0 Pull-Up/Pull-Down Er  | Reset: C4 <sub>H</sub> |                   |     | -       |          |          |          |          |          |          |

| ~~              |                                      |                        | Type              |     | r<br>P6 | rw<br>P5 | rw       | rw       | rw       | rw<br>P1 | rw<br>P0 |

| 90 <sub>H</sub> | P1_PUDSEL<br>P1 Pull-Up/Pull-Down Se | Reset: FF <sub>H</sub> | Bit Field         | P7  |         | -        |          | 0        |          |          |          |

| 04              |                                      |                        | Type              | rw  | rw      | rw       |          | r        |          | rw       | rw       |

| 91 <sub>H</sub> | P1_PUDEN<br>P1 Pull-Up/Pull-Down Er  | Reset: FF <sub>H</sub> | Bit Field         | P7  | P6      | P5       |          | 0        |          | P1       | P0       |

| ••              |                                      |                        | Туре              | rw  | rw      | rw       | 54       | r        |          | rw       | rw       |

| A0 <sub>H</sub> | P2_PUDSEL<br>P2 Pull-Up/Pull-Down Se | Reset: FF <sub>H</sub> | Bit Field         | P7  | P6      | P5       | P4       | P3       | P2       | P1       | P0       |

|                 |                                      |                        | Туре              | rw  | rw      | rw       | rw       | rw       | rw       | rw       | rw       |

| A1 <sub>H</sub> | P2_PUDEN<br>P2 Pull-Up/Pull-Down Er  | Reset: 00 <sub>H</sub> | Bit Field         | P7  | P6      | P5       | P4       | P3       | P2       | P1       | P0       |

|                 |                                      |                        | Туре              | rw  | rw      | rw       | rw       | rw       | rw       | rw       | rw       |

| в0 <sub>Н</sub> | P3_PUDSEL<br>P3 Pull-Up/Pull-Down Se | Reset: BF <sub>H</sub> | Bit Field         | P7  | P6      | P5       | P4       | P3       | P2       | P1       | P0       |

| -               |                                      |                        | Туре              | rw  | rw      | rw       | rw       | rw       | rw       | rw       | rw       |

| B1 <sub>H</sub> | P3_PUDEN<br>P3 Pull-Up/Pull-Down Er  | Reset: 40 <sub>H</sub> | Bit Field         | P7  | P6      | P5       | P4       | P3       | P2       | P1       | P0       |

|                 | •                                    | iaule register         | Туре              | rw  | rw      | rw       | rw       | rw       | rw       | rw       | rw       |

|                 | 0, Page 2                            |                        | lava:             |     |         |          |          |          |          |          |          |

| 80 <sub>H</sub> | P0_ALTSEL0                           | Reset: 00 <sub>H</sub> | Bit Field         |     | 0       | P5       | P4       | P3       | P2       | P1       | P0       |

|                 | P0 Alternate Select 0 Re             | •                      | Туре              |     | r       | rw       | rw       | rw       | rw       | rw       | rw       |

| 86 <sub>H</sub> | P0_ALTSEL1                           | Reset: 00 <sub>H</sub> | Bit Field         |     | 0       | P5       | P4       | P3       | P2       | P1       | P0       |

|                 | P0 Alternate Select 1 Re             | -                      | Туре              |     | r       | rw       | rw       | rw       | rw       | rw       | rw       |

| 90 <sub>H</sub> | P1_ALTSEL0                           | Reset: 00 <sub>H</sub> | Bit Field         | P7  | P6      | P5       |          | 0        |          | P1       | P0       |

|                 | P1 Alternate Select 0 Re             | •                      | Туре              | rw  | rw      | rw       |          | r        |          | rw       | rw       |

| 91 <sub>H</sub> | P1_ALTSEL1                           | Reset: 00 <sub>H</sub> | Bit Field         | P7  | P6      | P5       |          | 0        |          | P1       | P0       |

|                 | P1 Alternate Select 1 Re             | gister                 | Туре              | rw  | rw      | rw       |          | r        |          | rw       | rw       |

| B0 <sub>H</sub> | P3_ALTSEL0                           | Reset: 00 <sub>H</sub> | Bit Field         | P7  | P6      | P5       | P4       | P3       | P2       | P1       | P0       |

|                 | P3 Alternate Select 0 Re             | gister                 | Туре              | rw  | rw      | rw       | rw       | rw       | rw       | rw       | rw       |

#### Table 11 ADC Register Overview (cont'd)

| Addr            | Register Name                         |                        | Bit               | 7     | 6       | 5   | 4     | 3        | 2    | 1    | 0         |

|-----------------|---------------------------------------|------------------------|-------------------|-------|---------|-----|-------|----------|------|------|-----------|

| CA <sub>H</sub> | ADC_RESR0L                            | Reset: 00 <sub>H</sub> | Bit Field         | RESU  | LT[1:0] | 0   | VF    | DRC      |      | CHNR | 1         |

|                 | Result Register 0 Low                 |                        | Туре              | r     | h       | r   | rh    | rh       |      | rh   |           |

| CB <sub>H</sub> | ADC_RESR0H                            | Reset: 00 <sub>H</sub> | Bit Field         |       |         |     | RESU  | LT[9:2]  | 1    |      |           |

|                 | Result Register 0 High                |                        | Туре              |       |         |     | r     | ħ        |      |      |           |

| ССн             | ADC_RESR1L                            | Reset: 00 <sub>H</sub> | Bit Field         | RESU  | LT[1:0] | 0   | VF    | DRC      |      | CHNR |           |

|                 | Result Register 1 Low                 |                        | Туре              | r     | h       | r   | rh    | rh       |      | rh   |           |

| CD <sub>H</sub> | ADC_RESR1H                            | Reset: 00 <sub>H</sub> | Bit Field         |       |         |     | RESU  | LT[9:2]  | 1    |      |           |

|                 | Result Register 1 High                |                        | Туре              |       |         |     | r     | h i      |      |      |           |

| CEH             | ADC_RESR2L                            | Reset: 00 <sub>H</sub> | Bit Field         | RESU  | LT[1:0] | 0   | VF    | DRC      |      | CHNR |           |

|                 | Result Register 2 Low                 |                        | Туре              | r     | h       | r   | rh    | rh       |      | rh   |           |

| CF <sub>H</sub> | ADC_RESR2H                            | Reset: 00 <sub>H</sub> | Bit Field         |       |         |     | RESU  | LT[9:2]  |      |      |           |

|                 | Result Register 2 High                |                        | Туре              |       |         |     | r     | ħ        |      |      |           |

| D2 <sub>H</sub> | ADC_RESR3L                            | Reset: 00 <sub>H</sub> | Bit Field         | RESU  | LT[1:0] | 0   | VF    | DRC      |      | CHNR |           |

|                 | Result Register 3 Low                 |                        | Туре              | r     | h       | r   | rh    | rh       |      | rh   |           |

| D3 <sub>H</sub> | ADC_RESR3H                            | Reset: 00 <sub>H</sub> | Bit Field         |       |         |     | RESU  | LT[9:2]  | 1    |      |           |

|                 | Result Register 3 High                |                        | Туре              |       |         |     |       | h i      |      |      |           |

| RMAP =          | 0, Page 3                             |                        |                   |       |         |     |       |          |      |      |           |

| CA <sub>H</sub> | ADC RESRAOL                           | Reset: 00 <sub>H</sub> | Bit Field         | RE    | ESULT[2 | :0] | VF    | DRC      |      | CHNR |           |

| - 11            | Result Register 0, View               |                        | Туре              |       | rh      |     | rh    | rh       |      | rh   |           |

| CB <sub>H</sub> | ADC RESRA0H                           | Reset: 00 <sub>H</sub> | Bit Field         |       |         |     | RESUL | T[10:3]  |      |      |           |

| n               | Result Register 0, View               |                        | Туре              |       |         |     |       | h        |      |      |           |

| ССн             | ADC_RESRA1L                           | Reset: 00 <sub>H</sub> | Bit Field         | RE    | ESULT[2 | :01 | VF    | DRC      |      | CHNR |           |

| H               | Result Register 1, View               |                        | Туре              |       | rh      | ]   | rh    | rh       |      | rh   |           |

| CD <sub>H</sub> | ADC RESRA1H                           | Reset: 00 <sub>H</sub> | Bit Field         |       |         |     |       | T[10:3]  |      |      |           |

| 0DH             | Result Register 1, View               |                        | Туре              |       |         |     |       | h        |      |      |           |

| CEH             | ADC RESRA2L                           | Reset: 00 <sub>H</sub> | Bit Field         | RF    | ESULT[2 | ·01 | VF .  | DRC      |      | CHNR |           |

| 0-H             | Result Register 2, View               |                        | Туре              |       |         | .0] | rh    | rh       |      | rh   |           |

| CF <sub>H</sub> | ADC RESRA2H                           | Reset: 00 <sub>H</sub> | Bit Field         |       |         |     |       | T[10:3]  |      |      |           |

| 0. H            | Result Register 2, View               |                        | Туре              |       |         |     |       | h        |      |      |           |

| D2 <sub>H</sub> | ADC RESRA3L                           | Reset: 00 <sub>H</sub> | Bit Field         | RF    | ESULT[2 | ·01 | VF .  | DRC      |      | CHNR |           |

| 5-H             | Result Register 3, View               |                        | Туре              |       | rh      | .0] | rh    | rh       |      | rh   |           |

| D3 <sub>H</sub> | ADC RESRA3H                           | Reset: 00 <sub>H</sub> | Bit Field         |       |         |     |       | _T[10:3] |      |      |           |

| DOH             | Result Register 3, View /             |                        | Туре              |       |         |     |       | h        |      |      |           |

| RMAP =          | 0, Page 4                             |                        | 1300              |       |         |     |       |          |      |      |           |

| CA <sub>H</sub> | ADC RCR0                              | Reset: 00 <sub>H</sub> | Bit Field         | VFCTR | WFR     | 0   | IEN   | l        | 0    |      | DRCT      |

| o, H            | Result Control Register (             |                        | Bittiola          |       |         | Ũ   |       |          | Ũ    |      | R         |

|                 |                                       |                        | Туре              | rw    | rw      | r   | rw    |          | r    |      | rw        |

| СВн             | ADC_RCR1                              | Reset: 00 <sub>H</sub> | Bit Field         | VFCTR | WFR     | 0   | IEN   |          | 0    |      | DRCT      |

|                 | Result Control Register 1             |                        |                   |       |         |     |       |          |      |      | R         |

|                 |                                       |                        | Туре              | rw    | rw      | r   | rw    |          | r    |      | rw        |

| CCH             | ADC_RCR2<br>Result Control Register 2 | Reset: 00 <sub>H</sub> | Bit Field         | VFCTR | WFR     | 0   | IEN   |          | 0    |      | DRCT<br>R |

|                 | Ç. A                                  |                        | Туре              | rw    | rw      | r   | rw    |          | r    |      | rw        |

| CD <sub>H</sub> | ADC_RCR3<br>Result Control Register 3 | Reset: 00 <sub>H</sub> | Bit Field         | VFCTR | WFR     | 0   | IEN   |          | 0    |      | DRCT      |

|                 |                                       |                        | Туре              | rw    | rw      | r   | rw    |          | r    |      | rw        |

| CEH             | ADC_VFCR                              | Reset: 00 <sub>H</sub> | Bit Field         | 1 VV  |         | )   | 1 44  | VFC3     | VFC2 | VFC1 | VFC0      |

| UCH             | Valid Flag Clear Register             |                        | Бії Гіеій<br>Туре |       |         | r   |       | WFC3     | WFC2 | W    | WFCU      |

|                 | i g men regiotoi                      |                        | iyhe              | 1     |         |     |       | vv       | ٧V   | vv   | vv        |

#### Table 13 CCU6 Register Overview (cont'd)

| Addr            | Register Name                                                             | Bit       | 7     | 6            | 5            | 4          | 3            | 2          | 1            | 0          |

|-----------------|---------------------------------------------------------------------------|-----------|-------|--------------|--------------|------------|--------------|------------|--------------|------------|

| FF <sub>H</sub> | CCU6_TRPCTRH Reset: 00 <sub>H</sub>                                       | Bit Field |       | TRPEN        |              |            | TR           | PEN        |              |            |

|                 | Trap Control Register High                                                |           | N     | 13           |              |            |              |            |              |            |

|                 |                                                                           | Туре      | rw    | rw           |              |            | r            | w          |              |            |

| RMAP =          | 0, Page 3                                                                 |           |       |              |              |            |              |            |              |            |

| 9A <sub>H</sub> | CCU6_MCMOUTL Reset: 00 <sub>H</sub><br>Multi-Channel Mode Output Register | Bit Field | 0     | R            |              |            | MC           | MP         |              |            |

|                 | Low                                                                       | Туре      | r     | rh           |              |            | r            | h          |              |            |

| 9B <sub>H</sub> | CCU6_MCMOUTH Reset: 00 <sub>H</sub><br>Multi-Channel Mode Output Register | Bit Field | (     | )            |              | CURH       |              |            | EXPH         |            |

|                 | High                                                                      | Туре      | 1     | r            |              | rh         |              |            | rh           |            |

| 9C <sub>H</sub> | CCU6_ISL Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Status       | Bit Field | T12PM | T12OM        | ICC62F       | R          | ICC61F       | R          | ICC60F       | ICC60<br>R |

|                 | Register Low                                                              | Туре      | rh    | rh           | rh           | rh         | rh           | rh         | rh           | rh         |

| 9D <sub>H</sub> | CCU6_ISH Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Status       | Bit Field | STR   | IDLE         | WHE          | CHE        | TRPS         | TRPF       | T13PM        | T13CM      |

|                 | Register High                                                             | Туре      | rh    | rh           | rh           | rh         | rh           | rh         | rh           | rh         |

| 9E <sub>H</sub> | CCU6_PISEL0L Reset: 00 <sub>H</sub>                                       | Bit Field | IST   | RP           | ISC          | C62        | ISC          | C61        | ISC          | C60        |

|                 | Port Input Select Register 0 Low                                          | Туре      | r     | w            | r            | w          | r            | w          | r            | w          |

| 9F <sub>H</sub> | CCU6_PISEL0H Reset: 00 <sub>H</sub><br>Port Input Select Register 0 High  | Bit Field | IST1  | 2HR          | ISP          | OS2        | ISP          | OS1        | ISP          | OS0        |

|                 |                                                                           | Туре      | n     | w            | r            | w          | r            | w          | n            | w          |

| A4 <sub>H</sub> | CCU6_PISEL2 Reset: 00 <sub>H</sub>                                        | Bit Field |       |              | (            | C          |              |            | IST1         | 3HR        |

|                 | Port Input Select Register 2                                              | Туре      |       |              |              | r          |              |            | n            | w          |

| FA <sub>H</sub> | CCU6_T12L Reset: 00 <sub>H</sub>                                          | Bit Field |       |              |              | T12        | CVL          |            |              |            |

|                 | Timer T12 Counter Register Low                                            | Туре      |       |              |              | n          | vh           |            |              |            |

| FB <sub>H</sub> | CCU6_T12H Reset: 00 <sub>H</sub>                                          | Bit Field |       |              |              | T12        | CVH          |            |              |            |

|                 | Timer T12 Counter Register High                                           | Туре      |       |              |              | n          | vh           |            |              |            |

| FC <sub>H</sub> | CCU6_T13L Reset: 00 <sub>H</sub>                                          | Bit Field |       |              |              | T13        | CVL          |            |              |            |

|                 | Timer T13 Counter Register Low                                            | Туре      |       |              |              | n          | vh           |            |              |            |

| FD <sub>H</sub> | CCU6_T13H Reset: 00 <sub>H</sub>                                          | Bit Field |       |              |              | T13        | CVH          |            |              |            |

|                 | Timer T13 Counter Register High                                           | Туре      |       |              |              | n          | vh           |            |              |            |

| FE <sub>H</sub> | CCU6_CMPSTATL Reset: 00 <sub>H</sub><br>Compare State Register Low        | Bit Field | 0     | CC63<br>ST   | CCPO<br>S2   | CCPO<br>S1 | CCPO<br>S0   | CC62<br>ST | CC61<br>ST   | CC60<br>ST |

|                 |                                                                           | Туре      | r     | rh           | rh           | rh         | rh           | rh         | rh           | rh         |

| FF <sub>H</sub> | CCU6_CMPSTATH Reset: 00 <sub>H</sub><br>Compare State Register High       | Bit Field | T13IM | COUT<br>63PS | COUT<br>62PS | CC62<br>PS | COUT<br>61PS | CC61<br>PS | COUT<br>60PS | CC60<br>PS |

|                 |                                                                           | Туре      | rwh   | rwh          | rwh          | rwh        | rwh          | rwh        | rwh          | rwh        |

The SSC SFRs can be accessed in the standard memory area (RMAP = 0).

#### Table 14SSC Register Overview

| Addr            | Register Name                            |                        | Bit       | 7  | 6  | 5  | 4  | 3 | 2   | 1   | 0   |

|-----------------|------------------------------------------|------------------------|-----------|----|----|----|----|---|-----|-----|-----|

| RMAP =          | 0                                        |                        | •         |    |    |    |    |   |     |     |     |

| A9 <sub>H</sub> | SSC_PISEL                                | Reset: 00 <sub>H</sub> | Bit Field |    |    | 0  |    |   | CIS | SIS | MIS |

|                 | Port Input Select Regist                 | er                     | Туре      |    |    | r  |    |   | rw  | rw  | rw  |

| AA <sub>H</sub> | SSC_CONL                                 | Reset: 00 <sub>H</sub> | Bit Field | LB | PO | PH | HB |   | В   | М   |     |

|                 | Control Register Low<br>Programming Mode |                        | Туре      | rw | rw | rw | rw |   | r   | w   |     |

|                 | Operating Mode                           |                        | Bit Field |    |    | 0  |    |   | B   | С   |     |

|                 |                                          |                        | Туре      |    |    | r  |    |   | r   | h   |     |

For power saving purposes, the clocks may be disabled or slowed down according to **Table 23**.

#### Table 23System frequency (f<sub>sys</sub> = 80 MHz)

| Power Saving Mode | Action                                                                                                                                    |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Idle              | Clock to the CPU is disabled.                                                                                                             |

| Slow-down         | Clocks to the CPU and all the peripherals, including CCU6, are divided by a common programmable factor defined by bit field CMCON.CLKREL. |

| Power-down        | Oscillator and PLL are switched off.                                                                                                      |

• 8-bit reload value (BR\_VALUE) for the baud rate timer defined by register BG The following formulas calculate the final baud rate without and with the fractional divider respectively:

baud rate =

$$\frac{f_{PCLK}}{16 \times 2^{BRPRE} \times (BR_VALUE + 1)}$$

where  $2^{BRPRE} \times (BR_VALUE + 1) > 1$

baud rate =

$$\frac{f_{PCLK}}{16 \times 2^{BRPRE} \times (BR VALUE + 1)} \times \frac{STEP}{256}$$

The maximum baud rate that can be generated is limited to  $f_{PCLK}/32$ . Hence, for a module clock of 26.7 MHz, the maximum achievable baud rate is 0.83 MBaud.

Standard LIN protocal can support a maximum baud rate of 20kHz, the baud rate accuracy is not critical and the fractional divider can be disabled. Only the prescaler is used for auto baud rate calculation. For LIN fast mode, which supports the baud rate of 20kHz to 115.2kHz, the higher baud rates require the use of the fractional divider for greater accuracy.

**Table 26** lists the various commonly used baud rates with their corresponding parameter settings and deviation errors. The fractional divider is disabled and a module clock of 26.7 MHz is used.

| Baud rate  | Prescaling Factor<br>(2 <sup>BRPRE</sup> ) | Reload Value<br>(BR_VALUE + 1) | Deviation Error |

|------------|--------------------------------------------|--------------------------------|-----------------|

| 19.2 kBaud | 1 (BRPRE=000 <sub>B</sub> )                | 87 (57 <sub>H</sub> )          | -0.22 %         |

| 9600 Baud  | 1 (BRPRE=000 <sub>B</sub> )                | 174 (AE <sub>H</sub> )         | -0.22 %         |

| 4800 Baud  | 2 (BRPRE=001 <sub>B</sub> )                | 174 (AE <sub>H</sub> )         | -0.22 %         |

| 2400 Baud  | 4 (BRPRE=010 <sub>B</sub> )                | 174 (AE <sub>H</sub> )         | -0.22 %         |

Table 26

Typical Baud rates for UART with Fractional Divider disabled

The fractional divider allows baud rates of higher accuracy (lower deviation error) to be generated. **Table 27** lists the resulting deviation errors from generating a baud rate of

For module clock  $f_{ADC}$  = 26.7 MHz, the analog clock  $f_{ADCI}$  frequency can be selected as shown in **Table 30**.

| Module Clock f <sub>ADC</sub> | СТС                       | Prescaling Ratio | Analog Clock f <sub>ADCI</sub> |  |  |

|-------------------------------|---------------------------|------------------|--------------------------------|--|--|

| 26.7 MHz                      | 00 <sub>B</sub>           | ÷ 2              | 13.3 MHz (N.A)                 |  |  |

|                               | 01 <sub>B</sub>           | ÷ 3              | 8.9 MHz                        |  |  |

|                               | 10 <sub>B</sub>           | ÷ 4              | 6.7 MHz                        |  |  |

|                               | 11 <sub>B</sub> (default) | ÷ 32             | 833.3 kHz                      |  |  |

#### Table 30f\_ADCI Frequency Selection

As  $f_{ADCI}$  cannot exceed 10 MHz, bit field CTC should not be set to  $00_B$  when  $f_{ADC}$  is 26.7 MHz. During slow-down mode where  $f_{ADC}$  may be reduced to 13.3 MHz, 6.7 MHz etc., CTC can be set to  $00_B$  as long as the divided analog clock  $f_{ADCI}$  does not exceed 10 MHz. However, it is important to note that the conversion error could increase due to loss of charges on the capacitors, if  $f_{ADC}$  becomes too low during slow-down mode.

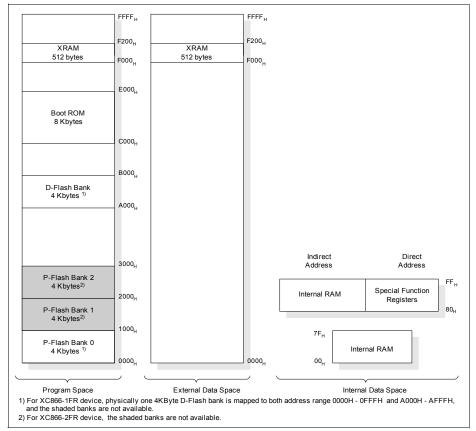

#### 3.18.2 ADC Conversion Sequence

The analog-to-digital conversion procedure consists of the following phases:

- Synchronization phase (t<sub>SYN</sub>)

- Sample phase (t<sub>S</sub>)

- Conversion phase

- Write result phase (t<sub>WR</sub>)

Figure 34 ADC Conversion Timing

#### 4.2 DC Parameters

#### 4.2.1 Input/Output Characteristics

#### Table 34 Input/Output Characteristics (Operating Conditions apply)

| Parameter                                                     | Symbol              |   | Limit Values                 |                             | Unit |                          |

|---------------------------------------------------------------|---------------------|---|------------------------------|-----------------------------|------|--------------------------|

|                                                               |                     |   | min.                         | n. max.                     |      | Remarks                  |

| V <sub>DDP</sub> = 5V Range                                   |                     |   |                              |                             |      |                          |

| Output low voltage                                            | V <sub>OL</sub> C   | С | -                            | 1.0                         | V    | I <sub>OL</sub> = 15 mA  |

|                                                               |                     |   | _                            | 0.4                         | V    | I <sub>OL</sub> = 5 mA   |

| Output high voltage                                           | V <sub>OH</sub> C   | С | V <sub>DDP</sub> -<br>1.0    | -                           | V    | I <sub>OH</sub> = -15 mA |

|                                                               |                     |   | V <sub>DDP</sub> - 0.4       | -                           | V    | I <sub>OH</sub> = -5 mA  |

| Input low voltage on<br>port pins<br>(all except P0.0 & P0.1) | V <sub>ILP</sub> S  | R | -                            | $0.3 \times V_{\text{DDP}}$ | V    | CMOS Mode                |

| nput low voltage on<br>P0.0 & P0.1                            | V <sub>ILP0</sub> S | R | -0.2                         | $0.3 \times V_{\text{DDP}}$ | V    | CMOS Mode                |

| nput low voltage on<br>RESET pin                              | V <sub>ILR</sub> S  | R | -                            | $0.3 \times V_{\text{DDP}}$ | V    | CMOS Mode                |

| nput low voltage on<br>ГMS pin                                | V <sub>ILT</sub> S  | R | -                            | $0.3 \times V_{ m DDP}$     | V    | CMOS Mode                |

| nput high voltage on<br>oort pins<br>all except P0.0 & P0.1)  | V <sub>IHP</sub> S  | R | $0.7 \times V_{\text{DDP}}$  | -                           | V    | CMOS Mode                |

| nput high voltage on<br>P0.0 & P0.1                           | V <sub>IHP0</sub> S | R | $0.7 \times V_{\text{DDP}}$  | V <sub>DDP</sub>            | V    | CMOS Mode                |

| nput high voltage on<br>RESET pin                             | V <sub>IHR</sub> S  | R | $0.7 \times V_{\text{DDP}}$  | -                           | V    | CMOS Mode                |

| nput high voltage on<br>MS pin                                | V <sub>IHT</sub> S  | R | $0.75 \times V_{\text{DDP}}$ | -                           | V    | CMOS Mode                |

| nput Hysteresis <sup>1)</sup> on<br>Port pins                 | HYS C               | С | $0.08 \times V_{\text{DDP}}$ | -                           | V    | CMOS Mode                |

| Input Hysteresis <sup>1)</sup> on<br>XTAL1                    | HYSXC               | С | $0.07 \times V_{ m DDC}$     | -                           | V    |                          |

**Electrical Parameters**

#### 4.2.2 Supply Threshold Characteristics

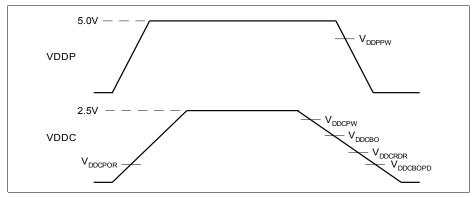

Figure 36 Supply Threshold Parameters

#### Table 35 Supply Threshold Parameters (Operating Conditions apply)

| Parameters                                                         | Symbol               |    | Lii  | mit Val | ues  | Unit | Remarks                  |

|--------------------------------------------------------------------|----------------------|----|------|---------|------|------|--------------------------|

|                                                                    |                      |    | min. | typ.    | max. |      |                          |

| V <sub>DDC</sub> prewarning voltage <sup>1)</sup>                  | V <sub>DDCPW</sub>   | СС | 2.2  | 2.3     | 2.4  | V    |                          |

| $V_{\text{DDC}}$ brownout voltage in active mode <sup>1)</sup>     | V <sub>DDCBO</sub>   | СС | 2.0  | 2.1     | 2.2  | V    | XC866-4FR,<br>XC866-2FR  |

|                                                                    |                      |    | 2.0  | 2.1     | 2.3  | V    | XC866-1FR,<br>ROM device |

| RAM data retention voltage                                         | V <sub>DDCRDR</sub>  | СС | 0.9  | 1.0     | 1.1  | V    |                          |

| $V_{\text{DDC}}$ brownout voltage in power-down mode <sup>2)</sup> | V <sub>DDCBOPD</sub> | CC | 1.3  | 1.5     | 1.7  | V    |                          |

| V <sub>DDP</sub> prewarning voltage <sup>3)</sup>                  | V <sub>DDPPW</sub>   | СС | 3.4  | 4.0     | 4.6  | V    |                          |

| Power-on reset voltage <sup>2)4)</sup>                             | V <sub>DDCPOR</sub>  | СС | 1.3  | 1.5     | 1.7  | V    |                          |

<sup>1)</sup> Detection is disabled in power-down mode.

<sup>2)</sup> Detection is enabled in both active and power-down mode.

<sup>3)</sup> Detection is enabled for external power supply of 5.0V. Detection must be disabled for external power supply of 3.3V.

<sup>4)</sup> The reset of EVR is extended by 300 µs typically after the VDDC reaches the power-on reset voltage.

#### **Electrical Parameters**

### Table 39Power Supply Current Parameters (Operating Conditions apply;<br/> $V_{\text{DDP}}$ = 3.3V range)

| Parameter                           | Symbol           | Limit              | Values             | Unit | <b>Test Condition</b>                  |  |

|-------------------------------------|------------------|--------------------|--------------------|------|----------------------------------------|--|

|                                     |                  | typ. <sup>1)</sup> | max. <sup>2)</sup> | 1    | Remarks                                |  |

| V <sub>DDP</sub> = 3.3V Range       |                  | -                  |                    | 4    |                                        |  |

| Active Mode                         | I <sub>DDP</sub> | 21.5               | 23.3               | mA   | 3)                                     |  |

| Idle Mode                           | I <sub>DDP</sub> | 16.4               | 18.9               | mA   | XC866-4FR,<br>XC866-2FR <sup>4)</sup>  |  |

|                                     |                  | 11.2               | 13.5               | mA   | XC866-1FR,<br>ROM device <sup>4)</sup> |  |

| Active Mode with slow-down enabled  | I <sub>DDP</sub> | 6.8                | 8                  | mA   | XC866-4FR,<br>XC866-2FR <sup>5)</sup>  |  |

|                                     |                  | 5.4                | 7.3                | mA   | XC866-1FR,<br>ROM device <sup>5)</sup> |  |

| Idle Mode with slow-down<br>enabled | I <sub>DDP</sub> | 6.8                | 7.8                | mA   | XC866-4FR,<br>XC866-2FR <sup>6)</sup>  |  |

|                                     |                  | 4.9                | 6.9                | mA   | XC866-1FR,<br>ROM device <sup>6)</sup> |  |

<sup>1)</sup> The typical  $I_{\text{DDP}}$  values are periodically measured at  $T_{\text{A}}$  = + 25 °C and  $V_{\text{DDP}}$  = 3.3 V.

<sup>2)</sup> The maximum  $I_{\text{DDP}}$  values are measured under worst case conditions ( $T_{\text{A}}$  = + 125 °C and  $V_{\text{DDP}}$  = 3.6 V).

<sup>3)</sup> I<sub>DDP</sub> (active mode) is measured with: CPU clock and input clock to all peripherals running at 26.7 MHz(set by on-chip oscillator of 10 MHz and NDIV in PLL\_CON to 0010<sub>B</sub>), RESET =  $V_{DDP}$ , no load on ports.

<sup>4)</sup> I<sub>DDP</sub> (idle mode) is measured with: <u>CPU clock</u> disabled, watchdog timer disabled, input clock to all peripherals enabled and running at 26.7 MHz, <u>RESET</u> = V<sub>DDP</sub>, no load on ports.

<sup>5)</sup> I<sub>DDP</sub> (active mode with slow-down mode) is measured with: <u>CPU</u> clock and input clock to all peripherals running at 833 KHz by setting CLKREL in CMCON to 0101<sub>B</sub>, <u>RESET</u> = V<sub>DDP</sub>, no load on ports.

<sup>6)</sup> I<sub>DDP</sub> (idle mode with slow-down mode) is measured with: CPU clock disabled, watchdog timer disabled, input <u>clock to all peripherals enable and running at 833 KHz by setting CLKREL in CMCON to 0101<sub>B</sub>,, <u>RESET = V<sub>DDP</sub>, no load on ports.</u></u>

#### **Electrical Parameters**

#### 4.3.4 On-Chip Oscillator Characteristics

| Table 43 | On-chip Oscillator Characteristics (Operating Conditions apply) |

|----------|-----------------------------------------------------------------|

|----------|-----------------------------------------------------------------|

| Parameter                                   | Symbol              | Lir  | nit Va | lues  | Unit | Test Conditions                                                                                                     |

|---------------------------------------------|---------------------|------|--------|-------|------|---------------------------------------------------------------------------------------------------------------------|

|                                             |                     | min. | typ.   | max.  |      |                                                                                                                     |

| Nominal frequency                           | f <sub>NOM</sub> CC | 9.75 | 10     | 10.25 | MHz  | under nominal<br>conditions <sup>1)</sup> after<br>IFX-backend trimming                                             |

| Long term frequency deviation <sup>2)</sup> | $\Delta f_{LT}$ CC  | -5.0 | -      | 5.0   | %    | with respect to $f_{NOM}$ , over<br>lifetime and temperature (–<br>10°C to 125°C), for one<br>device after trimming |

|                                             |                     | -6.0 | -      | 0     | %    | with respect to $f_{NOM}$ , over<br>lifetime and temperature (–<br>40°C to -10°C), for one<br>device after trimming |

| Short term frequency deviation              | ∆f <sub>ST</sub> CC | -1.0 | -      | 1.0   | %    | with respect to <i>f<sub>NOM</sub></i> , within<br>one LIN message (<10 ms<br>100 ms)                               |

<sup>1)</sup> Nominal condition:  $V_{DDC}$  = 2.5 V,  $T_A$  = + 25°C.

<sup>2)</sup> Not all parameters are 100% tested, but are verified by design/characterization and test correlation.

#### Package and Reliability

#### 5 Package and Reliability

#### 5.1 Package Parameters (PG-TSSOP-38)

Table 47 provides the thermal characteristics of the package.

| Parameter                                      | Symbol           |    | Limi | t Values | Unit | Notes |

|------------------------------------------------|------------------|----|------|----------|------|-------|

|                                                |                  |    | Min. | Max.     |      |       |

| Thermal resistance junction case <sup>1)</sup> | R <sub>TJC</sub> | CC | -    | 15.7     | K/W  | -     |

| Thermal resistance junction lead <sup>1)</sup> | R <sub>TJL</sub> | CC | -    | 39.2     | K/W  | -     |

<sup>)</sup> The thermal resistances between the case and the ambient (R<sub>TCA</sub>), the lead and the ambient (R<sub>TLA</sub>) are to be combined with the thermal resistances between the junction and the case (R<sub>TJC</sub>), the junction and the lead (R<sub>TJL</sub>) given above, in order to calculate the total thermal resistance between the junction and the ambient (R<sub>TJA</sub>). The thermal resistances between the case and the ambient (R<sub>TCA</sub>), the lead and the ambient (R<sub>TLA</sub>) depend on the external system (PCB, case) characteristics, and are under user responsibility.

The junction temperature can be calculated using the following equation:  $T_J=T_A + R_{TJA} \times P_D$ , where the  $R_{TJA}$  is the total thermal resistance between the junction and the ambient. This total junction ambient resistance  $R_{TJA}$  can be obtained from the upper four partial thermal resistances, by

a) simply adding only the two thermal resistances (junction lead and lead ambient), or

b) by taking all four resistances into account, depending on the precision needed.

#### Package and Reliability

#### 5.3 Quality Declaration

Table 48 shows the characteristics of the quality parameters in the XC866.

#### Table 48 Quality Parameters

| Parameter                                                             | Symbol           | Limit | t Values | Unit | Notes                                  |

|-----------------------------------------------------------------------|------------------|-------|----------|------|----------------------------------------|

|                                                                       |                  | Min.  | Max.     |      |                                        |

| ESD susceptibility<br>according to Human Body<br>Model (HBM)          | V <sub>HBM</sub> | -     | 2000     | V    | Conforming to<br>EIA/JESD22-<br>A114-B |

| ESD susceptibility<br>according to Charged<br>Device Model (CDM) pins | V <sub>CDM</sub> | -     | 500      | V    | Conforming to<br>JESD22-C101-C         |