Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product StatusLast Time BuyCore ProcessorXC800Core Size8-BitSpeed25MHzConnectivityLINbus, SSI, UART/USARTPeripheralsBrown-out Detect/Reset, POR, PWM, WDTNumber of I/O27Program Memory Size16KB (16K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size768 x 8Voltage - Supply (Vcc/Vdd)3V ~ 3.6VData ConvertersA/D 8x10bOperating Temperature-40°C ~ 150°C (TA)Mounting TypeSurface MountPackage / Case38-TFSOP (0.173", 4.40mm Width)Supplier Device Packagehttps://www.ex.fl.com/product-detail/infineon-technologies/xc866l4fra3vbekxuma1 | Details                    |                                                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|---------------------------------------------------------------------------------|

| Core Size8-BitSpeed25MHzConnectivityLINbus, SSI, UART/USARTPeripheralsBrown-out Detect/Reset, POR, PWM, WDTNumber of I/O27Program Memory Size16KB (16K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size768 x 8Voltage - Supply (Vcc/Vdd)3V ~ 3.6VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-40°C ~ 150°C (TA)Mounting TypeSurface MountPackage / Case38-TFSOP (0.173", 4.40mm Width)Supplier Device PackagePG-TSSOP-38                                                                                            | Product Status             | Last Time Buy                                                                   |

| Speed25MHzConnectivityLINbus, SSI, UART/USARTPeripheralsBrown-out Detect/Reset, POR, PWM, WDTNumber of I/O27Program Memory Size16KB (16K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size768 x 8Voltage - Supply (Vcc/Vdd)3V ~ 3.6VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-40°C ~ 150°C (TA)Mounting TypeSurface MountPackage / Case38-TFSOP (0.173", 4.40mm Width)Supplier Device PackagePG-TSSOP-38                                                                                                          | Core Processor             | XC800                                                                           |

| ConnectivityLINbus, SSI, UART/USARTPeripheralsBrown-out Detect/Reset, POR, PWM, WDTNumber of I/O27Program Memory Size16KB (16K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size768 x 8Voltage - Supply (Vcc/Vdd)3V ~ 3.6VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-40°C ~ 150°C (TA)Mounting TypeSurface MountPackage / Case38-TFSOP (0.173", 4.40mm Width)Supplier Device PackagePG-TSSOP-38                                                                                                                    | Core Size                  | 8-Bit                                                                           |

| PeripheralsBrown-out Detect/Reset, POR, PWM, WDTNumber of I/O27Program Memory Size16KB (16K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size768 x 8Voltage - Supply (Vcc/Vdd)3V ~ 3.6VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-40°C ~ 150°C (TA)Mounting TypeSurface MountPackage / Case38-TFSOP (0.173", 4.40mm Width)Supplier Device PackagePG-TSSOP-38                                                                                                                                                       | Speed                      | 25MHz                                                                           |

| Number of I/O27Program Memory Size16KB (16K × 8)Program Memory TypeFLASHEEPROM Size-RAM Size768 × 8Voltage - Supply (Vcc/Vdd)3V ~ 3.6VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-40°C ~ 150°C (TA)Mounting TypeSurface MountPackage / Case38-TFSOP (0.173", 4.40mm Width)Supplier Device PackagePG-TSSOP-38                                                                                                                                                                                                       | Connectivity               | LINbus, SSI, UART/USART                                                         |

| Program Memory Size16KB (16K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size768 x 8Voltage - Supply (Vcc/Vdd)3V ~ 3.6VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-40°C ~ 150°C (TA)Mounting TypeSurface MountPackage / Case38-TFSOP (0.173", 4.40mm Width)Supplier Device PackagePG-TSSOP-38                                                                                                                                                                                                                      | Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Program Memory TypeFLASHEEPROM Size-RAM Size768 x 8Voltage - Supply (Vcc/Vdd)3V ~ 3.6VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-40°C ~ 150°C (TA)Mounting TypeSurface MountPackage / Case38-TFSOP (0.173", 4.40mm Width)Supplier Device PackagePG-TSSOP-38                                                                                                                                                                                                                                                       | Number of I/O              | 27                                                                              |

| EEPROM Size-RAM Size768 x 8Voltage - Supply (Vcc/Vdd)3V ~ 3.6VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-40°C ~ 150°C (TA)Mounting TypeSurface MountPackage / Case38-TFSOP (0.173", 4.40mm Width)Supplier Device PackagePG-TSSOP-38                                                                                                                                                                                                                                                                               | Program Memory Size        | 16KB (16K x 8)                                                                  |

| RAM Size768 x 8Voltage - Supply (Vcc/Vdd)3V ~ 3.6VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-40°C ~ 150°C (TA)Mounting TypeSurface MountPackage / Case38-TFSOP (0.173", 4.40mm Width)Supplier Device PackagePG-TSSOP-38                                                                                                                                                                                                                                                                                           | Program Memory Type        | FLASH                                                                           |

| Voltage - Supply (Vcc/Vdd)3V ~ 3.6VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-40°C ~ 150°C (TA)Mounting TypeSurface MountPackage / Case38-TFSOP (0.173", 4.40mm Width)Supplier Device PackagePG-TSSOP-38                                                                                                                                                                                                                                                                                                          | EEPROM Size                | -                                                                               |

| Data ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-40°C ~ 150°C (TA)Mounting TypeSurface MountPackage / Case38-TFSOP (0.173", 4.40mm Width)Supplier Device PackagePG-TSSOP-38                                                                                                                                                                                                                                                                                                                                             | RAM Size                   | 768 x 8                                                                         |

| Oscillator TypeInternalOperating Temperature-40°C ~ 150°C (TA)Mounting TypeSurface MountPackage / Case38-TFSOP (0.173", 4.40mm Width)Supplier Device PackagePG-TSSOP-38                                                                                                                                                                                                                                                                                                                                                                     | Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Operating Temperature-40°C ~ 150°C (TA)Mounting TypeSurface MountPackage / Case38-TFSOP (0.173", 4.40mm Width)Supplier Device PackagePG-TSSOP-38                                                                                                                                                                                                                                                                                                                                                                                            | Data Converters            | A/D 8x10b                                                                       |

| Mounting TypeSurface MountPackage / Case38-TFSOP (0.173", 4.40mm Width)Supplier Device PackagePG-TSSOP-38                                                                                                                                                                                                                                                                                                                                                                                                                                   | Oscillator Type            | Internal                                                                        |

| Package / Case     38-TFSOP (0.173", 4.40mm Width)       Supplier Device Package     PG-TSSOP-38                                                                                                                                                                                                                                                                                                                                                                                                                                            | Operating Temperature      | -40°C ~ 150°C (TA)                                                              |

| Supplier Device Package PG-TSSOP-38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Mounting Type              | Surface Mount                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Package / Case             | 38-TFSOP (0.173", 4.40mm Width)                                                 |

| Purchase URL https://www.e-xfl.com/product-detail/infineon-technologies/xc866l4fra3vbekxuma1                                                                                                                                                                                                                                                                                                                                                                                                                                                | Supplier Device Package    | PG-TSSOP-38                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xc866l4fra3vbekxuma1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# XC866 8-Bit Single-Chip Microcontroller

# Microcontrollers

Never stop thinking

# **General Device Information**

# 2.4 Pin Definitions and Functions

# Table 3 Pin Definitions and Functions

| Symbol | Pin<br>Number | Туре | Reset<br>State | Function                            |                                                                                                                            |

|--------|---------------|------|----------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| P0     |               | I/O  |                | port. It can b                      | -bit bidirectional general purpose I/O<br>be used as alternate functions for the<br>6, UART, and the SSC.                  |

| P0.0   | 12            |      | Hi-Z           | TCK_0<br>T12HR_1                    | JTAG Clock Input<br>CCU6 Timer 12 Hardware Run<br>Input                                                                    |

|        |               |      |                | CC61_1<br>CLKOUT<br>RXDO_1          | Input/Output of Capture/Compare<br>channel 1<br>Clock Output<br>UART Transmit Data Output                                  |

| P0.1   | 14            |      | Hi-Z           | TDI_0<br>T13HR_1                    | JTAG Serial Data Input<br>CCU6 Timer 13 Hardware Run<br>Input                                                              |

|        |               |      |                | RXD_1<br>COUT61_1                   | UART Receive Data Input<br>Output of Capture/Compare<br>channel 1                                                          |

| P0.2   | 13            |      | PU             | EXF2_1<br>CTRAP_2<br>TDO_0<br>TXD_1 | Timer 2 External Flag Output<br>CCU6 Trap Input<br>JTAG Serial Data Output<br>UART Transmit Data Output/<br>Clock Output   |

| P0.3   | 2             |      | Hi-Z           | SCK_1<br>COUT63_1                   | SSC Clock Input/Output<br>Output of Capture/Compare<br>channel 3                                                           |

| P0.4   | 3             |      | Hi-Z           | MTSR_1<br>CC62_1                    | SSC Master Transmit Output/<br>Slave Receive Input<br>Input/Output of Capture/Compare<br>channel 2                         |

| P0.5   | 4             |      | Hi-Z           | MRST_1<br>EXINT0_0<br>COUT62_1      | SSC Master Receive Input/<br>Slave Transmit Output<br>External Interrupt Input 0<br>Output of Capture/Compare<br>channel 2 |

# **General Device Information**

| Table 5 |               |      | nis unu        |                    | ontaj                                                                         |

|---------|---------------|------|----------------|--------------------|-------------------------------------------------------------------------------|

| Symbol  | Pin<br>Number | Туре | Reset<br>State | Function           |                                                                               |

| P3      |               | I    |                |                    | directional general purpose I/O port. It as alternate functions for the CCU6. |

| P3.0    | 32            |      | Hi-Z           | CCPOS1_2<br>CC60_0 | CCU6 Hall Input 1<br>Input/Output of Capture/Compare<br>channel 0             |

| P3.1    | 33            |      | Hi-Z           | CCPOS0_2<br>CC61_2 | CCU6 Hall Input 0<br>Input/Output of Capture/Compare<br>channel 1             |

|         |               |      |                | COUT60_0           | Output of Capture/Compare<br>channel 0                                        |

| P3.2    | 34            |      | Hi-Z           | CCPOS2_2<br>CC61_0 | CCU6 Hall Input 2<br>Input/Output of Capture/Compare<br>channel 1             |

| P3.3    | 35            |      | Hi-Z           | COUT61_0           | Output of Capture/Compare<br>channel 1                                        |

| P3.4    | 36            |      | Hi-Z           | CC62_0             | Input/Output of Capture/Compare<br>channel 2                                  |

| P3.5    | 37            |      | Hi-Z           | COUT62_0           | Output of Capture/Compare<br>channel 2                                        |

| P3.6    | 30            |      | PD             | CTRAP_0            | CCU6 Trap Input                                                               |

| P3.7    | 31            |      | Hi-Z           | EXINT4<br>COUT63_0 | External Interrupt Input 4<br>Output of Capture/Compare<br>channel 3          |

# Table 3Pin Definitions and Functions (cont'd)

# XC866

#### **General Device Information**

| Symbol            | Pin<br>Number | Туре | Reset<br>State | Function                                                              |

|-------------------|---------------|------|----------------|-----------------------------------------------------------------------|

| V <sub>DDP</sub>  | 18            | -    | -              | I/O Port Supply (3.3 V/5.0 V)<br>Also used by EVR and analog modules. |

| V <sub>SSP</sub>  | 19            | -    | -              | I/O Port Ground                                                       |

| V <sub>DDC</sub>  | 8             | -    | -              | Core Supply Monitor (2.5 V)                                           |

| V <sub>ssc</sub>  | 7             | -    | _              | Core Supply Ground                                                    |

| V <sub>AREF</sub> | 25            | -    | -              | ADC Reference Voltage                                                 |

| V <sub>AGND</sub> | 24            | -    | _              | ADC Reference Ground                                                  |

| XTAL1             | 6             | I    | Hi-Z           | External Oscillator Input<br>(NC if not needed)                       |

| XTAL2             | 5             | 0    | Hi-Z           | External Oscillator Output<br>(NC if not needed)                      |

| TMS               | 11            | I    | PD             | Test Mode Select                                                      |

| RESET             | 38            | I    | PU             | Reset Input                                                           |

| MBC <sup>1)</sup> | 1             | I    | PU             | Monitor & BootStrap Loader Control                                    |

#### Table 3 Pin Definitions and Functions (cont'd)

<sup>1)</sup> An external pull-up device in the range of 4.7 k $\Omega$  to 100 k $\Omega$  is required to enter user mode. Alternatively MBC can be tied to high if alternate functions (for debugging) of the pin are not utilized.

# Table 7CPU Register Overview (cont'd)

| Addr            | Register Name                    |                                      | Bit       | 7           | 6           | 5           | 4           | 3    | 2    | 1     | 0         |

|-----------------|----------------------------------|--------------------------------------|-----------|-------------|-------------|-------------|-------------|------|------|-------|-----------|

| F0 <sub>H</sub> | В                                | Reset: 00 <sub>H</sub>               | Bit Field | B7          | B6          | B5          | B4          | B3   | B2   | B1    | B0        |

|                 | B Register                       |                                      | Туре      | rw          | rw          | rw          | rw          | rw   | rw   | rw    | rw        |

| F8 <sub>H</sub> | IP1<br>Interrupt Priority Regis  | Reset: 00 <sub>H</sub><br>iter 1     | Bit Field | PCCIP<br>3  | PCCIP<br>2  | PCCIP<br>1  | PCCIP<br>0  | PXM  | PX2  | PSSC  | PADC      |

|                 |                                  |                                      | Туре      | rw          | rw          | rw          | rw          | rw   | rw   | rw    | rw        |

| F9 <sub>H</sub> | IPH1<br>Interrupt Priority Regis | Reset: 00 <sub>H</sub><br>ter 1 High | Bit Field | PCCIP<br>3H | PCCIP<br>2H | PCCIP<br>1H | PCCIP<br>0H | PXMH | PX2H | PSSCH | PADC<br>H |

|                 |                                  |                                      | Туре      | rw          | rw          | rw          | rw          | rw   | rw   | rw    | rw        |

The system control SFRs can be accessed in the standard memory area (RMAP = 0).

# Table 8 System Control Register Overview

| Addr            | Register Name                                                       | Bit       | 7   | 6           | 5            | 4            | 3            | 2             | 1            | 0           |

|-----------------|---------------------------------------------------------------------|-----------|-----|-------------|--------------|--------------|--------------|---------------|--------------|-------------|

| RMAP =          | 0 or 1                                                              |           |     | 1           | 1            | 1            |              |               |              | 1           |

| 8F <sub>H</sub> | SYSCON0 Reset: 00 <sub>H</sub>                                      | Bit Field |     |             |              | 0            |              |               |              | RMAP        |

|                 | System Control Register 0                                           | Туре      |     |             |              | r            |              |               |              | rw          |

| RMAP =          | 0                                                                   |           |     |             |              |              |              |               |              | 1           |

| BF <sub>H</sub> | SCU_PAGE Reset: 00 <sub>H</sub>                                     | Bit Field | C   | P           | ST           | NR           | 0            |               | PAGE         |             |

|                 | Page Register for System Control                                    | Туре      | ١   | N           | \<br>\       | N            | r            |               | rwh          |             |

| RMAP =          | 0, Page 0                                                           |           |     |             | 1            |              |              |               |              |             |

| B3 <sub>H</sub> | MODPISEL Reset: 00 <sub>H</sub><br>Peripheral Input Select Register | Bit Field | 1   | 0           | JTAG<br>TDIS | JTAG<br>TCKS | (            | 0             | EXINT<br>0IS | URRIS       |

|                 |                                                                     | Туре      |     | r           | rw           | rw           |              | r             | rw           | rw          |

| B4 <sub>H</sub> | IRCON0 Reset: 00 <sub>H</sub><br>Interrupt Request Register 0       | Bit Field | 0   | EXINT<br>6  | EXINT<br>5   | EXINT<br>4   | EXINT<br>3   | EXINT<br>2    | EXINT<br>1   | EXINT<br>0  |

|                 |                                                                     | Туре      | r   | rwh         | rwh          | rwh          | rwh          | rwh           | rwh          | rwh         |

| B5 <sub>H</sub> | IRCON1 Reset: 00 <sub>H</sub><br>Interrupt Request Register 1       | Bit Field |     | 0           |              | ADCS<br>RC1  | ADCS<br>RC0  | RIR           | TIR          | EIR         |

|                 |                                                                     | Туре      |     | r           |              | rwh          | rwh          | rwh           | rwh          | rwh         |

| B7 <sub>H</sub> | EXICON0 Reset: 00 <sub>H</sub>                                      | Bit Field | EXI | NT3         | EXI          | NT2          | EXI          | NT1           | EXI          | NT0         |

|                 | External Interrupt Control Register 0                               | Туре      | r   | w           | n            | w            |              | w             | r            | w           |

| BA <sub>H</sub> | EXICON1 Reset: 00 <sub>H</sub>                                      | Bit Field | 0   |             | EXI          | NT6          | EXI          | NT5           | EXI          | NT4         |

|                 | External Interrupt Control Register 1                               | Туре      |     | r           | r            | w            | r            | w             | r            | w           |

| BB <sub>H</sub> | NMICON Reset: 00 <sub>H</sub><br>NMI Control Register               | Bit Field | 0   | NMI<br>ECC  | NMI<br>VDDP  | NMI<br>VDD   | NMI<br>OCDS  | NMI<br>FLASH  | NMI<br>PLL   | NMI<br>WDT  |

|                 |                                                                     | Туре      | r   | rw          | rw           | rw           | rw           | rw            | rw           | rw          |

| BC <sub>H</sub> | NMISR Reset: 00 <sub>H</sub><br>NMI Status Register                 | Bit Field | 0   | FNMI<br>ECC | FNMI<br>VDDP | FNMI<br>VDD  | FNMI<br>OCDS | FNMI<br>FLASH | FNMI<br>PLL  | FNMI<br>WDT |

|                 |                                                                     | Туре      | r   | rwh         | rwh          | rwh          | rwh          | rwh           | rwh          | rwh         |

| BD <sub>H</sub> | BCON Reset: 00 <sub>H</sub>                                         | Bit Field | BG  | SEL         | 0            | BREN         |              | BRPRE         |              | R           |

|                 | Baud Rate Control Register                                          | Туре      | r   | w           | r            | rw           |              | rw            |              | rw          |

| BE <sub>H</sub> | BG Reset: 00 <sub>H</sub>                                           | Bit Field |     |             |              | BR_V         | ALUE         |               |              |             |

|                 | Baud Rate Timer/Reload Register                                     | Туре      |     |             |              | r            | w            |               |              |             |

| E9 <sub>H</sub> | FDCON Reset: 00 <sub>H</sub><br>Fractional Divider Control Register | Bit Field | BGS | SYNEN       | ERRSY<br>N   | EOFSY<br>N   | BRK          | NDOV          | FDM          | FDEN        |

|                 |                                                                     | Туре      | rw  | rw          | rwh          | rwh          | rwh          | rwh           | rw           | rw          |

| EA <sub>H</sub> | FDSTEP Reset: 00 <sub>H</sub>                                       | Bit Field |     |             |              | ST           | ΈP           |               |              |             |

|                 | Fractional Divider Reload Register                                  | Туре      |     |             |              |              | w            |               |              |             |

| EB <sub>H</sub> | FDRES Reset: 00 <sub>H</sub>                                        | Bit Field |     |             |              | RES          | ULT          |               |              |             |

|                 | Fractional Divider Result Register                                  | Туре      |     |             |              | r            | h            |               |              |             |

# Table 8System Control Register Overview (cont'd)

| Addr            | Register Name                       |                                    | Bit       | 7                   | 6                      | 5          | 4           | 3           | 2             | 1           | 0            |  |

|-----------------|-------------------------------------|------------------------------------|-----------|---------------------|------------------------|------------|-------------|-------------|---------------|-------------|--------------|--|

| B3 <sub>H</sub> | ID                                  | Reset: 01 <sub>H</sub>             | Bit Field | PRODID VERID        |                        |            |             |             | 1             |             |              |  |

|                 | Identity Register                   |                                    | Туре      |                     |                        | r          |             | r           |               |             |              |  |

| B4 <sub>H</sub> | PMCON0<br>Power Mode Control Re     | Reset: 00 <sub>H</sub><br>gister 0 | Bit Field | 0                   | WDT WKRS WK<br>RST SEL |            | SD          | PD          | N             | /S          |              |  |

|                 |                                     |                                    | Туре      | r                   | rwh                    | rwh        | rw          | rw          | rwh           | r           | w            |  |

| B5 <sub>H</sub> | PMCON1<br>Power Mode Control Re     | Reset: 00 <sub>H</sub><br>gister 1 | Bit Field |                     | 0 T2                   |            | T2_DIS      | CCU<br>_DIS | SSC<br>_DIS   | ADC<br>_DIS |              |  |

|                 |                                     |                                    | Туре      | r                   |                        |            |             | rw          | rw            | rw          | rw           |  |

| B6 <sub>H</sub> | OSC_CON<br>OSC Control Register     | Reset: 08 <sub>H</sub>             | Bit Field |                     | 0                      |            | OSC<br>PD   | XPD         | OSC<br>SS     | ORD<br>RES  | OSCR         |  |

|                 |                                     |                                    | Туре      |                     | r rw                   |            |             |             | rw            | rwh         | rh           |  |

| В7 <sub>Н</sub> | PLL_CON<br>PLL Control Register     | Reset: 20 <sub>H</sub>             | Bit Field |                     |                        | VCO<br>BYP | OSC<br>DISC | RESLD       | LOCK          |             |              |  |

|                 |                                     |                                    | Туре      |                     | r                      | w          |             | rw          | rw            | rwh         | rh           |  |

| BA <sub>H</sub> | CMCON<br>Clock Control Register     | Reset: 00 <sub>H</sub>             | Bit Field | VCO<br>SEL          |                        | 0          |             |             | CLKREL        |             |              |  |

|                 |                                     |                                    | Туре      | rw                  |                        | r          |             |             | r             | w           |              |  |

| BB <sub>H</sub> | PASSWD<br>Password Register         | Reset: 07 <sub>H</sub>             | Bit Field |                     |                        | PASS       |             |             | PROTE<br>CT_S | MODE        |              |  |

|                 |                                     |                                    | Туре      | w rh                |                        |            |             |             |               | r           | w            |  |

| BC <sub>H</sub> | FEAL                                | Reset: 00 <sub>H</sub>             | Bit Field | ECCERRADDR[7:0]     |                        |            |             |             |               |             |              |  |

|                 | Flash Error Address Reg             | gister Low                         | Туре      | rh                  |                        |            |             |             |               |             |              |  |

| BD <sub>H</sub> | FEAH                                | Reset: 00 <sub>H</sub>             | Bit Field |                     |                        | E          | CCERR       | ADDR[15     | :8]           |             |              |  |

|                 | Flash Error Address Reg             |                                    | Туре      |                     |                        |            |             | 'n          |               |             |              |  |

| BE <sub>H</sub> | COCON<br>Clock Output Control Re    | Reset: 00 <sub>H</sub><br>gister   | Bit Field | I 0 TLEN COUT COREL |                        |            | REL         |             |               |             |              |  |

|                 |                                     |                                    | Туре      | Type r rw rw rw     |                        | w          |             |             |               |             |              |  |

| E9 <sub>H</sub> | MISC_CON<br>Miscellaneous Control R | Reset: 00 <sub>H</sub><br>tegister | Bit Field |                     |                        |            | 0           |             |               |             | DFLAS<br>HEN |  |

|                 |                                     |                                    | Туре      |                     |                        |            | r           |             |               |             | rwh          |  |

|                 | 0, Page 3                           |                                    |           |                     |                        |            |             |             |               |             |              |  |

| B3 <sub>H</sub> | XADDRH                              | Reset: F0 <sub>H</sub>             | Bit Field |                     |                        |            | AD          | DRH         |               |             |              |  |

|                 | On-Chip XRAM Address                | Higher Order                       | Туре      |                     |                        |            | 1           | w           |               |             |              |  |

|                 |                                     |                                    |           |                     |                        |            |             |             |               |             |              |  |

The WDT SFRs can be accessed in the mapped memory area (RMAP = 1).

# Table 9 WDT Register Overview

| Addr            | Register Name                                                    | Bit       | 7      | 6 | 5          | 4         | 3      | 2         | 1         | 0         |

|-----------------|------------------------------------------------------------------|-----------|--------|---|------------|-----------|--------|-----------|-----------|-----------|

| RMAP =          | 1                                                                |           |        |   | 1          |           |        |           |           |           |

| BB <sub>H</sub> | WDTCON Reset: 00 <sub>H</sub><br>Watchdog Timer Control Register | Bit Field |        | 0 | WINB<br>EN | WDT<br>PR | 0      | WDT<br>EN | WDT<br>RS | WDT<br>IN |

|                 |                                                                  | Туре      |        | r | rw         | rh        | r      | rw        | rwh       | rw        |

| BC <sub>H</sub> | WDTREL Reset: 00 <sub>H</sub>                                    | Bit Field | WDTREL |   |            |           |        |           |           |           |

|                 | Watchdog Timer Reload Register                                   |           |        |   |            | r         | w      |           |           |           |

| BD <sub>H</sub> | WDTWINB Reset: 00 <sub>H</sub><br>Watchdog Window-Boundary Count | Bit Field |        |   |            | WDT       | WINB   |           |           |           |

|                 | Register                                                         | Туре      |        |   |            | r         | w      |           |           |           |

| BE <sub>H</sub> | WDTL Reset: 00 <sub>H</sub>                                      | Bit Field |        |   |            | WDT       | [7:0]  |           |           |           |

|                 | Watchdog Timer Register Low                                      | Туре      |        |   |            | r         | h      |           |           |           |

| BF <sub>H</sub> | WDTH Reset: 00 <sub>H</sub>                                      | Bit Field |        |   |            | WDT       | [15:8] |           |           |           |

|                 | Watchdog Timer Register High                                     | Туре      |        |   |            | r         | h      |           |           |           |

#### Table 10Port Register Overview (cont'd)

| Addr            | Register Name                     | Bit       | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|-----------------|-----------------------------------|-----------|----|----|----|----|----|----|----|----|

| B1 <sub>H</sub> | P3_ALTSEL1 Reset: 00 <sub>H</sub> | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P3 Alternate Select 1 Register    | Туре      | rw |

| RMAP =          | 0, Page 3                         |           |    |    |    |    |    |    |    |    |

| 80 <sub>H</sub> | P0_OD Reset: 00 <sub>H</sub>      | Bit Field |    | C  | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P0 Open Drain Control Register    | Туре      |    | r  | rw | rw | rw | rw | rw | rw |

| 90 <sub>H</sub> | P1_OD Reset: 00 <sub>H</sub>      | Bit Field | P7 | P6 | P5 |    | 0  |    | P1 | P0 |

|                 | P1 Open Drain Control Register    | Туре      | rw | rw | rw |    | r  |    | rw | rw |

| B0 <sub>H</sub> | P3_OD Reset: 00 <sub>H</sub>      | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P3 Open Drain Control Register    | Туре      | rw |

The ADC SFRs can be accessed in the standard memory area (RMAP = 0).

# Table 11 ADC Register Overview

| Addr            | Register Name                                   |                              | Bit       | 7                   | 6     | 5   | 4    | 3      | 2     | 1          | 0     |

|-----------------|-------------------------------------------------|------------------------------|-----------|---------------------|-------|-----|------|--------|-------|------------|-------|

| RMAP =          | 0                                               |                              |           |                     |       |     |      | 1      |       | 1          |       |

| D1 <sub>H</sub> |                                                 | set: 00 <sub>H</sub>         | Bit Field | OP STNR             |       | 0   | PAGE |        |       |            |       |

|                 | Page Register for ADC                           |                              | Туре      | \<br>\              | v     | ,   | N    | r      |       | rwh        |       |

| RMAP =          | 0, Page 0                                       |                              |           |                     |       |     |      | 1      |       |            |       |

| CA <sub>H</sub> | ADC_GLOBCTR Reset: 30 <sub>H</sub>              |                              | Bit Field | ANON                | DW    | C   | тс   |        | (     | D          |       |

|                 | Global Control Register                         |                              | Туре      | rw                  | rw    | r   | w    |        |       | r          |       |

| CB <sub>H</sub> | ADC_GLOBSTR Res<br>Global Status Register       | set: 00 <sub>H</sub>         | Bit Field | (                   | )     |     | CHNR |        | 0     | SAM<br>PLE | BUSY  |

|                 |                                                 |                              | Туре      |                     | r     |     | rh   |        | r     | rh         | rh    |

| CCH             |                                                 | set: 00 <sub>H</sub>         | Bit Field | ASEN1               | ASEN0 | 0   | ARBM | CSM1   | PRIO1 | CSM0       | PRIO0 |

|                 | Priority and Arbitration Register               | er                           | Туре      | rw                  | rw    | r   | rw   | rw     | rw    | rw         | rw    |

| CD <sub>H</sub> |                                                 | set: B7 <sub>H</sub>         | Bit Field |                     | BOU   | ND1 |      |        | BOL   | IND0       |       |

|                 | Limit Check Boundary Registe                    | er                           | Туре      |                     | n     | N   |      |        | r     | w          |       |

| CEH             |                                                 | set: 00 <sub>H</sub>         | Bit Field |                     |       |     | S    | TC     |       |            |       |

|                 | Input Class Register 0                          |                              | Туре      | rw                  |       |     |      |        |       |            |       |

| CF <sub>H</sub> | ADC_ETRCR Res<br>External Trigger Control Regis | set: 00 <sub>H</sub><br>ster | Bit Field | SYNEN SYNEN ETRSEL1 |       | 1   | I    | ETRSEL | 0     |            |       |

|                 |                                                 |                              | Туре      | rw                  | rw    |     | rw   |        |       | rw         |       |

| RMAP =          | 0, Page 1                                       |                              |           |                     |       |     |      |        |       |            |       |

| CA <sub>H</sub> |                                                 | set: 00 <sub>H</sub>         | Bit Field | 0                   | LCC   |     | (    | 0      | RES   | RSEL       |       |

|                 | Channel Control Register 0                      |                              | Туре      | r                   |       | rw  |      |        | r rv  |            | w     |

| CB <sub>H</sub> |                                                 | set: 00 <sub>H</sub>         | Bit Field | 0                   |       | LCC |      | (      | 0     | RES        | RSEL  |

|                 | Channel Control Register 1                      |                              | Туре      | r                   |       | rw  |      |        | r rw  |            |       |

| CCH             |                                                 | set: 00 <sub>H</sub>         | Bit Field | 0                   |       | LCC |      | (      | 0     | RES        | RSEL  |

|                 | Channel Control Register 2                      |                              | Туре      | r                   |       | rw  |      |        | r     | r          | w     |

| CD <sub>H</sub> |                                                 | set: 00 <sub>H</sub>         | Bit Field | 0                   |       | LCC |      | (      | 0     | RES        | RSEL  |

|                 | Channel Control Register 3                      |                              | Туре      | r                   |       | rw  |      |        | r     | r          | w     |

| CEH             |                                                 | set: 00 <sub>H</sub>         | Bit Field | 0                   |       | LCC |      | (      | 0     | RES        | RSEL  |

|                 | Channel Control Register 4                      |                              | Туре      | r                   |       | rw  |      |        | r     | r          | w     |

| CF <sub>H</sub> |                                                 | set: 00 <sub>H</sub>         | Bit Field | 0                   |       | LCC |      | (      | 0     | RES        | RSEL  |

|                 | Channel Control Register 5                      |                              | Туре      | r                   |       | rw  |      |        | r     | r          | w     |

| D2 <sub>H</sub> |                                                 | set: 00 <sub>H</sub>         | Bit Field | 0                   |       | LCC |      |        | 0     | RES        | RSEL  |

|                 | Channel Control Register 6                      |                              | Туре      | r                   |       | rw  |      |        | r     |            | w     |

| D3 <sub>H</sub> |                                                 | set: 00 <sub>H</sub>         | Bit Field | 0                   |       | LCC |      |        | 0     | RES        | RSEL  |

| DOH             | Channel Control Register 7                      |                              |           |                     |       |     |      |        | r     |            |       |

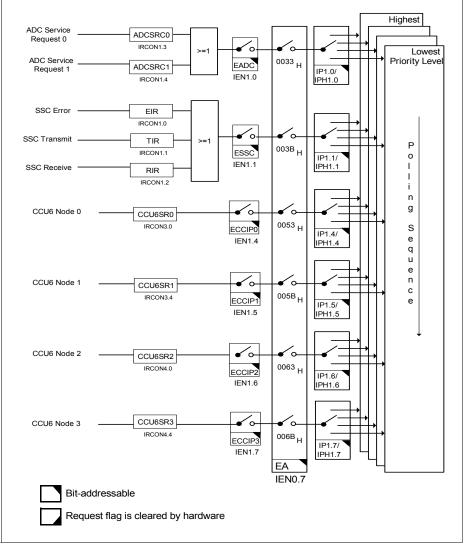

Figure 16 Interrupt Request Sources (Part 3)

# XC866

# **Functional Description**

| XINTR6  | 0033 <sub>H</sub> | ADC                  | EADC   | IEN1 |

|---------|-------------------|----------------------|--------|------|

| XINTR7  | 003B <sub>H</sub> | SSC                  | ESSC   |      |

| XINTR8  | 0043 <sub>H</sub> | External Interrupt 2 | EX2    |      |

| XINTR9  | 004B <sub>H</sub> | External Interrupt 3 | EXM    |      |

|         |                   | External Interrupt 4 |        |      |

|         |                   | External Interrupt 5 |        |      |

|         |                   | External Interrupt 6 |        |      |

| XINTR10 | 0053 <sub>H</sub> | CCU6 INP0            | ECCIP0 |      |

| XINTR11 | 005B <sub>H</sub> | CCU6 INP1            | ECCIP1 |      |

| XINTR12 | 0063 <sub>H</sub> | CCU6 INP2            | ECCIP2 |      |

| XINTR13 | 006B <sub>H</sub> | CCU6 INP3            | ECCIP3 |      |

# Table 17 Interrupt Vector Addresses (cont'd)

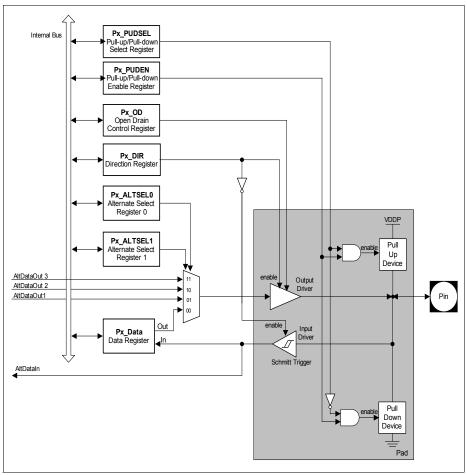

# 3.5 Parallel Ports

The XC866 has 27 port pins organized into four parallel ports, Port 0 (P0) to Port 3 (P3). Each pin has a pair of internal pull-up and pull-down devices that can be individually enabled or disabled. Ports P0, P1 and P3 are bidirectional and can be used as general purpose input/output (GPIO) or to perform alternate input/output functions for the on-chip peripherals. When configured as an output, the open drain mode can be selected. Port P2 is an input-only port, providing general purpose input functions, alternate input functions for the on-chip peripherals, and also analog inputs for the Analog-to-Digital Converter (ADC).

#### **Bidirectional Port Features:**

- Configurable pin direction

- Configurable pull-up/pull-down devices

- · Configurable open drain mode

- Transfer of data through digital inputs and outputs (general purpose I/O)

- Alternate input/output for on-chip peripherals

#### Input Port Features:

- · Configurable input driver

- Configurable pull-up/pull-down devices

- Receive of data through digital input (general purpose input)

- · Alternate input for on-chip peripherals

- · Analog input for ADC module

Figure 18 General Structure of Bidirectional Port

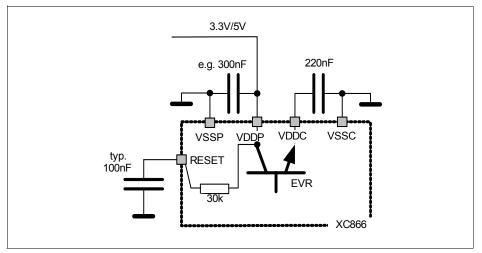

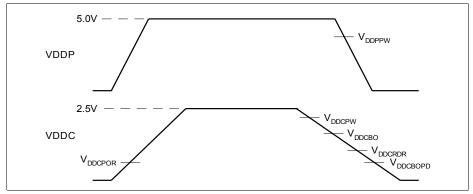

# 3.7 Reset Control

The XC866 has five types of reset: power-on reset, hardware reset, watchdog timer reset, power-down wake-up reset, and brownout reset.

When the XC866 is first powered up, the status of certain pins (see **Table 20**) must be defined to ensure proper start operation of the device. At the end of a reset sequence, the sampled values are latched to select the desired boot option, which cannot be modified until the next power-on reset or hardware reset. This guarantees stable conditions during the normal operation of the device.

In order to power up the system properly, the external reset pin RESET must be asserted until  $V_{DDC}$  reaches  $0.9^*V_{DDC}$ . The delay of external reset can be realized by an external capacitor at RESET pin. This capacitor value must be selected so that  $V_{RESET}$  reaches 0.4 V, but not before  $V_{DDC}$  reaches 0.9\*  $V_{DDC}$ .

A typical application example is shown in Figure 21.  $V_{DDP}$  capacitor value is 300 nF.  $V_{DDC}$  capacitor value is 220 nF. The capacitor connected to RESET pin is 100 nF.

Typically, the time taken for  $V_{DDC}$  to reach  $0.9^*V_{DDC}$  is less than 50 µs once  $V_{DDP}$  reaches 2.3V. Hence, based on the condition that 10% to 90%  $V_{DDP}$  (slew rate) is less than 500 µs, the RESET pin should be held low for 500 µs typically. See Figure 22.

For power saving purposes, the clocks may be disabled or slowed down according to **Table 23**.

# Table 23System frequency (f<sub>sys</sub> = 80 MHz)

| Power Saving Mode | Action                                                                                                                                    |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Idle              | Clock to the CPU is disabled.                                                                                                             |

| Slow-down         | Clocks to the CPU and all the peripherals, including CCU6, are divided by a common programmable factor defined by bit field CMCON.CLKREL. |

| Power-down        | Oscillator and PLL are switched off.                                                                                                      |

8-bit reload value (BR\_VALUE) for the baud rate timer defined by register BG

The following formulas calculate the final baud rate without and with the fractional divider respectively:

baud rate =

$$\frac{f_{PCLK}}{16 \times 2^{BRPRE} \times (BR \text{ VALUE} + 1)}$$

where  $2^{BRPRE} \times (BR_VALUE + 1) > 1$

baud rate =

$$\frac{f_{PCLK}}{16 \times 2^{BRPRE} \times (BR VALUE + 1)} \times \frac{STEP}{256}$$

The maximum baud rate that can be generated is limited to  $f_{PCLK}/32$ . Hence, for a module clock of 26.7 MHz, the maximum achievable baud rate is 0.83 MBaud.

Standard LIN protocal can support a maximum baud rate of 20kHz, the baud rate accuracy is not critical and the fractional divider can be disabled. Only the prescaler is used for auto baud rate calculation. For LIN fast mode, which supports the baud rate of 20kHz to 115.2kHz, the higher baud rates require the use of the fractional divider for greater accuracy.

**Table 26** lists the various commonly used baud rates with their corresponding parameter settings and deviation errors. The fractional divider is disabled and a module clock of 26.7 MHz is used.

| Baud rate Prescaling Factor (2 <sup>BRPRE</sup> ) |                             | Reload Value<br>(BR_VALUE + 1) | Deviation Error |  |  |

|---------------------------------------------------|-----------------------------|--------------------------------|-----------------|--|--|

| 19.2 kBaud                                        | 1 (BRPRE=000 <sub>B</sub> ) | 87 (57 <sub>H</sub> )          | -0.22 %         |  |  |

| 9600 Baud                                         | 1 (BRPRE=000 <sub>B</sub> ) | 174 (AE <sub>H</sub> )         | -0.22 %         |  |  |

| 4800 Baud                                         | 2 (BRPRE=001 <sub>B</sub> ) | 174 (AE <sub>H</sub> )         | -0.22 %         |  |  |

| 2400 Baud                                         | 4 (BRPRE=010 <sub>B</sub> ) | 174 (AE <sub>H</sub> )         | -0.22 %         |  |  |

| Table 26 | Typical Baud rates for UART with Fractional Divider disabled |

|----------|--------------------------------------------------------------|

|----------|--------------------------------------------------------------|

The fractional divider allows baud rates of higher accuracy (lower deviation error) to be generated. Table 27 lists the resulting deviation errors from generating a baud rate of

# 3.11.2 Baud Rate Generation using Timer 1

In UART modes 1 and 3, Timer 1 can be used for generating the variable baud rates. In theory, this timer could be used in any of its modes. But in practice, it should be set into auto-reload mode (Timer 1 mode 2), with its high byte set to the appropriate value for the required baud rate. The baud rate is determined by the Timer 1 overflow rate and the value of SMOD as follows:

[3.1]

Mode 1, 3 baud rate=  $\frac{2^{\text{SMOD}} \times f_{\text{PCLK}}}{32 \times 2 \times (256 - \text{TH1})}$

# 3.12 Normal Divider Mode (8-bit Auto-reload Timer)

Setting bit FDM in register FDCON to 1 configures the fractional divider to normal divider mode, while at the same time disables baud rate generation (see **Figure 29**). Once the fractional divider is enabled (FDEN = 1), it functions as an 8-bit auto-reload timer (with no relation to baud rate generation) and counts up from the reload value with each input clock pulse. Bit field RESULT in register FDRES represents the timer value, while bit field STEP in register FDSTEP defines the reload value. At each timer overflow, an overflow flag (FDCON.NDOV) will be set and an interrupt request generated. This gives an output clock  $f_{MOD}$  that is 1/n of the input clock  $f_{DIV}$ , where n is defined by 256 - STEP.

The output frequency in normal divider mode is derived as follows:

$f_{MOD} = f_{DIV} \times \frac{1}{256 - STEP}$ [3.2]

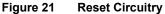

The block diagram of the CCU6 module is shown in Figure 32.

Figure 32 CCU6 Block Diagram

# XC866

# **Electrical Parameters**

# Table 34 Input/Output Characteristics (Operating Conditions apply)

| Parameter                                                                 | Symbol            |    | Limit Values             |                           | Unit | Test Conditions                                                                                       |  |  |

|---------------------------------------------------------------------------|-------------------|----|--------------------------|---------------------------|------|-------------------------------------------------------------------------------------------------------|--|--|

|                                                                           |                   |    | min.                     | max.                      |      | Remarks                                                                                               |  |  |

| Input low voltage at<br>XTAL1                                             | V <sub>ILX</sub>  | SR | V <sub>SS</sub> -<br>0.5 | $0.3 \times V_{ m DDC}$   | V    |                                                                                                       |  |  |

| Input high voltage at XTAL1                                               | V <sub>IHX</sub>  | SR | $0.7 \times V_{ m DDC}$  | V <sub>DDC</sub><br>+ 0.5 | V    |                                                                                                       |  |  |

| Pull-up current                                                           | I <sub>PU</sub>   | SR | -                        | -10                       | μA   | V <sub>IH,min</sub>                                                                                   |  |  |

|                                                                           |                   |    | -150                     | -                         | μA   | V <sub>IL,max</sub>                                                                                   |  |  |

| Pull-down current                                                         | $I_{PD}$          | SR | -                        | 10                        | μA   | V <sub>IL,max</sub>                                                                                   |  |  |

|                                                                           |                   |    | 150                      | -                         | μA   | V <sub>IH,min</sub>                                                                                   |  |  |

| Input leakage current <sup>2)</sup>                                       | I <sub>OZ1</sub>  | CC | -1                       | 1                         | μA   | 0 < $V_{\rm IN}$ < $V_{\rm DDP}$ ,<br>$T_{\rm A} \le 125^{\circ}{\rm C}$ , XC866-4FR<br>and XC866-2FR |  |  |

|                                                                           |                   |    | -2.5                     | 1                         | μA   | $0 < V_{IN} < V_{DDP},$<br>$T_A \le 125^{\circ}C, XC866-1FR$<br>and ROM device                        |  |  |

| Input current at XTAL1                                                    | $I_{ILX}$         | CC | -10                      | 10                        | μA   |                                                                                                       |  |  |

| Overload current on any pin                                               | I <sub>OV</sub>   | SR | -5                       | 5                         | mA   |                                                                                                       |  |  |

| Absolute sum of overload currents                                         | $\Sigma  I_{OV} $ | SR | -                        | 25                        | mA   | 3)                                                                                                    |  |  |

| Voltage on any pin during $V_{\text{DDP}}$ power off                      | V <sub>PO</sub>   | SR | -                        | 0.3                       | V    | 4)                                                                                                    |  |  |

| Maximum current per pin (excluding $V_{\text{DDP}}$ and $V_{\text{SS}}$ ) | I <sub>M</sub>    | SR | -                        | 15                        | mA   |                                                                                                       |  |  |

| Maximum current for all pins (excluding $V_{\rm DDP}$ and $V_{\rm SS}$ )  | $\Sigma  I_{M} $  | SR | -                        | 60                        | mA   |                                                                                                       |  |  |

| Maximum current into $V_{\text{DDP}}$                                     | I <sub>MVDE</sub> | SR | -                        | 80                        | mA   |                                                                                                       |  |  |

| $\frac{\rm Maximum\ current\ out\ of}{V_{\rm SS}}$                        | I <sub>MVSS</sub> | SR | -                        | 80                        | mA   |                                                                                                       |  |  |

#### **Electrical Parameters**

#### Table 34 Input/Output Characteristics (Operating Conditions apply)

| Parameter                                                                                                       | Symbol            |        | Limit Values |      | Unit | Test Conditions                                                                |  |

|-----------------------------------------------------------------------------------------------------------------|-------------------|--------|--------------|------|------|--------------------------------------------------------------------------------|--|

|                                                                                                                 |                   |        | min.         | max. |      | Remarks                                                                        |  |

| Pull-up current                                                                                                 | I <sub>PU</sub>   | SR     | -            | -5   | μA   | V <sub>IH,min</sub>                                                            |  |

|                                                                                                                 |                   |        | -50          | -    | μA   | V <sub>IL,max</sub>                                                            |  |

| Pull-down current                                                                                               | $I_{PD}$          | SR     | -            | 5    | μA   | V <sub>IL,max</sub>                                                            |  |

|                                                                                                                 |                   |        | 50           | -    | μA   | V <sub>IH,min</sub>                                                            |  |

| Input leakage current <sup>2)</sup>                                                                             | I <sub>OZ1</sub>  | CC     | -1           | 1    | μA   | $0 < V_{IN} < V_{DDP},$<br>$T_A \le 125^{\circ}C$ , XC866-4FR<br>and XC866-2FR |  |

|                                                                                                                 |                   |        | -2.5         | 1    | μA   | $0 < V_{IN} < V_{DDP},$<br>$T_A \le 125^{\circ}C, XC866-1FR$<br>and ROM device |  |

| Input current at XTAL1                                                                                          | $I_{ILX}$         | CC     | - 10         | 10   | μA   |                                                                                |  |

| Overload current on any pin                                                                                     | I <sub>OV</sub>   | SR     | -5           | 5    | mA   |                                                                                |  |

| Absolute sum of overload currents                                                                               | $\Sigma   I_{OV}$ | <br>SR | -            | 25   | mA   | 3)                                                                             |  |

| Voltage on any pin during $V_{\text{DDP}}$ power off                                                            | V <sub>PO</sub>   | SR     | -            | 0.3  | V    | 4)                                                                             |  |

| $\begin{tabular}{l} \hline Maximum current per \\ pin (excluding $V_{\rm DDP}$ and $V_{\rm SS}$) \end{tabular}$ | I <sub>M</sub>    | SR     | -            | 15   | mA   |                                                                                |  |

| Maximum current for all pins (excluding $V_{\rm DDP}$ and $V_{\rm SS}$ )                                        | $\Sigma  I_{M} $  | SR     | -            | 60   | mA   |                                                                                |  |

| Maximum current into $V_{\text{DDP}}$                                                                           | I <sub>MVDE</sub> | SR     | -            | 80   | mA   |                                                                                |  |

| Maximum current out of $V_{\rm SS}$                                                                             | I <sub>MVSS</sub> | SR     | -            | 80   | mA   |                                                                                |  |

<sup>1)</sup> Not subjected to production test, verified by design/characterization. Hysteresis is implemented to avoid meta stable states and switching due to internal ground bounce. It cannot be guaranteed that it suppresses switching due to external system noise.

<sup>2)</sup> <u>An additional error current ( $l_{INJ}$ ) will flow if an overload current flows through an adjacent pin. TMS pin and RESET pin have internal pull devices and are not included in the input leakage current characteristic.</u>

<sup>3)</sup> Not subjected to production test, verified by design/characterization.

**Electrical Parameters**

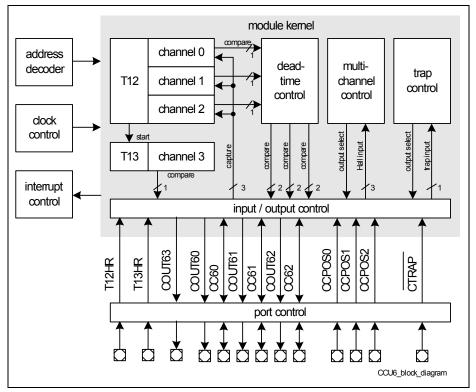

# 4.2.2 Supply Threshold Characteristics

Figure 36 Supply Threshold Parameters

#### Table 35 Supply Threshold Parameters (Operating Conditions apply)

| Parameters                                                         | Symbol               |    | Limit Values |     |      | Unit | Remarks                  |

|--------------------------------------------------------------------|----------------------|----|--------------|-----|------|------|--------------------------|

|                                                                    |                      |    | min. typ.    |     | max. |      |                          |

| V <sub>DDC</sub> prewarning voltage <sup>1)</sup>                  | V <sub>DDCPW</sub>   | СС | 2.2          | 2.3 | 2.4  | V    |                          |

| $V_{\text{DDC}}$ brownout voltage in active mode <sup>1)</sup>     | V <sub>DDCBO</sub>   | СС | 2.0          | 2.1 | 2.2  | V    | XC866-4FR,<br>XC866-2FR  |

|                                                                    |                      |    | 2.0          | 2.1 | 2.3  | V    | XC866-1FR,<br>ROM device |

| RAM data retention voltage                                         | V <sub>DDCRDR</sub>  | СС | 0.9          | 1.0 | 1.1  | V    |                          |

| $V_{\text{DDC}}$ brownout voltage in power-down mode <sup>2)</sup> | V <sub>DDCBOPD</sub> | CC | 1.3          | 1.5 | 1.7  | V    |                          |

| V <sub>DDP</sub> prewarning voltage <sup>3)</sup>                  | V <sub>DDPPW</sub>   | CC | 3.4          | 4.0 | 4.6  | V    |                          |

| Power-on reset voltage <sup>2)4)</sup>                             | V <sub>DDCPOR</sub>  | СС | 1.3          | 1.5 | 1.7  | V    |                          |

<sup>1)</sup> Detection is disabled in power-down mode.

<sup>2)</sup> Detection is enabled in both active and power-down mode.

<sup>3)</sup> Detection is enabled for external power supply of 5.0V. Detection must be disabled for external power supply of 3.3V.

<sup>4)</sup> The reset of EVR is extended by 300 µs typically after the VDDC reaches the power-on reset voltage.

# XC866

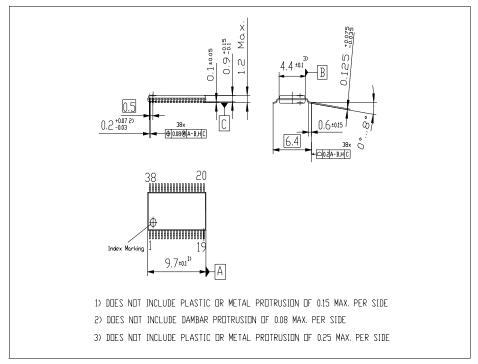

#### Package and Reliability

# 5.2 Package Outline

Figure 46 PG-TSSOP-38-4 Package Outline