Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                |

|--------------------------------|----------------------------------------------------------------|

| Product Status                 | Obsolete                                                       |

| Number of LABs/CLBs            | -                                                              |

| Number of Logic Elements/Cells | 9216                                                           |

| Total RAM Bits                 | 55296                                                          |

| Number of I/O                  | 97                                                             |

| Number of Gates                | 400000                                                         |

| Voltage - Supply               | 1.14V ~ 1.575V                                                 |

| Mounting Type                  | Surface Mount                                                  |

| Operating Temperature          | 0°C ~ 70°C (TA)                                                |

| Package / Case                 | 144-LBGA                                                       |

| Supplier Device Package        | 144-FPBGA (13x13)                                              |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microsemi/agl400v2-fg144t |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1 – IGLOO Device Family Overview

## **General Description**

The IGLOO family of flash FPGAs, based on a 130-nm flash process, offers the lowest power FPGA, a single-chip solution, small footprint packages, reprogrammability, and an abundance of advanced features.

The Flash\*Freeze technology used in IGLOO devices enables entering and exiting an ultra-low power mode that consumes as little as 5 µW while retaining SRAM and register data. Flash\*Freeze technology simplifies power management through I/O and clock management with rapid recovery to operation mode.

The Low Power Active capability (static idle) allows for ultra-low power consumption (from 12  $\mu$ W) while the IGLOO device is completely functional in the system. This allows the IGLOO device to control system power management based on external inputs (e.g., scanning for keyboard stimulus) while consuming minimal power.

Nonvolatile flash technology gives IGLOO devices the advantage of being a secure, low power, singlechip solution that is Instant On. IGLOO is reprogrammable and offers time-to-market benefits at an ASIClevel unit cost.

These features enable designers to create high-density systems using existing ASIC or FPGA design flows and tools.

IGLOO devices offer 1 kbit of on-chip, reprogrammable, nonvolatile FlashROM storage as well as clock conditioning circuitry based on an integrated phase-locked loop (PLL). The AGL015 and AGL030 devices have no PLL or RAM support. IGLOO devices have up to 1 million system gates, supported with up to 144 kbits of true dual-port SRAM and up to 300 user I/Os.

M1 IGLOO devices support the high-performance, 32-bit Cortex-M1 processor developed by ARM for implementation in FPGAs. Cortex-M1 is a soft processor that is fully implemented in the FPGA fabric. It has a three-stage pipeline that offers a good balance between low power consumption and speed when implemented in an M1 IGLOO device. The processor runs the ARMv6-M instruction set, has a configurable nested interrupt controller, and can be implemented with or without the debug block. Cortex-M1 is available for free from Microsemi for use in M1 IGLOO FPGAs.

The ARM-enabled devices have ordering numbers that begin with M1AGL and do not support AES decryption.

## Flash\*Freeze Technology

The IGLOO device offers unique Flash\*Freeze technology, allowing the device to enter and exit ultra-low power Flash\*Freeze mode. IGLOO devices do not need additional components to turn off I/Os or clocks while retaining the design information, SRAM content, and registers. Flash\*Freeze technology is combined with in-system programmability, which enables users to quickly and easily upgrade and update their designs in the final stages of manufacturing or in the field. The ability of IGLOO V2 devices to support a wide range of core voltage (1.2 V to 1.5 V) allows further reduction in power consumption, thus achieving the lowest total system power.

When the IGLOO device enters Flash\*Freeze mode, the device automatically shuts off the clocks and inputs to the FPGA core; when the device exits Flash\*Freeze mode, all activity resumes and data is retained.

The availability of low power modes, combined with reprogrammability, a single-chip and single-voltage solution, and availability of small-footprint, high pin-count packages, make IGLOO devices the best fit for portable electronics.

Revision 27 1-1

#### Flash Advantages

#### Low Power

Flash-based IGLOO devices exhibit power characteristics similar to those of an ASIC, making them an ideal choice for power-sensitive applications. IGLOO devices have only a very limited power-on current surge and no high-current transition period, both of which occur on many FPGAs.

IGLOO devices also have low dynamic power consumption to further maximize power savings; power is even further reduced by the use of a 1.2 V core voltage.

Low dynamic power consumption, combined with low static power consumption and Flash\*Freeze technology, gives the IGLOO device the lowest total system power offered by any FPGA.

#### Security

Nonvolatile, flash-based IGLOO devices do not require a boot PROM, so there is no vulnerable external bitstream that can be easily copied. IGLOO devices incorporate FlashLock, which provides a unique combination of reprogrammability and design security without external overhead, advantages that only an FPGA with nonvolatile flash programming can offer.

IGLOO devices utilize a 128-bit flash-based lock and a separate AES key to provide the highest level of protection in the FPGA industry for intellectual property and configuration data. In addition, all FlashROM data in IGLOO devices can be encrypted prior to loading, using the industry-leading AES-128 (FIPS192) bit block cipher encryption standard. AES was adopted by the National Institute of Standards and Technology (NIST) in 2000 and replaces the 1977 DES standard. IGLOO devices have a built-in AES decryption engine and a flash-based AES key that make them the most comprehensive programmable logic device security solution available today. IGLOO devices with AES-based security provide a high level of protection for remote field updates over public networks such as the Internet, and are designed to ensure that valuable IP remains out of the hands of system overbuilders, system cloners, and IP thieves.

Security, built into the FPGA fabric, is an inherent component of the IGLOO family. The flash cells are located beneath seven metal layers, and many device design and layout techniques have been used to make invasive attacks extremely difficult. The IGLOO family, with FlashLock and AES security, is unique in being highly resistant to both invasive and noninvasive attacks. Your valuable IP is protected with industry-standard security, making remote ISP possible. An IGLOO device provides the best available security for programmable logic designs.

#### Single Chip

Flash-based FPGAs store their configuration information in on-chip flash cells. Once programmed, the configuration data is an inherent part of the FPGA structure, and no external configuration data needs to be loaded at system power-up (unlike SRAM-based FPGAs). Therefore, flash-based IGLOO FPGAs do not require system configuration components such as EEPROMs or microcontrollers to load device configuration data. This reduces bill-of-materials costs and PCB area, and increases security and system reliability.

#### Instant On

Flash-based IGLOO devices support Level 0 of the Instant On classification standard. This feature helps in system component initialization, execution of critical tasks before the processor wakes up, setup and configuration of memory blocks, clock generation, and bus activity management. The Instant On feature of flash-based IGLOO devices greatly simplifies total system design and reduces total system cost, often eliminating the need for CPLDs and clock generation PLLs. In addition, glitches and brownouts in system power will not corrupt the IGLOO device's flash configuration, and unlike SRAM-based FPGAs, the device will not have to be reloaded when system power is restored. This enables the reduction or complete removal of the configuration PROM, expensive voltage monitor, brownout detection, and clock generator devices from the PCB design. Flash-based IGLOO devices simplify total system design and reduce cost and design risk while increasing system reliability and improving system initialization time.

IGLOO flash FPGAs allow the user to quickly enter and exit Flash\*Freeze mode. This is done almost instantly (within 1 µs) and the device retains configuration and data in registers and RAM. Unlike SRAM-based FPGAs the device does not need to reload configuration and design state from external memory components; instead it retains all necessary information to resume operation immediately.

#### Reduced Cost of Ownership

Advantages to the designer extend beyond low unit cost, performance, and ease of use. Unlike SRAM-based FPGAs, Flash-based IGLOO devices allow all functionality to be Instant On; no external boot PROM is required. On-board security mechanisms prevent access to all the programming information and enable secure remote updates of the FPGA logic. Designers can perform secure remote in-system reprogramming to support future design iterations and

Revision 27 1-2

#### User Nonvolatile FlashROM

IGLOO devices have 1 kbit of on-chip, user-accessible, nonvolatile FlashROM. The FlashROM can be used in diverse system applications:

- · Internet protocol addressing (wireless or fixed)

- · System calibration settings

- · Device serialization and/or inventory control

- Subscription-based business models (for example, set-top boxes)

- · Secure key storage for secure communications algorithms

- Asset management/tracking

- Date stamping

- · Version management

The FlashROM is written using the standard IGLOO IEEE 1532 JTAG programming interface. The core can be individually programmed (erased and written), and on-chip AES decryption can be used selectively to securely load data over public networks (except in the AGL015 and AGL030 devices), as in security keys stored in the FlashROM for a user design.

The FlashROM can be programmed via the JTAG programming interface, and its contents can be read back either through the JTAG programming interface or via direct FPGA core addressing. Note that the FlashROM can only be programmed from the JTAG interface and cannot be programmed from the internal logic array.

The FlashROM is programmed as 8 banks of 128 bits; however, reading is performed on a byte-by-byte basis using a synchronous interface. A 7-bit address from the FPGA core defines which of the 8 banks and which of the 16 bytes within that bank are being read. The three most significant bits (MSBs) of the FlashROM address determine the bank, and the four least significant bits (LSBs) of the FlashROM address define the byte.

The Microsemi development software solutions, Libero<sup>®</sup> System-on-Chip (SoC) and Designer, have extensive support for the FlashROM. One such feature is auto-generation of sequential programming files for applications requiring a unique serial number in each part. Another feature allows the inclusion of static data for system version control. Data for the FlashROM can be generated quickly and easily using Libero SoC and Designer software tools. Comprehensive programming file support is also included to allow for easy programming of large numbers of parts with differing FlashROM contents.

#### SRAM and FIFO

IGLOO devices (except the AGL015 and AGL030 devices) have embedded SRAM blocks along their north and south sides. Each variable-aspect-ratio SRAM block is 4,608 bits in size. Available memory configurations are 256x18, 512x9, 1kx4, 2kx2, and 4kx1 bits. The individual blocks have independent read and write ports that can be configured with different bit widths on each port. For example, data can be sent through a 4-bit port and read as a single bitstream. The embedded SRAM blocks can be initialized via the device JTAG port (ROM emulation mode) using the UJTAG macro (except in the AGL015 and AGL030 devices).

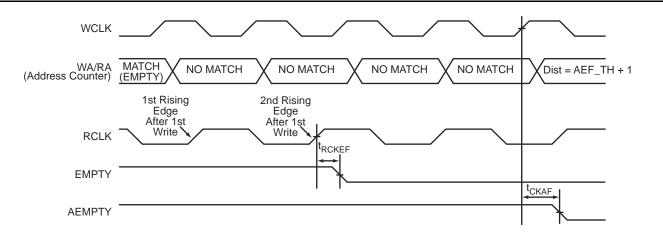

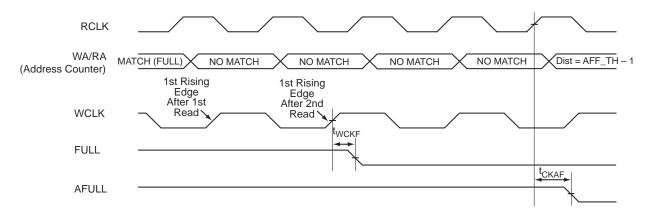

In addition, every SRAM block has an embedded FIFO control unit. The control unit allows the SRAM block to be configured as a synchronous FIFO without using additional core VersaTiles. The FIFO width and depth are programmable. The FIFO also features programmable Almost Empty (AEMPTY) and Almost Full (AFULL) flags in addition to the normal Empty and Full flags. The embedded FIFO control unit contains the counters necessary for generation of the read and write address pointers. The embedded SRAM/FIFO blocks can be cascaded to create larger configurations.

#### PLL and CCC

IGLOO devices provide designers with very flexible clock conditioning circuit (CCC) capabilities. Each member of the IGLOO family contains six CCCs. One CCC (center west side) has a PLL. The AGL015 and AGL030 do not have a PLL

The six CCC blocks are located at the four corners and the centers of the east and west sides. One CCC (center west side) has a PLL.

All six CCC blocks are usable; the four corner CCCs and the east CCC allow simple clock delay operations as well as clock spine access.

The inputs of the six CCC blocks are accessible from the FPGA core or from one of several inputs located near the CCC that have dedicated connections to the CCC block.

The CCC block has these key features:

Revision 27 1-6

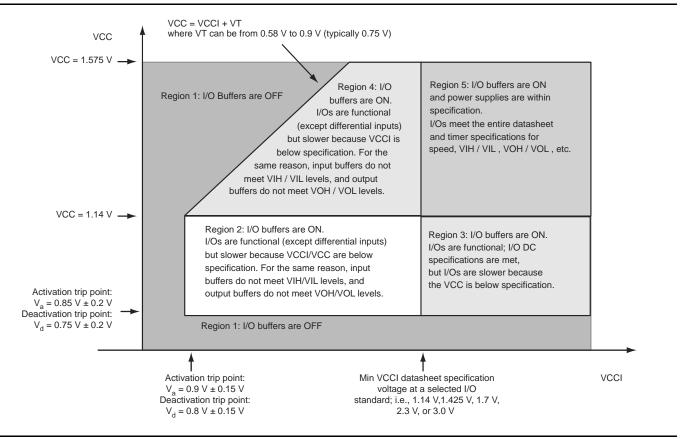

Figure 2-2 • V2 Devices – I/O State as a Function of VCCI and VCC Voltage Levels

### **Thermal Characteristics**

#### Introduction

The temperature variable in the Designer software refers to the junction temperature, not the ambient temperature. This is an important distinction because dynamic and static power consumption cause the chip junction to be higher than the ambient temperature.

EQ 1 can be used to calculate junction temperature.

$T_J$  = Junction Temperature =  $\Delta T + T_A$

EQ 1

#### where:

T<sub>A</sub> = Ambient Temperature

$\Delta T$  = Temperature gradient between junction (silicon) and ambient  $\Delta T$  =  $\theta_{ja}$  \* P

$\theta_{ia}$  = Junction-to-ambient of the package.  $\theta_{ia}$  numbers are located in Table 2-5 on page 2-6.

P = Power dissipation

Revision 27 2-5

Table 2-42 • I/O Short Currents IOSH/IOSL Applicable to Advanced I/O Banks

|                            | Drive Strength              | IOSL (mA)*                   | IOSH (mA)*                   |

|----------------------------|-----------------------------|------------------------------|------------------------------|

| 3.3 V LVTTL / 3.3 V LVCMOS | 2 mA                        | 25                           | 27                           |

|                            | 4 mA                        | 25                           | 27                           |

|                            | 6 mA                        | 51                           | 54                           |

|                            | 8 mA                        | 51                           | 54                           |

|                            | 12 mA                       | 103                          | 109                          |

|                            | 16 mA                       | 132                          | 127                          |

|                            | 24 mA                       | 268                          | 181                          |

| 3.3 V LVCMOS Wide Range    | 100 μΑ                      | Same as regular 3.3 V LVCMOS | Same as regular 3.3 V LVCMOS |

| 2.5 V LVCMOS               | 2 mA                        | 16                           | 18                           |

|                            | 4 mA                        | 16                           | 18                           |

|                            | 6 mA                        | 32                           | 37                           |

|                            | 8 mA                        | 32                           | 37                           |

|                            | 12 mA                       | 65                           | 74                           |

|                            | 16 mA                       | 83                           | 87                           |

|                            | 24 mA                       | 169                          | 124                          |

| 1.8 V LVCMOS               | 2 mA                        | 9                            | 11                           |

|                            | 4 mA                        | 17                           | 22                           |

|                            | 6 mA                        | 35                           | 44                           |

|                            | 8 mA                        | 45                           | 51                           |

|                            | 12 mA                       | 91                           | 74                           |

|                            | 16 mA                       | 91                           | 74                           |

| 1.5 V LVCMOS               | 2 mA                        | 13                           | 16                           |

|                            | 4 mA                        | 25                           | 33                           |

|                            | 6 mA                        | 32                           | 39                           |

|                            | 8 mA                        | 66                           | 55                           |

|                            | 12 mA                       | 66                           | 55                           |

| 1.2 V LVCMOS               | 2 mA                        | 20                           | 26                           |

| 1.2 V LVCMOS Wide Range    | 100 μΑ                      | 20                           | 26                           |

| 3.3 V PCI/PCI-X            | Per PCI/PCI-X specification | 103                          | 109                          |

Note:  ${}^*T_J = 100 {}^{\circ}C$

Revision 27 2-37

Table 2-97 • Minimum and Maximum DC Input and Output Levels

Applicable to Standard I/O Banks

| 1.8 V<br>LVCMOS   | VIL VIH   |             | VIH         |           | VOL       | VOH         | IOL | ЮН | IOSH                    | IOSL                    | IIL <sup>1</sup> | IIH <sup>2</sup>        |

|-------------------|-----------|-------------|-------------|-----------|-----------|-------------|-----|----|-------------------------|-------------------------|------------------|-------------------------|

| Drive<br>Strength | Min.<br>V | Max.<br>V   | Min.<br>V   | Max.<br>V | Max.<br>V | Min.<br>V   | mA  | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μA <sup>4</sup>  | μ <b>Α</b> <sup>4</sup> |

| 2 mA              | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 3.6       | 0.45      | VCCI - 0.45 | 2   | 2  | 9                       | 11                      | 10               | 10                      |

| 4 mA              | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 3.6       | 0.45      | VCCI - 0.45 | 4   | 4  | 17                      | 22                      | 10               | 10                      |

#### Notes:

- 1. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

- 2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges

- 3. Currents are measured at 100°C junction temperature and maximum voltage.

- 4. Currents are measured at 85°C junction temperature.

- 5. Software default selection highlighted in gray.

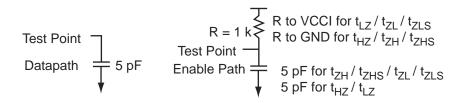

Figure 2-9 • AC Loading

Table 2-98 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|------------------------|

| 0             | 1.8            | 0.9                  | 5                      |

Note: \*Measuring point = Vtrip. See Table 2-29 on page 2-28 for a complete table of trip points.

#### **Timing Characteristics**

#### 1.5 V DC Core Voltage

Table 2-99 • 1.8 V LVCMOS Low Slew – Applies to 1.5 V DC Core Voltage

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.7 V

Applicable to Advanced I/O Banks

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | $t_{ZL}$ | $t_{ZH}$ | $t_{LZ}$ | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>ZHS</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|-------------------|----------|----------|----------|-----------------|------------------|------------------|-------|

| 2 mA           | Std.        | 0.97              | 6.38            | 0.18             | 1.01            | 0.66              | 6.51     | 5.93     | 2.33     | 1.56            | 10.10            | 9.53             | ns    |

| 4 mA           | Std.        | 0.97              | 5.35            | 0.18             | 1.01            | 0.66              | 5.46     | 5.04     | 2.67     | 2.38            | 9.05             | 8.64             | ns    |

| 6 mA           | Std.        | 0.97              | 4.62            | 0.18             | 1.01            | 0.66              | 4.71     | 4.44     | 2.90     | 2.79            | 8.31             | 8.04             | ns    |

| 8 mA           | Std.        | 0.97              | 4.37            | 0.18             | 1.01            | 0.66              | 4.46     | 4.31     | 2.95     | 2.89            | 8.05             | 7.90             | ns    |

| 12 mA          | Std.        | 0.97              | 4.32            | 0.18             | 1.01            | 0.66              | 4.37     | 4.32     | 3.03     | 3.30            | 7.97             | 7.92             | ns    |

| 16 mA          | Std.        | 0.97              | 4.32            | 0.18             | 1.01            | 0.66              | 4.37     | 4.32     | 3.03     | 3.30            | 7.97             | 7.92             | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

2-62 Revision 27

#### 1.5 V LVCMOS (JESD8-11)

Low-Voltage CMOS for 1.5 V is an extension of the LVCMOS standard (JESD8-5) used for general-purpose 1.5 V applications. It uses a 1.5 V input buffer and a push-pull output buffer.

Table 2-111 • Minimum and Maximum DC Input and Output Levels

Applicable to Advanced I/O Banks

| 1.5 V<br>LVCMOS   |           | VIL         | VIH         |           | VOL         | VOH         | IOL | ЮН | IOSH                    | IOSL                    | IIL <sup>1</sup>        | IIH <sup>2</sup>        |

|-------------------|-----------|-------------|-------------|-----------|-------------|-------------|-----|----|-------------------------|-------------------------|-------------------------|-------------------------|

| Drive<br>Strength | Min.<br>V | Max.<br>V   | Min.<br>V   | Max.<br>V | Max.<br>V   | Min.<br>V   | mA  | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μ <b>Α</b> <sup>4</sup> | μ <b>Α</b> <sup>4</sup> |

| 2 mA              | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 1.575     | 0.25 * VCCI | 0.75 * VCCI | 2   | 2  | 13                      | 16                      | 10                      | 10                      |

| 4 mA              | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 1.575     | 0.25 * VCCI | 0.75 * VCCI | 4   | 4  | 25                      | 33                      | 10                      | 10                      |

| 6 mA              | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 1.575     | 0.25 * VCCI | 0.75 * VCCI | 6   | 6  | 32                      | 39                      | 10                      | 10                      |

| 8 mA              | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 1.575     | 0.25 * VCCI | 0.75 * VCCI | 8   | 8  | 66                      | 55                      | 10                      | 10                      |

| 12 mA             | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 1.575     | 0.25 * VCCI | 0.75 * VCCI | 12  | 12 | 66                      | 55                      | 10                      | 10                      |

#### Notes:

- 1. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

- 2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges

- 3. Currents are measured at 100°C junction temperature and maximum voltage.

- 4. Currents are measured at 85°C junction temperature.

- 5. Software default selection highlighted in gray.

Table 2-112 • Minimum and Maximum DC Input and Output Levels

Applicable to Standard Plus I/O Banks

| 1.5 V<br>LVCMOS   |           | VIL         | VIH         |           | VOL         | VOH         | IOL | ЮН | IOSH                    | IOSL                    | IIL <sup>1</sup>        | IIH <sup>2</sup>        |

|-------------------|-----------|-------------|-------------|-----------|-------------|-------------|-----|----|-------------------------|-------------------------|-------------------------|-------------------------|

| Drive<br>Strength | Min.<br>V | Max.<br>V   | Min.<br>V   | Max.<br>V | Max.<br>V   | Min.<br>V   | mA  | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μ <b>Α</b> <sup>4</sup> | μ <b>Α</b> <sup>4</sup> |

| 2 mA              | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 1.575     | 0.25 * VCCI | 0.75 * VCCI | 2   | 2  | 13                      | 16                      | 10                      | 10                      |

| 4 mA              | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 1.575     | 0.25 * VCCI | 0.75 * VCCI | 4   | 4  | 25                      | 33                      | 10                      | 10                      |

#### Notes:

- 1. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

- 2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges

- 3. Currents are measured at 100°C junction temperature and maximum voltage.

- 4. Currents are measured at 85°C junction temperature.

- 5. Software default selection highlighted in gray.

2-66 Revision 27

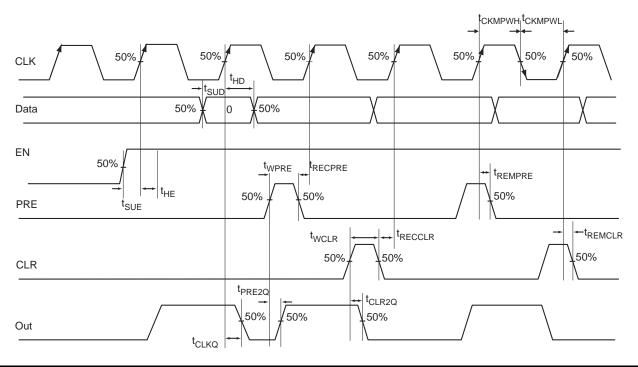

Figure 2-28 • Timing Model and Waveforms

# Timing Characteristics 1.5 V DC Core Voltage

Table 2-171 • Register Delays Commercial-Case Conditions:  $T_J = 70^{\circ}\text{C}$ , Worst-Case VCC = 1.425 V

| Parameter           | Description                                                   | Std. | Units |

|---------------------|---------------------------------------------------------------|------|-------|

| t <sub>CLKQ</sub>   | Clock-to-Q of the Core Register                               | 0.89 | ns    |

| t <sub>SUD</sub>    | Data Setup Time for the Core Register                         | 0.81 | ns    |

| t <sub>HD</sub>     | Data Hold Time for the Core Register                          | 0.00 | ns    |

| t <sub>SUE</sub>    | Enable Setup Time for the Core Register                       | 0.73 | ns    |

| t <sub>HE</sub>     | Enable Hold Time for the Core Register                        | 0.00 | ns    |

| t <sub>CLR2Q</sub>  | Asynchronous Clear-to-Q of the Core Register                  | 0.60 | ns    |

| t <sub>PRE2Q</sub>  | Asynchronous Preset-to-Q of the Core Register                 | 0.62 | ns    |

| t <sub>REMCLR</sub> | Asynchronous Clear Removal Time for the Core Register         | 0.00 | ns    |

| t <sub>RECCLR</sub> | Asynchronous Clear Recovery Time for the Core Register        | 0.24 | ns    |

| t <sub>REMPRE</sub> | Asynchronous Preset Removal Time for the Core Register        | 0.00 | ns    |

| t <sub>RECPRE</sub> | Asynchronous Preset Recovery Time for the Core Register       | 0.23 | ns    |

| t <sub>WCLR</sub>   | Asynchronous Clear Minimum Pulse Width for the Core Register  | 0.30 | ns    |

| t <sub>WPRE</sub>   | Asynchronous Preset Minimum Pulse Width for the Core Register | 0.30 | ns    |

| t <sub>CKMPWH</sub> | Clock Minimum Pulse Width High for the Core Register          | 0.56 | ns    |

| t <sub>CKMPWL</sub> | Clock Minimum Pulse Width Low for the Core Register           | 0.56 | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

Revision 27 2-99

## **Embedded SRAM and FIFO Characteristics**

#### **SRAM**

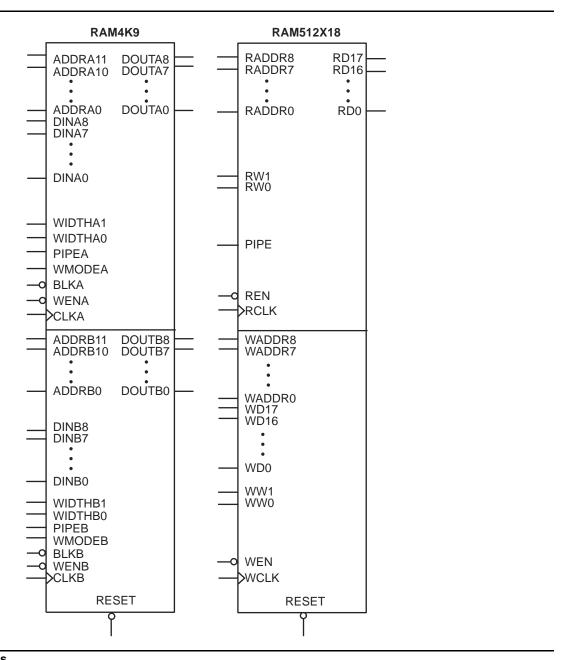

Figure 2-31 • RAM Models

Revision 27 2-113

## **Timing Waveforms**

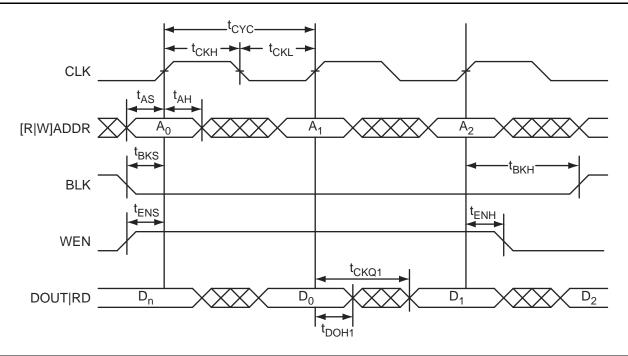

Figure 2-32 • RAM Read for Pass-Through Output. Applicable to Both RAM4K9 and RAM512x18.

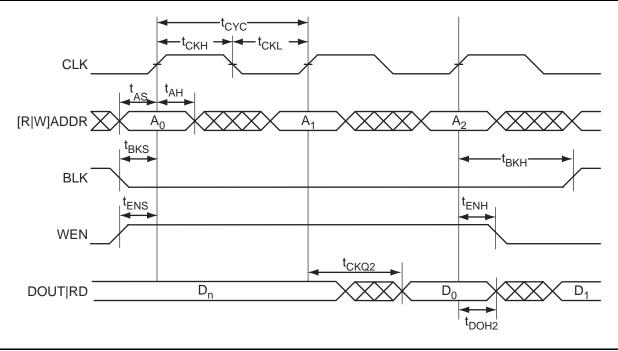

Figure 2-33 • RAM Read for Pipelined Output. Applicable to Both RAM4K9 and RAM512x18.

2-114 Revision 27

Figure 2-42 • FIFO FULL Flag and AFULL Flag Assertion

Figure 2-43 • FIFO EMPTY Flag and AEMPTY Flag Deassertion

Figure 2-44 • FIFO FULL Flag and AFULL Flag Deassertion

2-124 Revision 27

Package Pin Assignments

|            | ON 40           |

|------------|-----------------|

|            | QN48            |

| Pin Number | AGL030 Function |

| 1          | IO82RSB1        |

| 2          | GEC0/IO73RSB1   |

| 3          | GEA0/IO72RSB1   |

| 4          | GEB0/IO71RSB1   |

| 5          | GND             |

| 6          | VCCIB1          |

| 7          | IO68RSB1        |

| 8          | IO67RSB1        |

| 9          | IO66RSB1        |

| 10         | IO65RSB1        |

| 11         | IO64RSB1        |

| 12         | IO62RSB1        |

| 13         | IO61RSB1        |

| 14         | FF/IO60RSB1     |

| 15         | IO57RSB1        |

| 16         | IO55RSB1        |

| 17         | IO53RSB1        |

| 18         | VCC             |

| 19         | VCCIB1          |

| 20         | IO46RSB1        |

| 21         | IO42RSB1        |

| 22         | TCK             |

| 23         | TDI             |

| 24         | TMS             |

| 25         | VPUMP           |

| 26         | TDO             |

| 27         | TRST            |

| 28         | VJTAG           |

| 29         | IO38RSB0        |

| 30         | GDB0/IO34RSB0   |

| 31         | GDA0/IO33RSB0   |

| 32         | GDC0/IO32RSB0   |

| 33         | VCCIB0          |

| 34         | GND             |

| 35         | VCC             |

| 36         | IO25RSB0        |

|            |                 |

| (          | QN48            |

|------------|-----------------|

| Pin Number | AGL030 Function |

| 37         | IO24RSB0        |

| 38         | IO22RSB0        |

| 39         | IO20RSB0        |

| 40         | IO18RSB0        |

| 41         | IO16RSB0        |

| 42         | IO14RSB0        |

| 43         | IO10RSB0        |

| 44         | IO08RSB0        |

| 45         | IO06RSB0        |

| 46         | IO04RSB0        |

| 47         | IO02RSB0        |

| 48         | IO00RSB0        |

4-24 Revision 27

IGLOO Low Power Flash FPGAs

| (          | QN132           |

|------------|-----------------|

| Pin Number | AGL060 Function |

| A1         | GAB2/IO00RSB1   |

| A2         | IO93RSB1        |

| A3         | VCCIB1          |

| A4         | GFC1/IO89RSB1   |

| A5         | GFB0/IO86RSB1   |

| A6         | VCCPLF          |

| A7         | GFA1/IO84RSB1   |

| A8         | GFC2/IO81RSB1   |

| A9         | IO78RSB1        |

| A10        | VCC             |

| A11        | GEB1/IO75RSB1   |

| A12        | GEA0/IO72RSB1   |

| A13        | GEC2/IO69RSB1   |

| A14        | IO65RSB1        |

| A15        | VCC             |

| A16        | IO64RSB1        |

| A17        | IO63RSB1        |

| A18        | IO62RSB1        |

| A19        | IO61RSB1        |

| A20        | IO58RSB1        |

| A21        | GDB2/IO55RSB1   |

| A22        | NC              |

| A23        | GDA2/IO54RSB1   |

| A24        | TDI             |

| A25        | TRST            |

| A26        | GDC1/IO48RSB0   |

| A27        | VCC             |

| A28        | IO47RSB0        |

| A29        | GCC2/IO46RSB0   |

| A30        | GCA2/IO44RSB0   |

| A31        | GCA0/IO43RSB0   |

| A32        | GCB1/IO40RSB0   |

| A33        | IO36RSB0        |

| A34        | VCC             |

| A35        | IO31RSB0        |

| A36        | GBA2/IO28RSB0   |

| QN132      |                      |  |  |  |  |

|------------|----------------------|--|--|--|--|

| Pin Number | AGL060 Function      |  |  |  |  |

| A37        | GBB1/IO25RSB0        |  |  |  |  |

| A38        | GBC0/IO22RSB0        |  |  |  |  |

| A39        | VCCIB0               |  |  |  |  |

|            |                      |  |  |  |  |

| A40        | IO21RSB0             |  |  |  |  |

| A41        | IO18RSB0             |  |  |  |  |

| A42        | IO15RSB0             |  |  |  |  |

| A43        | IO14RSB0             |  |  |  |  |

| A44        | IO11RSB0             |  |  |  |  |

| A45        | GAB1/IO08RSB0        |  |  |  |  |

| A46        | NC                   |  |  |  |  |

| A47        | GAB0/IO07RSB0        |  |  |  |  |

| A48        | IO04RSB0             |  |  |  |  |

| B1         | IO01RSB1             |  |  |  |  |

| B2         | GAC2/IO94RSB1        |  |  |  |  |

| В3         | GND                  |  |  |  |  |

| B4         | GFC0/IO88RSB1        |  |  |  |  |

| B5         | VCOMPLF              |  |  |  |  |

| В6         | GND                  |  |  |  |  |

| B7         | GFB2/IO82RSB1        |  |  |  |  |

| B8         | IO79RSB1             |  |  |  |  |

| B9         | GND                  |  |  |  |  |

| B10        | GEB0/IO74RSB1        |  |  |  |  |

| B11        | VMV1                 |  |  |  |  |

| B12        | FF/GEB2/IO70RSB<br>1 |  |  |  |  |

| B13        | IO67RSB1             |  |  |  |  |

| B14        | GND                  |  |  |  |  |

| B15        | NC                   |  |  |  |  |

| B16        | NC                   |  |  |  |  |

| B17        | GND                  |  |  |  |  |

| B18        | IO59RSB1             |  |  |  |  |

| B19        | GDC2/IO56RSB1        |  |  |  |  |

| B20        | GND                  |  |  |  |  |

| B21        | GNDQ                 |  |  |  |  |

| B22        | TMS                  |  |  |  |  |

| B23        | TDO                  |  |  |  |  |

|            |                      |  |  |  |  |

| QN132      |                 |

|------------|-----------------|

| Pin Number | AGL060 Function |

| B24        | GDC0/IO49RSB0   |

| B25        | GND             |

| B26        | NC              |

| B27        | GCB2/IO45RSB0   |

| B28        | GND             |

| B29        | GCB0/IO41RSB0   |

| B30        | GCC1/IO38RSB0   |

| B31        | GND             |

| B32        | GBB2/IO30RSB0   |

| B33        | VMV0            |

| B34        | GBA0/IO26RSB0   |

| B35        | GBC1/IO23RSB0   |

| B36        | GND             |

| B37        | IO20RSB0        |

| B38        | IO17RSB0        |

| B39        | GND             |

| B40        | IO12RSB0        |

| B41        | GAC0/IO09RSB0   |

| B42        | GND             |

| B43        | GAA1/IO06RSB0   |

| B44        | GNDQ            |

| C1         | GAA2/IO02RSB1   |

| C2         | IO95RSB1        |

| C3         | VCC             |

| C4         | GFB1/IO87RSB1   |

| C5         | GFA0/IO85RSB1   |

| C6         | GFA2/IO83RSB1   |

| C7         | IO80RSB1        |

| C8         | VCCIB1          |

| C9         | GEA1/IO73RSB1   |

| C10        | GNDQ            |

| C11        | GEA2/IO71RSB1   |

| C12        | IO68RSB1        |

| C13        | VCCIB1          |

| C14        | NC              |

| C15        | NC              |

Revision 27 4-31

## Package Pin Assignments

| QN132      |                 |

|------------|-----------------|

| Pin Number | AGL250 Function |

| C17        | IO74RSB2        |

| C18        | VCCIB2          |

| C19        | TCK             |

| C20        | VMV2            |

| C21        | VPUMP           |

| C22        | VJTAG           |

| C23        | VCCIB1          |

| C24        | IO53NSB1        |

| C25        | IO51NPB1        |

| C26        | GCA1/IO50PPB1   |

| C27        | GCC0/IO48NDB1   |

| C28        | VCCIB1          |

| C29        | IO42NDB1        |

| C30        | GNDQ            |

| C31        | GBA1/IO40RSB0   |

| C32        | GBB0/IO37RSB0   |

| C33        | VCC             |

| C34        | IO24RSB0        |

| C35        | IO19RSB0        |

| C36        | IO16RSB0        |

| C37        | IO10RSB0        |

| C38        | VCCIB0          |

| C39        | GAB1/IO03RSB0   |

| C40        | VMV0            |

| D1         | GND             |

| D2         | GND             |

| D3         | GND             |

| D4         | GND             |

4-36 Revision 27

Package Pin Assignments

|            | VQ100                 |

|------------|-----------------------|

| Pin Number | AGL125 Function       |

| 1          | GND                   |

| 2          | GAA2/IO67RSB1         |

| 3          | IO68RSB1              |

| 4          | GAB2/IO69RSB1         |

| 5          | IO132RSB1             |

| 6          | GAC2/IO131RSB1        |

| 7          | IO130RSB1             |

| 8          | IO129RSB1             |

| 9          | GND                   |

| 10         | GFB1/IO124RSB1        |

| 11         | GFB0/IO123RSB1        |

| 12         | VCOMPLF               |

| 13         | GFA0/IO122RSB1        |

| 14         | VCCPLF                |

| 15         | GFA1/IO121RSB1        |

| 16         | GFA2/IO120RSB1        |

| 17         | VCC                   |

| 18         | VCCIB1                |

| 19         | GEC0/IO111RSB1        |

| 20         | GEB1/IO110RSB1        |

| 21         | GEB0/IO109RSB1        |

| 22         | GEA1/IO108RSB1        |

| 23         | GEA0/IO107RSB1        |

| 24         | VMV1                  |

| 25         | GNDQ                  |

| 26         | GEA2/IO106RSB1        |

| 27         | FF/GEB2/IO105RSB<br>1 |

| 28         | GEC2/IO104RSB1        |

| 29         | IO102RSB1             |

| 30         | IO100RSB1             |

| 31         | IO99RSB1              |

| 32         | IO97RSB1              |

| 33         | IO96RSB1              |

| 34         | IO95RSB1              |

| 35         | IO94RSB1              |

| VQ100                        |               |

|------------------------------|---------------|

| Pin Number   AGL125 Function |               |

| 36                           | IO93RSB1      |

| 37                           | VCC           |

| 38                           | GND           |

| 39                           | VCCIB1        |

| 40                           | IO87RSB1      |

| 41                           | IO84RSB1      |

| 42                           | IO81RSB1      |

| 43                           | IO75RSB1      |

| 44                           | GDC2/IO72RSB1 |

| 45                           | GDB2/IO71RSB1 |

| 46                           | GDA2/IO70RSB1 |

| 47                           | TCK           |

| 48                           | TDI           |

| 49                           | TMS           |

| 50                           | VMV1          |

| 51                           | GND           |

| 52                           | VPUMP         |

| 53                           | NC            |

| 54                           | TDO           |

| 55                           | TRST          |

| 56                           | VJTAG         |

| 57                           | GDA1/IO65RSB0 |

| 58                           | GDC0/IO62RSB0 |

| 59                           | GDC1/IO61RSB0 |

| 60                           | GCC2/IO59RSB0 |

| 61                           | GCB2/IO58RSB0 |

| 62                           | GCA0/IO56RSB0 |

| 63                           | GCA1/IO55RSB0 |

| 64                           | GCC0/IO52RSB0 |

| 65                           | GCC1/IO51RSB0 |

| 66                           | VCCIB0        |

| 67                           | GND           |

| 68                           | VCC           |

| 69                           | IO47RSB0      |

| 70                           | GBC2/IO45RSB0 |

| 71                           | GBB2/IO43RSB0 |

| VQ100      |                 |

|------------|-----------------|

| Pin Number | AGL125 Function |

| 72         | IO42RSB0        |

| 73         | GBA2/IO41RSB0   |

| 74         | VMV0            |

| 75         | GNDQ            |

| 76         | GBA1/IO40RSB0   |

| 77         | GBA0/IO39RSB0   |

| 78         | GBB1/IO38RSB0   |

| 79         | GBB0/IO37RSB0   |

| 80         | GBC1/IO36RSB0   |

| 81         | GBC0/IO35RSB0   |

| 82         | IO32RSB0        |

| 83         | IO28RSB0        |

| 84         | IO25RSB0        |

| 85         | IO22RSB0        |

| 86         | IO19RSB0        |

| 87         | VCCIB0          |

| 88         | GND             |

| 89         | VCC             |

| 90         | IO15RSB0        |

| 91         | IO13RSB0        |

| 92         | IO11RSB0        |

| 93         | IO09RSB0        |

| 94         | IO07RSB0        |

| 95         | GAC1/IO05RSB0   |

| 96         | GAC0/IO04RSB0   |

| 97         | GAB1/IO03RSB0   |

| 98         | GAB0/IO02RSB0   |

| 99         | GAA1/IO01RSB0   |

| 100        | GAA0/IO00RSB0   |

4-40 Revision 27

IGLOO Low Power Flash FPGAs

|            | FG144            |

|------------|------------------|

| Pin Number | AGL1000 Function |

| A1         | GNDQ             |

| A2         | VMV0             |

| A3         | GAB0/IO02RSB0    |

| A4         | GAB1/IO03RSB0    |

| A5         | IO10RSB0         |

| A6         | GND              |

| A7         | IO44RSB0         |

| A8         | VCC              |

| A9         | IO69RSB0         |

| A10        | GBA0/IO76RSB0    |

| A11        | GBA1/IO77RSB0    |

| A12        | GNDQ             |

| B1         | GAB2/IO224PDB3   |

| B2         | GND              |

| В3         | GAA0/IO00RSB0    |

| B4         | GAA1/IO01RSB0    |

| B5         | IO13RSB0         |

| В6         | IO26RSB0         |

| B7         | IO35RSB0         |

| B8         | IO60RSB0         |

| В9         | GBB0/IO74RSB0    |

| B10        | GBB1/IO75RSB0    |

| B11        | GND              |

| B12        | VMV1             |

| C1         | IO224NDB3        |

| C2         | GFA2/IO206PPB3   |

| C3         | GAC2/IO223PDB3   |

| C4         | VCC              |

| C5         | IO16RSB0         |

| C6         | IO29RSB0         |

| C7         | IO32RSB0         |

| C8         | IO63RSB0         |

| C9         | IO66RSB0         |

| C10        | GBA2/IO78PDB1    |

| C11        | IO78NDB1         |

| C12        | GBC2/IO80PPB1    |

|            | FG144            |

|------------|------------------|

| Pin Number | AGL1000 Function |

| D1         | IO213PDB3        |

| D2         | IO213NDB3        |

| D3         | IO223NDB3        |

| D4         | GAA2/IO225PPB3   |

| D5         | GAC0/IO04RSB0    |

| D6         | GAC1/IO05RSB0    |

| D7         | GBC0/IO72RSB0    |

| D8         | GBC1/IO73RSB0    |

| D9         | GBB2/IO79PDB1    |

| D10        | IO79NDB1         |

| D11        | IO80NPB1         |

| D12        | GCB1/IO92PPB1    |

| E1         | VCC              |

| E2         | GFC0/IO209NDB3   |

| E3         | GFC1/IO209PDB3   |

| E4         | VCCIB3           |

| E5         | IO225NPB3        |

| E6         | VCCIB0           |

| E7         | VCCIB0           |

| E8         | GCC1/IO91PDB1    |

| E9         | VCCIB1           |

| E10        | VCC              |

| E11        | GCA0/IO93NDB1    |

| E12        | IO94NDB1         |

| F1         | GFB0/IO208NPB3   |

| F2         | VCOMPLF          |

| F3         | GFB1/IO208PPB3   |

| F4         | IO206NPB3        |

| F5         | GND              |

| F6         | GND              |

| F7         | GND              |

| F8         | GCC0/IO91NDB1    |

| F9         | GCB0/IO92NPB1    |

| F10        | GND              |

| F11        | GCA1/IO93PDB1    |

| F12        | GCA2/IO94PDB1    |

| FG144      |                  |

|------------|------------------|

| Din Number | AGL1000 Function |

| Pin Number |                  |

| G1         | GFA1/IO207PPB3   |

| G2         | GND              |

| G3         | VCCPLF           |

| G4         | GFA0/IO207NPB3   |

| G5         | GND              |

| G6         | GND              |

| G7         | GND              |

| G8         | GDC1/IO111PPB1   |

| G9         | IO96NDB1         |

| G10        | GCC2/IO96PDB1    |

| G11        | IO95NDB1         |

| G12        | GCB2/IO95PDB1    |

| H1         | VCC              |

| H2         | GFB2/IO205PDB3   |

| H3         | GFC2/IO204PSB3   |

| H4         | GEC1/IO190PDB3   |

| H5         | VCC              |

| H6         | IO105PDB1        |

| H7         | IO105NDB1        |

| H8         | GDB2/IO115RSB2   |

| H9         | GDC0/IO111NPB1   |

| H10        | VCCIB1           |

| H11        | IO101PSB1        |

| H12        | VCC              |

| J1         | GEB1/IO189PDB3   |

| J2         | IO205NDB3        |

| J3         | VCCIB3           |

| J4         | GEC0/IO190NDB3   |

| J5         | IO160RSB2        |

| J6         | IO157RSB2        |

| J7         | VCC              |

| J8         | TCK              |

| J9         | GDA2/IO114RSB2   |

| J10        | TDO              |

| J11        | GDA1/IO113PDB1   |

| J12        | GDB1/IO112PDB1   |

Revision 27 4-51

| FG484      |                 |

|------------|-----------------|

| Pin Number | AGL600 Function |

| R9         | VCCIB2          |

| R10        | VCCIB2          |

| R11        | IO117RSB2       |

| R12        | IO110RSB2       |

| R13        | VCCIB2          |

| R14        | VCCIB2          |

| R15        | VMV2            |

| R16        | IO94RSB2        |

| R17        | GDB1/IO87PPB1   |

| R18        | GDC1/IO86PDB1   |

| R19        | IO84NDB1        |

| R20        | VCC             |

| R21        | IO81NDB1        |

| R22        | IO82PDB1        |

| T1         | IO152PDB3       |

| T2         | IO152NDB3       |

| Т3         | NC              |

| T4         | IO150NDB3       |

| T5         | IO147PPB3       |

| T6         | GEC1/IO146PPB3  |

| T7         | IO140RSB2       |

| Т8         | GNDQ            |

| Т9         | GEA2/IO143RSB2  |

| T10        | IO126RSB2       |

| T11        | IO120RSB2       |

| T12        | IO108RSB2       |

| T13        | IO103RSB2       |

| T14        | IO99RSB2        |

| T15        | GNDQ            |

| T16        | IO92RSB2        |

| T17        | VJTAG           |

| T18        | GDC0/IO86NDB1   |

| T19        | GDA1/IO88PDB1   |

| T20        | NC              |

| T21        | IO83PDB1        |

| T22        | IO82NDB1        |

4-86 Revision 27

| FG484      |                  |

|------------|------------------|

| Pin Number | AGL1000 Function |

| N17        | IO100NPB1        |

| N18        | IO102NDB1        |

| N19        | IO102PDB1        |

| N20        | NC               |

| N21        | IO101NPB1        |

| N22        | IO103PDB1        |

| P1         | NC               |

| P2         | IO199PDB3        |

| P3         | IO199NDB3        |

| P4         | IO202NDB3        |

| P5         | IO202PDB3        |

| P6         | IO196PPB3        |

| P7         | IO193PPB3        |

| P8         | VCCIB3           |

| P9         | GND              |

| P10        | VCC              |

| P11        | VCC              |

| P12        | VCC              |

| P13        | VCC              |

| P14        | GND              |

| P15        | VCCIB1           |

| P16        | GDB0/IO112NPB1   |

| P17        | IO106NDB1        |

| P18        | IO106PDB1        |

| P19        | IO107PDB1        |

| P20        | NC               |

| P21        | IO104PDB1        |

| P22        | IO103NDB1        |

| R1         | NC               |

| R2         | IO197PPB3        |

| R3         | VCC              |

| R4         | IO197NPB3        |

| R5         | IO196NPB3        |

| R6         | IO193NPB3        |

| R7         | GEC0/IO190NPB3   |

| R8         | VMV3             |

|            |                  |

Revision 27 4-99

| Revision                        | Changes                                                                                                                                                                                                                                                                                                                                                                                                                          | Page                                            |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| Revision 21 (continued)         | Pin description table for AGL125 CS121 was removed as it was incorrectly added to the datasheet in revision 19 (SAR 38217).                                                                                                                                                                                                                                                                                                      | -                                               |

| Revision 20<br>(March 2012)     | Notes indicating that AGL015 is not recommended for new designs have been added. The "Devices Not Recommended For New Designs" section is new (SAR 35015).                                                                                                                                                                                                                                                                       | I to IV                                         |

|                                 | Notes indicating that device/package support is TBD for AGL250-QN132 and AGL060-FG144 have been reinserted (SAR 33689).                                                                                                                                                                                                                                                                                                          | I to IV                                         |

|                                 | Values for the power data for PAC1, PAC2, PAC3, PAC4, PAC7, and PAC8 were revised in Table 2-19 • Different Components Contributing to Dynamic Power Consumption in IGLOO Devices and Table 2-21 • Different Components Contributing to Dynamic Power Consumption in IGLOO Devices to match the SmartPower tool in Libero software version 9.0 SP1 and Power Calculator spreadsheet v7a released on 08/10/2010 (SAR 33768).      | 2-15                                            |

|                                 | The reference to guidelines for global spines and VersaTile rows, given in the "Global Clock Contribution—PCLOCK" section, was corrected to the "Spine Architecture" section of the Global Resources chapter in the <i>IGLOO FPGA Fabric User Guide</i> (SAR 34730).                                                                                                                                                             |                                                 |

|                                 | Figure 2-4 • Input Buffer Timing Model and Delays (example) has been modified for the DIN waveform; the Rise and Fall time label has been changed to t <sub>DIN</sub> (SAR 37104).                                                                                                                                                                                                                                               | 2-21                                            |

|                                 | <ul> <li>Added missing characteristics for 3.3 V LVCMOS, 3.3 V LVCMOS Wide range, 1.2 V LVCMOS, and 1.2 V LVCMOS Wide range to the following tables:</li> <li>Table 2-38, Table 2-39, Table 2-40, Table 2-42, Table 2-43, and Table 2-44 (SARs 33854 and 36891)</li> <li>Table 2-63, Table 2-64, and Table 2-65 (SAR 33854)</li> <li>Table 2-127, Table 2-128, Table 2-129, Table 2-137, Table 2-138, and Table 2-139</li> </ul> | 2-40,<br>2-47 to<br>2-49,<br>2-74,<br>2-77, and |

|                                 | (SAR 36891).  AC Loading figures in the "Single-Ended I/O Characteristics" section were updated to match Table 2-50 · AC Waveforms, Measuring Points, and Capacitive Loads (SAR 34878).                                                                                                                                                                                                                                          |                                                 |

|                                 | Added values for minimum pulse width and removed the FRMAX row from Table 2-173 through Table 2-188 in the "Global Tree Timing Characteristics" section. Use the software to determine the FRMAX for the device you are using (SAR 29271).                                                                                                                                                                                       |                                                 |

| Revision 19<br>(September 2011) | CS121 was added to the product tables in the "IGLOO Low Power Flash FPGAs" section for AGL125 (SAR 22737). CS81 was added for AGL250 (SAR 22737).                                                                                                                                                                                                                                                                                | I                                               |

|                                 | Notes indicating that device/package support is TBD for AGL250-QN132 and AGL060-FG144 have been removed (SAR 33689).                                                                                                                                                                                                                                                                                                             | I to IV                                         |

|                                 | M1AGL400 was removed from the "I/Os Per Package1" table. This device was discontinued in April 2009 (SAR 32450).                                                                                                                                                                                                                                                                                                                 | II                                              |

|                                 | Dimensions for the QN48 package were added to Table 1 • IGLOO FPGAs Package Sizes Dimensions (SAR 30537).                                                                                                                                                                                                                                                                                                                        | II                                              |

|                                 | The Y security option and Licensed DPA Logo were added to the "IGLOO Ordering Information" section. The trademarked Licensed DPA Logo identifies that a product is covered by a DPA counter-measures license from Cryptography Research (SAR 32151).                                                                                                                                                                             |                                                 |

|                                 | The "In-System Programming (ISP) and Security" section and "Security" section were revised to clarify that although no existing security measures can give an absolute guarantee, Microsemi FPGAs implement the best security available in the industry (SAR 32865).                                                                                                                                                             |                                                 |

5-3 Revision 27

IGLOO Low Power Flash FPGAs

| Revision / Version                                  | Changes                                                                                                                                                                                                                                                                  | Page         |

|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Revision 18 (Nov 2009)                              | The version changed to v2.0 for IGLOO datasheet chapters, indicating the datasheet contains information based on final characterization. Please review the datasheet carefully as most tables were updated with new data.                                                | N/A          |

| Revision 17 (Sep 2009) Product Brief v1.6           | The "Reprogrammable Flash Technology" section was modified to add "250 MHz (1.5 V systems) and 160 MHz (1.2 V systems) System Performance."                                                                                                                              | I            |

|                                                     | "IGLOO Ordering Information" was revised to note that halogen-free packages are available with RoHS-compliant packaging.                                                                                                                                                 | III          |

|                                                     | Table 1-1 • I/O Standards Supported is new.                                                                                                                                                                                                                              | 1-7          |

|                                                     | The definitions of hot-swap and cold-sparing were added to the "I/Os with Advanced I/O Standards" section.                                                                                                                                                               | 1-7          |

| Revision 16 (Apr 2009)<br>Product Brief v1.5        | M1AGL400 is no longer offered and was removed from the "IGLOO Devices" product table, "IGLOO Ordering Information", and "Temperature Grade Offerings".                                                                                                                   | I, III, IV   |

|                                                     | The -F speed grade is no longer offered for IGLOO devices. The speed grade column and note regarding -F speed grade were removed from "IGLOO Ordering Information". The "Speed Grade and Temperature Grade Matrix" section was removed.                                  | III, IV      |

|                                                     | This datasheet now has fully characterized data and has moved from being Advance to a Production version. The version number changed from Advance v0.5 to v2.0.                                                                                                          | N/A          |

|                                                     | Please review the datasheet carefully as most tables were updated with new data.                                                                                                                                                                                         |              |

| DC and Switching<br>Characteristics<br>Advance v0.6 | $3.3\ V\ LVCMOS$ and $1.2\ V\ LVCMOS$ Wide Range support was added to the datasheet. This affects all tables that contained $3.3\ V\ LVCMOS$ and $1.2\ V\ LVCMOS$ data.                                                                                                  |              |

|                                                     | ${\rm I}_{\rm IL}$ and ${\rm I}_{\rm IH}$ input leakage current information was added to all "Minimum and Maximum DC Input and Output Levels" tables.                                                                                                                    | N/A          |

|                                                     | -F was removed from the datasheet. The speed grade is no longer supported.                                                                                                                                                                                               | N/A          |

|                                                     | The notes in Table 2-2 • Recommended Operating Conditions 1 were updated.                                                                                                                                                                                                | 2-2          |

|                                                     | Table 2-4 • Overshoot and Undershoot Limits 1 was updated.                                                                                                                                                                                                               | 2-3          |

|                                                     | Table 2-5 • Package Thermal Resistivities was updated.                                                                                                                                                                                                                   | 2-6          |

|                                                     | Table 2-6 • Temperature and Voltage Derating Factors for Timing Delays (normalized to TJ = $70^{\circ}$ C, VCC = $1.425$ V) and Table 2-7 • Temperature and Voltage Derating Factors for Timing Delays (normalized to TJ = $70^{\circ}$ C, VCC = $1.14$ V) were updated. | 2-7          |

|                                                     | In Table 2-191 • RAM4K9 and Table 2-193 • RAM4K9, the following specifications were removed:                                                                                                                                                                             | 2-122<br>and |

|                                                     | t <sub>WRO</sub>                                                                                                                                                                                                                                                         | 2-124        |

|                                                     | <sup>†</sup> ССКН                                                                                                                                                                                                                                                        | _            |

|                                                     | In Table 2-192 • RAM512X18 and Table 2-194 • RAM512X18, the following specifications were removed:                                                                                                                                                                       | 2-123<br>and |

|                                                     | two                                                                                                                                                                                                                                                                      | 2-125        |

|                                                     | t <sub>сскн</sub>                                                                                                                                                                                                                                                        |              |

| Revision 15 (Feb 2009)                              | The "QN132" pin table for the AGL060 device is new.                                                                                                                                                                                                                      | 4-31         |

| Packaging v1.9                                      |                                                                                                                                                                                                                                                                          |              |

Revision 27 5-6