Welcome to **E-XFL.COM**

## Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                |

|--------------------------------|----------------------------------------------------------------|

| Product Status                 | Obsolete                                                       |

| Number of LABs/CLBs            | -                                                              |

| Number of Logic Elements/Cells | 9216                                                           |

| Total RAM Bits                 | 55296                                                          |

| Number of I/O                  | 178                                                            |

| Number of Gates                | 400000                                                         |

| Voltage - Supply               | 1.14V ~ 1.575V                                                 |

| Mounting Type                  | Surface Mount                                                  |

| Operating Temperature          | 0°C ~ 70°C (TA)                                                |

| Package / Case                 | 256-LBGA                                                       |

| Supplier Device Package        | 256-FPBGA (17x17)                                              |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microsemi/agl400v2-fg256t |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

field upgrades with confidence that valuable intellectual property cannot be compromised or copied. Secure ISP can be performed using the industry-standard AES algorithm. The IGLOO family device architecture mitigates the need for ASIC migration at higher user volumes. This makes the IGLOO family a cost-effective ASIC replacement solution, especially for applications in the consumer, networking/communications, computing, and avionics markets.

## Firm-Error Immunity

Firm errors occur most commonly when high-energy neutrons, generated in the upper atmosphere, strike a configuration cell of an SRAM FPGA. The energy of the collision can change the state of the configuration cell and thus change the logic, routing, or I/O behavior in an unpredictable way. These errors are impossible to prevent in SRAM FPGAs. The consequence of this type of error can be a complete system failure. Firm errors do not exist in the configuration memory of IGLOO flash-based FPGAs. Once it is programmed, the flash cell configuration element of IGLOO FPGAs cannot be altered by high-energy neutrons and is therefore immune to them. Recoverable (or soft) errors occur in the user data SRAM of all FPGA devices. These can easily be mitigated by using error detection and correction (EDAC) circuitry built into the FPGA fabric.

## Advanced Flash Technology

The IGLOO family offers many benefits, including nonvolatility and reprogrammability, through an advanced flash-based, 130-nm LVCMOS process with seven layers of metal. Standard CMOS design techniques are used to implement logic and control functions. The combination of fine granularity, enhanced flexible routing resources, and abundant flash switches allows for very high logic utilization without compromising device routability or performance. Logic functions within the device are interconnected through a four-level routing hierarchy.

IGLOO family FPGAs utilize design and process techniques to minimize power consumption in all modes of operation.

#### Advanced Architecture

The proprietary IGLOO architecture provides granularity comparable to standard-cell ASICs. The IGLOO device consists of five distinct and programmable architectural features (Figure 1-1 on page 1-4 and Figure 1-2 on page 1-4):

- Flash\*Freeze technology

- FPGA VersaTiles

- · Dedicated FlashROM

- Dedicated SRAM/FIFO memory<sup>†</sup>

- Extensive CCCs and PLLs<sup>†</sup>

- Advanced I/O structure

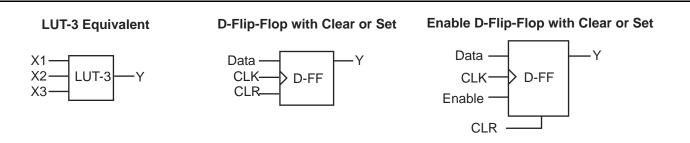

The FPGA core consists of a sea of VersaTiles. Each VersaTile can be configured as a three-input logic function, a D-flip-flop (with or without enable), or a latch by programming the appropriate flash switch interconnections. The versatility of the IGLOO core tile as either a three-input lookup table (LUT) equivalent or a D-flip-flop/latch with enable allows for efficient use of the FPGA fabric. The VersaTile capability is unique to the ProASIC<sup>®</sup> family of third-generation-architecture flash FPGAs.

1-3 Revision 27

<sup>†</sup> The AGL015 and AGL030 do not support PLL or SRAM.

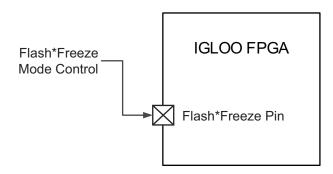

## Flash\*Freeze Technology

The IGLOO device has an ultra-low power static mode, called Flash\*Freeze mode, which retains all SRAM and register information and can still quickly return to normal operation. Flash\*Freeze technology enables the user to quickly (within 1 µs) enter and exit Flash\*Freeze mode by activating the Flash\*Freeze pin while all power supplies are kept at their original values. In addition, I/Os and global I/Os can still be driven and can be toggling without impact on power consumption, clocks can still be driven or can be toggling without impact on power consumption, and the device retains all core registers, SRAM information, and states. I/O states are tristated during Flash\*Freeze mode or can be set to a certain state using weak pull-up or pull-down I/O attribute configuration. No power is consumed by the I/O banks, clocks, JTAG pins, or PLL, and the device consumes as little as 5 µW in this mode.

Flash\*Freeze technology allows the user to switch to active mode on demand, thus simplifying the power management of the device.

The Flash\*Freeze pin (active low) can be routed internally to the core to allow the user's logic to decide when it is safe to transition to this mode. It is also possible to use the Flash\*Freeze pin as a regular I/O if Flash\*Freeze mode usage is not planned, which is advantageous because of the inherent low power static (as low as 12 µW) and dynamic capabilities of the IGLOO device. Refer to Figure 1-3 for an illustration of entering/exiting Flash\*Freeze mode.

Figure 1-3 • IGLOO Flash\*Freeze Mode

#### VersaTiles

The IGLOO core consists of VersaTiles, which have been enhanced beyond the ProASIC PLUS® core tiles. The IGLOO VersaTile supports the following:

- All 3-input logic functions—LUT-3 equivalent

- · Latch with clear or set

- · D-flip-flop with clear or set

- Enable D-flip-flop with clear or set

Refer to Figure 1-4 for VersaTile configurations.

Figure 1-4 • VersaTile Configurations

1-5 Revision 27

Table 2-3 • Flash Programming Limits – Retention, Storage, and Operating Temperature<sup>1</sup>

| Product Grade | Programming Cycles | Program Retention (biased/unbiased) | Maximum Storage<br>Temperature T <sub>STG</sub> (°C) <sup>2</sup> | Maximum Operating Junction<br>Temperature T <sub>J</sub> (°C) <sup>2</sup> |

|---------------|--------------------|-------------------------------------|-------------------------------------------------------------------|----------------------------------------------------------------------------|

| Commercial    | 500                | 20 years                            | 110                                                               | 100                                                                        |

| Industrial    | 500                | 20 years                            | 110                                                               | 100                                                                        |

- 1. This is a stress rating only; functional operation at any condition other than those indicated is not implied.

- These limits apply for program/data retention only. Refer to Table 2-1 on page 2-1 and Table 2-2 on page 2-2 for device operating conditions and absolute limits.

Table 2-4 • Overshoot and Undershoot Limits 1

| VCCI          | Average VCCI–GND Overshoot or Undershoot Duration as a Percentage of Clock Cycle <sup>2</sup> | Maximum Overshoot/<br>Undershoot <sup>2</sup> |

|---------------|-----------------------------------------------------------------------------------------------|-----------------------------------------------|

| 2.7 V or less | 10%                                                                                           | 1.4 V                                         |

|               | 5%                                                                                            | 1.49 V                                        |

| 3 V           | 10%                                                                                           | 1.1 V                                         |

|               | 5%                                                                                            | 1.19 V                                        |

| 3.3 V         | 10%                                                                                           | 0.79 V                                        |

|               | 5%                                                                                            | 0.88 V                                        |

| 3.6 V         | 10%                                                                                           | 0.45 V                                        |

|               | 5%                                                                                            | 0.54 V                                        |

#### Notes:

- 1. Based on reliability requirements at junction temperature at 85°C.

- 2. The duration is allowed at one out of six clock cycles. If the overshoot/undershoot occurs at one out of two cycles, the maximum overshoot/undershoot has to be reduced by 0.15 V.

- 3. This table does not provide PCI overshoot/undershoot limits.

# I/O Power-Up and Supply Voltage Thresholds for Power-On Reset (Commercial and Industrial)

Sophisticated power-up management circuitry is designed into every IGLOO device. These circuits ensure easy transition from the powered-off state to the powered-up state of the device. The many different supplies can power up in any sequence with minimized current spikes or surges. In addition, the I/O will be in a known state through the power-up sequence. The basic principle is shown in Figure 2-1 on page 2-4 and Figure 2-2 on page 2-5.

There are five regions to consider during power-up.

IGLOO I/Os are activated only if ALL of the following three conditions are met:

- 1. VCC and VCCI are above the minimum specified trip points (Figure 2-1 on page 2-4 and Figure 2-2 on page 2-5).

- 2. VCCI > VCC 0.75 V (typical)

- 3. Chip is in the operating mode.

#### **VCCI Trip Point:**

Ramping up (V5 devices): 0.6 V < trip\_point\_up < 1.2 V Ramping down (V5 Devices): 0.5 V < trip\_point\_down < 1.1 V Ramping up (V2 devices): 0.75 V < trip\_point\_up < 1.05 V Ramping down (V2 devices): 0.65 V < trip\_point\_down < 0.95 V

### **VCC Trip Point:**

Ramping up (V5 devices): 0.6 V < trip\_point\_up < 1.1 V Ramping down (V5 devices): 0.5 V < trip\_point\_down < 1.0 V

## Package Thermal Characteristics

The device junction-to-case thermal resistivity is  $\theta_{jc}$  and the junction-to-ambient air thermal resistivity is  $\theta_{ja}$ . The thermal characteristics for  $\theta_{ja}$  are shown for two air flow rates. The absolute maximum junction temperature is 100°C. EQ 2 shows a sample calculation of the absolute maximum power dissipation allowed for the AGL1000-FG484 package at commercial temperature and in still air.

$$\text{Maximum Power Allowed } = \frac{\text{Max. junction temp. (°C)} - \text{Max. ambient temp. (°C)}}{\theta_{ja}(°\text{C/W})} = \frac{100°\text{C} - 70°\text{C}}{23.3°\text{C/W}} = 1.28~\text{W}$$

EQ2

Table 2-5 • Package Thermal Resistivities

|                                 |         |           |                     |           | $\theta$ ja |         |      |

|---------------------------------|---------|-----------|---------------------|-----------|-------------|---------|------|

| Package Type                    | Device  | Pin Count | $\theta$ j $_{f c}$ | Still Air | 1 m/s       | 2.5 m/s | Unit |

| Quad Flat No Lead (QN)          | AGL030  | 132       | 13.1                | 21.4      | 16.8        | 15.3    | C/W  |

|                                 | AGL060  | 132       | 11.0                | 21.2      | 16.6        | 15.0    | C/W  |

|                                 | AGL125  | 132       | 9.2                 | 21.1      | 16.5        | 14.9    | C/W  |

|                                 | AGL250  | 132       | 8.9                 | 21.0      | 16.4        | 14.8    | C/W  |

|                                 | AGL030  | 68        | 13.4                | 68.4      | 45.8        | 43.1    | C/W  |

| Very Thin Quad Flat Pack (VQ)*  |         | 100       | 10.0                | 35.3      | 29.4        | 27.1    | C/W  |

| Chip Scale Package (CS)         | AGL1000 | 281       | 6.0                 | 28.0      | 22.8        | 21.5    | C/W  |

|                                 | AGL400  | 196       | 7.2                 | 37.1      | 31.1        | 28.9    | C/W  |

|                                 | AGL250  | 196       | 7.6                 | 38.3      | 32.2        | 30.0    | C/W  |

|                                 | AGL125  | 196       | 8.0                 | 39.5      | 33.4        | 31.1    | C/W  |

|                                 | AGL030  | 81        | 12.4                | 32.8      | 28.5        | 27.2    | C/W  |

|                                 | AGL060  | 81        | 11.1                | 28.8      | 24.8        | 23.5    | C/W  |

|                                 | AGL250  | 81        | 10.4                | 26.9      | 22.3        | 20.9    | C/W  |

| Micro Chip Scale Package (UC)   | AGL030  | 81        | 16.9                | 40.6      | 35.2        | 33.7    | C/W  |

| Fine Pitch Ball Grid Array (FG) | AGL060  | 144       | 18.6                | 55.2      | 49.4        | 47.2    | C/W  |

|                                 | AGL1000 | 144       | 6.3                 | 31.6      | 26.2        | 24.2    | C/W  |

|                                 | AGL400  | 144       | 6.8                 | 37.6      | 31.2        | 29.0    | C/W  |

|                                 | AGL250  | 256       | 12.0                | 38.6      | 34.7        | 33.0    | C/W  |

|                                 | AGL1000 | 256       | 6.6                 | 28.1      | 24.4        | 22.7    | C/W  |

|                                 | AGL1000 | 484       | 8.0                 | 23.3      | 19.0        | 16.7    | C/W  |

Note: \*Thermal resistances for other device-package combinations will be posted in a later revision.

#### Disclaimer:

The simulation for determining the junction-to-air thermal resistance is based on JEDEC standards (JESD51) and assumptions made in building the model. Junction-to-case is based on SEMI G38-88. JESD51 is only used for comparing one package to another package, provided the two tests uses the same condition. They have little relevance in actual application and therefore should be used with a degree of caution.

2-6 Revision 27

Table 2-10 • Quiescent Supply Current (IDD) Characteristics, IGLOO Sleep Mode\*

|                                                 | Core<br>Voltage  | AGL015 | AGL030 | AGL060 | AGL125 | AGL250 | AGL400 | AGL600 | AGL1000 | Units |

|-------------------------------------------------|------------------|--------|--------|--------|--------|--------|--------|--------|---------|-------|

| VCCI/VJTAG = 1.2 V<br>(per bank) Typical (25°C) | 1.2 V            | 1.7    | 1.7    | 1.7    | 1.7    | 1.7    | 1.7    | 1.7    | 1.7     | μΑ    |

| VCCI/VJTAG = 1.5 V<br>(per bank) Typical (25°C) | 1.2 V / 1.5<br>V | 1.8    | 1.8    | 1.8    | 1.8    | 1.8    | 1.8    | 1.8    | 1.8     | μΑ    |

| VCCI/VJTAG = 1.8 V<br>(per bank) Typical (25°C) | 1.2 V / 1.5<br>V | 1.9    | 1.9    | 1.9    | 1.9    | 1.9    | 1.9    | 1.9    | 1.9     | μA    |

| VCCI/VJTAG = 2.5 V<br>(per bank) Typical (25°C) | 1.2 V / 1.5<br>V | 2.2    | 2.2    | 2.2    | 2.2    | 2.2    | 2.2    | 2.2    | 2.2     | μA    |

| VCCI/VJTAG = 3.3 V<br>(per bank) Typical (25°C) | 1.2 V / 1.5<br>V | 2.5    | 2.5    | 2.5    | 2.5    | 2.5    | 2.5    | 2.5    | 2.5     | μΑ    |

Note:  $IDD = N_{BANKS} \times ICCI$ . Values do not include I/O static contribution, which is shown in Table 2-13 on page 2-10 through Table 2-15 on page 2-11 and Table 2-16 on page 2-11 through Table 2-18 on page 2-12 (PDC6 and PDC7).

Table 2-11 • Quiescent Supply Current (IDD) Characteristics, IGLOO Shutdown Mode

|                | Core Voltage  | AGL015 | AGL030 | Units |

|----------------|---------------|--------|--------|-------|

| Typical (25°C) | 1.2 V / 1.5 V | 0      | 0      | μΑ    |

Table 2-12 • Quiescent Supply Current (IDD), No IGLOO Flash\*Freeze Mode<sup>1</sup>

|                                                 | Core<br>Voltage  | AGL015 | AGL030 | AGL060 | AGL125 | AGL250 | AGL400 | AGL600 | AGL1000 | Units |  |  |  |

|-------------------------------------------------|------------------|--------|--------|--------|--------|--------|--------|--------|---------|-------|--|--|--|

| CCA Current <sup>2</sup>                        |                  |        |        |        |        |        |        |        |         |       |  |  |  |

| Typical (25°C)                                  | 1.2 V            | 5      | 6      | 10     | 13     | 18     | 25     | 28     | 42      | μΑ    |  |  |  |

|                                                 | 1.5 V            | 14     | 16     | 20     | 28     | 44     | 66     | 82     | 137     | μΑ    |  |  |  |

| ICCI or IJTAG Current <sup>3</sup>              |                  |        |        |        |        |        |        |        |         |       |  |  |  |

| VCCI/VJTAG = 1.2 V<br>(per bank) Typical (25°C) | 1.2 V            | 1.7    | 1.7    | 1.7    | 1.7    | 1.7    | 1.7    | 1.7    | 1.7     | μΑ    |  |  |  |

| VCCI/VJTAG = 1.5 V (per bank) Typical (25°C)    | 1.2 V /<br>1.5 V | 1.8    | 1.8    | 1.8    | 1.8    | 1.8    | 1.8    | 1.8    | 1.8     | μΑ    |  |  |  |

| VCCI/VJTAG = 1.8 V (per bank) Typical (25°C)    | 1.2 V /<br>1.5 V | 1.9    | 1.9    | 1.9    | 1.9    | 1.9    | 1.9    | 1.9    | 1.9     | μΑ    |  |  |  |

| VCCI/VJTAG = 2.5 V (per<br>bank) Typical (25°C) | 1.2 V /<br>1.5 V | 2.2    | 2.2    | 2.2    | 2.2    | 2.2    | 2.2    | 2.2    | 2.2     | μΑ    |  |  |  |

| VCCI/VJTAG = 3.3 V (per bank) Typical (25°C)    | 1.2 V /<br>1.5 V | 2.5    | 2.5    | 2.5    | 2.5    | 2.5    | 2.5    | 2.5    | 2.5     | μA    |  |  |  |

#### Notes:

- 1.  $IDD = N_{BANKS} \times ICCI + ICCA$ . JTAG counts as one bank when powered.

- 2. Includes VCC, VPUMP, and VCCPLL currents.

- 3. Values do not include I/O static contribution (PDC6 and PDC7).

2-8 Revision 27

Table 2-17 • Summary of I/O Output Buffer Power (per pin) – Default I/O Software Settings<sup>1</sup>

Applicable to Standard Plus I/O Banks

|                                      | C <sub>LOAD</sub> (pF) | VCCI (V) | Static Power<br>PDC7 (mW) <sup>2</sup> | Dynamic Power<br>PAC10 (μW/MHz) <sup>3</sup> |

|--------------------------------------|------------------------|----------|----------------------------------------|----------------------------------------------|

| Single-Ended                         |                        |          |                                        |                                              |

| 3.3 V LVTTL / 3.3 V LVCMOS           | 5                      | 3.3      | -                                      | 122.16                                       |

| 3.3 V LVCMOS Wide Range <sup>4</sup> | 5                      | 3.3      | -                                      | 122.16                                       |

| 2.5 V LVCMOS                         | 5                      | 2.5      | -                                      | 68.37                                        |

| 1.8 V LVCMOS                         | 5                      | 1.8      | -                                      | 34.53                                        |

| 1.5 V LVCMOS (JESD8-11)              | 5                      | 1.5      | -                                      | 23.66                                        |

| 1.2 V LVCMOS <sup>5</sup>            | 5                      | 1.2      | _                                      | 14.90                                        |

| 1.2 V LVCMOS Wide Range <sup>5</sup> | 5                      | 1.2      | _                                      | 14.90                                        |

| 3.3 V PCI                            | 10                     | 3.3      | -                                      | 181.06                                       |

| 3.3 V PCI-X                          | 10                     | 3.3      | -                                      | 181.06                                       |

- 1. Dynamic power consumption is given for standard load and software default drive strength and output slew.

- 2. P<sub>DC7</sub> is the static power (where applicable) measured on VCCI.

- 3. P<sub>AC10</sub> is the total dynamic power measured on VCCI.

- 4. All LVCMOS 3.3 V software macros support LVCMOS 3.3 V wide range as specified in the JESD-8B specification.

- 5. Applicable for IGLOO V2 devices only.

Table 2-18 • Summary of I/O Output Buffer Power (per pin) – Default I/O Software Settings<sup>1</sup>

Applicable to Standard I/O Banks

|                                      | C <sub>LOAD</sub> (pF) | VCCI (V) | Static Power<br>PDC7 (mW) <sup>2</sup> | Dynamic Power<br>PAC10 (μW/MHz) <sup>3</sup> |

|--------------------------------------|------------------------|----------|----------------------------------------|----------------------------------------------|

| Single-Ended                         | •                      | •        |                                        |                                              |

| 3.3 V LVTTL / 3.3 V LVCMOS           | 5                      | 3.3      | _                                      | 104.38                                       |

| 3.3 V LVCMOS Wide Range <sup>4</sup> | 5                      | 3.3      | _                                      | 104.38                                       |

| 2.5 V LVCMOS                         | 5                      | 2.5      | -                                      | 59.86                                        |

| 1.8 V LVCMOS                         | 5                      | 1.8      | -                                      | 31.26                                        |

| 1.5 V LVCMOS (JESD8-11)              | 5                      | 1.5      | -                                      | 21.96                                        |

| 1.2 V LVCMOS <sup>5</sup>            | 5                      | 1.2      | -                                      | 13.49                                        |

| 1.2 V LVCMOS Wide Range <sup>5</sup> | 5                      | 1.2      | -                                      | 13.49                                        |

#### Notes:

- 1. Dynamic power consumption is given for standard load and software default drive strength and output slew.

- 2. PDC7 is the static power (where applicable) measured on VCCI.

- 3. PAC10 is the total dynamic power measured on VCCI.

- 4. All LVCMOS 3.3 V software macros support LVCMOS 3.3 V wide range as specified in the JESD-8B specification.

- 5. Applicable for IGLOO V2 devices only.

Table 2-31 • Summary of I/O Timing Characteristics—Software Default Settings, Std. Speed Grade, Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI (per standard)

Applicable to Advanced I/O Banks

| I/O Standard                                  | Drive Strength     | Equivalent Software Default<br>Drive Strength Option <sup>1</sup> (mA) | Slew Rate | Capacitive Load (pF) | External Resistor $(\Omega)$ | t <sub>DOUT</sub> (ns) | t <sub>DP</sub> (ns) | <sup>t</sup> DIN (ns) | t <sub>PY</sub> (ns) | t <sub>EOUT</sub> (ns) | t <sub>ZL</sub> (ns) | (su) <sup>HZ</sup> <sub>1</sub> | t <sub>LZ</sub> (ns) | t <sub>HZ</sub> (ns) | t <sub>ZLS</sub> (ns) | (su) SHZ <sub>1</sub> | Units |

|-----------------------------------------------|--------------------|------------------------------------------------------------------------|-----------|----------------------|------------------------------|------------------------|----------------------|-----------------------|----------------------|------------------------|----------------------|---------------------------------|----------------------|----------------------|-----------------------|-----------------------|-------|

| 3.3 V<br>LVTTL /<br>3.3 V<br>LVCMOS           | 12 mA              | 12                                                                     | High      | 5                    | _                            | 0.97                   | 2.09                 | 0.18                  | 0.85                 | 0.66                   | 2.14                 | 1.68                            | 2.67                 | 3.05                 | 5.73                  | 5.27                  | ns    |

| 3.3 V<br>LVCMOS<br>Wide<br>Range <sup>2</sup> | 100 μΑ             | 12                                                                     | High      | 5                    | _                            | 0.97                   | 2.93                 | 0.18                  | 1.19                 | 0.66                   | 2.95                 | 2.27                            | 3.81                 | 4.30                 | 6.54                  | 5.87                  | ns    |

| 2.5 V<br>LVCMOS                               | 12 mA              | 12                                                                     | High      | 5                    | -                            | 0.97                   | 2.09                 | 0.18                  | 1.08                 | 0.66                   | 2.14                 | 1.83                            | 2.73                 | 2.93                 | 5.73                  | 5.43                  | ns    |

| 1.8 V<br>LVCMOS                               | 12 mA              | 12                                                                     | High      | 5                    | _                            | 0.97                   | 2.24                 | 0.18                  | 1.01                 | 0.66                   | 2.29                 | 2.00                            | 3.02                 | 3.40                 | 5.88                  | 5.60                  | ns    |

| 1.5 V<br>LVCMOS                               | 12 mA              | 12                                                                     | High      | 5                    | _                            | 0.97                   | 2.50                 | 0.18                  | 1.17                 | 0.66                   | 2.56                 | 2.27                            | 3.21                 | 3.48                 | 6.15                  | 5.86                  | ns    |

| 3.3 V PCI                                     | Per PCI<br>spec    | 1                                                                      | High      | 10                   | 25 <sup>2</sup>              | 0.97                   | 2.32                 | 0.18                  | 0.74                 | 0.66                   | 2.37                 | 1.78                            | 2.67                 | 3.05                 | 5.96                  | 5.38                  | ns    |

| 3.3 V<br>PCI-X                                | Per PCI-<br>X spec | -                                                                      | High      | 10                   | 25 <sup>2</sup>              | 0.97                   | 2.32                 | 0.19                  | 0.70                 | 0.66                   | 2.37                 | 1.78                            | 2.67                 | 3.05                 | 5.96                  | 5.38                  | ns    |

| LVDS                                          | 24 mA              | _                                                                      | High      | -                    | -                            | 0.97                   | 1.74                 | 0.19                  | 1.35                 | _                      | _                    | -                               | -                    | _                    | _                     | -                     | ns    |

| LVPECL                                        | 24 mA              | _                                                                      | High      | -                    | -                            | 0.97                   | 1.68                 | 0.19                  | 1.16                 | _                      | _                    | _                               | _                    | _                    | _                     | _                     | ns    |

| N1-4                                          |                    |                                                                        |           |                      |                              |                        |                      |                       |                      |                        |                      |                                 |                      |                      |                       |                       |       |

4. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

2-28 Revision 27

The minimum drive strength for any LVCMOS 3.3 V software configuration when run in wide range is ±100 μA. Drive strength displayed in the software is supported for normal range only. For a detailed I/V curve, refer to the IBIS models.

<sup>2.</sup> All LVCMOS 3.3 V software macros support LVCMOS 3.3 V wide range as specified in the JESD-8B specification.

<sup>3.</sup> Resistance is used to measure I/O propagation delays as defined in PCI specifications. See Figure 2-12 on page 2-79 for connectivity. This resistor is not required during normal operation.

Table 2-32 • Summary of I/O Timing Characteristics—Software Default Settings, Std. Speed Grade, Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI (per standard)

Applicable to Standard Plus I/O Banks

| I/O Standard                                  | Drive Strength     | Equivalent Software Default<br>Drive Strength Option <sup>1</sup> (mA <sup>)</sup> | Slew Rate | Capacitive Load (pF) | External Resistor $(\Omega)$ | t <sub>DOUT</sub> (ns) | t <sub>DP</sub> (ns) | t <sub>DIN</sub> (ns) | t <sub>PY</sub> (ns) | t <sub>EOUT</sub> (ns) | t <sub>ZL</sub> (ns) | t <sub>ZH</sub> (ns) | t <sub>LZ</sub> (ns) | t <sub>HZ</sub> (ns) | t <sub>ZLS</sub> (ns) | t <sub>ZHS</sub> (ns) | Units |

|-----------------------------------------------|--------------------|------------------------------------------------------------------------------------|-----------|----------------------|------------------------------|------------------------|----------------------|-----------------------|----------------------|------------------------|----------------------|----------------------|----------------------|----------------------|-----------------------|-----------------------|-------|

| 3.3 V<br>LVTTL /<br>3.3 V<br>LVCMOS           | 12 mA              | 12                                                                                 | High      | 5                    | _                            | 0.97                   | 1.75                 | 0.18                  | 0.85                 | 0.66                   | 1.79                 | 1.40                 | 2.36                 | 2.79                 | 5.38                  | 4.99                  | ns    |

| 3.3 V<br>LVCMOS<br>Wide<br>Range <sup>2</sup> | 100 μΑ             | 12                                                                                 | High      | 5                    | _                            | 0.97                   | 2.45                 | 0.18                  | 1.20                 | 0.66                   | 2.47                 | 1.92                 | 3.33                 | 3.90                 | 6.06                  | 5.51                  | ns    |

| 2.5 V<br>LVCMOS                               | 12 mA              | 12                                                                                 | High      | 5                    | _                            | 0.97                   | 1.75                 | 0.18                  | 1.08                 | 0.66                   | 1.79                 | 1.52                 | 2.38                 | 2.70                 | 5.39                  | 5.11                  | ns    |

| 1.8 V<br>LVCMOS                               | 8 mA               | 8                                                                                  | High      | 5                    | _                            | 0.97                   | 1.97                 | 0.18                  | 1.01                 | 0.66                   | 2.02                 | 1.76                 | 2.46                 | 2.66                 | 5.61                  | 5.36                  | ns    |

| 1.5 V<br>LVCMOS                               | 4 mA               | 4                                                                                  | High      | 5                    | _                            | 0.97                   | 2.25                 | 0.18                  | 1.18                 | 0.66                   | 2.30                 | 2.00                 | 2.53                 | 2.68                 | 5.89                  | 5.59                  | ns    |

| 3.3 V PCI                                     | Per PCI<br>spec    | Ι                                                                                  | High      | 10                   | 25 <sup>2</sup>              | 0.97                   | 1.97                 | 0.18                  | 0.73                 | 0.66                   | 2.01                 | 1.50                 | 2.36                 | 2.79                 | 5.61                  | 5.10                  | ns    |

| 3.3 V<br>PCI-X                                | Per PCI-<br>X spec | _                                                                                  | High      | 10                   | 25 <sup>2</sup>              | 0.97                   | 1.97                 | 0.19                  | 0.70                 | 0.66                   | 2.01                 | 1.50                 | 2.36                 | 2.79                 | 5.61                  | 5.10                  | ns    |

4. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

The minimum drive strength for any LVCMOS 3.3 V software configuration when run in wide range is ±100 μA. Drive strength displayed in the software is supported for normal range only. For a detailed I/V curve, refer to the IBIS models.

<sup>2.</sup> All LVCMOS 3.3 V software macros support LVCMOS 3.3 V wide range as specified in the JESD-8B specification.

<sup>3.</sup> Resistance is used to measure I/O propagation delays as defined in PCI specifications. See Figure 2-12 on page 2-79 for connectivity. This resistor is not required during normal operation.

Table 2-44 • I/O Short Currents IOSH/IOSL

Applicable to Standard I/O Banks

|                            | Drive Strength | IOSL (mA)*                   | IOSH (mA)*                   |

|----------------------------|----------------|------------------------------|------------------------------|

| 3.3 V LVTTL / 3.3 V LVCMOS | 2 mA           | 25                           | 27                           |

|                            | 4 mA           | 25                           | 27                           |

|                            | 6 mA           | 51                           | 54                           |

|                            | 8 mA           | 51                           | 54                           |

| 3.3 V LVCMOS Wide Range    | 100 μΑ         | Same as regular 3.3 V LVCMOS | Same as regular 3.3 V LVCMOS |

| 2.5 V LVCMOS               | 2 mA           | 16                           | 18                           |

|                            | 4 mA           | 16                           | 18                           |

|                            | 6 mA           | 32                           | 37                           |

|                            | 8 mA           | 32                           | 37                           |

| 1.8 V LVCMOS               | 2 mA           | 9                            | 11                           |

|                            | 4 mA           | 17                           | 22                           |

| 1.5 V LVCMOS               | 2 mA           | 13                           | 16                           |

| 1.2 V LVCMOS               | 1 mA           | 20                           | 26                           |

| 1.2 V LVCMOS Wide Range    | 100 μΑ         | 20                           | 26                           |

Note:  ${}^*T_J = 100^{\circ}C$

The length of time an I/O can withstand  $I_{OSH}/I_{OSL}$  events depends on the junction temperature. The reliability data below is based on a 3.3 V, 12 mA I/O setting, which is the worst case for this type of analysis.

For example, at 100°C, the short current condition would have to be sustained for more than six months to cause a reliability concern. The I/O design does not contain any short circuit protection, but such protection would only be needed in extremely prolonged stress conditions.

Table 2-45 • Duration of Short Circuit Event before Failure

| Temperature | Time before Failure |

|-------------|---------------------|

| -40°C       | > 20 years          |

| -20°C       | > 20 years          |

| 0°C         | > 20 years          |

| 25°C        | > 20 years          |

| 70°C        | 5 years             |

| 85°C        | 2 years             |

| 100°C       | 6 months            |

Table 2-46 • I/O Input Rise Time, Fall Time, and Related I/O Reliability1

| Input Buffer                  | Input Rise/Fall Time (min.) | Input Rise/Fall Time (max.) | Reliability      |

|-------------------------------|-----------------------------|-----------------------------|------------------|

| LVTTL/LVCMOS                  | No requirement              | 10 ns *                     | 20 years (100°C) |

| LVDS/B-LVDS/M-LVDS/<br>LVPECL | No requirement              | 10 ns *                     | 10 years (100°C) |

Note: The maximum input rise/fall time is related to the noise induced into the input buffer trace. If the noise is low, then the rise time and fall time of input buffers can be increased beyond the maximum value. The longer the rise/fall times, the more susceptible the input signal is to the board noise. Microsemi recommends signal integrity evaluation/characterization of the system to ensure that there is no excessive noise coupling into input signals.

Table 2-77 • 3.3 V LVCMOS Wide Range Low Slew – Applies to 1.2 V DC Core Voltage Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case V<sub>CC</sub> = 1.14 V, Worst-Case VCCI = 2.7 Applicable to Standard Banks

| Drive<br>Strength | Equivalent<br>Software<br>Default Drive<br>Strength<br>Option <sup>1</sup> | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|-------------------|----------------------------------------------------------------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 100 μΑ            | 2 mA                                                                       | Std.           | 1.55              | 6.44            | 0.26             | 1.29            | 1.10              | 6.44            | 5.64            | 2.99            | 3.28            | ns    |

| 100 μΑ            | 4 mA                                                                       | Std.           | 1.55              | 6.44            | 0.26             | 1.29            | 1.10              | 6.44            | 5.64            | 2.99            | 3.28            | ns    |

| 100 μΑ            | 6 mA                                                                       | Std.           | 1.55              | 5.41            | 0.26             | 1.29            | 1.10              | 5.41            | 4.91            | 3.35            | 3.89            | ns    |

| 100 μΑ            | 8 mA                                                                       | Std.           | 1.55              | 5.41            | 0.26             | 1.29            | 1.10              | 5.41            | 4.91            | 3.35            | 3.89            | ns    |

- The minimum drive strength for any LVCMOS 3.3 V software configuration when run in wide range is ± 100 μA. Drive strengths

displayed in software are supported for normal range only. For a detailed I/V curve, refer to the IBIS models.

- 2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

Table 2-78 • 3.3 V LVCMOS Wide Range High Slew – Applies to 1.2 V DC Core Voltage

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 2.7

Applicable to Standard Banks

| Drive<br>Strength | Equivalent<br>Software<br>Default Drive<br>Strength<br>Option <sup>1</sup> | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|-------------------|----------------------------------------------------------------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 100 μΑ            | 2 mA                                                                       | Std.           | 1.55              | 3.89            | 0.26             | 1.29            | 1.10              | 3.89            | 3.13            | 2.99            | 3.45            | ns    |

| 100 μΑ            | 4 mA                                                                       | Std.           | 1.55              | 3.89            | 0.26             | 1.29            | 1.10              | 3.89            | 3.13            | 2.99            | 3.45            | ns    |

| 100 μΑ            | 6 mA                                                                       | Std.           | 1.55              | 3.33            | 0.26             | 1.29            | 1.10              | 3.33            | 2.62            | 3.34            | 4.07            | ns    |

| 100 μΑ            | 8 mA                                                                       | Std.           | 1.55              | 3.33            | 0.26             | 1.29            | 1.10              | 3.33            | 2.62            | 3.34            | 4.07            | ns    |

#### Notes:

- 1. The minimum drive strength for any LVCMOS 3.3 V software configuration when run in wide range is  $\pm$  100  $\mu$ A. Drive strengths displayed in software are supported for normal range only. For a detailed I/V curve, refer to the IBIS models.

- 2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

- 3. Software default selection highlighted in gray.

2-54 Revision 27

#### Applies to 1.2 V Core Voltage

Table 2-89 • 2.5 V LVCMOS Low Slew – Applies to 1.2 V DC Core Voltage

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 2.3 V

Applicable to Advanced I/O Banks

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>ZHS</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA           | Std.        | 1.55              | 5.59            | 0.26             | 1.20            | 1.10              | 5.68            | 5.14            | 2.82            | 2.80            | 11.47            | 10.93            | ns    |

| 4 mA           | Std.        | 1.55              | 5.59            | 0.26             | 1.20            | 1.10              | 5.68            | 5.14            | 2.82            | 2.80            | 11.47            | 10.93            | ns    |

| 6 mA           | Std.        | 1.55              | 4.76            | 0.26             | 1.20            | 1.10              | 4.84            | 4.47            | 3.10            | 3.33            | 10.62            | 10.26            | ns    |

| 8 mA           | Std.        | 1.55              | 4.76            | 0.26             | 1.20            | 1.10              | 4.84            | 4.47            | 3.10            | 3.33            | 10.62            | 10.26            | ns    |

| 12 mA          | Std.        | 1.55              | 4.17            | 0.26             | 1.20            | 1.10              | 4.23            | 3.99            | 3.30            | 3.67            | 10.02            | 9.77             | ns    |

| 16 mA          | Std.        | 1.55              | 3.98            | 0.26             | 1.20            | 1.10              | 4.04            | 3.88            | 3.34            | 3.76            | 9.83             | 9.66             | ns    |

| 24 mA          | Std.        | 1.55              | 3.90            | 0.26             | 1.20            | 1.10              | 3.96            | 3.90            | 3.40            | 4.09            | 9.75             | 9.68             | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

Table 2-90 • 2.5 V LVCMOS High Slew – Applies to 1.2 V DC Core Voltage

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 2.3 V

Applicable to Advanced I/O Banks

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>ZHS</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA           | Std.        | 1.55              | 3.33            | 0.26             | 1.20            | 1.10              | 3.38            | 3.09            | 2.82            | 2.91            | 9.17             | 8.88             | ns    |

| 4 mA           | Std.        | 1.55              | 3.33            | 0.26             | 1.20            | 1.10              | 3.38            | 3.09            | 2.82            | 2.91            | 9.17             | 8.88             | ns    |

| 6 mA           | Std.        | 1.55              | 2.89            | 0.26             | 1.20            | 1.10              | 2.93            | 2.56            | 3.10            | 3.45            | 8.72             | 8.34             | ns    |

| 8 mA           | Std.        | 1.55              | 2.89            | 0.26             | 1.20            | 1.10              | 2.93            | 2.56            | 3.10            | 3.45            | 8.72             | 8.34             | ns    |

| 12 mA          | Std.        | 1.55              | 2.64            | 0.26             | 1.20            | 1.10              | 2.67            | 2.29            | 3.30            | 3.79            | 8.46             | 8.08             | ns    |

| 16 mA          | Std.        | 1.55              | 2.59            | 0.26             | 1.20            | 1.10              | 2.63            | 2.24            | 3.34            | 3.88            | 8.41             | 8.03             | ns    |

| 24 mA          | Std.        | 1.55              | 2.60            | 0.26             | 1.20            | 1.10              | 2.64            | 2.18            | 3.40            | 4.22            | 8.42             | 7.97             | ns    |

#### Notes:

- 1. Software default selection highlighted in gray.

- 2. For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

Table 2-91 • 2.5 V LVCMOS Low Slew – Applies to 1.2 V DC Core Voltage

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 2.3 V

Applicable to Standard Plus Banks

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>ZHS</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA           | Std.        | 1.55              | 5.02            | 0.26             | 1.19            | 1.10              | 5.11            | 4.60            | 2.50            | 2.62            | 10.89            | 10.38            | ns    |

| 4 mA           | Std.        | 1.55              | 5.02            | 0.26             | 1.19            | 1.10              | 5.11            | 4.60            | 2.50            | 2.62            | 10.89            | 10.38            | ns    |

| 6 mA           | Std.        | 1.55              | 4.21            | 0.26             | 1.19            | 1.10              | 4.27            | 4.00            | 2.76            | 3.10            | 10.06            | 9.79             | ns    |

| 8 mA           | Std.        | 1.55              | 4.21            | 0.26             | 1.19            | 1.10              | 4.27            | 4.00            | 2.76            | 3.10            | 10.06            | 9.79             | ns    |

| 12 mA          | Std.        | 1.55              | 3.66            | 0.26             | 1.19            | 1.10              | 3.71            | 3.55            | 2.94            | 3.41            | 9.50             | 9.34             | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

## 1.2 V LVCMOS (JESD8-12A)

Low-Voltage CMOS for 1.2 V complies with the LVCMOS standard JESD8-12A for general purpose 1.2 V applications. It uses a 1.2 V input buffer and a push-pull output buffer. Furthermore, all LVCMOS 1.2 V software macros comply with LVCMOS 1.2 V wide range as specified in the JESD8-12A specification.

Table 2-127 • Minimum and Maximum DC Input and Output Levels

Applicable to Advanced I/O Banks

| 1.2 V<br>LVCMOS   |           | VIL         | VIH         |           | VOL         | VOH         | IOL | ЮН | IOSH                    | IOSL                    | IIL <sup>1</sup>        | IIH <sup>2</sup>        |

|-------------------|-----------|-------------|-------------|-----------|-------------|-------------|-----|----|-------------------------|-------------------------|-------------------------|-------------------------|

| Drive<br>Strength | Min.<br>V | Max.<br>V   | Min.<br>V   | Max.<br>V | Max.<br>V   | Min.<br>V   | mA  | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μ <b>Α</b> <sup>4</sup> | μ <b>Α</b> <sup>4</sup> |

| 2 mA              | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 1.26      | 0.25 * VCCI | 0.75 * VCCI | 2   | 2  | 20                      | 26                      | 10                      | 10                      |

#### Notes:

- 1. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

- 2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges

- 3. Currents are measured at 100°C junction temperature and maximum voltage.

- 4. Currents are measured at 85°C junction temperature.

- 5. Software default selection highlighted in gray.

Table 2-128 • Minimum and Maximum DC Input and Output Levels

Applicable to Standard Plus I/O Banks

| 1.2 V<br>LVCMOS   |           | VIL         | VIH         |           | VOL         | VOH         | I <sub>OL</sub> | ЮН | IOSH                    | IOSL                    | IIL <sup>1</sup>        | IIH <sup>2</sup>        |

|-------------------|-----------|-------------|-------------|-----------|-------------|-------------|-----------------|----|-------------------------|-------------------------|-------------------------|-------------------------|

| Drive<br>Strength | Min.<br>V | Max.<br>V   | Min.<br>V   | Max.<br>V | Max.<br>V   | Min.<br>V   | mA              | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μ <b>Α</b> <sup>4</sup> | μ <b>Α</b> <sup>4</sup> |

| 2 mA              | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 1.26      | 0.25 * VCCI | 0.75 * VCCI | 2               | 2  | 20                      | 26                      | 10                      | 10                      |

#### Notes:

- 1. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

- 2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges

- 3. Currents are measured at 100°C junction temperature and maximum voltage.

- 4. Currents are measured at 85°C junction temperature.

- 5. Software default selection highlighted in gray.

Table 2-129 • Minimum and Maximum DC Input and Output Levels

Applicable to Standard I/O Banks

| 1.2 V<br>LVCMOS   |           | VIL         | VIH         |           | VOL         | VOH         | IOL | ЮН | IOSH                    | IOSL                    | IIL <sup>1</sup>        | IIH <sup>2</sup> |

|-------------------|-----------|-------------|-------------|-----------|-------------|-------------|-----|----|-------------------------|-------------------------|-------------------------|------------------|

| Drive<br>Strength | Min.<br>V | Max.<br>V   | Min.<br>V   | Max.<br>V | Max.<br>V   | Min.<br>V   | mA  | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μ <b>Α</b> <sup>4</sup> | μA <sup>4</sup>  |

| 1 mA              | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 3.6       | 0.25 * VCCI | 0.75 * VCCI | 1   | 1  | 20                      | 26                      | 10                      | 10               |

#### Notes:

- 1. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

- 2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges

- 3. Currents are measured at 100°C junction temperature and maximum voltage.

- 4. Currents are measured at 85°C junction temperature.

- 5. Software default selection highlighted in gray.

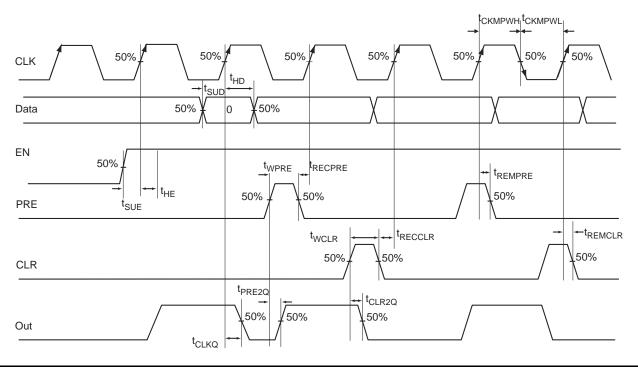

Figure 2-28 • Timing Model and Waveforms

## Timing Characteristics 1.5 V DC Core Voltage

Table 2-171 • Register Delays Commercial-Case Conditions:  $T_J = 70^{\circ}\text{C}$ , Worst-Case VCC = 1.425 V

| Parameter           | Description                                                   | Std. | Units |

|---------------------|---------------------------------------------------------------|------|-------|

| t <sub>CLKQ</sub>   | Clock-to-Q of the Core Register                               | 0.89 | ns    |

| t <sub>SUD</sub>    | Data Setup Time for the Core Register                         | 0.81 | ns    |

| t <sub>HD</sub>     | Data Hold Time for the Core Register                          | 0.00 | ns    |

| t <sub>SUE</sub>    | Enable Setup Time for the Core Register                       | 0.73 | ns    |

| t <sub>HE</sub>     | Enable Hold Time for the Core Register                        | 0.00 | ns    |

| t <sub>CLR2Q</sub>  | Asynchronous Clear-to-Q of the Core Register                  | 0.60 | ns    |

| t <sub>PRE2Q</sub>  | Asynchronous Preset-to-Q of the Core Register                 | 0.62 | ns    |

| t <sub>REMCLR</sub> | Asynchronous Clear Removal Time for the Core Register         | 0.00 | ns    |

| t <sub>RECCLR</sub> | Asynchronous Clear Recovery Time for the Core Register        | 0.24 | ns    |

| t <sub>REMPRE</sub> | Asynchronous Preset Removal Time for the Core Register        | 0.00 | ns    |

| t <sub>RECPRE</sub> | Asynchronous Preset Recovery Time for the Core Register       | 0.23 | ns    |

| t <sub>WCLR</sub>   | Asynchronous Clear Minimum Pulse Width for the Core Register  | 0.30 | ns    |

| t <sub>WPRE</sub>   | Asynchronous Preset Minimum Pulse Width for the Core Register | 0.30 | ns    |

| t <sub>CKMPWH</sub> | Clock Minimum Pulse Width High for the Core Register          | 0.56 | ns    |

| t <sub>CKMPWL</sub> | Clock Minimum Pulse Width Low for the Core Register           | 0.56 | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

Table 2-179 • AGL600 Global Resource

Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.425 V

|                      |                                           |                   | Std.              |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 1.48              | 1.82              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 1.52              | 1.94              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | 1.18              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  | 1.15              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.42              | ns    |

#### Notes:

- Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

- 2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

- 3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

Table 2-180 • AGL1000 Global Resource

Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.425 V

|                      |                                           | Std.              |                   |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 1.55              | 1.89              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 1.60              | 2.02              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | 1.18              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  | 1.15              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.42              | ns    |

#### Notes:

- 1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

- 2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

- 3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

## Timing Characteristics 1.5 V DC Core Voltage

Table 2-195 • FIFO Worst Commercial-Case Conditions:  $T_J = 70$  °C, VCC = 1.425 V

| Parameter            | Description                                       | Std.  | Units |

|----------------------|---------------------------------------------------|-------|-------|

| t <sub>ENS</sub>     | REN, WEN Setup Time                               | 1.99  | ns    |

| t <sub>ENH</sub>     | REN, WEN Hold Time                                | 0.16  | ns    |

| t <sub>BKS</sub>     | BLK Setup Time                                    | 0.30  | ns    |

| t <sub>BKH</sub>     | BLK Hold Time                                     | 0.00  | ns    |

| t <sub>DS</sub>      | Input Data (WD) Setup Time                        | 0.76  | ns    |

| t <sub>DH</sub>      | Input Data (WD) Hold Time                         | 0.25  | ns    |

| t <sub>CKQ1</sub>    | Clock High to New Data Valid on RD (flow-through) | 3.33  | ns    |

| t <sub>CKQ2</sub>    | Clock High to New Data Valid on RD (pipelined)    | 1.80  | ns    |

| t <sub>RCKEF</sub>   | RCLK High to Empty Flag Valid                     | 3.53  | ns    |

| t <sub>WCKFF</sub>   | WCLK High to Full Flag Valid                      | 3.35  | ns    |

| t <sub>CKAF</sub>    | Clock High to Almost Empty/Full Flag Valid        | 12.85 | ns    |

| t <sub>RSTFG</sub>   | RESET Low to Empty/Full Flag Valid                | 3.48  | ns    |

| t <sub>RSTAF</sub>   | RESET Low to Almost Empty/Full Flag Valid         | 12.72 | ns    |

| t <sub>RSTBQ</sub>   | RESET Low to Data Out Low on RD (flow-through)    | 2.02  | ns    |

|                      | RESET Low to Data Out Low on RD (pipelined)       | 2.02  | ns    |

| t <sub>REMRSTB</sub> | RESET Removal                                     | 0.61  | ns    |

| t <sub>RECRSTB</sub> | RESET Recovery                                    | 3.21  | ns    |

| t <sub>MPWRSTB</sub> | RESET Minimum Pulse Width                         | 0.68  | ns    |

| t <sub>CYC</sub>     | Clock Cycle Time                                  | 6.24  | ns    |

| F <sub>MAX</sub>     | Maximum Frequency for FIFO                        | 160   | MHz   |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

The Flash\*Freeze pin can be used with any single-ended I/O standard supported by the I/O bank in which the pin is located, and input signal levels compatible with the I/O standard selected. The FF pin should be treated as a sensitive asynchronous signal. When defining pin placement and board layout, simultaneously switching outputs (SSOs) and their effects on sensitive asynchronous pins must be considered.

Unused FF or I/O pins are tristated with weak pull-up. This default configuration applies to both Flash\*Freeze mode and normal operation mode. No user intervention is required.

Table 3-1 shows the Flash\*Freeze pin location on the available packages for IGLOO a devices. The Flash\*Freeze pin location is independent of device, allowing migration to larger or smaller IGLOO devices while maintaining the same pin location on the board. Refer to the "Flash\*Freeze Technology and Low Power Modes" chapter of the *IGLOO FPGA Fabric User Guide* for more information on I/O states during Flash\*Freeze mode.

Table 3-1 • Flash\*Freeze Pin Location in IGLOO Family Packages (device-independent)

| IGLOO Packages | Flash*Freeze Pin |

|----------------|------------------|

| CS81/UC81      | H2               |

| CS121          | J5               |

| CS196          | P3               |

| CS281          | W2               |

| QN48           | 14               |

| QN68           | 18               |

| QN132          | B12              |

| VQ100          | 27               |

| FG144          | L3               |

| FG256          | Т3               |

| FG484          | W6               |

3-3 Revision 27

Package Pin Assignments

| CS196      |                 | CS196      |                 |  |

|------------|-----------------|------------|-----------------|--|

| Pin Number | AGL125 Function | Pin Number | AGL125 Function |  |

| A1         | GND             | C9         | IO23RSB0        |  |

| A2         | GAA0/IO00RSB0   | C10        | IO29RSB0        |  |

| А3         | GAC0/IO04RSB0   | C11        | VCCIB0          |  |

| A4         | GAC1/IO05RSB0   | C12        | IO42RSB0        |  |

| A5         | IO09RSB0        | C13        | GNDQ            |  |

| A6         | IO15RSB0        | C14        | IO44RSB0        |  |

| A7         | IO18RSB0        | D1         | IO127RSB1       |  |

| A8         | IO22RSB0        | D2         | IO129RSB1       |  |

| A9         | IO27RSB0        | D3         | GAA2/IO132RSB1  |  |

| A10        | GBC0/IO35RSB0   | D4         | IO126RSB1       |  |

| A11        | GBB0/IO37RSB0   | D5         | IO06RSB0        |  |

| A12        | GBB1/IO38RSB0   | D6         | IO13RSB0        |  |

| A13        | GBA1/IO40RSB0   | D7         | IO19RSB0        |  |

| A14        | GND             | D8         | IO21RSB0        |  |

| B1         | VCCIB1          | D9         | IO26RSB0        |  |

| B2         | VMV0            | D10        | IO31RSB0        |  |

| В3         | GAA1/IO01RSB0   | D11        | IO30RSB0        |  |

| B4         | GAB1/IO03RSB0   | D12        | VMV0            |  |

| B5         | GND             | D13        | IO46RSB0        |  |

| B6         | IO16RSB0        | D14        | GBC2/IO45RSB0   |  |

| B7         | IO20RSB0        | E1         | IO125RSB1       |  |

| B8         | IO24RSB0        | E2         | GND             |  |

| B9         | IO28RSB0        | E3         | IO131RSB1       |  |

| B10        | GND             | E4         | VCCIB1          |  |

| B11        | GBC1/IO36RSB0   | E5         | NC              |  |

| B12        | GBA0/IO39RSB0   | E6         | IO08RSB0        |  |

| B13        | GBA2/IO41RSB0   | E7         | IO17RSB0        |  |

| B14        | GBB2/IO43RSB0   | E8         | IO12RSB0        |  |

| C1         | GAC2/IO128RSB1  | E9         | IO11RSB0        |  |

| C2         | GAB2/IO130RSB1  | E10        | NC              |  |

| C3         | GNDQ            | E11        | VCCIB0          |  |

| C4         | VCCIB0          | E12        | IO32RSB0        |  |

| C5         | GAB0/IO02RSB0   | E13        | GND             |  |

| C6         | IO14RSB0        | E14        | IO34RSB0        |  |

| C7         | VCCIB0          | F1         | IO124RSB1       |  |

| C8         | NC              | F2         | IO114RSB1       |  |

| CS196      |                 |  |

|------------|-----------------|--|

| Pin Number | AGL125 Function |  |

| F3         | IO113RSB1       |  |

| F4         | IO112RSB1       |  |

| F5         | IO111RSB1       |  |

| F6         | NC              |  |

| F7         | VCC             |  |

| F8         | VCC             |  |

| F9         | NC              |  |

| F10        | IO07RSB0        |  |

| F11        | IO25RSB0        |  |

| F12        | IO10RSB0        |  |

| F13        | IO33RSB0        |  |

| F14        | IO47RSB0        |  |

| G1         | GFB1/IO121RSB1  |  |

| G2         | GFA0/IO119RSB1  |  |

| G3         | GFA2/IO117RSB1  |  |

| G4         | VCOMPLF         |  |

| G5         | GFC0/IO122RSB1  |  |

| G6         | VCC             |  |

| <b>G</b> 7 | GND             |  |

| G8         | GND             |  |

| G9         | VCC             |  |

| G10        | GCC0/IO52RSB0   |  |

| G11        | GCB1/IO53RSB0   |  |

| G12        | GCA0/IO56RSB0   |  |

| G13        | IO48RSB0        |  |

| G14        | GCC2/IO59RSB0   |  |

| H1         | GFB0/IO120RSB1  |  |

| H2         | GFA1/IO118RSB1  |  |

| H3         | VCCPLF          |  |

| H4         | GFB2/IO116RSB1  |  |

| H5         | GFC1/IO123RSB1  |  |

| H6         | VCC             |  |

| H7         | GND             |  |

| H8         | GND             |  |

| H9         | VCC             |  |

| H10        | GCC1/IO51RSB0   |  |

4-10 Revision 27

## Package Pin Assignments

| FG484      |                   |  |

|------------|-------------------|--|

| Pin Number | AGL400 Function   |  |

| V15        | IO85RSB2          |  |

| V16        | GDB2/IO81RSB2     |  |

| V17        | TDI               |  |

| V18        | NC                |  |

| V19        | TDO               |  |

| V20        | GND               |  |

| V21        | NC                |  |

| V22        | NC                |  |

| W1         | NC                |  |

| W2         | NC                |  |

| W3         | NC                |  |

| W4         | GND               |  |

| W5         | IO126RSB2         |  |

| W6         | FF/GEB2/IO133RSB2 |  |

| W7         | IO124RSB2         |  |

| W8         | IO116RSB2         |  |

| W9         | IO113RSB2         |  |

| W10        | IO107RSB2         |  |

| W11        | IO105RSB2         |  |

| W12        | IO102RSB2         |  |

| W13        | IO97RSB2          |  |

| W14        | IO92RSB2          |  |

| W15        | GDC2/IO82RSB2     |  |

| W16        | IO86RSB2          |  |

| W17        | GDA2/IO80RSB2     |  |

| W18        | TMS               |  |

| W19        | GND               |  |

| W20        | NC                |  |

| W21        | NC                |  |

| W22        | NC                |  |

| Y1         | VCCIB3            |  |

| Y2         | NC                |  |

| Y3         | NC                |  |

| Y4         | NC                |  |

| Y5         | GND               |  |

| Y6         | NC                |  |

4-76 Revision 27

| FG484                         |                |  |

|-------------------------------|----------------|--|

| Pin Number   AGL1000 Function |                |  |

| G5                            | IO222PDB3      |  |

| G6                            | GAC2/IO223PDB3 |  |

| G7                            | IO223NDB3      |  |

| G8                            | GNDQ           |  |

| G9                            | IO23RSB0       |  |

| G10                           | IO29RSB0       |  |

| G11                           | IO33RSB0       |  |

| G12                           | IO46RSB0       |  |

| G13                           | IO52RSB0       |  |

| G14                           | IO60RSB0       |  |

| G15                           | GNDQ           |  |

| G16                           | IO80NDB1       |  |

| G17                           | GBB2/IO79PDB1  |  |

| G18                           | IO79NDB1       |  |

| G19                           | IO82NPB1       |  |

| G20                           | IO85PDB1       |  |

| G21                           | IO85NDB1       |  |

| G22                           | NC             |  |

| H1                            | NC             |  |

| H2                            | NC             |  |

| H3                            | VCC            |  |

| H4                            | IO217PDB3      |  |

| H5                            | IO218PDB3      |  |

| H6                            | IO221NDB3      |  |

| H7                            | IO221PDB3      |  |

| H8                            | VMV0           |  |

| H9                            | VCCIB0         |  |

| H10                           | VCCIB0         |  |

| H11                           | IO38RSB0       |  |

| H12                           | IO47RSB0       |  |

| H13                           | VCCIB0         |  |

| H14                           | VCCIB0         |  |

| H15                           | VMV1           |  |

| H16                           | GBC2/IO80PDB1  |  |

| H17                           | IO83PPB1       |  |

| H18                           | IO86PPB1       |  |

| FG484      |                  |  |

|------------|------------------|--|

| Pin Number | AGL1000 Function |  |

| U1         | IO195PDB3        |  |

| U2         | IO195NDB3        |  |

| U3         | IO194NPB3        |  |

| U4         | GEB1/IO189PDB3   |  |

| U5         | GEB0/IO189NDB3   |  |

| U6         | VMV2             |  |

| U7         | IO179RSB2        |  |

| U8         | IO171RSB2        |  |

| U9         | IO165RSB2        |  |

| U10        | IO159RSB2        |  |

| U11        | IO151RSB2        |  |

| U12        | IO137RSB2        |  |

| U13        | IO134RSB2        |  |

| U14        | IO128RSB2        |  |

| U15        | VMV1             |  |

| U16        | TCK              |  |

| U17        | VPUMP            |  |

| U18        | TRST             |  |

| U19        | GDA0/IO113NDB1   |  |

| U20        | NC               |  |

| U21        | IO108NDB1        |  |

| U22        | IO109PDB1        |  |

| V1         | NC               |  |

| V2         | NC               |  |

| V3         | GND              |  |

| V4         | GEA1/IO188PDB3   |  |

| V5         | GEA0/IO188NDB3   |  |

| V6         | IO184RSB2        |  |

| V7         | GEC2/IO185RSB2   |  |

| V8         | IO168RSB2        |  |

| V9         | IO163RSB2        |  |

| V10        | IO157RSB2        |  |

| V11        | IO149RSB2        |  |

| V12        | IO143RSB2        |  |

| V13        | IO138RSB2        |  |

| V14        | IO131RSB2        |  |