Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                 |

|--------------------------------|-----------------------------------------------------------------|

| Product Status                 | Obsolete                                                        |

| Number of LABs/CLBs            | -                                                               |

| Number of Logic Elements/Cells | 13824                                                           |

| Total RAM Bits                 | 110592                                                          |

| Number of I/O                  | 97                                                              |

| Number of Gates                | 600000                                                          |

| Voltage - Supply               | 1.14V ~ 1.575V                                                  |

| Mounting Type                  | Surface Mount                                                   |

| Operating Temperature          | 0°C ~ 70°C (TA)                                                 |

| Package / Case                 | 144-LBGA                                                        |

| Supplier Device Package        | 144-FPBGA (13x13)                                               |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microsemi/agl600v2-fgg144t |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Temperature Grade Offerings**

|                    | AGL015 <sup>1</sup> | AGL030 | AGL060            | AGL125 | AGL250   | AGL400 | AGL600   | AGL1000   |

|--------------------|---------------------|--------|-------------------|--------|----------|--------|----------|-----------|

| Package            |                     |        |                   |        | M1AGL250 |        | M1AGL600 | M1AGL1000 |

| QN48               | _                   | C, I   | _                 | _      | _        | -      | _        | _         |

| QN68               | C, I                | -      | -                 | -      | -        | _      | -        | _         |

| UC81               | _                   | C, I   | -                 | -      | -        | _      | -        | _         |

| CS81               | _                   | C, I   | -                 | -      | -        | _      | -        | _         |

| CS121              | _                   | -      | C, I              | C, I   | -        | _      | -        | _         |

| VQ100              | _                   | C, I   | C, I              | C, I   | C, I     | _      | -        | _         |

| QN132 <sup>2</sup> | _                   | C, I   | C, I <sup>2</sup> | C, I   | _        | _      | _        | _         |

| CS196              | _                   | -      | -                 | C, I   | C, I     | C, I   | -        | _         |

| FG144              | _                   | -      | -                 | C, I   | C, I     | C, I   | C, I     | C, I      |

| FG256              | _                   | _      | _                 | _      | _        | C, I   | C, I     | C, I      |

| CS281              | _                   | _      | _                 | _      | _        | -      | C, I     | C, I      |

| FG484              | -                   | _      | _                 | -      | -        | C, I   | C, I     | C, I      |

#### Notes:

# **IGLOO Device Status**

| IGLOO Devices | Status                           | M1 IGLOO Devices | Status     |

|---------------|----------------------------------|------------------|------------|

| AGL015        | Not recommended for new designs. |                  |            |

| AGL030        | Production                       |                  |            |

| AGL060        | Production                       |                  |            |

| AGL125        | Production                       |                  |            |

| AGL250        | Production                       | M1AGL250         | Production |

| AGL400        | Production                       |                  |            |

| AGL600        | Production                       | M1AGL600         | Production |

| AGL1000       | Production                       | M1AGL1000        | Production |

References made to IGLOO devices also apply to ARM-enabled IGLOOe devices. The ARM-enabled part numbers start with M1 (Cortex-M1).

Contact your local Microsemi SoC Products Group representative for device availability: www.microsemi.com/soc/contact/default.aspx.

## AGL015 and AGL030

The AGL015 and AGL030 are architecturally compatible; there are no RAM or PLL features.

# **Devices Not Recommended For New Designs**

AGL015 is not recommended for new designs.

IV Revision 27

<sup>1.</sup> AGL015 is not recommended for new designs.

<sup>2.</sup> Package not available.

C = Commercial temperature range: 0°C to 85°C junction temperature.

I = Industrial temperature range: -40°C to 100°C junction temperature.

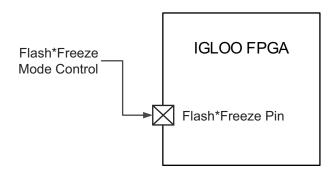

## Flash\*Freeze Technology

The IGLOO device has an ultra-low power static mode, called Flash\*Freeze mode, which retains all SRAM and register information and can still quickly return to normal operation. Flash\*Freeze technology enables the user to quickly (within 1 µs) enter and exit Flash\*Freeze mode by activating the Flash\*Freeze pin while all power supplies are kept at their original values. In addition, I/Os and global I/Os can still be driven and can be toggling without impact on power consumption, clocks can still be driven or can be toggling without impact on power consumption, and the device retains all core registers, SRAM information, and states. I/O states are tristated during Flash\*Freeze mode or can be set to a certain state using weak pull-up or pull-down I/O attribute configuration. No power is consumed by the I/O banks, clocks, JTAG pins, or PLL, and the device consumes as little as 5 µW in this mode.

Flash\*Freeze technology allows the user to switch to active mode on demand, thus simplifying the power management of the device.

The Flash\*Freeze pin (active low) can be routed internally to the core to allow the user's logic to decide when it is safe to transition to this mode. It is also possible to use the Flash\*Freeze pin as a regular I/O if Flash\*Freeze mode usage is not planned, which is advantageous because of the inherent low power static (as low as 12 µW) and dynamic capabilities of the IGLOO device. Refer to Figure 1-3 for an illustration of entering/exiting Flash\*Freeze mode.

Figure 1-3 • IGLOO Flash\*Freeze Mode

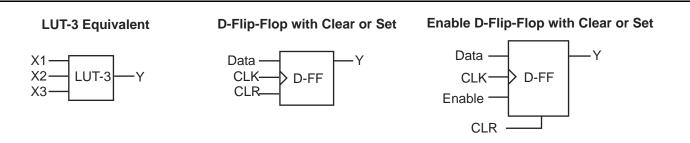

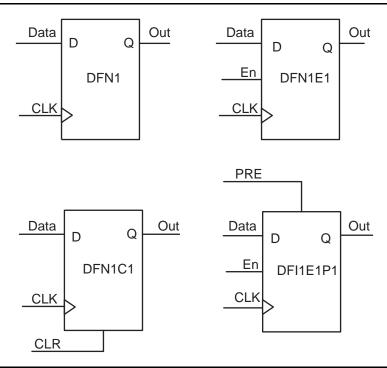

#### VersaTiles

The IGLOO core consists of VersaTiles, which have been enhanced beyond the ProASIC PLUS® core tiles. The IGLOO VersaTile supports the following:

- All 3-input logic functions—LUT-3 equivalent

- · Latch with clear or set

- · D-flip-flop with clear or set

- Enable D-flip-flop with clear or set

Refer to Figure 1-4 for VersaTile configurations.

Figure 1-4 • VersaTile Configurations

1-5 Revision 27

Table 2-15 • Summary of I/O Input Buffer Power (per pin) – Default I/O Software Settings Applicable to Standard I/O Banks

|                                      | VCCI (V) | Static Power<br>PDC6 (mW) <sup>1</sup> | Dynamic Power<br>PAC9 (μW/MHz) <sup>2</sup> |

|--------------------------------------|----------|----------------------------------------|---------------------------------------------|

| Single-Ended                         |          |                                        |                                             |

| 3.3 V LVTTL / 3.3 V LVCMOS           | 3.3      | _                                      | 17.24                                       |

| 3.3 V LVCMOS Wide Range <sup>3</sup> | 3.3      | -                                      | 17.24                                       |

| 2.5 V LVCMOS                         | 2.5      | _                                      | 5.64                                        |

| 1.8 V LVCMOS                         | 1.8      | -                                      | 2.63                                        |

| 1.5 V LVCMOS (JESD8-11)              | 1.5      | _                                      | 1.97                                        |

| 1.2 V LVCMOS <sup>4</sup>            | 1.2      | _                                      | 0.57                                        |

| 1.2 V LVCMOS Wide Range <sup>4</sup> | 1.2      | -                                      | 0.57                                        |

#### Notes:

- 1. PDC6 is the static power (where applicable) measured on VCCI.

- 2. PAC9 is the total dynamic power measured on VCCI.

- 3. All LVCMOS 3.3 V software macros support LVCMOS 3.3 V wide range as specified in the JESD-8B specification.

- 4. Applicable for IGLOO V2 devices only.

Table 2-16 • Summary of I/O Output Buffer Power (per pin) – Default I/O Software Settings<sup>1</sup>

Applicable to Advanced I/O Banks

| C <sub>LOAD</sub> (pF) | VCCI (V)                             | Static Power PDC7 (mW) <sup>2</sup>                           | Dynamic Power<br>PAC10 (μW/MHz) <sup>3</sup>                                                                                                                                                                                                                                                                                                                          |

|------------------------|--------------------------------------|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                        |                                      |                                                               |                                                                                                                                                                                                                                                                                                                                                                       |

| 5                      | 3.3                                  | -                                                             | 136.95                                                                                                                                                                                                                                                                                                                                                                |

| 5                      | 3.3                                  | -                                                             | 136.95                                                                                                                                                                                                                                                                                                                                                                |

| 5                      | 2.5                                  | _                                                             | 76.84                                                                                                                                                                                                                                                                                                                                                                 |

| 5                      | 1.8                                  | -                                                             | 49.31                                                                                                                                                                                                                                                                                                                                                                 |

| 5                      | 1.5                                  | -                                                             | 33.36                                                                                                                                                                                                                                                                                                                                                                 |

| 5                      | 1.2                                  | _                                                             | 16.24                                                                                                                                                                                                                                                                                                                                                                 |

| 5                      | 1.2                                  | -                                                             | 16.24                                                                                                                                                                                                                                                                                                                                                                 |

| 10                     | 3.3                                  | -                                                             | 194.05                                                                                                                                                                                                                                                                                                                                                                |

| 10                     | 3.3                                  | _                                                             | 194.05                                                                                                                                                                                                                                                                                                                                                                |

| •                      |                                      |                                                               |                                                                                                                                                                                                                                                                                                                                                                       |

| -                      | 2.5                                  | 7.74                                                          | 156.22                                                                                                                                                                                                                                                                                                                                                                |

| -                      | 3.3                                  | 19.54                                                         | 339.35                                                                                                                                                                                                                                                                                                                                                                |

|                        | 5<br>5<br>5<br>5<br>5<br>5<br>5<br>5 | 5 3.3<br>5 2.5<br>5 1.8<br>5 1.5<br>5 1.2<br>10 3.3<br>10 3.3 | CLOAD (pF)         VCCI (V)         PDC7 (mW)²           5         3.3         -           5         2.5         -           5         1.8         -           5         1.5         -           5         1.2         -           5         1.2         -           10         3.3         -           10         3.3         -           -         2.5         7.74 |

#### Notes:

- 1. Dynamic power consumption is given for standard load and software default drive strength and output slew.

- 2. PDC7 is the static power (where applicable) measured on VCCI.

- 3. PAC10 is the total dynamic power measured on VCCI.

- 4. All LVCMOS 3.3 V software macros support LVCMOS 3.3 V wide range as specified in the JESD-8B specification.

- 5. Applicable for IGLOO V2 devices only.

2-10 Revision 27

Table 2-33 • Summary of I/O Timing Characteristics—Software Default Settings, Std. Speed Grade, Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI (per standard)

Applicable to Standard I/O Banks

| I/O Standard                                  | Drive Strength) | Equivalent Software Default<br>Drive Strength Option <sup>1</sup> (mA) | Slew Rate | Capacitive Load (pF) | External Resistor (᠒) | t <sub>DOUT</sub> (ns) | t <sub>DP</sub> (ns) | t <sub>DIN</sub> (ns) | t <sub>PY</sub> (ns) | t <sub>EOUT</sub> (ns) | t <sub>ZL</sub> (ns) | t <sub>ZH</sub> (ns) | t <sub>LZ</sub> (ns) | t <sub>HZ</sub> (ns) | Units |

|-----------------------------------------------|-----------------|------------------------------------------------------------------------|-----------|----------------------|-----------------------|------------------------|----------------------|-----------------------|----------------------|------------------------|----------------------|----------------------|----------------------|----------------------|-------|

| 3.3 V<br>LVTTL /<br>3.3 V<br>LVCMOS           | 8 mA            | 8                                                                      | High      | 5                    | _                     | 0.97                   | 1.85                 | 0.18                  | 0.83                 | 0.66                   | 1.89                 | 1.46                 | 1.96                 | 2.26                 | ns    |

| 3.3 V<br>LVCMOS<br>Wide<br>Range <sup>2</sup> | 100 μΑ          | 8                                                                      | High      | 5                    | _                     | 0.97                   | 2.62                 | 0.18                  | 1.17                 | 0.66                   | 2.63                 | 2.02                 | 2.79                 | 3.17                 | ns    |

| 2.5 V<br>LVCMOS                               | 8 mA            | 8                                                                      | High      | 5                    | _                     | 0.97                   | 1.88                 | 0.18                  | 1.04                 | 0.66                   | 1.92                 | 1.63                 | 1.95                 | 2.15                 | ns    |

| 1.8 V<br>LVCMOS                               | 4 mA            | 4                                                                      | High      | 5                    | _                     | 0.97                   | 2.18                 | 0.18                  | 0.98                 | 0.66                   | 2.22                 | 1.93                 | 1.97                 | 2.06                 | ns    |

| 1.5 V<br>LVCMOS                               | 2 mA            | 2                                                                      | High      | 5                    | -                     | 0.97                   | 2.51                 | 0.18                  | 1.14                 | 0.66                   | 2.56                 | 2.21                 | 1.99                 | 2.03                 | ns    |

#### Notes:

2-30 Revision 27

The minimum drive strength for any LVCMOS 3.3 V software configuration when run in wide range is ±100 μA. Drive strength displayed in the software is supported for normal range only. For a detailed I/V curve, refer to the IBIS models.

<sup>2.</sup> All LVCMOS 3.3 V software macros support LVCMOS 3.3 V wide range as specified in the JESD-8B specification.

<sup>3.</sup> For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

Table 2-43 • I/O Short Currents IOSH/IOSL Applicable to Standard Plus I/O Banks

|                            | Drive Strength              | IOSL (mA)*                   | IOSH (mA)*                   |

|----------------------------|-----------------------------|------------------------------|------------------------------|

| 3.3 V LVTTL / 3.3 V LVCMOS | 2 mA                        | 25                           | 27                           |

|                            | 4 mA                        | 25                           | 27                           |

|                            | 6 mA                        | 51                           | 54                           |

|                            | 8 mA                        | 51                           | 54                           |

|                            | 12 mA                       | 103                          | 109                          |

|                            | 16 mA                       | 103                          | 109                          |

| 3.3 V LVCMOS Wide Range    | 100 μΑ                      | Same as regular 3.3 V LVCMOS | Same as regular 3.3 V LVCMOS |

| 2.5 V LVCMOS               | 2 mA                        | 16                           | 18                           |

|                            | 4 mA                        | 16                           | 18                           |

|                            | 6 mA                        | 32                           | 37                           |

|                            | 8 mA                        | 32                           | 37                           |

|                            | 12 mA                       | 65                           | 74                           |

| 1.8 V LVCMOS               | 2 mA                        | 9                            | 11                           |

|                            | 4 mA                        | 17                           | 22                           |

|                            | 6 mA                        | 35                           | 44                           |

|                            | 8 mA                        | 35                           | 44                           |

| 1.5 V LVCMOS               | 2 mA                        | 13                           | 16                           |

|                            | 4 mA                        | 25                           | 33                           |

| 1.2 V LVCMOS               | 2 mA                        | 20                           | 26                           |

| 1.2 V LVCMOS Wide Range    | 100 μΑ                      | 20                           | 26                           |

| 3.3 V PCI/PCI-X            | Per PCI/PCI-X specification | 103                          | 109                          |

Note:  ${}^*T_J = 100^{\circ}C$

2-38 Revision 27

## Single-Ended I/O Characteristics

## 3.3 V LVTTL / 3.3 V LVCMOS

Low-Voltage Transistor–Transistor Logic (LVTTL) is a general-purpose standard (EIA/JESD) for 3.3 V applications. It uses an LVTTL input buffer and push-pull output buffer. Furthermore, all LVCMOS 3.3 V software macros comply with LVCMOS 3.3 V wide range as specified in the JESD8a specification.

Table 2-47 • Minimum and Maximum DC Input and Output Levels

Applicable to Advanced I/O Banks

| 3.3 V LVTTL /<br>3.3 V LVCMOS | v         | TL.       | v         | TH .      | VOL       | VOH       | IOL | ЮН | IOSL                    | IOSH                    | IIL <sup>1</sup>        | IIH <sup>2</sup> |

|-------------------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----|----|-------------------------|-------------------------|-------------------------|------------------|

| Drive<br>Strength             | Min.<br>V | Max.<br>V | Min.<br>V | Max.<br>V | Max.<br>V | Min.<br>V | mA  | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μ <b>Α</b> <sup>4</sup> | μA <sup>4</sup>  |

| 2 mA                          | -0.3      | 0.8       | 2         | 3.6       | 0.4       | 2.4       | 2   | 2  | 25                      | 27                      | 10                      | 10               |

| 4 mA                          | -0.3      | 0.8       | 2         | 3.6       | 0.4       | 2.4       | 4   | 4  | 25                      | 27                      | 10                      | 10               |

| 6 mA                          | -0.3      | 0.8       | 2         | 3.6       | 0.4       | 2.4       | 6   | 6  | 51                      | 54                      | 10                      | 10               |

| 8 mA                          | -0.3      | 0.8       | 2         | 3.6       | 0.4       | 2.4       | 8   | 8  | 51                      | 54                      | 10                      | 10               |

| 12 mA                         | -0.3      | 0.8       | 2         | 3.6       | 0.4       | 2.4       | 12  | 12 | 103                     | 109                     | 10                      | 10               |

| 16 mA                         | -0.3      | 0.8       | 2         | 3.6       | 0.4       | 2.4       | 16  | 16 | 132                     | 127                     | 10                      | 10               |

| 24 mA                         | -0.3      | 0.8       | 2         | 3.6       | 0.4       | 2.4       | 24  | 24 | 268                     | 181                     | 10                      | 10               |

#### Notes:

- 1. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

- 2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

- 3. Currents are measured at 100°C junction temperature and maximum voltage.

- 4. Currents are measured at 85°C junction temperature.

- 5. Software default selection highlighted in gray.

Table 2-48 • Minimum and Maximum DC Input and Output Levels

Applicable to Standard Plus I/O Banks

| 3.3 V LVTTL /<br>3.3 V LVCMOS | v         | TL.       | V         | IH        | V <sub>OL</sub> | VOH       | IOL | ЮН | IOSL                    | IOSH                    | IIL <sup>1</sup>        | IIH <sup>2</sup>        |

|-------------------------------|-----------|-----------|-----------|-----------|-----------------|-----------|-----|----|-------------------------|-------------------------|-------------------------|-------------------------|

| Drive<br>Strength             | Min.<br>V | Max.<br>V | Min.<br>V | Max.<br>V | Max.<br>V       | Min.<br>V | mA  | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μ <b>Α</b> <sup>4</sup> | μ <b>Α</b> <sup>4</sup> |

| 2 mA                          | -0.3      | 0.8       | 2         | 3.6       | 0.4             | 2.4       | 2   | 2  | 25                      | 27                      | 10                      | 10                      |

| 4 mA                          | -0.3      | 0.8       | 2         | 3.6       | 0.4             | 2.4       | 4   | 4  | 25                      | 27                      | 10                      | 10                      |

| 6 mA                          | -0.3      | 0.8       | 2         | 3.6       | 0.4             | 2.4       | 6   | 6  | 51                      | 54                      | 10                      | 10                      |

| 8 mA                          | -0.3      | 0.8       | 2         | 3.6       | 0.4             | 2.4       | 8   | 8  | 51                      | 54                      | 10                      | 10                      |

| 12 mA                         | -0.3      | 0.8       | 2         | 3.6       | 0.4             | 2.4       | 12  | 12 | 103                     | 109                     | 10                      | 10                      |

| 16 mA                         | -0.3      | 0.8       | 2         | 3.6       | 0.4             | 2.4       | 16  | 16 | 103                     | 109                     | 10                      | 10                      |

#### Notes:

- 1. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

- 2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges

- 3. Currents are measured at 100°C junction temperature and maximum voltage.

- 4. Currents are measured at 85°C junction temperature.

- 5. Software default selection highlighted in gray.

2-40 Revision 27

Table 2-77 • 3.3 V LVCMOS Wide Range Low Slew – Applies to 1.2 V DC Core Voltage Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case V<sub>CC</sub> = 1.14 V, Worst-Case VCCI = 2.7 Applicable to Standard Banks

| Drive<br>Strength | Equivalent<br>Software<br>Default Drive<br>Strength<br>Option <sup>1</sup> | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|-------------------|----------------------------------------------------------------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 100 μΑ            | 2 mA                                                                       | Std.           | 1.55              | 6.44            | 0.26             | 1.29            | 1.10              | 6.44            | 5.64            | 2.99            | 3.28            | ns    |

| 100 μΑ            | 4 mA                                                                       | Std.           | 1.55              | 6.44            | 0.26             | 1.29            | 1.10              | 6.44            | 5.64            | 2.99            | 3.28            | ns    |

| 100 μΑ            | 6 mA                                                                       | Std.           | 1.55              | 5.41            | 0.26             | 1.29            | 1.10              | 5.41            | 4.91            | 3.35            | 3.89            | ns    |

| 100 μΑ            | 8 mA                                                                       | Std.           | 1.55              | 5.41            | 0.26             | 1.29            | 1.10              | 5.41            | 4.91            | 3.35            | 3.89            | ns    |

#### Notes:

- The minimum drive strength for any LVCMOS 3.3 V software configuration when run in wide range is ± 100 μA. Drive strengths

displayed in software are supported for normal range only. For a detailed I/V curve, refer to the IBIS models.

- 2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

Table 2-78 • 3.3 V LVCMOS Wide Range High Slew – Applies to 1.2 V DC Core Voltage

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 2.7

Applicable to Standard Banks

| Drive<br>Strength | Equivalent<br>Software<br>Default Drive<br>Strength<br>Option <sup>1</sup> | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|-------------------|----------------------------------------------------------------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 100 μΑ            | 2 mA                                                                       | Std.           | 1.55              | 3.89            | 0.26             | 1.29            | 1.10              | 3.89            | 3.13            | 2.99            | 3.45            | ns    |

| 100 μΑ            | 4 mA                                                                       | Std.           | 1.55              | 3.89            | 0.26             | 1.29            | 1.10              | 3.89            | 3.13            | 2.99            | 3.45            | ns    |

| 100 μΑ            | 6 mA                                                                       | Std.           | 1.55              | 3.33            | 0.26             | 1.29            | 1.10              | 3.33            | 2.62            | 3.34            | 4.07            | ns    |

| 100 μΑ            | 8 mA                                                                       | Std.           | 1.55              | 3.33            | 0.26             | 1.29            | 1.10              | 3.33            | 2.62            | 3.34            | 4.07            | ns    |

#### Notes:

- 1. The minimum drive strength for any LVCMOS 3.3 V software configuration when run in wide range is  $\pm$  100  $\mu$ A. Drive strengths displayed in software are supported for normal range only. For a detailed I/V curve, refer to the IBIS models.

- 2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

- 3. Software default selection highlighted in gray.

2-54 Revision 27

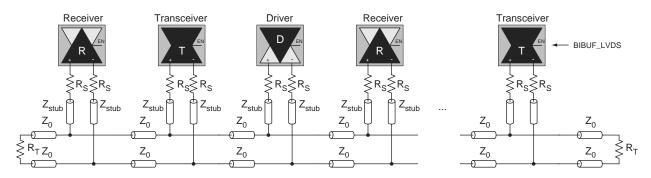

### **B-LVDS/M-LVDS**

Bus LVDS (B-LVDS) and Multipoint LVDS (M-LVDS) specifications extend the existing LVDS standard to high-performance multipoint bus applications. Multidrop and multipoint bus configurations may contain any combination of drivers, receivers, and transceivers. Microsemi LVDS drivers provide the higher drive current required by B-LVDS and M-LVDS to accommodate the loading. The drivers require series terminations for better signal quality and to control voltage swing. Termination is also required at both ends of the bus since the driver can be located anywhere on the bus. These configurations can be implemented using the TRIBUF\_LVDS and BIBUF\_LVDS macros along with appropriate terminations. Multipoint designs using Microsemi LVDS macros can achieve up to 200 MHz with a maximum of 20 loads. A sample application is given in Figure 2-14. The input and output buffer delays are available in the LVDS section in Table 2-149 on page 2-81 and Table 2-150 on page 2-81.

Example: For a bus consisting of 20 equidistant loads, the following terminations provide the required differential voltage, in worst-case Industrial operating conditions, at the farthest receiver:  $R_S = 60~\Omega$  and  $R_T = 70~\Omega$ , given  $Z_0 = 50~\Omega$  (2") and  $Z_{stub} = 50~\Omega$  (~1.5").

Figure 2-14 • B-LVDS/M-LVDS Multipoint Application Using LVDS I/O Buffers

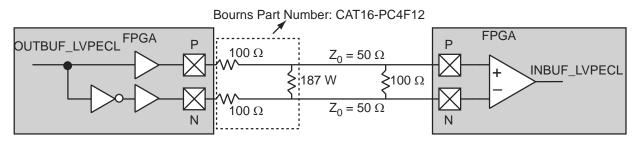

### **LVPECL**

Low-Voltage Positive Emitter-Coupled Logic (LVPECL) is another differential I/O standard. It requires that one data bit be carried through two signal lines. Like LVDS, two pins are needed. It also requires external resistor termination.

The full implementation of the LVDS transmitter and receiver is shown in an example in Figure 2-15. The building blocks of the LVPECL transmitter-receiver are one transmitter macro, one receiver macro, three board resistors at the transmitter end, and one resistor at the receiver end. The values for the three driver resistors are different from those used in the LVDS implementation because the output standard specifications are different.

Figure 2-15 • LVPECL Circuit Diagram and Board-Level Implementation

2-78 Revision 27

# VersaTile Specifications as a Sequential Module

The IGLOO library offers a wide variety of sequential cells, including flip-flops and latches. Each has a data input and optional enable, clear, or preset. In this section, timing characteristics are presented for a representative sample from the library. For more details, refer to the *IGLOO*, *Fusion*, and *ProASIC3 Macro Library Guide*.

Figure 2-27 • Sample of Sequential Cells

2-98 Revision 27

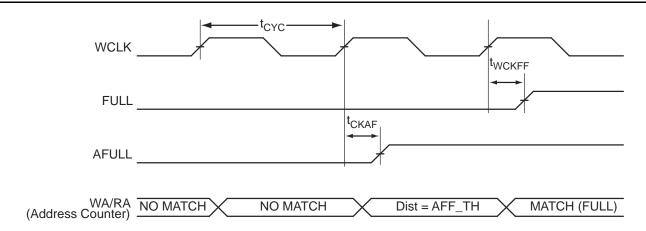

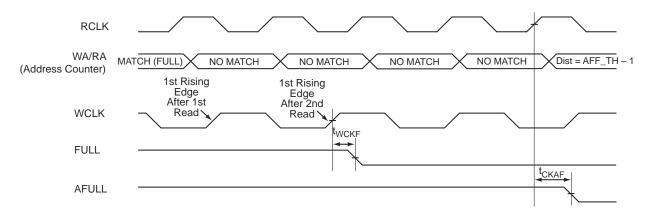

Figure 2-42 • FIFO FULL Flag and AFULL Flag Assertion

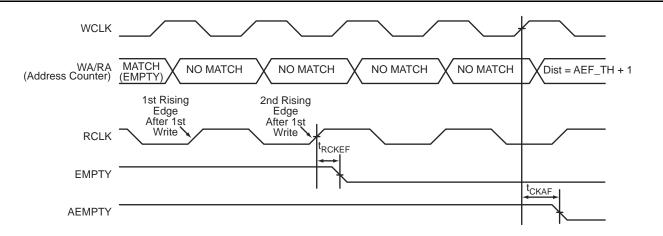

Figure 2-43 • FIFO EMPTY Flag and AEMPTY Flag Deassertion

Figure 2-44 • FIFO FULL Flag and AFULL Flag Deassertion

2-124 Revision 27

# 1.2 V DC Core Voltage

Table 2-196 • FIFO Worst Commercial-Case Conditions:  $T_J = 70^{\circ}\text{C}$ , VCC = 1.14 V

| Parameter            | Description                                       | Std.  | Units |

|----------------------|---------------------------------------------------|-------|-------|

| t <sub>ENS</sub>     | REN, WEN Setup Time                               | 4.13  | ns    |

| t <sub>ENH</sub>     | REN, WEN Hold Time                                | 0.31  | ns    |

| t <sub>BKS</sub>     | BLK Setup Time                                    | 0.47  | ns    |

| t <sub>BKH</sub>     | BLK Hold Time                                     | 0.00  | ns    |

| t <sub>DS</sub>      | Input Data (WD) Setup Time                        | 1.56  | ns    |

| t <sub>DH</sub>      | Input Data (WD) Hold Time                         | 0.49  | ns    |

| t <sub>CKQ1</sub>    | Clock High to New Data Valid on RD (flow-through) | 6.80  | ns    |

| t <sub>CKQ2</sub>    | Clock High to New Data Valid on RD (pipelined)    | 3.62  | ns    |

| t <sub>RCKEF</sub>   | RCLK High to Empty Flag Valid                     | 7.23  | ns    |

| t <sub>WCKFF</sub>   | WCLK High to Full Flag Valid                      | 6.85  | ns    |

| t <sub>CKAF</sub>    | Clock High to Almost Empty/Full Flag Valid        | 26.61 | ns    |

| t <sub>RSTFG</sub>   | RESET Low to Empty/Full Flag Valid                | 7.12  | ns    |

| t <sub>RSTAF</sub>   | RESET Low to Almost Empty/Full Flag Valid         | 26.33 | ns    |

| t <sub>RSTBQ</sub>   | RESET Low to Data Out Low on RD (flow-through)    | 4.09  | ns    |

|                      | RESET Low to Data Out Low on RD (pipelined)       | 4.09  | ns    |

| t <sub>REMRSTB</sub> | RESET Removal                                     | 1.23  | ns    |

| t <sub>RECRSTB</sub> | RESET Recovery                                    | 6.58  | ns    |

| t <sub>MPWRSTB</sub> | RESET Minimum Pulse Width                         | 1.18  | ns    |

| t <sub>CYC</sub>     | Clock Cycle Time                                  | 10.90 | ns    |

| F <sub>MAX</sub>     | Maximum Frequency for FIFO                        | 92    | MHz   |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

2-126 Revision 27

Package Pin Assignments

|            | CS196           |

|------------|-----------------|

| Pin Number | AGL250 Function |

| A1         | GND             |

| A2         | GAA0/IO00RSB0   |

| А3         | GAC0/IO04RSB0   |

| A4         | GAC1/IO05RSB0   |

| A5         | IO10RSB0        |

| A6         | IO13RSB0        |

| A7         | IO17RSB0        |

| A8         | IO19RSB0        |

| A9         | IO23RSB0        |

| A10        | GBC0/IO35RSB0   |

| A11        | GBB0/IO37RSB0   |

| A12        | GBB1/IO38RSB0   |

| A13        | GBA1/IO40RSB0   |

| A14        | GND             |

| B1         | VCCIB3          |

| B2         | VMV0            |

| В3         | GAA1/IO01RSB0   |

| B4         | GAB1/IO03RSB0   |

| B5         | GND             |

| В6         | IO12RSB0        |

| В7         | IO16RSB0        |

| B8         | IO22RSB0        |

| B9         | IO24RSB0        |

| B10        | GND             |

| B11        | GBC1/IO36RSB0   |

| B12        | GBA0/IO39RSB0   |

| B13        | GBA2/IO41PPB1   |

| B14        | GBB2/IO42PDB1   |

| C1         | GAC2/IO116UDB3  |

| C2         | GAB2/IO117UDB3  |

| C3         | GNDQ            |

| C4         | VCCIB0          |

| C5         | GAB0/IO02RSB0   |

| C6         | IO11RSB0        |

| C7         | VCCIB0          |

| C8         | IO20RSB0        |

|            | CS196           |

|------------|-----------------|

| Pin Number | AGL250 Function |

| C9         | IO30RSB0        |

| C10        | IO33RSB0        |

| C11        | VCCIB0          |

| C12        | IO41NPB1        |

| C13        | GNDQ            |

| C14        | IO42NDB1        |

| D1         | IO116VDB3       |

| D2         | IO117VDB3       |

| D3         | GAA2/IO118UDB3  |

| D4         | IO113PPB3       |

| D5         | IO08RSB0        |

| D6         | IO14RSB0        |

| D7         | IO15RSB0        |

| D8         | IO18RSB0        |

| D9         | IO25RSB0        |

| D10        | IO32RSB0        |

| D11        | IO44PPB1        |

| D12        | VMV1            |

| D13        | IO43NDB1        |

| D14        | GBC2/IO43PDB1   |

| E1         | IO112PDB3       |

| E2         | GND             |

| E3         | IO118VDB3       |

| E4         | VCCIB3          |

| E5         | IO114USB3       |

| E6         | IO07RSB0        |

| E7         | IO09RSB0        |

| E8         | IO21RSB0        |

| E9         | IO31RSB0        |

| E10        | IO34RSB0        |

| E11        | VCCIB1          |

| E12        | IO44NPB1        |

| E13        | GND             |

| E14        | IO45PDB1        |

| F1         | IO112NDB3       |

| F2         | IO107NPB3       |

|            |                 |

| 00400      |                 |

|------------|-----------------|

|            | CS196           |

| Pin Number | AGL250 Function |

| F3         | IO111PDB3       |

| F4         | IO111NDB3       |

| F5         | IO113NPB3       |

| F6         | IO06RSB0        |

| F7         | VCC             |

| F8         | VCC             |

| F9         | IO28RSB0        |

| F10        | IO54PDB1        |

| F11        | IO54NDB1        |

| F12        | IO47NDB1        |

| F13        | IO47PDB1        |

| F14        | IO45NDB1        |

| G1         | GFB1/IO109PDB3  |

| G2         | GFA0/IO108NDB3  |

| G3         | GFA2/IO107PPB3  |

| G4         | VCOMPLF         |

| G5         | GFC0/IO110NDB3  |

| G6         | VCC             |

| G7         | GND             |

| G8         | GND             |

| G9         | VCC             |

| G10        | GCC0/IO48NDB1   |

| G11        | GCB1/IO49PDB1   |

| G12        | GCA0/IO50NDB1   |

| G13        | IO53NDB1        |

| G14        | GCC2/IO53PDB1   |

| H1         | GFB0/IO109NDB3  |

| H2         | GFA1/IO108PDB3  |

| H3         | VCCPLF          |

| H4         | GFB2/IO106PPB3  |

| H5         | GFC1/IO110PDB3  |

| H6         | VCC             |

| H7         | GND             |

| H8         | GND             |

| H9         | VCC             |

| H10        | GCC1/IO48PDB1   |

| <b>I</b>   |                 |

4-12 Revision 27

Package Pin Assignments

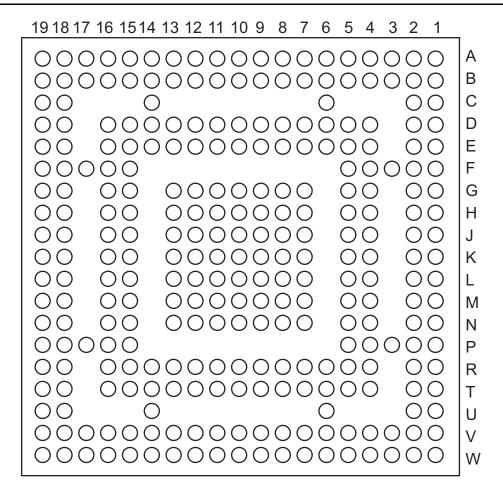

# **CS281**

Note: This is the bottom view of the package.

### Note

For more information on package drawings, see PD3068: Package Mechanical Drawings.

4-16 Revision 27

IGLOO Low Power Flash FPGAs

| (          | QN132           |

|------------|-----------------|

| Pin Number | AGL030 Function |

| A1         | IO80RSB1        |

| A2         | IO77RSB1        |

| A3         | NC              |

| A4         | IO76RSB1        |

| A5         | GEC0/IO73RSB1   |

| A6         | NC              |

| A7         | GEB0/IO71RSB1   |

| A8         | IO69RSB1        |

| A9         | NC              |

| A10        | VCC             |

| A11        | IO67RSB1        |

| A12        | IO64RSB1        |

| A13        | IO59RSB1        |

| A14        | IO56RSB1        |

| A15        | NC              |

| A16        | IO55RSB1        |

| A17        | IO53RSB1        |

| A18        | VCC             |

| A19        | IO50RSB1        |

| A20        | IO48RSB1        |

| A21        | IO45RSB1        |

| A22        | IO44RSB1        |

| A23        | IO43RSB1        |

| A24        | TDI             |

| A25        | TRST            |

| A26        | IO40RSB0        |

| A27        | NC              |

| A28        | IO39RSB0        |

| A29        | IO38RSB0        |

| A30        | IO36RSB0        |

| A31        | IO35RSB0        |

| A32        | GDC0/IO32RSB0   |

| A33        | NC              |

| A34        | VCC             |

| A35        | IO30RSB0        |

| A36        | IO27RSB0        |

|            | QN132           |  |

|------------|-----------------|--|

| Pin Number | AGL030 Function |  |

| A37        | IO22RSB0        |  |

| A38        | IO19RSB0        |  |

| A39        | NC              |  |

| A40        | IO18RSB0        |  |

| A41        | IO16RSB0        |  |

| A42        | IO14RSB0        |  |

| A43        | VCC             |  |

| A44        | IO11RSB0        |  |

| A45        | IO08RSB0        |  |

| A46        | IO06RSB0        |  |

| A47        | IO05RSB0        |  |

| A48        | IO02RSB0        |  |

| B1         | IO81RSB1        |  |

| B2         | IO78RSB1        |  |

| В3         | GND             |  |

| B4         | IO75RSB1        |  |

| B5         | NC              |  |

| В6         | GND             |  |

| B7         | IO70RSB1        |  |

| B8         | NC              |  |

| В9         | GND             |  |

| B10        | IO66RSB1        |  |

| B11        | IO63RSB1        |  |

| B12        | FF/IO60RSB1     |  |

| B13        | IO57RSB1        |  |

| B14        | GND             |  |

| B15        | IO54RSB1        |  |

| B16        | IO52RSB1        |  |

| B17        | GND             |  |

| B18        | IO49RSB1        |  |

| B19        | IO46RSB1        |  |

| B20        | GND             |  |

| B21        | IO42RSB1        |  |

| B22        | TMS             |  |

| B23        | TDO             |  |

| B24        | IO41RSB0        |  |

| QN132      |                 |

|------------|-----------------|

| Pin Number | AGL030 Function |

| B25        | GND             |

|            |                 |

| B26        | NC<br>LCCZDODO  |

| B27        | IO37RSB0        |

| B28        | GND             |

| B29        | GDA0/IO33RSB0   |

| B30        | NC              |

| B31        | GND             |

| B32        | IO29RSB0        |

| B33        | IO26RSB0        |

| B34        | IO23RSB0        |

| B35        | IO20RSB0        |

| B36        | GND             |

| B37        | IO17RSB0        |

| B38        | IO15RSB0        |

| B39        | GND             |

| B40        | IO12RSB0        |

| B41        | IO09RSB0        |

| B42        | GND             |

| B43        | IO04RSB0        |

| B44        | IO01RSB0        |

| C1         | IO82RSB1        |

| C2         | IO79RSB1        |

| C3         | NC              |

| C4         | IO74RSB1        |

| C5         | GEA0/IO72RSB1   |

| C6         | NC              |

| C7         | NC              |

| C8         | VCCIB1          |

| C9         | IO65RSB1        |

| C10        | IO62RSB1        |

| C11        | IO61RSB1        |

| C12        | IO58RSB1        |

| C13        | NC              |

| C14        | NC              |

| C15        | IO51RSB1        |

| C16        | VCCIB1          |

Revision 27 4-29

Package Pin Assignments

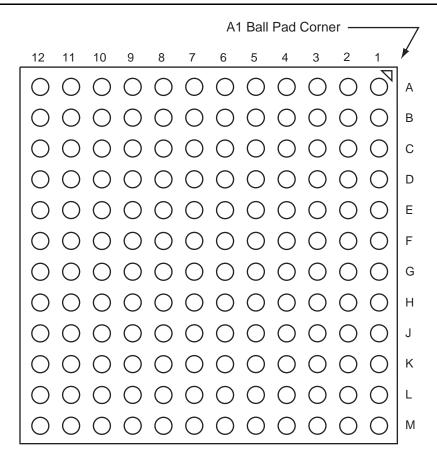

# **FG144**

Note: This is the bottom view of the package.

## Note

For more information on package drawings, see PD3068: Package Mechanical Drawings.

4-42 Revision 27

Package Pin Assignments

|            | FG144             |

|------------|-------------------|

| Pin Number | AGL400 Function   |

|            |                   |

| K1         | GEB0/IO136NDB3    |

| K2         | GEA1/IO135PDB3    |

| K3         | GEA0/IO135NDB3    |

| K4         | GEA2/IO134RSB2    |

| K5         | IO127RSB2         |

| K6         | IO121RSB2         |

| K7         | GND               |

| K8         | IO104RSB2         |

| K9         | GDC2/IO82RSB2     |

| K10        | GND               |

| K11        | GDA0/IO79VDB1     |

| K12        | GDB0/IO78VDB1     |

| L1         | GND               |

| L2         | VMV3              |

| L3         | FF/GEB2/IO133RSB2 |

| L4         | IO128RSB2         |

| L5         | VCCIB2            |

| L6         | IO119RSB2         |

| L7         | IO114RSB2         |

| L8         | IO110RSB2         |

| L9         | TMS               |

| L10        | VJTAG             |

| L11        | VMV2              |

| L12        | TRST              |

| M1         | GNDQ              |

| M2         | GEC2/IO132RSB2    |

| M3         | IO129RSB2         |

| M4         | IO126RSB2         |

| M5         | IO124RSB2         |

| M6         | IO122RSB2         |

| M7         | IO117RSB2         |

| M8         | IO115RSB2         |

| M9         | TDI               |

| M10        | VCCIB2            |

| M11        | VPUMP             |

| M12        | GNDQ              |

|            |                   |

4-48 Revision 27

|            | FG484           |

|------------|-----------------|

| Pin Number | AGL400 Function |

| U1         | NC NC           |

| U2         | NC<br>NC        |

| U3         | NC NC           |

|            |                 |

| U4         | GEB1/IO136PDB3  |

| U5         | GEB0/IO136NDB3  |

| U6         | VMV2            |

| U7         | IO129RSB2       |

| U8         | IO128RSB2       |

| U9         | IO122RSB2       |

| U10        | IO115RSB2       |

| U11        | IO110RSB2       |

| U12        | IO98RSB2        |

| U13        | IO95RSB2        |

| U14        | IO88RSB2        |

| U15        | IO84RSB2        |

| U16        | TCK             |

| U17        | VPUMP           |

| U18        | TRST            |

| U19        | GDA0/IO79VDB1   |

| U20        | NC              |

| U21        | NC              |

| U22        | NC              |

| V1         | NC              |

| V2         | NC              |

| V3         | GND             |

| V4         | GEA1/IO135PDB3  |

| V5         | GEA0/IO135NDB3  |

| V6         | IO127RSB2       |

| V7         | GEC2/IO132RSB2  |

| V8         | IO123RSB2       |

| V9         | IO118RSB2       |

| V10        | IO112RSB2       |

| V11        | IO106RSB2       |

| V12        | IO100RSB2       |

| V13        | IO96RSB2        |

| V14        | IO89RSB2        |

|            |                 |

Revision 27 4-75

# 5 - Datasheet Information

# **List of Changes**

The following tables list critical changes that were made in each revision of the IGLOO datasheet.

| Revision                    | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Page                   |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| Revision 27<br>(May 2016)   | Added the deleted package FG144 from AGL125 device in "IGLOO Devices" (SAR 79355).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1-I                    |

| Revision 26<br>(March 2016) | <ul> <li>Updated "IGLOO Ordering Information" and "Temperature Grade Offerings" notes by:</li> <li>Replacing Commercial (0°C to +70°C Ambient Temperature) with Commercial (0°C to +85°C Junction Temperature) (SAR 48352).</li> <li>Replacing Industrial (-40°C to +85°C Ambient Temperature) with Industrial (-40°C to +100°C Junction Temperature) (SAR 48352).</li> </ul>                                                                                                                                                                                                                                                                                                                                                                              | 1-III and<br>1-IV      |

|                             | Ambient temperature row removed in Table 2-2 (SAR 48352).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2-2                    |

|                             | Updated Table 2-2 note 2 from "To ensure targeted reliability standards are met across ambient and junction operating temperatures, Microsemi recommends that the user follow best design practices using Microsemi's timing and power simulation tools." to "Software Default Junction Temperature Range in the Libero SoC software is set to 0°C to +70°C for commercial, and -40°C to +85°C for industrial. To ensure targeted reliability standards are met across the full range of junction temperatures, Microsemi recommends using custom settings for temperature range before running timing and power analysis tools. For more information on custom settings, refer to the New Project Dialog Box in the Libero SoC Online Help." (SAR 77087). | 2-2                    |

|                             | Updated Table 2-2 note 9 from "VMV pins must be connected to the corresponding VCCI pins. See the "Pin Descriptions" chapter of the IGLOO FPGA Fabric User Guide for further information." to "VMV and VCCI must be at the same voltage within a given I/O bank. VMV pins must be connected to the corresponding VCCI pins. See the "VMVx I/O Supply Voltage (quiet)" on page 3-1 for further information." (SAR 77087)                                                                                                                                                                                                                                                                                                                                    |                        |

|                             | Added 2 mA drive strengths in tables same as 4 mA (SAR 57179).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | NA                     |

|                             | Added reference of Package Mechanical Drawings document in all package pin assignment notes (76777).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | NA                     |

| Revision 25<br>(June2015)   | Removed package FG144 from AGL060 device in the following tables: "IGLOO Devices", "I/Os Per Package1" and "Temperature Grade Offerings" (SAR 68517)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | I, II, and<br>IV       |

|                             | Removed Package Pin Assignment table of AGL060 device from FG144.(SAR 68517)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -                      |

| Revision 24<br>(March 2014) | Note added for the discontinuance of QN132 package to the following tables: "IGLOO Devices", "I/Os Per Package1", "IGLOO FPGAs Package Sizes Dimensions", and "Temperature Grade Offerings" and "QN132" section (SAR 55117, PDN 1306).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | I, II, IV,<br>and 4-28 |

|                             | Removed packages CS81 and QN132 from AGL250 device in the following tables: "IGLOO Devices", "I/Os Per Package1", and "Temperature Grade Offerings" (SAR 49472).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | I, II, and<br>IV       |

Revision 27 5-1

## IGLOO Low Power Flash FPGAs

| Revision                        | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Page            |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| Revision 23<br>(December 2012)  | The "IGLOO Ordering Information" section has been updated to mention "Y" as "Blank" mentioning "Device Does Not Include License to Implement IP Based on the Cryptography Research, Inc. (CRI) Patent Portfolio" (SAR 43173).                                                                                                                                                                                                                                                | III             |

|                                 | The note in Table 2-189 · IGLOO CCC/PLL Specification and Table 2-190 · IGLOO CCC/PLL Specification referring the reader to SmartGen was revised to refer instead to the online help associated with the core (SAR 42564). Additionally, note regarding SSOs was added.                                                                                                                                                                                                      | 2-115,<br>2-116 |

|                                 | Live at Power-Up (LAPU) has been replaced with 'Instant On'.                                                                                                                                                                                                                                                                                                                                                                                                                 | NA              |

| Revision 22<br>(September 2012) | The "Security" section was modified to clarify that Microsemi does not support read-back of programmed data.                                                                                                                                                                                                                                                                                                                                                                 | 1-2             |

|                                 | Libero Integrated Design Environment (IDE) was changed to Libero System-on-Chip (SoC) throughout the document (SAR 40271).                                                                                                                                                                                                                                                                                                                                                   | N/A             |

| Revision 21<br>(May 2012)       | Under AGL125, in the Package Pin list, CS121 was incorrectly added to the datasheet in revision 19 and has been removed (SAR 38217).                                                                                                                                                                                                                                                                                                                                         | I to IV         |

|                                 | Corrected the inadvertent error for Max Values for LVPECL VIH and revised the same to '3.6' in Table 2-151 · Minimum and Maximum DC Input and Output Levels (SAR 37685).                                                                                                                                                                                                                                                                                                     | 2-82            |

|                                 | Figure 2-38 • FIFO Read and Figure 2-39 • FIFO Write have been added (SAR 34841).                                                                                                                                                                                                                                                                                                                                                                                            | 2-127           |

|                                 | The following sentence was removed from the VMVx description in the "Pin Descriptions" section: "Within the package, the VMV plane is decoupled from the simultaneous switching noise originating from the output buffer VCCI domain" and replaced with "Within the package, the VMV plane biases the input stage of the I/Os in the I/O banks" (SAR 38317). The datasheet mentions that "VMV pins must be connected to the corresponding VCCI pins" for an ESD enhancement. | 3-1             |

Revision 27 5-2

IGLOO Low Power Flash FPGAs

| Revision / Version                                  | Changes                                                                                                                                                                                                                                                                  | Page         |

|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Revision 18 (Nov 2009)                              | The version changed to v2.0 for IGLOO datasheet chapters, indicating the datasheet contains information based on final characterization. Please review the datasheet carefully as most tables were updated with new data.                                                | N/A          |

| Revision 17 (Sep 2009) Product Brief v1.6           | The "Reprogrammable Flash Technology" section was modified to add "250 MHz (1.5 V systems) and 160 MHz (1.2 V systems) System Performance."                                                                                                                              | I            |

|                                                     | "IGLOO Ordering Information" was revised to note that halogen-free packages are available with RoHS-compliant packaging.                                                                                                                                                 | III          |

|                                                     | Table 1-1 • I/O Standards Supported is new.                                                                                                                                                                                                                              | 1-7          |

|                                                     | The definitions of hot-swap and cold-sparing were added to the "I/Os with Advanced I/O Standards" section.                                                                                                                                                               | 1-7          |

| Revision 16 (Apr 2009)<br>Product Brief v1.5        | M1AGL400 is no longer offered and was removed from the "IGLOO Devices" product table, "IGLOO Ordering Information", and "Temperature Grade Offerings".                                                                                                                   | I, III, IV   |

|                                                     | The -F speed grade is no longer offered for IGLOO devices. The speed grade column and note regarding -F speed grade were removed from "IGLOO Ordering Information". The "Speed Grade and Temperature Grade Matrix" section was removed.                                  | III, IV      |

|                                                     | This datasheet now has fully characterized data and has moved from being Advance to a Production version. The version number changed from Advance v0.5 to v2.0.                                                                                                          | N/A          |

|                                                     | Please review the datasheet carefully as most tables were updated with new data.                                                                                                                                                                                         |              |

| DC and Switching<br>Characteristics<br>Advance v0.6 | $3.3\ V\ LVCMOS$ and $1.2\ V\ LVCMOS$ Wide Range support was added to the datasheet. This affects all tables that contained $3.3\ V\ LVCMOS$ and $1.2\ V\ LVCMOS$ data.                                                                                                  |              |

|                                                     | $\rm I_{\rm IL}$ and $\rm I_{\rm IH}$ input leakage current information was added to all "Minimum and Maximum DC Input and Output Levels" tables.                                                                                                                        | N/A          |

|                                                     | -F was removed from the datasheet. The speed grade is no longer supported.                                                                                                                                                                                               | N/A          |

|                                                     | The notes in Table 2-2 • Recommended Operating Conditions 1 were updated.                                                                                                                                                                                                | 2-2          |

|                                                     | Table 2-4 • Overshoot and Undershoot Limits 1 was updated.                                                                                                                                                                                                               | 2-3          |

|                                                     | Table 2-5 • Package Thermal Resistivities was updated.                                                                                                                                                                                                                   | 2-6          |

|                                                     | Table 2-6 • Temperature and Voltage Derating Factors for Timing Delays (normalized to TJ = $70^{\circ}$ C, VCC = $1.425$ V) and Table 2-7 • Temperature and Voltage Derating Factors for Timing Delays (normalized to TJ = $70^{\circ}$ C, VCC = $1.14$ V) were updated. | 2-7          |

|                                                     | In Table 2-191 • RAM4K9 and Table 2-193 • RAM4K9, the following specifications were removed:                                                                                                                                                                             | 2-122<br>and |

|                                                     | twro .                                                                                                                                                                                                                                                                   | 2-124        |

|                                                     | tockh                                                                                                                                                                                                                                                                    | 0.15-        |

|                                                     | In Table 2-192 • RAM512X18 and Table 2-194 • RAM512X18, the following specifications were removed:                                                                                                                                                                       | 2-123<br>and |

|                                                     | two                                                                                                                                                                                                                                                                      | 2-125        |

|                                                     | т <sub>сскн</sub>                                                                                                                                                                                                                                                        |              |

| Revision 15 (Feb 2009)                              | The "QN132" pin table for the AGL060 device is new.                                                                                                                                                                                                                      | 4-31         |