Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                                |

|--------------------------------|----------------------------------------------------------------|

| Product Status                 | Obsolete                                                       |

| Number of LABs/CLBs            | -                                                              |

| Number of Logic Elements/Cells | 13824                                                          |

| Total RAM Bits                 | 110592                                                         |

| Number of I/O                  | 235                                                            |

| Number of Gates                | 600000                                                         |

| Voltage - Supply               | 1.425V ~ 1.575V                                                |

| Mounting Type                  | Surface Mount                                                  |

| Operating Temperature          | -40°C ~ 85°C (TA)                                              |

| Package / Case                 | 484-BGA                                                        |

| Supplier Device Package        | 484-FPBGA (23x23)                                              |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microsemi/agl600v5-fg484i |

|                                |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

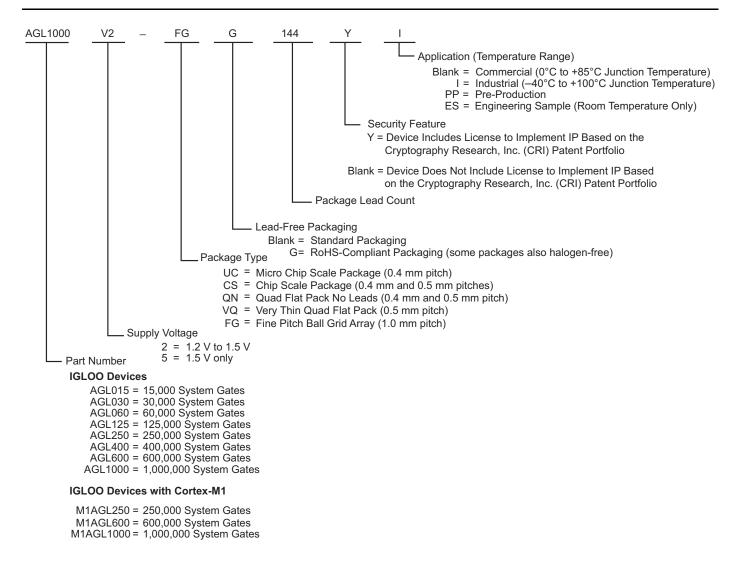

# **IGLOO Ordering Information**

Note: Marking Information: IGLOO V2 devices do not have V2 marking, but IGLOO V5 devices are marked accordingly.

- Wide input frequency range ( $f_{IN CCC}$ ) = 1.5 MHz up to 250 MHz

- Output frequency range (f<sub>OUT CCC</sub>) = 0.75 MHz up to 250 MHz

- 2 programmable delay types for clock skew minimization

- Clock frequency synthesis (for PLL only)

Additional CCC specifications:

- Internal phase shift = 0°, 90°, 180°, and 270°. Output phase shift depends on the output divider configuration (for PLL only).

- Output duty cycle =  $50\% \pm 1.5\%$  or better (for PLL only)

- Low output jitter: worst case < 2.5% × clock period peak-to-peak period jitter when single global network used (for PLL only)

- Maximum acquisition time is 300 µs (for PLL only)

- Exceptional tolerance to input period jitter—allowable input jitter is up to 1.5 ns (for PLL only)

- Four precise phases; maximum misalignment between adjacent phases of 40 ps × 250 MHz / f<sub>OUT\_CCC</sub> (for PLL only)

### **Global Clocking**

IGLOO devices have extensive support for multiple clocking domains. In addition to the CCC and PLL support described above, there is a comprehensive global clock distribution network.

Each VersaTile input and output port has access to nine VersaNets: six chip (main) and three quadrant global networks. The VersaNets can be driven by the CCC or directly accessed from the core via multiplexers (MUXes). The VersaNets can be used to distribute low-skew clock signals or for rapid distribution of high-fanout nets.

## I/Os with Advanced I/O Standards

The IGLOO family of FPGAs features a flexible I/O structure, supporting a range of voltages (1.2 V, 1.5 V, 1.8 V, 2.5 V, 3.0 V wide range, and 3.3 V). IGLOO FPGAs support many different I/O standards—single-ended and differential.

The I/Os are organized into banks, with two or four banks per device. The configuration of these banks determines the I/O standards supported (Table 1-1).

|               |                                                                                       | I/O Standards Supported |               |                                 |  |  |  |

|---------------|---------------------------------------------------------------------------------------|-------------------------|---------------|---------------------------------|--|--|--|

| I/O Bank Type | Device and Bank Location                                                              | LVTTL/<br>LVCMOS        | PCI/PCI-X     | LVPECL, LVDS,<br>B-LVDS, M-LVDS |  |  |  |

| Advanced      | East and west banks of AGL250 and larger devices                                      | $\checkmark$            | $\checkmark$  | $\checkmark$                    |  |  |  |

| Standard Plus | North and south banks of AGL250 and larger devices<br>All banks of AGL060 and AGL125K | $\checkmark$            | $\checkmark$  | Not supported                   |  |  |  |

| Standard      | All banks of AGL015 and AGL030                                                        | $\checkmark$            | Not supported | Not supported                   |  |  |  |

#### Table 1-1 • I/O Standards Supported

Each I/O module contains several input, output, and enable registers. These registers allow the implementation of the following:

- Single-Data-Rate applications

- Double-Data-Rate applications—DDR LVDS, B-LVDS, and M-LVDS I/Os for point-to-point communications

IGLOO banks for the AGL250 device and above support LVPECL, LVDS, B-LVDS, and M-LVDS. B-LVDS and M-LVDS can support up to 20 loads.

Hot-swap (also called hot-plug, or hot-insertion) is the operation of hot-insertion or hot-removal of a card in a poweredup system.

Cold-sparing (also called cold-swap) refers to the ability of a device to leave system data undisturbed when the system is powered up, while the component itself is powered down, or when power supplies are floating.

## Guidelines

### **Toggle Rate Definition**

A toggle rate defines the frequency of a net or logic element relative to a clock. It is a percentage. If the toggle rate of a net is 100%, this means that this net switches at half the clock frequency. Below are some examples:

- The average toggle rate of a shift register is 100% because all flip-flop outputs toggle at half of the clock frequency.

- The average toggle rate of an 8-bit counter is 25%:

- Bit 0 (LSB) = 100%

- Bit 1 = 50%

- Bit 2 = 25%

- ...

- Bit 7 (MSB) = 0.78125%

- Average toggle rate = (100% + 50% + 25% + 12.5% + . . . + 0.78125%) / 8

### Enable Rate Definition

Output enable rate is the average percentage of time during which tristate outputs are enabled. When nontristate output buffers are used, the enable rate should be 100%.

#### Table 2-23 • Toggle Rate Guidelines Recommended for Power Calculation

| Component  | Definition                       | Guideline |

|------------|----------------------------------|-----------|

| $\alpha_1$ | Toggle rate of VersaTile outputs | 10%       |

| $\alpha_2$ | I/O buffer toggle rate           | 10%       |

#### Table 2-24 • Enable Rate Guidelines Recommended for Power Calculation

| Component      | Definition                           | Guideline |

|----------------|--------------------------------------|-----------|

| β <sub>1</sub> | I/O output buffer enable rate        | 100%      |

| β <sub>2</sub> | RAM enable rate for read operations  | 12.5%     |

| β <sub>3</sub> | RAM enable rate for write operations | 12.5%     |

### Table 2-104 • 1.8 V LVCMOS High Slew – Applies to 1.5 V DC Core Voltage

Commercial-Case Conditions:  $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.7 V Applicable to Standard Banks

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA           | Std.        | 2.62              | 0.18            | 0.98             | 0.66            | 2.67              | 2.59            | 1.67            | 1.29            | 2.62            | ns    |

| 4 mA           | Std.        | 2.18              | 0.18            | 0.98             | 0.66            | 2.22              | 1.93            | 1.97            | 2.06            | 2.18            | ns    |

Notes:

1. Software default selection highlighted in gray.

2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

#### 1.2 V DC Core Voltage

Table 2-105 • 1.8 V LVCMOS Low Slew – Applies to 1.2 V DC Core Voltage Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 1.7 V Applicable to Advanced I/O Banks

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA           | Std.        | 1.55              | 6.97            | 0.26             | 1.11            | 1.10              | 7.08            | 6.48            | 2.87            | 2.29            | 12.87            | 12.27            | ns    |

| 4 mA           | Std.        | 1.55              | 5.91            | 0.26             | 1.11            | 1.10              | 6.01            | 5.57            | 3.21            | 3.14            | 11.79            | 11.36            | ns    |

| 6 mA           | Std.        | 1.55              | 5.16            | 0.26             | 1.11            | 1.10              | 5.24            | 4.95            | 3.45            | 3.55            | 11.03            | 10.74            | ns    |

| 8 mA           | Std.        | 1.55              | 4.90            | 0.26             | 1.11            | 1.10              | 4.98            | 4.81            | 3.50            | 3.66            | 10.77            | 10.60            | ns    |

| 12 mA          | Std.        | 1.55              | 4.83            | 0.26             | 1.11            | 1.10              | 4.90            | 4.83            | 3.58            | 4.08            | 10.68            | 10.61            | ns    |

| 16 mA          | Std.        | 1.55              | 4.83            | 0.26             | 1.11            | 1.10              | 4.90            | 4.83            | 3.58            | 4.08            | 10.68            | 10.61            | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

### Table 2-106 • 1.8 V LVCMOS High Slew – Applies to 1.2 V DC Core Voltage

Commercial-Case Conditions:  $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 1.7 V Applicable to Advanced I/O Banks

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>ZHS</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA           | Std.        | 1.55              | 3.73            | 0.26             | 1.11            | 1.10              | 3.71            | 3.73            | 2.86            | 2.34            | 9.49             | 9.51             | ns    |

| 4 mA           | Std.        | 1.55              | 3.12            | 0.26             | 1.11            | 1.10              | 3.16            | 2.97            | 3.21            | 3.22            | 8.95             | 8.75             | ns    |

| 6 mA           | Std.        | 1.55              | 2.79            | 0.26             | 1.11            | 1.10              | 2.83            | 2.59            | 3.45            | 3.65            | 8.62             | 8.38             | ns    |

| 8 mA           | Std.        | 1.55              | 2.73            | 0.26             | 1.11            | 1.10              | 2.77            | 2.52            | 3.50            | 3.75            | 8.56             | 8.30             | ns    |

| 12 mA          | Std.        | 1.55              | 2.72            | 0.26             | 1.11            | 1.10              | 2.76            | 2.43            | 3.58            | 4.19            | 8.55             | 8.22             | ns    |

| 16 mA          | Std.        | 1.55              | 2.72            | 0.26             | 1.11            | 1.10              | 2.76            | 2.43            | 3.58            | 4.19            | 8.55             | 8.22             | ns    |

Notes:

1. Software default selection highlighted in gray.

2. For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

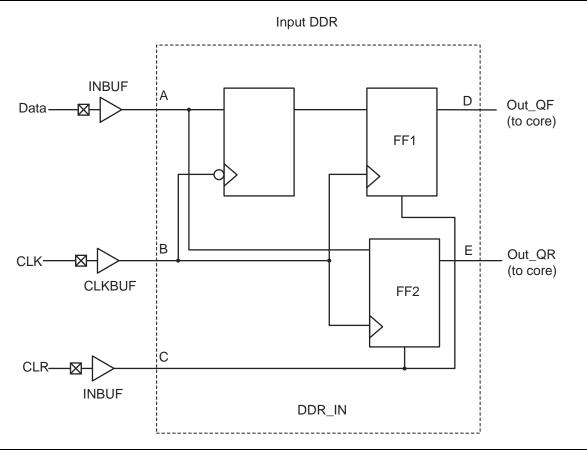

# **DDR Module Specifications**

# Input DDR Module

### Figure 2-21 • Input DDR Timing Model

| Table 2-163 • F | Parameter | Definitions |

|-----------------|-----------|-------------|

|-----------------|-----------|-------------|

| Parameter Name          | Parameter Definition         | Measuring Nodes (from, to) |

|-------------------------|------------------------------|----------------------------|

| t <sub>DDRICLKQ1</sub>  | Clock-to-Out Out_QR          | B, D                       |

| tDDRICLKQ2              | Clock-to-Out Out_QF          | B, E                       |

| tDDRISUD                | Data Setup Time of DDR input | А, В                       |

|                         | Data Hold Time of DDR input  | A, B                       |

| t <sub>DDRICLR2Q1</sub> | Clear-to-Out Out_QR          | C, D                       |

| t <sub>DDRICLR2Q2</sub> | Clear-to-Out Out_QF          | C, E                       |

| t <sub>DDRIREMCLR</sub> | Clear Removal                | С, В                       |

| t <sub>DDRIRECCLR</sub> | Clear Recovery               | С, В                       |

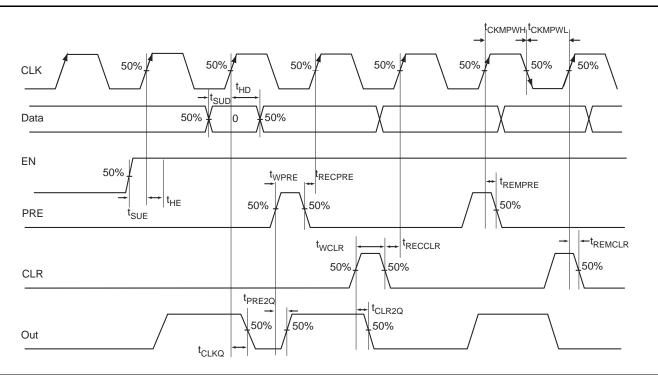

# **Timing Characteristics**

1.5 V DC Core Voltage

## Table 2-171 • Register Delays

## Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V

| Parameter           | Description                                                   | Std. | Units |

|---------------------|---------------------------------------------------------------|------|-------|

| t <sub>CLKQ</sub>   | Clock-to-Q of the Core Register                               | 0.89 | ns    |

| t <sub>SUD</sub>    | Data Setup Time for the Core Register                         | 0.81 | ns    |

| t <sub>HD</sub>     | Data Hold Time for the Core Register                          | 0.00 | ns    |

| t <sub>SUE</sub>    | Enable Setup Time for the Core Register                       | 0.73 | ns    |

| t <sub>HE</sub>     | Enable Hold Time for the Core Register                        | 0.00 | ns    |

| t <sub>CLR2Q</sub>  | Asynchronous Clear-to-Q of the Core Register                  | 0.60 | ns    |

| t <sub>PRE2Q</sub>  | Asynchronous Preset-to-Q of the Core Register                 | 0.62 | ns    |

| t <sub>REMCLR</sub> | Asynchronous Clear Removal Time for the Core Register         | 0.00 | ns    |

| t <sub>RECCLR</sub> | Asynchronous Clear Recovery Time for the Core Register        | 0.24 | ns    |

| t <sub>REMPRE</sub> | Asynchronous Preset Removal Time for the Core Register        | 0.00 | ns    |

| t <sub>RECPRE</sub> | Asynchronous Preset Recovery Time for the Core Register       | 0.23 | ns    |

| t <sub>WCLR</sub>   | Asynchronous Clear Minimum Pulse Width for the Core Register  | 0.30 | ns    |

| t <sub>WPRE</sub>   | Asynchronous Preset Minimum Pulse Width for the Core Register | 0.30 | ns    |

| t <sub>CKMPWH</sub> | Clock Minimum Pulse Width High for the Core Register          | 0.56 | ns    |

| t <sub>CKMPWL</sub> | Clock Minimum Pulse Width Low for the Core Register           | 0.56 | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

## 1.2 V DC Core Voltage

### Table 2-172 • Register Delays

## Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V

| Parameter           | Description                                                   | Std. | Units |

|---------------------|---------------------------------------------------------------|------|-------|

| t <sub>CLKQ</sub>   | Clock-to-Q of the Core Register                               | 1.61 | ns    |

| t <sub>SUD</sub>    | Data Setup Time for the Core Register                         | 1.17 | ns    |

| t <sub>HD</sub>     | Data Hold Time for the Core Register                          | 0.00 | ns    |

| t <sub>SUE</sub>    | Enable Setup Time for the Core Register                       | 1.29 | ns    |

| t <sub>HE</sub>     | Enable Hold Time for the Core Register                        | 0.00 | ns    |

| t <sub>CLR2Q</sub>  | Asynchronous Clear-to-Q of the Core Register                  | 0.87 | ns    |

| t <sub>PRE2Q</sub>  | Asynchronous Preset-to-Q of the Core Register                 | 0.89 | ns    |

| t <sub>REMCLR</sub> | Asynchronous Clear Removal Time for the Core Register         | 0.00 | ns    |

| t <sub>RECCLR</sub> | Asynchronous Clear Recovery Time for the Core Register        | 0.24 | ns    |

| t <sub>REMPRE</sub> | Asynchronous Preset Removal Time for the Core Register        | 0.00 | ns    |

| t <sub>RECPRE</sub> | Asynchronous Preset Recovery Time for the Core Register       | 0.24 | ns    |

| t <sub>WCLR</sub>   | Asynchronous Clear Minimum Pulse Width for the Core Register  | 0.46 | ns    |

| t <sub>WPRE</sub>   | Asynchronous Preset Minimum Pulse Width for the Core Register | 0.46 | ns    |

| t <sub>CKMPWH</sub> | Clock Minimum Pulse Width High for the Core Register          | 0.95 | ns    |

| t <sub>CKMPWL</sub> | Clock Minimum Pulse Width Low for the Core Register           | 0.95 | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

### 1.2 V DC Core Voltage

# Table 2-181 • AGL015 Global ResourceCommercial-Case Conditions: TJ = 70°C, VCC = 1.14 V

|                      |                                           | S                 | td.               |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 1.79              | 2.09              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 1.87              | 2.26              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | 1.40              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  | 1.65              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.39              | ns    |

Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

# Table 2-182 • AGL030 Global Resource

#### Commercial-Case Conditions: $T_J = 70^{\circ}C$ , VCC = 1.14 V

|                      |                                           | S                 | Std.              |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 1.80              | 2.09              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 1.88              | 2.27              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | 1.40              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  | 1.65              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.39              | ns    |

Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

# Timing Waveforms

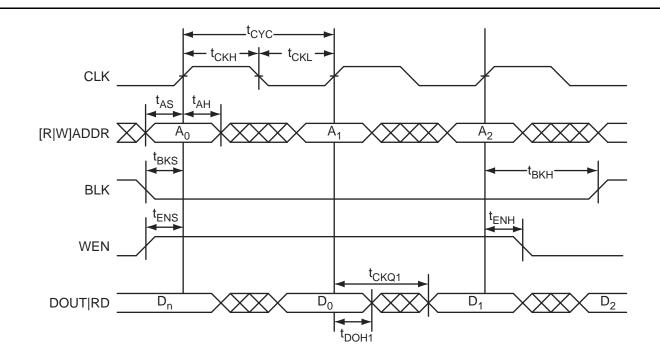

Figure 2-32 • RAM Read for Pass-Through Output. Applicable to Both RAM4K9 and RAM512x18.

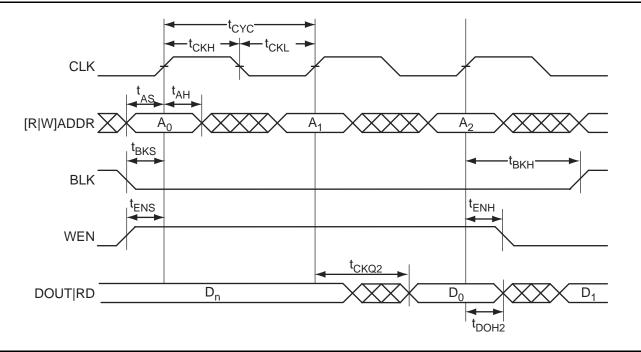

Figure 2-33 • RAM Read for Pipelined Output. Applicable to Both RAM4K9 and RAM512x18.

IGLOO Low Power Flash FPGAs

|            | CS81            | CS81       |               |  |

|------------|-----------------|------------|---------------|--|

| Pin Number | AGL250 Function | Pin Number | AGL250 Funct  |  |

| A1         | GAA0/IO00RSB0   | E1         | GFB0/IO109ND  |  |

| A2         | GAA1/IO01RSB0   | E2         | GFB1/IO109PD  |  |

| A3         | GAC0/IO04RSB0   | E3         | GFA1/IO108PS  |  |

| A4         | IO13RSB0        | E4         | VCCIB3        |  |

| A5         | IO21RSB0        | E5         | VCC           |  |

| A6         | IO27RSB0        | E6         | VCCIB1        |  |

| A7         | GBB0/IO37RSB0   | E7         | GCA0/IO50ND   |  |

| A8         | GBA1/IO40RSB0   | E8         | GCA1/IO50PD   |  |

| A9         | GBA2/IO41PPB1   | E9         | GCB2/IO52PPI  |  |

| B1         | GAA2/IO118UPB3  | F1         | VCCPLF        |  |

| B2         | GAB0/IO02RSB0   | F2         | VCOMPLF       |  |

| B3         | GAC1/IO05RSB0   | F3         | GND           |  |

| B4         | IO11RSB0        | F4         | GND           |  |

| B5         | IO23RSB0        | F5         | VCCIB2        |  |

| B6         | GBC0/IO35RSB0   | F6         | GND           |  |

| B7         | GBB1/IO38RSB0   | F7         | GDA1/IO60US   |  |

| B8         | IO41NPB1        | F8         | GDC1/IO58UD   |  |

| B9         | GBB2/IO42PSB1   | F9         | GDC0/IO58VD   |  |

| C1         | GAB2/IO117UPB3  | G1         | GEA0/IO98ND   |  |

| C2         | IO118VPB3       | G2         | GEC1/IO100PD  |  |

| C3         | GND             | G3         | GEC0/IO100ND  |  |

| C4         | IO15RSB0        | G4         | IO91RSB2      |  |

| C5         | IO25RSB0        | G5         | IO86RSB2      |  |

| C6         | GND             | G6         | IO71RSB2      |  |

| C7         | GBA0/IO39RSB0   | G7         | GDB2/IO62RS   |  |

| C8         | GBC2/IO43PDB1   | G8         | VJTAG         |  |

| C9         | IO43NDB1        | G9         | TRST          |  |

| D1         | GAC2/IO116USB3  | H1         | GEA1/IO98PDI  |  |

| D2         | IO117VPB3       | H2         | FF/GEB2/IO96R |  |

| D3         | GFA2/IO107PSB3  | H3         | IO93RSB2      |  |

| D4         | VCC             | H4         | IO90RSB2      |  |

| D5         | VCCIB0          | H5         | IO85RSB2      |  |

| D6         | GND             | H6         | IO77RSB2      |  |

| D7         | IO52NPB1        | H7         | GDA2/IO61RS   |  |

| D8         | GCC1/IO48PDB1   | H8         | TDI           |  |

| D9         | GCC0/IO48NDB1   | H9         | TDO           |  |

| CS81       |                 |  |  |

|------------|-----------------|--|--|

| Pin Number | AGL250 Function |  |  |

| J1         | GEA2/IO97RSB2   |  |  |

| J2         | GEC2/IO95RSB2   |  |  |

| J3         | IO92RSB2        |  |  |

| J4         | IO88RSB2        |  |  |

| J5         | IO84RSB2        |  |  |

| J6         | IO74RSB2        |  |  |

| J7         | ТСК             |  |  |

| J8         | TMS             |  |  |

| J9         | VPUMP           |  |  |

Package Pin Assignments

| CS196                      |                |                            | CS196          |            | CS196           |  |  |

|----------------------------|----------------|----------------------------|----------------|------------|-----------------|--|--|

| Pin Number AGL250 Function |                | Pin Number AGL250 Function |                | Pin Number | AGL250 Function |  |  |

| A1                         | GND            | C9                         | IO30RSB0       | F3         | IO111PDB3       |  |  |

| A2                         | GAA0/IO00RSB0  | C10                        | IO33RSB0       | F4         | IO111NDB3       |  |  |

| A3                         | GAC0/IO04RSB0  | C11                        | VCCIB0         | F5         | IO113NPB3       |  |  |

| A4                         | GAC1/IO05RSB0  | C12                        | IO41NPB1       | F6         | IO06RSB0        |  |  |

| A5                         | IO10RSB0       | C13                        | GNDQ           | F7         | VCC             |  |  |

| A6                         | IO13RSB0       | C14                        | IO42NDB1       | F8         | VCC             |  |  |

| A7                         | IO17RSB0       | D1                         | IO116VDB3      | F9         | IO28RSB0        |  |  |

| A8                         | IO19RSB0       | D2                         | IO117VDB3      | F10        | IO54PDB1        |  |  |

| A9                         | IO23RSB0       | D3                         | GAA2/IO118UDB3 | F11        | IO54NDB1        |  |  |

| A10                        | GBC0/IO35RSB0  | D4                         | IO113PPB3      | F12        | IO47NDB1        |  |  |

| A11                        | GBB0/IO37RSB0  | D5                         | IO08RSB0       | F13        | IO47PDB1        |  |  |

| A12                        | GBB1/IO38RSB0  | D6                         | IO14RSB0       | F14        | IO45NDB1        |  |  |

| A13                        | GBA1/IO40RSB0  | D7                         | IO15RSB0       | G1         | GFB1/IO109PDB3  |  |  |

| A14                        | GND            | D8                         | IO18RSB0       | G2         | GFA0/IO108NDB3  |  |  |

| B1                         | VCCIB3         | D9                         | IO25RSB0       | G3         | GFA2/IO107PPB3  |  |  |

| B2                         | VMV0           | D10                        | IO32RSB0       | G4         | VCOMPLF         |  |  |

| B3                         | GAA1/IO01RSB0  | D11                        | IO44PPB1       | G5         | GFC0/IO110NDB3  |  |  |

| B4                         | GAB1/IO03RSB0  | D12                        | VMV1           | G6         | VCC             |  |  |

| B5                         | GND            | D13                        | IO43NDB1       | G7         | GND             |  |  |

| B6                         | IO12RSB0       | D14                        | GBC2/IO43PDB1  | G8         | GND             |  |  |

| B7                         | IO16RSB0       | E1                         | IO112PDB3      | G9         | VCC             |  |  |

| B8                         | IO22RSB0       | E2                         | GND            | G10        | GCC0/IO48NDB1   |  |  |

| B9                         | IO24RSB0       | E3                         | IO118VDB3      | G11        | GCB1/IO49PDB1   |  |  |

| B10                        | GND            | E4                         | VCCIB3         | G12        | GCA0/IO50NDB1   |  |  |

| B11                        | GBC1/IO36RSB0  | E5                         | IO114USB3      | G13        | IO53NDB1        |  |  |

| B12                        | GBA0/IO39RSB0  | E6                         | IO07RSB0       | G14        | GCC2/IO53PDB1   |  |  |

| B13                        | GBA2/IO41PPB1  | E7                         | IO09RSB0       | H1         | GFB0/IO109NDB3  |  |  |

| B14                        | GBB2/IO42PDB1  | E8                         | IO21RSB0       | H2         | GFA1/IO108PDB3  |  |  |

| C1                         | GAC2/IO116UDB3 | E9                         | IO31RSB0       | H3         | VCCPLF          |  |  |

| C2                         | GAB2/IO117UDB3 | E10                        | IO34RSB0       | H4         | GFB2/IO106PPB3  |  |  |

| C3                         | GNDQ           | E11                        | VCCIB1         | H5         | GFC1/IO110PDB3  |  |  |

| C4                         | VCCIB0         | E12                        | IO44NPB1       | H6         | VCC             |  |  |

| C5                         | GAB0/IO02RSB0  | E13                        | GND            | H7         | GND             |  |  |

| C6                         | IO11RSB0       | E14                        | IO45PDB1       | H8         | GND             |  |  |

| C7                         | VCCIB0         | F1                         | IO112NDB3      | H9         | VCC             |  |  |

| C8                         | IO20RSB0       | F2                         | IO107NPB3      | H10        | GCC1/IO48PDB1   |  |  |

Package Pin Assignments

| QN132      |                 |  |  |

|------------|-----------------|--|--|

| Pin Number | AGL030 Function |  |  |

| C17        | IO47RSB1        |  |  |

| C18        | NC              |  |  |

| C19        | ТСК             |  |  |

| C20        | NC              |  |  |

| C21        | VPUMP           |  |  |

| C22        | VJTAG           |  |  |

| C23        | NC              |  |  |

| C24        | NC              |  |  |

| C25        | NC              |  |  |

| C26        | GDB0/IO34RSB0   |  |  |

| C27        | NC              |  |  |

| C28        | VCCIB0          |  |  |

| C29        | IO28RSB0        |  |  |

| C30        | IO25RSB0        |  |  |

| C31        | IO24RSB0        |  |  |

| C32        | IO21RSB0        |  |  |

| C33        | NC              |  |  |

| C34        | NC              |  |  |

| C35        | VCCIB0          |  |  |

| C36        | IO13RSB0        |  |  |

| C37        | IO10RSB0        |  |  |

| C38        | IO07RSB0        |  |  |

| C39        | IO03RSB0        |  |  |

| C40        | IO00RSB0        |  |  |

| D1         | GND             |  |  |

| D2         | GND             |  |  |

| D3         | GND             |  |  |

| D4         | GND             |  |  |

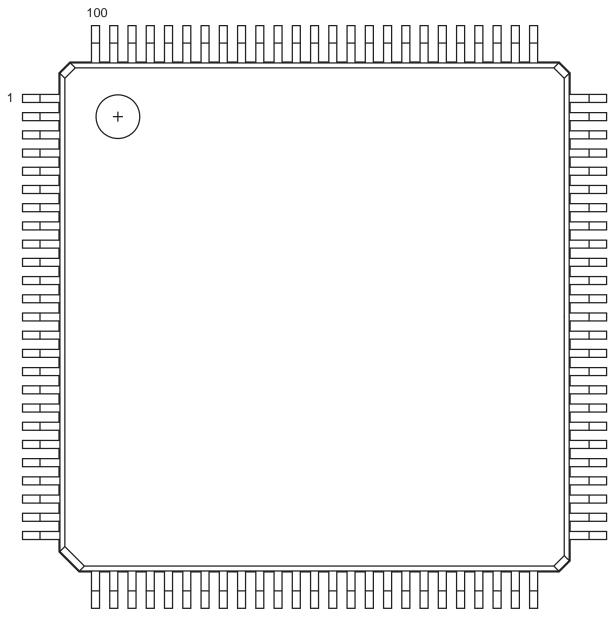

# VQ100

Note: This is the top view of the package.

# Note

For more information on package drawings, see PD3068: Package Mechanical Drawings.

IGLOO Low Power Flash FPGAs

| FG256      |                 | FG256      |                 | FG256      |                 |  |

|------------|-----------------|------------|-----------------|------------|-----------------|--|

| Pin Number | AGL400 Function | Pin Number | AGL400 Function | Pin Number | AGL400 Function |  |

| H3         | GFB1/IO146PPB3  | K9         | GND             | M15        | GDC1/IO77UDB1   |  |

| H4         | VCOMPLF         | K10        | GND             | M16        | IO75NDB1        |  |

| H5         | GFC0/IO147NPB3  | K11        | VCC             | N1         | IO140NDB3       |  |

| H6         | VCC             | K12        | VCCIB1          | N2         | IO138PPB3       |  |

| H7         | GND             | K13        | IO71NPB1        | N3         | GEC1/IO137PPB3  |  |

| H8         | GND             | K14        | IO74RSB1        | N4         | IO131RSB2       |  |

| H9         | GND             | K15        | IO72NPB1        | N5         | GNDQ            |  |

| H10        | GND             | K16        | IO70NDB1        | N6         | GEA2/IO134RSB2  |  |

| H11        | VCC             | L1         | IO142NDB3       | N7         | IO117RSB2       |  |

| H12        | GCC0/IO67NPB1   | L2         | IO141NPB3       | N8         | IO111RSB2       |  |

| H13        | GCB1/IO68PPB1   | L3         | IO125RSB2       | N9         | IO99RSB2        |  |

| H14        | GCA0/IO69NPB1   | L4         | IO139RSB3       | N10        | IO94RSB2        |  |

| H15        | NC              | L5         | VCCIB3          | N11        | IO87RSB2        |  |

| H16        | GCB0/IO68NPB1   | L6         | GND             | N12        | GNDQ            |  |

| J1         | GFA2/IO144PPB3  | L7         | VCC             | N13        | IO93RSB2        |  |

| J2         | GFA1/IO145PDB3  | L8         | VCC             | N14        | VJTAG           |  |

| J3         | VCCPLF          | L9         | VCC             | N15        | GDC0/IO77VDB1   |  |

| J4         | IO143NDB3       | L10        | VCC             | N16        | GDA1/IO79UDB1   |  |

| J5         | GFB2/IO143PDB3  | L11        | GND             | P1         | GEB1/IO136PDB3  |  |

| J6         | VCC             | L12        | VCCIB1          | P2         | GEB0/IO136NDB3  |  |

| J7         | GND             | L13        | GDB0/IO78VPB1   | P3         | VMV2            |  |

| J8         | GND             | L14        | IO76VDB1        | P4         | IO129RSB2       |  |

| J9         | GND             | L15        | IO76UDB1        | P5         | IO128RSB2       |  |

| J10        | GND             | L16        | IO75PDB1        | P6         | IO122RSB2       |  |

| J11        | VCC             | M1         | IO140PDB3       | P7         | IO115RSB2       |  |

| J12        | GCB2/IO71PPB1   | M2         | IO130RSB2       | P8         | IO110RSB2       |  |

| J13        | GCA1/IO69PPB1   | M3         | IO138NPB3       | P9         | IO98RSB2        |  |

| J14        | GCC2/IO72PPB1   | M4         | GEC0/IO137NPB3  | P10        | IO95RSB2        |  |

| J15        | NC              | M5         | VMV3            | P11        | IO88RSB2        |  |

| J16        | GCA2/IO70PDB1   | M6         | VCCIB2          | P12        | IO84RSB2        |  |

| K1         | GFC2/IO142PDB3  | M7         | VCCIB2          | P13        | TCK             |  |

| K2         | IO144NPB3       | M8         | IO108RSB2       | P14        | VPUMP           |  |

| K3         | IO141PPB3       | M9         | IO101RSB2       | P15        | TRST            |  |

| K4         | IO120RSB2       | M10        | VCCIB2          | P16        | GDA0/IO79VDB1   |  |

| K5         | VCCIB3          | M11        | VCCIB2          | R1         | GEA1/IO135PDB3  |  |

| K6         | VCC             | M12        | VMV2            | R2         | GEA0/IO135NDB3  |  |

| K7         | GND             | M13        | IO83RSB2        | R3         | IO127RSB2       |  |

| K8         | GND             | M14        | GDB1/IO78UPB1   | R4         | GEC2/IO132RSB2  |  |

|            | FG484           |  |  |  |  |

|------------|-----------------|--|--|--|--|

| Pin Number | AGL400 Function |  |  |  |  |

| N17        | IO74RSB1        |  |  |  |  |

| N18        | IO72NPB1        |  |  |  |  |

| N19        | IO70NDB1        |  |  |  |  |

| N20        | NC              |  |  |  |  |

| N21        | NC              |  |  |  |  |

| N22        | NC              |  |  |  |  |

| P1         | NC              |  |  |  |  |

| P2         | NC              |  |  |  |  |

| P3         | NC              |  |  |  |  |

| P4         | IO142NDB3       |  |  |  |  |

| P5         | IO141NPB3       |  |  |  |  |

| P6         | IO125RSB2       |  |  |  |  |

| P7         | IO139RSB3       |  |  |  |  |

| P8         | VCCIB3          |  |  |  |  |

| P9         | GND             |  |  |  |  |

| P10        | VCC             |  |  |  |  |

| P11        | VCC             |  |  |  |  |

| P12        | VCC             |  |  |  |  |

| P13        | VCC             |  |  |  |  |

| P14        | GND             |  |  |  |  |

| P15        | VCCIB1          |  |  |  |  |

| P16        | GDB0/IO78VPB1   |  |  |  |  |

| P17        | IO76VDB1        |  |  |  |  |

| P18        | IO76UDB1        |  |  |  |  |

| P19        | IO75PDB1        |  |  |  |  |

| P20        | NC              |  |  |  |  |

| P21        | NC              |  |  |  |  |

| P22        | NC              |  |  |  |  |

| R1         | NC              |  |  |  |  |

| R2         | NC              |  |  |  |  |

| R3         | VCC             |  |  |  |  |

| R4         | IO140PDB3       |  |  |  |  |

| R5         | IO130RSB2       |  |  |  |  |

| R6         | IO138NPB3       |  |  |  |  |

| R7         | GEC0/IO137NPB3  |  |  |  |  |

| R8         | VMV3            |  |  |  |  |

Package Pin Assignments

| FG484                      |                   |  |  |  |

|----------------------------|-------------------|--|--|--|

| Pin Number AGL400 Function |                   |  |  |  |

| V15                        | IO85RSB2          |  |  |  |

| V16                        | GDB2/IO81RSB2     |  |  |  |

| V17                        | TDI               |  |  |  |

| V18                        | NC                |  |  |  |

| V19                        | TDO               |  |  |  |

| V20                        | GND               |  |  |  |

| V21                        | NC                |  |  |  |

| V22                        | NC                |  |  |  |

| W1                         | NC                |  |  |  |

| W2                         | NC                |  |  |  |

| W3                         | NC                |  |  |  |

| W4                         | GND               |  |  |  |

| W5                         | IO126RSB2         |  |  |  |

| W6                         | FF/GEB2/IO133RSB2 |  |  |  |

| W7                         | IO124RSB2         |  |  |  |

| W8                         | IO116RSB2         |  |  |  |

| W9                         | IO113RSB2         |  |  |  |

| W10                        | IO107RSB2         |  |  |  |

| W11                        | IO105RSB2         |  |  |  |

| W12                        | IO102RSB2         |  |  |  |

| W13                        | IO97RSB2          |  |  |  |

| W14                        | IO92RSB2          |  |  |  |

| W15                        | GDC2/IO82RSB2     |  |  |  |

| W16                        | IO86RSB2          |  |  |  |

| W17                        | GDA2/IO80RSB2     |  |  |  |

| W18                        | TMS               |  |  |  |

| W19                        | GND               |  |  |  |

| W20                        | NC                |  |  |  |

| W21                        | NC                |  |  |  |

| W22                        | NC                |  |  |  |

| Y1                         | VCCIB3            |  |  |  |

| Y2                         | NC                |  |  |  |

| Y3                         | NC                |  |  |  |

| Y4                         | NC                |  |  |  |

| Y5                         | GND               |  |  |  |

| Y6                         | NC                |  |  |  |

| FG484      |                 |  |  |

|------------|-----------------|--|--|

| Pin Number | AGL600 Function |  |  |

| K11        | GND             |  |  |

| K12        | GND             |  |  |

| K13        | GND             |  |  |

| K14        | VCC             |  |  |

| K15        | VCCIB1          |  |  |

| K16        | GCC1/IO69PPB1   |  |  |

| K17        | IO65NPB1        |  |  |

| K18        | IO75PDB1        |  |  |

| K19        | IO75NDB1        |  |  |

| K20        | NC              |  |  |

| K21        | IO76NDB1        |  |  |

| K22        | IO76PDB1        |  |  |

| L1         | NC              |  |  |

| L2         | IO155PDB3       |  |  |

| L3         | NC              |  |  |

| L4         | GFB0/IO163NPB3  |  |  |

| L5         | GFA0/IO162NDB3  |  |  |

| L6         | GFB1/IO163PPB3  |  |  |

| L7         | VCOMPLF         |  |  |

| L8         | GFC0/IO164NPB3  |  |  |

| L9         | VCC             |  |  |

| L10        | GND             |  |  |

| L11        | GND             |  |  |

| L12        | GND             |  |  |

| L13        | GND             |  |  |

| L14        | VCC             |  |  |

| L15        | GCC0/IO69NPB1   |  |  |

| L16        | GCB1/IO70PPB1   |  |  |

| L17        | GCA0/IO71NPB1   |  |  |

| L18        | IO67NPB1        |  |  |

| L19        | GCB0/IO70NPB1   |  |  |

| L20        | IO77PDB1        |  |  |

| L21        | IO77NDB1        |  |  |

| L22        | IO78NPB1        |  |  |

| M1         | NC              |  |  |

| M2         | IO155NDB3       |  |  |

| FG484                       |           |  |  |  |

|-----------------------------|-----------|--|--|--|

| Pin Number AGL1000 Function |           |  |  |  |

| AA15                        | NC        |  |  |  |

| AA16                        | IO122RSB2 |  |  |  |

| AA17                        | IO119RSB2 |  |  |  |

| AA18                        | IO117RSB2 |  |  |  |

| AA19                        | NC        |  |  |  |

| AA20                        | NC        |  |  |  |

| AA21                        | VCCIB1    |  |  |  |

| AA22                        | GND       |  |  |  |

| AB1                         | GND       |  |  |  |

| AB2                         | GND       |  |  |  |

| AB3                         | VCCIB2    |  |  |  |

| AB4                         | IO180RSB2 |  |  |  |

| AB5                         | IO176RSB2 |  |  |  |

| AB6                         | IO173RSB2 |  |  |  |

| AB7                         | IO167RSB2 |  |  |  |

| AB8                         | IO162RSB2 |  |  |  |

| AB9                         | IO156RSB2 |  |  |  |

| AB10                        | IO150RSB2 |  |  |  |

| AB11                        | IO145RSB2 |  |  |  |

| AB12                        | IO144RSB2 |  |  |  |

| AB13                        | IO132RSB2 |  |  |  |

| AB14                        | IO127RSB2 |  |  |  |

| AB15                        | IO126RSB2 |  |  |  |

| AB16                        | IO123RSB2 |  |  |  |

| AB17                        | IO121RSB2 |  |  |  |

| AB18                        | IO118RSB2 |  |  |  |

| AB19                        | NC        |  |  |  |

| AB20                        | VCCIB2    |  |  |  |

| AB21                        | GND       |  |  |  |

| AB22                        | GND       |  |  |  |

| B1                          | GND       |  |  |  |

| B2                          | VCCIB3    |  |  |  |

| B3                          | NC        |  |  |  |

| B4                          | IO06RSB0  |  |  |  |

| B5                          | IO08RSB0  |  |  |  |

| B6                          | IO12RSB0  |  |  |  |

|                             |           |  |  |  |

| FG484      |                  |  |  |  |

|------------|------------------|--|--|--|

| Pin Number | AGL1000 Function |  |  |  |

| Y7         | IO174RSB2        |  |  |  |

| Y8         | VCC              |  |  |  |

| Y9         | VCC              |  |  |  |

| Y10        | IO154RSB2        |  |  |  |

| Y11        | IO148RSB2        |  |  |  |

| Y12        | IO140RSB2        |  |  |  |

| Y13        | NC               |  |  |  |

| Y14        | VCC              |  |  |  |

| Y15        | VCC              |  |  |  |

| Y16        | NC               |  |  |  |

| Y17        | NC               |  |  |  |

| Y18        | GND              |  |  |  |

| Y19        | NC               |  |  |  |

| Y20        | NC               |  |  |  |

| Y21        | NC               |  |  |  |

| Y22        | VCCIB1           |  |  |  |

IGLOO Low Power Flash FPGAs

| Revision / Version                                  | Changes                                                                                                                                                                                                                                                              | Page         |

|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Revision 18 (Nov 2009)                              | The version changed to v2.0 for IGLOO datasheet chapters, indicating the datasheet contains information based on final characterization. Please review the datasheet carefully as most tables were updated with new data.                                            | N/A          |

| Revision 17 (Sep 2009)<br>Product Brief v1.6        | The "Reprogrammable Flash Technology" section was modified to add "250 MHz (1.5 V systems) and 160 MHz (1.2 V systems) System Performance."                                                                                                                          | I            |

|                                                     | "IGLOO Ordering Information" was revised to note that halogen-free packages are available with RoHS-compliant packaging.                                                                                                                                             |              |

|                                                     | Table 1-1 • I/O Standards Supported is new.                                                                                                                                                                                                                          | 1-7          |

|                                                     | The definitions of hot-swap and cold-sparing were added to the "I/Os with Advanced I/O Standards" section.                                                                                                                                                           | 1-7          |

| Revision 16 (Apr 2009)<br>Product Brief v1.5        | M1AGL400 is no longer offered and was removed from the "IGLOO Devices" product table, "IGLOO Ordering Information", and "Temperature Grade Offerings".                                                                                                               | I, III, IV   |

|                                                     | The –F speed grade is no longer offered for IGLOO devices. The speed grade column and note regarding –F speed grade were removed from "IGLOO Ordering Information". The "Speed Grade and Temperature Grade Matrix" section was removed.                              | III, IV      |

|                                                     | This datasheet now has fully characterized data and has moved from being Advance to a Production version. The version number changed from Advance v0.5 to v2.0.                                                                                                      | N/A          |

|                                                     | Please review the datasheet carefully as most tables were updated with new data.                                                                                                                                                                                     |              |

| DC and Switching<br>Characteristics<br>Advance v0.6 | $3.3~\rm V$ LVCMOS and 1.2 V LVCMOS Wide Range support was added to the datasheet. This affects all tables that contained 3.3 V LVCMOS and 1.2 V LVCMOS data.                                                                                                        |              |

|                                                     | $\rm I_{\rm IL}$ and $\rm I_{\rm IH}$ input leakage current information was added to all "Minimum and Maximum DC Input and Output Levels" tables.                                                                                                                    | N/A          |

|                                                     | -F was removed from the datasheet. The speed grade is no longer supported.                                                                                                                                                                                           | N/A          |

|                                                     | The notes in Table 2-2 • Recommended Operating Conditions 1 were updated.                                                                                                                                                                                            | 2-2          |

|                                                     | Table 2-4 • Overshoot and Undershoot Limits 1 was updated.                                                                                                                                                                                                           | 2-3          |

|                                                     | Table 2-5 • Package Thermal Resistivities was updated.                                                                                                                                                                                                               | 2-6          |

|                                                     | Table 2-6 • Temperature and Voltage Derating Factors for Timing Delays (normalized to $TJ = 70^{\circ}$ C, VCC = 1.425 V) and Table 2-7 • Temperature and Voltage Derating Factors for Timing Delays (normalized to $TJ = 70^{\circ}$ C, VCC = 1.14 V) were updated. | 2-7          |

|                                                     | In Table 2-191 • RAM4K9 and Table 2-193 • RAM4K9, the following specifications were removed:                                                                                                                                                                         | 2-122<br>and |

|                                                     | twro                                                                                                                                                                                                                                                                 | 2-124        |

|                                                     | tсскн                                                                                                                                                                                                                                                                |              |

|                                                     | In Table 2-192 • RAM512X18 and Table 2-194 • RAM512X18, the following specifications were removed:                                                                                                                                                                   | 2-123<br>and |

|                                                     | twro                                                                                                                                                                                                                                                                 | 2-125        |

|                                                     | tсскн                                                                                                                                                                                                                                                                |              |

| Revision 15 (Feb 2009)                              | The "QN132" pin table for the AGL060 device is new.                                                                                                                                                                                                                  | 4-31         |

| Packaging v1.9                                      |                                                                                                                                                                                                                                                                      |              |