Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                        |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | XC800                                                                           |

| Core Size                  | 8-Bit                                                                           |

| Speed                      | 24MHz                                                                           |

| Connectivity               | SSI, UART/USART                                                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 34                                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | · ·                                                                             |

| RAM Size                   | 1.75K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                     |

| Data Converters            | A/D 8x10b                                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 48-LQFP                                                                         |

| Supplier Device Package    | PG-TQFP-48                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/saf-xc886-8ffa-5v-ac |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Summary of Features

Features: (continued)

- Power-on reset generation

- Brownout detection for core logic supply

- On-chip OSC and PLL for clock generation

- PLL loss-of-lock detection

- Power saving modes

- slow-down mode

- idle mode

- power-down mode with wake-up capability via RXD or EXINT0

- clock gating control to each peripheral

- Programmable 16-bit Watchdog Timer (WDT)

- Six ports

- Up to 48 pins as digital I/O

- 8 pins as digital/analog input

- 8-channel, 10-bit ADC

- Four 16-bit timers

- Timer 0 and Timer 1 (T0 and T1)

- Timer 2 and Timer 21 (T2 and T21)

- Multiplication/Division Unit for arithmetic operations (MDU)

- Software libraries to support floating point and MDU calculations

- CORDIC Coprocessor for computation of trigonometric, hyperbolic and linear functions

- MultiCAN with 2 nodes, 32 message objects

- Capture/compare unit for PWM signal generation (CCU6)

- Two full-duplex serial interfaces (UART and UART1)

- Synchronous serial channel (SSC)

- On-chip debug support

- 1 Kbyte of monitor ROM (part of the 12-Kbyte Boot ROM)

- 64 bytes of monitor RAM

- Packages:

- PG-TQFP-48

- PG-TQFP-64

- Temperature range *T*<sub>A</sub>:

- SAF (-40 to 85 °C)

- SAK (-40 to 125 °C)

## **General Device Information**

# 2.2 Logic Symbol

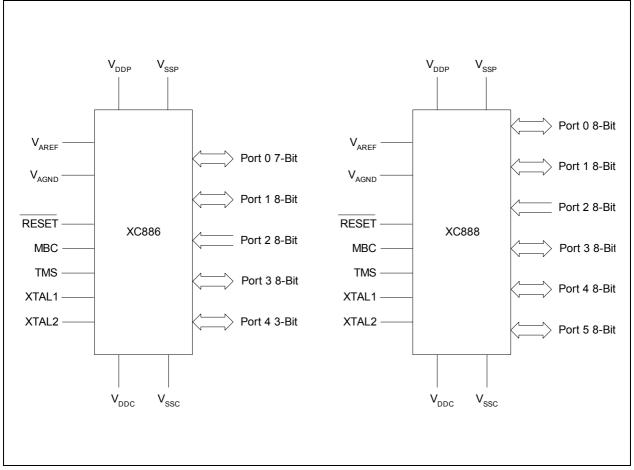

The logic symbols of the XC886/888 are shown in Figure 3.

Figure 3 XC886/888 Logic Symbol

SYSCON0

#### **Functional Description**

#### System Control Register 0 Reset Value: 04 7 5 4 3 2 1 0 6 IMODE 1 RMAP 0 0 0 r r r r rw rw

| Field | Bits          | Туре | Description                                                                                                                                                    |

|-------|---------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RMAP  | 0             | rw   | <ul> <li>Interrupt Node XINTR0 Enable</li> <li>The access to the standard SFR area is enabled</li> <li>The access to the mapped SFR area is enabled</li> </ul> |

| 1     | 2             | r    | <b>Reserved</b><br>Returns 1 if read; should be written with 1.                                                                                                |

| 0     | [7:5],<br>3,1 | r    | <b>Reserved</b><br>Returns 0 if read; should be written with 0.                                                                                                |

Note: The RMAP bit should be cleared/set by ANL or ORL instructions.

# 3.2.2.2 Address Extension by Paging

Address extension is further performed at the module level by paging. With the address extension by mapping, the XC886/888 has a 256-SFR address range. However, this is still less than the total number of SFRs needed by the on-chip peripherals. To meet this requirement, some peripherals have a built-in local address extension mechanism for increasing the number of addressable SFRs. The extended address range is not directly controlled by the CPU instruction itself, but is derived from bit field PAGE in the module page register MOD\_PAGE. Hence, the bit field PAGE must be programmed before accessing the SFR of the target module. Each module may contain a different number of pages and a different number of SFRs per page, depending on the specific requirement. Besides setting the correct RMAP bit value to select the SFR area, the user must also ensure that a valid PAGE is selected to target the desired SFR. A page inside the extended address range can be selected as shown in **Figure 9**.

# 3.2.4 XC886/888 Register Overview

The SFRs of the XC886/888 are organized into groups according to their functional units. The contents (bits) of the SFRs are summarized in **Chapter 3.2.4.1** to **Chapter 3.2.4.14**.

Note: The addresses of the bitaddressable SFRs appear in bold typeface.

# 3.2.4.1 CPU Registers

The CPU SFRs can be accessed in both the standard and mapped memory areas (RMAP = 0 or 1).

| Addr            | Register Name                                            | Bit       | 7         | 6    | 5    | 4           | 3         | 2    | 1    | 0          |

|-----------------|----------------------------------------------------------|-----------|-----------|------|------|-------------|-----------|------|------|------------|

| RMAP =          | = 0 or 1                                                 | I.        |           |      |      |             |           |      |      |            |

| 81 <sub>H</sub> | SP Reset: 07 <sub>H</sub>                                | Bit Field |           |      |      | S           | P         |      |      |            |

|                 | Stack Pointer Register                                   | Туре      |           |      |      | r           | W         |      |      |            |

| 82 <sub>H</sub> | DPL Reset: 00 <sub>H</sub>                               | Bit Field | DPL7      | DPL6 | DPL5 | DPL4        | DPL3      | DPL2 | DPL1 | DPL0       |

|                 | Data Pointer Register Low                                | Туре      | rw        | rw   | rw   | rw          | rw        | rw   | rw   | rw         |

| 83 <sub>H</sub> | DPH Reset: 00 <sub>H</sub>                               | Bit Field | DPH7      | DPH6 | DPH5 | DPH4        | DPH3      | DPH2 | DPH1 | DPH0       |

|                 | Data Pointer Register High                               | Туре      | rw        | rw   | rw   | rw          | rw        | rw   | rw   | rw         |

| 87 <sub>H</sub> | PCON Reset: 00 <sub>H</sub>                              | Bit Field | SMOD      |      | 0    |             | GF1       | GF0  | 0    | IDLE       |

|                 | Power Control Register                                   | Туре      | rw        |      | r    |             | rw        | rw   | r    | rw         |

| <sup>88</sup> H | TCON Reset: 00 <sub>H</sub>                              | Bit Field | TF1       | TR1  | TF0  | TR0         | IE1       | IT1  | IE0  | IT0        |

|                 | Timer Control Register                                   | Туре      | rwh       | rw   | rwh  | rw          | rwh       | rw   | rwh  | rw         |

| 89 <sub>H</sub> | TMOD Reset: 00 <sub>H</sub><br>Timer Mode Register       | Bit Field | GATE<br>1 | T1S  | T1   | 1M          | GATE<br>0 | TOS  | T    | M          |

|                 |                                                          | Туре      | rw        | rw   | r    | w           | rw        | rw   | r    | w          |

| 8A <sub>H</sub> | TL0 Reset: 00 <sub>H</sub>                               | Bit Field |           | •    |      | V           | AL        | •    |      |            |

|                 | Timer 0 Register Low                                     | Туре      |           |      |      | rv          | vh        |      |      |            |

| 8B <sub>H</sub> | TL1 Reset: 00 <sub>H</sub>                               | Bit Field |           |      |      | V           | AL        |      |      |            |

|                 | Timer 1 Register Low                                     | Туре      |           |      |      | rv          | vh        |      |      |            |

| 8C <sub>H</sub> | THO Reset: 00 <sub>H</sub>                               | Bit Field |           |      |      | V           | AL        |      |      |            |

|                 | Timer 0 Register High                                    | Туре      |           |      |      | rv          | vh        |      |      |            |

| 8D <sub>H</sub> | TH1 Reset: 00 <sub>H</sub>                               | Bit Field |           |      |      | V           | AL        |      |      |            |

|                 | Timer 1 Register High                                    | Туре      |           |      |      | rv          | vh        |      |      |            |

| 98 <sub>H</sub> | SCON Reset: 00 <sub>H</sub>                              | Bit Field | SM0       | SM1  | SM2  | REN         | TB8       | RB8  | TI   | RI         |

|                 | Serial Channel Control Register                          | Туре      | rw        | rw   | rw   | rw          | rw        | rwh  | rwh  | rwh        |

| 99 <sub>H</sub> | SBUF Reset: 00 <sub>H</sub>                              | Bit Field |           |      |      | V           | AL        |      |      |            |

|                 | Serial Data Buffer Register                              | Туре      |           |      |      | rv          | vh        |      |      |            |

| A2 <sub>H</sub> | EO Reset: 00 <sub>H</sub><br>Extended Operation Register | Bit Field |           | 0    |      | TRAP_<br>EN |           | 0    |      | DPSE<br>L0 |

|                 |                                                          | Туре      |           | r    |      | rw          |           | r    |      | rw         |

#### Table 5 CPU Register Overview

| Addr            | Register Name              | Bit       | 7        | 6 | 5 | 4  | 3  | 2 | 1 | 0 |  |

|-----------------|----------------------------|-----------|----------|---|---|----|----|---|---|---|--|

| B3 <sub>H</sub> | MR1 Reset: 00 <sub>H</sub> | Bit Field |          |   |   | DA | TA |   |   |   |  |

|                 | MDU Result Register 1      | Туре      |          |   |   | r  | h  |   |   |   |  |

| B4 <sub>H</sub> | MD2 Reset: 00 <sub>H</sub> | Bit Field |          |   |   | DA | TA |   |   |   |  |

|                 | MDU Operand Register 2     | Туре      |          |   |   | r  | w  |   |   |   |  |

| B4 <sub>H</sub> | MR2 Reset: 00 <sub>H</sub> | Bit Field |          |   |   | DA | TA |   |   |   |  |

|                 | MDU Result Register 2      | Туре      |          |   |   | r  | h  |   |   |   |  |

| в5 <sub>Н</sub> | MD3 Reset: 00 <sub>H</sub> | Bit Field |          |   |   | DA | TA |   |   |   |  |

|                 | MDU Operand Register 3     | Туре      | rw       |   |   |    |    |   |   |   |  |

| в5 <sub>Н</sub> | MR3 Reset: 00 <sub>H</sub> | Bit Field | eld DATA |   |   |    |    |   |   |   |  |

|                 | MDU Result Register 3      | Туре      |          |   |   | r  | h  |   |   |   |  |

| B6 <sub>H</sub> | MD4 Reset: 00 <sub>H</sub> | Bit Field |          |   |   | DA | TA |   |   |   |  |

|                 | MDU Operand Register 4     | Туре      |          |   |   | r  | w  |   |   |   |  |

| B6 <sub>H</sub> | MR4 Reset: 00 <sub>H</sub> | Bit Field |          |   |   | DA | TA |   |   |   |  |

|                 | MDU Result Register 4      | Туре      |          |   |   | r  | h  |   |   |   |  |

| в7 <sub>Н</sub> | MD5 Reset: 00 <sub>H</sub> | Bit Field |          |   |   | DA | TA |   |   |   |  |

|                 | MDU Operand Register 5     | Туре      |          |   |   | r  | w  |   |   |   |  |

| в7 <sub>Н</sub> | MR5 Reset: 00 <sub>H</sub> | Bit Field |          |   |   | DA | TA |   |   |   |  |

|                 | MDU Result Register 5      | Туре      |          |   |   | r  | 'n |   |   |   |  |

#### Table 6MDU Register Overview (cont'd)

# 3.2.4.3 CORDIC Registers

The CORDIC SFRs can be accessed in the mapped memory area (RMAP = 1).

#### Table 7 CORDIC Register Overview

| Addr            | Register Name                    | Bit       | 7 | 6 | 5 | 4  | 3   | 2 | 1 | 0 |

|-----------------|----------------------------------|-----------|---|---|---|----|-----|---|---|---|

| RMAP =          | = 1                              |           |   |   |   |    |     | 1 |   |   |

| 9A <sub>H</sub> | CD_CORDXL Reset: 00 <sub>H</sub> | Bit Field |   |   |   | DA | TAL |   |   |   |

|                 | CORDIC X Data Low Byte           | Туре      |   |   |   | r  | W   |   |   |   |

| 9B <sub>H</sub> | CD_CORDXH Reset: 00 <sub>H</sub> | Bit Field |   |   |   | DA | TAH |   |   |   |

|                 | CORDIC X Data High Byte          | Туре      |   |   |   | r  | W   |   |   |   |

| 9CH             | CD_CORDYL Reset: 00 <sub>H</sub> | Bit Field |   |   |   | DA | TAL |   |   |   |

|                 | CORDIC Y Data Low Byte           | Туре      |   |   |   | r  | W   |   |   |   |

| 9D <sub>H</sub> | CD_CORDYH Reset: 00 <sub>H</sub> | Bit Field |   |   |   | DA | TAH |   |   |   |

|                 | CORDIC Y Data High Byte          | Туре      |   |   |   | r  | W   |   |   |   |

| 9E <sub>H</sub> | CD_CORDZL Reset: 00 <sub>H</sub> | Bit Field |   |   |   | DA | TAL |   |   |   |

|                 | CORDIC Z Data Low Byte           | Туре      |   |   |   | r  | W   |   |   |   |

| 9F <sub>H</sub> | CD_CORDZH Reset: 00 <sub>H</sub> | Bit Field |   |   |   | DA | ТАН |   |   |   |

|                 | CORDIC Z Data High Byte          | Туре      |   |   |   | r  | W   |   |   |   |

### Table 8SCU Register Overview (cont'd)

| Addr            | Register Name                                                          | Bit       | 7          | 6           | 5            | 4           | 3            | 2             | 1           | 0           |

|-----------------|------------------------------------------------------------------------|-----------|------------|-------------|--------------|-------------|--------------|---------------|-------------|-------------|

| вс <sub>Н</sub> | NMISR Reset: 00 <sub>H</sub><br>NMI Status Register                    | Bit Field | 0          | FNMI<br>ECC | FNMI<br>VDDP | FNMI<br>VDD | FNMI<br>OCDS | FNMI<br>FLASH | FNMI<br>PLL | FNMI<br>WDT |

|                 |                                                                        | Туре      | r          | rwh         | rwh          | rwh         | rwh          | rwh           | rwh         | rwh         |

| вd <sub>Н</sub> | BCON Reset: 00 <sub>H</sub>                                            | Bit Field | BG         | SEL         | 0            | BRDIS       |              | BRPRE         |             | R           |

|                 | Baud Rate Control Register                                             | Туре      | r          | N           | r            | rw          |              | rw rv         |             |             |

| be <sub>h</sub> | BG Reset: 00 <sub>H</sub>                                              | Bit Field |            |             |              | BR_V        | ALUE         |               |             |             |

|                 | Baud Rate Timer/Reload<br>Register                                     | Туре      |            |             |              | rv          | h            |               |             |             |

| E9 <sub>H</sub> | FDCON Reset: 00 <sub>H</sub><br>Fractional Divider Control<br>Register | Bit Field | BGS        | SYNE<br>N   | ERRS<br>YN   | EOFS<br>YN  | BRK          | NDOV          | FDM         | FDEN        |

|                 | Register                                                               | Туре      | rw         | rw          | rwh          | rwh         | rwh          | rwh           | rw          | rw          |

| EA <sub>H</sub> | FDSTEP Reset: 00 <sub>H</sub>                                          | Bit Field |            |             |              | ST          | EP           |               |             |             |

|                 | Fractional Divider Reload<br>Register                                  | Туре      |            |             |              | r           | N            |               |             |             |

| EB <sub>H</sub> | FDRES Reset: 00 <sub>H</sub>                                           | Bit Field |            |             |              | RES         | ULT          |               |             |             |

|                 | Fractional Divider Result<br>Register                                  | Туре      |            |             |              | r           | h            |               |             |             |

| RMAP =          | : 0, PAGE 1                                                            |           |            |             |              |             |              |               |             |             |

| вз <sub>Н</sub> | ID Reset: UU <sub>H</sub>                                              | Bit Field |            |             | PRODID       |             |              | VERID         |             |             |

|                 | Identity Register                                                      | Туре      |            |             | r            |             | r            |               |             |             |

| B4 <sub>H</sub> | PMCON0 Reset: 00 <sub>H</sub><br>Power Mode Control Register 0         | Bit Field | 0          | WDT<br>RST  | WKRS         | WK<br>SEL   | SD           | PD            | V           | /S          |

|                 |                                                                        | Туре      | r          | rwh         | rwh          | rw          | rw           | rwh           | r           | w           |

| в5 <sub>Н</sub> | PMCON1 Reset: 00 <sub>H</sub><br>Power Mode Control Register 1         | Bit Field | 0          | CDC_<br>DIS | CAN_<br>DIS  | MDU_<br>DIS | T2_<br>DIS   | CCU_<br>DIS   | SSC_<br>DIS | ADC_<br>DIS |

|                 |                                                                        | Туре      | r          | rw          | rw           | rw          | rw           | rw            | rw          | rw          |

| в6 <sub>Н</sub> | OSC_CON Reset: 08 <sub>H</sub><br>OSC Control Register                 | Bit Field |            | 0           |              | OSC<br>PD   | XPD          | OSC<br>SS     | ORD<br>RES  | OSCR        |

|                 |                                                                        | Туре      |            | r           |              | rw          | rw           | rw            | rwh         | rh          |

| в7 <sub>Н</sub> | PLL_CON Reset: 90 <sub>H</sub><br>PLL Control Register                 | Bit Field |            | N           | VIV          |             | VCO<br>BYP   | OSC<br>DISC   | RESL<br>D   | LOCK        |

|                 |                                                                        | Туре      |            | r           | w            |             | rw           | rw            | rwh         | rh          |

| ва <sub>Н</sub> | CMCON Reset: 10 <sub>H</sub><br>Clock Control Register                 | Bit Field | VCO<br>SEL | KDIV        | 0            | FCCF<br>G   |              | CLK           | REL         |             |

|                 |                                                                        | Туре      | rw         | rw          | r            | rw          |              | n             | N           |             |

| вв <sub>Н</sub> | PASSWD Reset: 07 <sub>H</sub><br>Password Register                     | Bit Field |            |             | PASS         |             |              | PROT<br>ECT_S | MC          | DE          |

|                 |                                                                        | Туре      |            |             | wh           |             |              | rh            | r           | w           |

| вс <sub>Н</sub> | FEAL Reset: 00 <sub>H</sub>                                            | Bit Field |            |             |              | ECCER       | RADDR        | DDR           |             |             |

|                 | Flash Error Address Register                                           | Туре      |            |             |              | r           | <br>ו        |               |             |             |

| вd <sub>Н</sub> | FEAH Reset: 00 <sub>H</sub>                                            | Bit Field |            |             |              | ECCER       | RADDR        |               |             |             |

|                 | Flash Error Address Register                                           | Туре      |            |             |              | r           | h            |               |             |             |

# Table 11ADC Register Overview (cont'd)

| Addr            | Register Name                                                         | Bit       | 7          | 6          | 5          | 4          | 3          | 2          | 1          | 0          |

|-----------------|-----------------------------------------------------------------------|-----------|------------|------------|------------|------------|------------|------------|------------|------------|

| D3 <sub>H</sub> | ADC_RESR3H Reset: 00 <sub>H</sub>                                     | Bit Field |            |            |            | RES        | ULT        |            |            |            |

|                 | Result Register 3 High                                                | Туре      |            |            |            | r          | h          |            |            |            |

| RMAP =          | 0, PAGE 3                                                             |           |            |            |            |            |            |            |            |            |

| CA <sub>H</sub> | ADC_RESRA0L Reset: 00 <sub>H</sub>                                    | Bit Field |            | RESULT     |            | VF         | DRC        |            | CHNR       |            |

|                 | Result Register 0, View A Low                                         | Туре      |            | rh         |            | rh         | rh         |            | rh         |            |

| св <sub>Н</sub> | ADC_RESRA0H Reset: 00 <sub>H</sub>                                    | Bit Field |            |            |            | RES        | SULT       |            |            |            |

|                 | Result Register 0, View A High                                        | Туре      |            |            |            | r          | h          |            |            |            |

| сс <sub>Н</sub> | ADC_RESRA1L Reset: 00 <sub>H</sub>                                    | Bit Field |            | RESULT     |            | VF         | DRC        |            | CHNR       |            |

|                 | Result Register 1, View A Low                                         | Туре      |            | rh         |            | rh         | rh         |            | rh         |            |

| CD <sub>H</sub> | ADC_RESRA1H Reset: 00 <sub>H</sub>                                    | Bit Field |            |            |            | RES        | SULT       |            |            |            |

|                 | Result Register 1, View A High                                        | Туре      |            |            |            | r          | h          |            |            |            |

| Ce <sub>H</sub> | ADC_RESRA2L Reset: 00 <sub>H</sub>                                    | Bit Field |            | RESULT     |            | VF         | DRC        |            | CHNR       |            |

|                 | Result Register 2, View A Low                                         | Туре      |            | rh         |            | rh         | rh         |            | rh         |            |

| CF <sub>H</sub> | ADC_RESRA2H Reset: 00 <sub>H</sub>                                    | Bit Field |            |            |            | RES        | SULT       |            |            |            |

|                 | Result Register 2, View A High                                        | Туре      |            |            |            | r          | h          |            |            |            |

| D2 <sub>H</sub> | ADC_RESRA3L Reset: 00 <sub>H</sub>                                    | Bit Field |            | RESULT     |            | VF         | DRC        |            | CHNR       |            |

|                 | Result Register 3, View A Low                                         | Туре      |            | rh         |            | rh         | rh         |            | rh         |            |

| D3 <sub>H</sub> | ADC_RESRA3H Reset: 00 <sub>H</sub>                                    | Bit Field |            |            |            | RES        | ULT        |            |            |            |

|                 | Result Register 3, View A High                                        | Туре      |            |            |            | r          | h          |            |            |            |

| RMAP =          | = 0, PAGE 4                                                           |           |            |            |            |            |            |            |            |            |

| CA <sub>H</sub> | ADC_RCR0 Reset: 00 <sub>H</sub><br>Result Control Register 0          | Bit Field | VFCT<br>R  | WFR        | 0          | IEN        |            | 0          |            | DRCT<br>R  |

|                 |                                                                       | Туре      | rw         | rw         | r          | rw         |            | r          |            | rw         |

| св <sub>Н</sub> | ADC_RCR1 Reset: 00 <sub>H</sub><br>Result Control Register 1          | Bit Field | VFCT<br>R  | WFR        | 0          | IEN        |            | 0          |            | DRCT<br>R  |

|                 |                                                                       | Туре      | rw         | rw         | r          | rw         |            | r          |            | rw         |

| сс <sup>н</sup> | ADC_RCR2 Reset: 00 <sub>H</sub><br>Result Control Register 2          | Bit Field | VFCT<br>R  | WFR        | 0          | IEN        |            | 0          |            | DRCT<br>R  |

|                 |                                                                       | Туре      | rw         | rw         | r          | rw         |            | r          |            | rw         |

| CDH             | ADC_RCR3 Reset: 00 <sub>H</sub><br>Result Control Register 3          | Bit Field | VFCT<br>R  | WFR        | 0          | IEN        |            | 0          |            | DRCT<br>R  |

|                 |                                                                       | Туре      | rw         | rw         | r          | rw         |            | r          |            | rw         |

| Ce <sub>H</sub> | ADC_VFCR Reset: 00 <sub>H</sub>                                       | Bit Field |            |            | ט          |            | VFC3       | VFC2       | VFC1       | VFC0       |

|                 | Valid Flag Clear Register                                             | Туре      |            |            | r          |            | w          | w          | w          | w          |

| RMAP =          | = 0, PAGE 5                                                           |           |            |            |            |            |            |            |            |            |

| CA <sub>H</sub> | ADC_CHINFR Reset: 00 <sub>H</sub><br>Channel Interrupt Flag Register  | Bit Field | CHINF<br>7 | CHINF<br>6 | CHINF<br>5 | CHINF<br>4 | CHINF<br>3 | CHINF<br>2 | CHINF<br>1 | CHINF<br>0 |

|                 |                                                                       | Туре      | rh         |

| св <sub>Н</sub> | ADC_CHINCR Reset: 00 <sub>H</sub><br>Channel Interrupt Clear Register | Bit Field | CHINC<br>7 | CHINC<br>6 | CHINC<br>5 | CHINC<br>4 | CHINC<br>3 | CHINC<br>2 | CHINC<br>1 | CHINC<br>0 |

|                 |                                                                       | Туре      | w          | w          | w          | w          | w          | w          | w          | w          |

# Table 11ADC Register Overview (cont'd)

| Addr            | Register Name                                                          | Bit       | 7          | 6          | 5          | 4          | 3          | 2          | 1          | 0          |

|-----------------|------------------------------------------------------------------------|-----------|------------|------------|------------|------------|------------|------------|------------|------------|

| cc <sup>H</sup> | ADC_CHINSR Reset: 00 <sub>H</sub><br>Channel Interrupt Set Register    | Bit Field | CHINS<br>7 | CHINS<br>6 | CHINS<br>5 | CHINS<br>4 | CHINS<br>3 | CHINS<br>2 | CHINS<br>1 | CHINS<br>0 |

|                 |                                                                        | Туре      | w          | w          | w          | w          | w          | W          | w          | w          |

| CD <sub>H</sub> | ADC_CHINPR Reset: 00 <sub>H</sub><br>Channel Interrupt Node Pointer    | Bit Field | CHINP<br>7 | CHINP<br>6 | CHINP<br>5 | CHINP<br>4 | CHINP<br>3 | CHINP<br>2 | CHINP<br>1 | CHINP<br>0 |

|                 | Register                                                               | Туре      | rw         |

| Ceh             | ADC_EVINFR Reset: 00 <sub>H</sub><br>Event Interrupt Flag Register     | Bit Field | EVINF<br>7 | EVINF<br>6 | EVINF<br>5 | EVINF<br>4 | (          | )          | EVINF<br>1 | EVINF<br>0 |

|                 |                                                                        | Туре      | rh         | rh         | rh         | rh         |            | r          | rh         | rh         |

| CF <sub>H</sub> | ADC_EVINCR Reset: 00 <sub>H</sub><br>Event Interrupt Clear Flag        | Bit Field | EVINC<br>7 | EVINC<br>6 | EVINC<br>5 | EVINC<br>4 | (          | )          | EVINC<br>1 | EVINC<br>0 |

|                 | Register                                                               | Туре      | w          | w          | w          | w          |            | r          | w          | w          |

| D2 <sub>H</sub> | ADC_EVINSR Reset: 00 <sub>H</sub><br>Event Interrupt Set Flag Register | Bit Field | EVINS<br>7 | EVINS<br>6 | EVINS<br>5 | EVINS<br>4 | (          | )          | EVINS<br>1 | EVINS<br>0 |

|                 |                                                                        | Туре      | w          | w          | w          | w          |            | r          | w          | w          |

| D3 <sub>H</sub> | ADC_EVINPR Reset: 00 <sub>H</sub><br>Event Interrupt Node Pointer      | Bit Field | EVINP<br>7 | EVINP<br>6 | EVINP<br>5 | EVINP<br>4 | (          | )          | EVINP<br>1 | EVINP<br>0 |

|                 | Register                                                               | Туре      | rw         | rw         | rw         | rw         |            | r          | rw         | rw         |

| RMAP =          | = 0, PAGE 6                                                            |           |            |            |            |            |            |            |            |            |

| CA <sub>H</sub> | ADC_CRCR1 Reset: 00 <sub>H</sub>                                       | Bit Field | CH7        | CH6        | CH5        | CH4        |            | (          | )          |            |

|                 | Conversion Request Control<br>Register 1                               | Туре      | rwh        | rwh        | rwh        | rwh        |            | I          | r          |            |

| св <sub>Н</sub> | ADC_CRPR1 Reset: 00 <sub>H</sub>                                       | Bit Field | CHP7       | CHP6       | CHP5       | CHP4       |            | (          | )          |            |

|                 | Conversion Request Pending<br>Register 1                               | Туре      | rwh        | rwh        | rwh        | rwh        |            | I          | r          |            |

| сс <sup>н</sup> | ADC_CRMR1 Reset: 00 <sub>H</sub><br>Conversion Request Mode            | Bit Field | Rsv        | LDEV       | CLRP<br>ND | SCAN       | ENSI       | ENTR       | 0          | ENGT       |

|                 | Register 1                                                             | Туре      | r          | w          | w          | rw         | rw         | rw         | r          | rw         |

| CD <sub>H</sub> | ADC_QMR0 Reset: 00 <sub>H</sub><br>Queue Mode Register 0               | Bit Field | CEV        | TREV       | FLUS<br>H  | CLRV       | 0          | ENTR       | 0          | ENGT       |

|                 |                                                                        | Туре      | w          | w          | w          | w          | r          | rw         | r          | rw         |

| Ceh             | ADC_QSR0 Reset: 20 <sub>H</sub><br>Queue Status Register 0             | Bit Field | Rsv        | 0          | EMPT<br>Y  | EV         | (          | )          | FI         | LL         |

|                 |                                                                        | Туре      | r          | r          | rh         | rh         |            | r          | r          | h          |

| CF <sub>H</sub> | ADC_Q0R0 Reset: 00 <sub>H</sub>                                        | Bit Field | EXTR       | ENSI       | RF         | V          | 0          | F          | REQCHN     | २          |

|                 | Queue 0 Register 0                                                     | Туре      | rh         | rh         | rh         | rh         | r          |            | rh         |            |

| D2 <sub>H</sub> | ADC_QBUR0 Reset: 00 <sub>H</sub>                                       | Bit Field | EXTR       | ENSI       | RF         | V          | 0          | F          | REQCHN     | ۲          |

|                 | Queue Backup Register 0                                                | Туре      | rh         | rh         | rh         | rh         | r          |            | rh         |            |

| D2 <sub>H</sub> | ADC_QINR0 Reset: 00 <sub>H</sub>                                       | Bit Field | EXTR       | ENSI       | RF         | (          | )          | F          | REQCHN     | २          |

|                 | Queue Input Register 0                                                 | Туре      | w          | w          | w          |            | r          |            | w          |            |

# Table 14CCU6 Register Overview (cont'd)

| Addr            | Register Name                                                         | Bit       | 7   | 6    | 5         | 4    | 3          | 2        | 1        | 0    |

|-----------------|-----------------------------------------------------------------------|-----------|-----|------|-----------|------|------------|----------|----------|------|

| FA <sub>H</sub> | CCU6_CC60SRL Reset: 00 <sub>H</sub>                                   | Bit Field |     |      | <u> </u>  | CC6  | OSL        | <u> </u> | <u> </u> |      |

|                 | Capture/Compare Shadow Register<br>for Channel CC60 Low               | Туре      |     |      |           | rv   | vh         |          |          |      |

| FB <sub>H</sub> | CCU6_CC60SRH Reset: 00 <sub>H</sub>                                   | Bit Field |     |      |           | CC6  | 0SH        |          |          |      |

|                 | Capture/Compare Shadow Register<br>for Channel CC60 High              | Туре      |     |      |           | rv   | vh         |          |          |      |

| FC <sub>H</sub> | CCU6_CC61SRL Reset: 00 <sub>H</sub>                                   | Bit Field |     |      |           | CC6  | 51SL       |          |          |      |

|                 | Capture/Compare Shadow Register<br>for Channel CC61 Low               | Туре      |     |      |           | rv   | vh         |          |          |      |

| FD <sub>H</sub> | CCU6_CC61SRH Reset: 00 <sub>H</sub>                                   | Bit Field |     |      |           | CC6  | 1SH        |          |          |      |

|                 | Capture/Compare Shadow Register<br>for Channel CC61 High              | Туре      |     |      |           | rv   | vh         |          |          |      |

| Fe <sub>H</sub> | CCU6_CC62SRL Reset: 00 <sub>H</sub>                                   | Bit Field |     |      |           | CC6  | 2SL        |          |          |      |

|                 | Capture/Compare Shadow Register<br>for Channel CC62 Low               | Туре      |     |      |           | rv   | vh         |          |          |      |

| FF <sub>H</sub> | CCU6_CC62SRH Reset: 00 <sub>H</sub>                                   | Bit Field |     |      |           | CC6  | 2SH        |          |          |      |

|                 | Capture/Compare Shadow Register<br>for Channel CC62 High              | Туре      |     |      |           | rv   | vh         |          |          |      |

| RMAP =          | 0, PAGE 1                                                             |           |     |      |           |      |            |          |          |      |

| 9A <sub>H</sub> | CCU6_CC63RL Reset: 00 <sub>H</sub>                                    | Bit Field |     |      |           | CC6  | 3VL        |          |          |      |

|                 | Capture/Compare Register for<br>Channel CC63 Low                      | Туре      |     |      |           | r    | h          |          |          |      |

| 98 <sub>H</sub> | CCU6_CC63RH Reset: 00 <sub>H</sub>                                    | Bit Field |     |      |           | CC6  | 3VH        |          |          |      |

|                 | Capture/Compare Register for<br>Channel CC63 High                     | Туре      |     |      |           | r    | h          |          |          |      |

| 9CH             | CCU6_T12PRL Reset: 00 <sub>H</sub>                                    | Bit Field |     |      |           | T12  | PVL        |          |          |      |

|                 | Timer T12 Period Register Low                                         | Туре      |     |      |           | rv   | vh         |          |          |      |

| 9D <sub>H</sub> | CCU6_T12PRH Reset: 00 <sub>H</sub><br>Timer T12 Period Register High  | Bit Field |     |      |           | T12  | PVH        |          |          |      |

|                 |                                                                       | Туре      |     |      |           | rv   | vh         |          |          |      |

| 9E <sub>H</sub> | CCU6_T13PRLReset: 00HTimer T13 Period Register Low                    | Bit Field |     |      |           | T13  | PVL        |          |          |      |

|                 |                                                                       | Туре      |     |      |           | rv   | vh         |          |          |      |

| 9F <sub>H</sub> | CCU6_T13PRH Reset: 00 <sub>H</sub><br>Timer T13 Period Register High  | Bit Field |     |      |           | T13  | PVH        |          |          |      |

|                 |                                                                       | Туре      |     |      |           | rv   | vh         |          |          |      |

| A4 <sub>H</sub> | CCU6_T12DTCL Reset: 00 <sub>H</sub><br>Dead-Time Control Register for | Bit Field |     |      |           | D    | ΓM         |          |          |      |

|                 | Timer T12 Low                                                         | Туре      |     |      |           | r    | N          |          |          |      |

| А5 <sub>Н</sub> | CCU6_T12DTCH Reset: 00 <sub>H</sub><br>Dead-Time Control Register for | Bit Field | 0   | DTR2 | DTR1      | DTR0 | 0          | DTE2     | DTE1     | DTE0 |

|                 | Timer T12 High                                                        | Туре      | r   | rh   | rh        | rh   | r          | rw       | rw       | rw   |

| A6 <sub>H</sub> | CCU6_TCTR0L Reset: 00 <sub>H</sub><br>Timer Control Register 0 Low    | Bit Field | СТМ | CDIR | STE1<br>2 | T12R | T12<br>PRE |          | T12CLK   |      |

|                 |                                                                       | Туре      | rw  | rh   | rh        | rh   | rw         |          | rw       |      |

| А7 <sub>Н</sub> | CCU6_TCTR0H Reset: 00 <sub>H</sub><br>Timer Control Register 0 High   | Bit Field |     | 0    | STE1<br>3 | T13R | T13<br>PRE |          | T13CLK   |      |

|                 |                                                                       | Туре      |     | r    | rh        | rh   | rw         |          | rw       |      |

| FA <sub>H</sub> | CCU6_CC60RL Reset: 00 <sub>H</sub>                                    | Bit Field |     |      |           | CC6  | 60VL       |          |          |      |

|                 | Capture/Compare Register for<br>Channel CC60 Low                      | Туре      |     |      |           | r    | h          |          |          |      |

# Table 14CCU6 Register Overview (cont'd)

| Addr            | Register Name                                                        | Bit       | 7          | 6          | 5          | 4          | 3          | 2          | 1           | 0           |

|-----------------|----------------------------------------------------------------------|-----------|------------|------------|------------|------------|------------|------------|-------------|-------------|

| FB <sub>H</sub> | CCU6_CC60RH Reset: 00 <sub>H</sub>                                   | Bit Field |            | 1          | 1          | CC6        | 60VH       | 1          | 1           | 1           |

|                 | Capture/Compare Register for<br>Channel CC60 High                    | Туре      |            |            |            | r          | 'n         |            |             |             |

| FC <sub>H</sub> | CCU6_CC61RL Reset: 00 <sub>H</sub>                                   | Bit Field |            |            |            | CC6        | 61VL       |            |             |             |

|                 | Capture/Compare Register for<br>Channel CC61 Low                     | Туре      |            |            |            | r          | 'n         |            |             |             |

| FD <sub>H</sub> | CCU6_CC61RH Reset: 00 <sub>H</sub>                                   | Bit Field |            |            |            | CC6        | 61VH       |            |             |             |

|                 | Capture/Compare Register for<br>Channel CC61 High                    | Туре      | rh         |            |            |            |            |            |             |             |

| FE <sub>H</sub> | CCU6_CC62RL Reset: 00 <sub>H</sub>                                   | Bit Field |            |            |            | CC6        | 62VL       |            |             |             |

|                 | Capture/Compare Register for<br>Channel CC62 Low                     | Туре      |            |            |            | r          | h          |            |             |             |

| FF <sub>H</sub> | CCU6_CC62RH Reset: 00 <sub>H</sub>                                   | Bit Field |            |            |            | CC6        | 62VH       |            |             |             |

|                 | Capture/Compare Register for<br>Channel CC62 High                    | Туре      |            |            |            | r          | 'n         |            |             |             |

| RMAP =          | 0, PAGE 2                                                            | _         |            |            |            |            | _          |            |             |             |

| 9A <sub>H</sub> | CCU6_T12MSELL Reset: 00 <sub>H</sub>                                 | Bit Field |            | MS         | EL61       |            |            | MSE        | EL60        |             |

|                 | T12 Capture/Compare Mode Select<br>Register Low                      | Туре      |            | r          | w          |            |            | r          | w           |             |

| 9В <sub>Н</sub> | CCU6_T12MSELH Reset: 00 <sub>H</sub>                                 | Bit Field | DBYP       |            | HSYNC      |            |            | MSE        | EL62        |             |

|                 | T12 Capture/Compare Mode Select<br>Register High                     | Туре      | rw         |            | rw         |            |            | r          | w           |             |

| 9CH             | CCU6_IENL Reset: 00 <sub>H</sub>                                     | Bit Field | ENT1       | ENT1       | ENCC       | ENCC       | ENCC       | ENCC       | ENCC        | ENCC        |

|                 | Capture/Compare Interrupt Enable<br>Register Low                     |           | 2<br>PM    | 2<br>OM    | 62F        | 62R        | 61F        | 61R        | 60F         | 60R         |

|                 |                                                                      | Туре      | rw          | rw          |

| 9D <sub>H</sub> | CCU6_IENH Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Enable | Bit Field | EN<br>STR  | EN<br>IDLE | EN<br>WHE  | EN<br>CHE  | 0          | EN<br>TRPF | ENT1<br>3PM | ENT1<br>3CM |

|                 | Register High                                                        | Туре      | rw         | rw         | rw         | rw         | r          | rw         | rw          | rw          |

| 9E <sub>H</sub> | CCU6_INPL Reset: 40 <sub>H</sub>                                     | Bit Field | INP        | CHE        | INPO       | CC62       | INPO       | CC61       | INPO        | CC60        |

|                 | Capture/Compare Interrupt Node<br>Pointer Register Low               | Туре      | r          | w          | r          | w          | r          | w          | r           | w           |

| 9F <sub>H</sub> | CCU6_INPH Reset: 39 <sub>H</sub>                                     | Bit Field | (          | 0          | INP        | T13        | INF        | PT12       | INP         | ERR         |

|                 | Capture/Compare Interrupt Node<br>Pointer Register High              | Туре      |            | r          | r          | w          | r          | w          | r           | w           |

| A4 <sub>H</sub> | CCU6_ISSL Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Status | Bit Field | ST12<br>PM | ST12<br>OM | SCC6<br>2F | SCC6<br>2R | SCC6<br>1F | SCC6<br>1R | SCC6<br>0F  | SCC6<br>0R  |

|                 | Set Register Low                                                     | Туре      | w          | w          | w          | w          | w          | w          | w           | w           |

| A5 <sub>H</sub> | CCU6_ISSH Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Status | Bit Field | SSTR       | SIDLE      | SWHE       | SCHE       | SWH<br>C   | STRP<br>F  | ST13<br>PM  | ST13<br>CM  |

|                 | Set Register High                                                    | Туре      | w          | w          | w          | w          | w          | w          | w           | w           |

| A6 <sub>H</sub> | CCU6_PSLR Reset: 00 <sub>H</sub>                                     | Bit Field | PSL63      | 0          |            |            | P          | SL         | •           |             |

|                 | Passive State Level Register                                         | Туре      | rwh        | r          |            |            | rv         | vh         |             |             |

| а7 <sub>Н</sub> | CCU6_MCMCTR Reset: 00 <sub>H</sub>                                   | Bit Field | (          | 0          | SW         | SYN        | 0          |            | SWSEL       |             |

|                 | Multi-Channel Mode Control Register                                  | Туре      |            | r          | r          | w          | r          |            | rw          |             |

| FA <sub>H</sub> | CCU6_TCTR2LReset: 00HTimer Control Register 2 Low                    | Bit Field | 0          | T13        | TED        |            | T13TEC     |            | T13<br>SSC  | T12<br>SSC  |

|                 |                                                                      | Туре      | r          | r          | W          |            | rw         |            | rw          | rw          |

# **Functional Description**

| Interrupt<br>Source | Vector<br>Address | Assignment for<br>XC886/888                           | Enable Bit | SFR  |

|---------------------|-------------------|-------------------------------------------------------|------------|------|

| XINTR6              | 0033 <sub>H</sub> | MultiCAN Nodes 1 and 2                                | EADC       | IEN1 |

|                     |                   | ADC[1:0]                                              |            |      |

| XINTR7              | 003B <sub>H</sub> | SSC                                                   | ESSC       |      |

| XINTR8              | 0043 <sub>H</sub> | External Interrupt 2                                  | EX2        |      |

|                     |                   | T21                                                   |            |      |

|                     |                   | CORDIC                                                |            |      |

|                     |                   | UART1                                                 |            |      |

|                     |                   | UART1 Fractional Divider<br>(Normal Divider Overflow) |            |      |

|                     |                   | MDU[1:0]                                              | 1          |      |

| XINTR9              | 004B <sub>H</sub> | External Interrupt 3                                  | EXM        |      |

|                     |                   | External Interrupt 4                                  | 1          |      |

|                     |                   | External Interrupt 5                                  |            |      |

|                     |                   | External Interrupt 6                                  |            |      |

|                     |                   | MultiCAN Node 3                                       |            |      |

| XINTR10             | 0053 <sub>H</sub> | CCU6 INP0                                             | ECCIP0     |      |

|                     |                   | MultiCAN Node 4                                       |            |      |

| XINTR11             | 005B <sub>H</sub> | CCU6 INP1                                             | ECCIP1     |      |

|                     |                   | MultiCAN Node 5                                       |            |      |

| XINTR12             | 0063 <sub>H</sub> | CCU6 INP2                                             | ECCIP2     |      |

|                     |                   | MultiCAN Node 6                                       |            |      |

| XINTR13             | 006B <sub>H</sub> | CCU6 INP3                                             | ECCIP3     |      |

|                     |                   | MultiCAN Node 7                                       |            |      |

Table 25 shows the VCO range for the XC886/888.

| <i>f</i> <sub>vcomin</sub> | f <sub>VCOmax</sub> | $f_{\sf VCOFREEmin}$ | <b><i>f</i></b> <sub>VCOFREEmax</sub> | Unit |

|----------------------------|---------------------|----------------------|---------------------------------------|------|

| 150                        | 200                 | 20                   | 80                                    | MHz  |

| 100                        | 150                 | 10                   | 80                                    | MHz  |

# 3.8.1 Recommended External Oscillator Circuits

The oscillator circuit, a Pierce oscillator, is designed to work with both, an external crystal oscillator or an external stable clock source. It basically consists of an inverting amplifier and a feedback element with XTAL1 as input, and XTAL2 as output.

When using a crystal, a proper external oscillator circuitry must be connected to both pins, XTAL1 and XTAL2. The crystal frequency can be within the range of 4 MHz to 12 MHz. Additionally, it is necessary to have two load capacitances  $C_{X1}$  and  $C_{X2}$ , and depending on the crystal type, a series resistor  $R_{X2}$ , to limit the current. A test resistor  $R_Q$  may be temporarily inserted to measure the oscillation allowance (negative resistance) of the oscillator circuitry.  $R_Q$  values are typically specified by the crystal vendor. The  $C_{X1}$  and  $C_{X2}$  values shown in **Figure 25** can be used as starting points for the negative resistance evaluation and for non-productive systems. The exact values and related operating range are dependent on the crystal frequency and have to be determined and optimized together with the final target system is strongly recommended to verify the input amplitude at XTAL1 and to determine the actual oscillation allowance (margin negative resistance) for the oscillator-crystal system.

When using an external clock signal, the signal must be connected to XTAL1. XTAL2 is left open (unconnected).

The oscillator can also be used in combination with a ceramic resonator. The final circuitry must also be verified by the resonator vendor. **Figure 25** shows the recommended external oscillator circuitries for both operating modes, external crystal mode and external input clock mode.

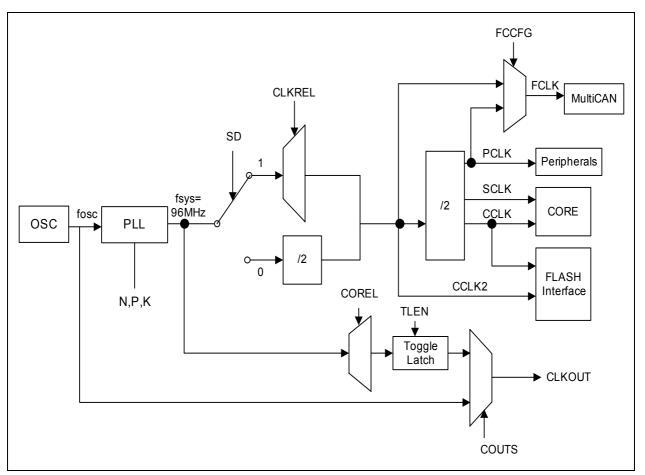

# 3.8.2 Clock Management

The CGU generates all clock signals required within the microcontroller from a single clock,  $f_{sys}$ . During normal system operation, the typical frequencies of the different modules are as follow:

- CPU clock: CCLK, SCLK = 24 MHz

- Fast clock (used by MultiCAN): FCLK = 24 or 48 MHz

- Peripheral clock: PCLK = 24 MHz

- Flash Interface clock: CCLK2 = 48 MHz and CCLK = 24 MHz

In addition, different clock frequencies can be output to pin CLKOUT (P0.0 or P0.7). The clock output frequency, which is derived from the clock output divider (bit COREL), can further be divided by 2 using toggle latch (bit TLEN is set to 1). The resulting output frequency has a 50% duty cycle. **Figure 26** shows the clock distribution of the XC886/888.

Figure 26 Clock Generation from  $f_{sys}$

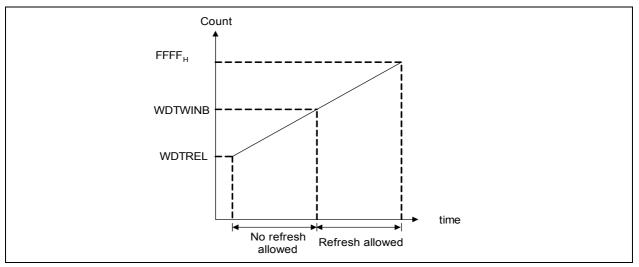

#### Figure 29 WDT Timing Diagram

**Table 27** lists the possible watchdog time ranges that can be achieved using a certain module clock. Some numbers are rounded to 3 significant digits.

#### Table 27Watchdog Time Ranges

| Reload value<br>In WDTREL          | Prescaler for <i>f</i> <sub>PCLK</sub> |                 |  |  |  |  |

|------------------------------------|----------------------------------------|-----------------|--|--|--|--|

|                                    | 2 (WDTIN = 0)                          | 128 (WDTIN = 1) |  |  |  |  |

|                                    | 24 MHz                                 | 24 MHz          |  |  |  |  |

| FF <sub>H</sub>                    | 21.3 μs                                | 1.37 ms         |  |  |  |  |

| FF <sub>H</sub><br>7F <sub>H</sub> | 2.75 ms                                | 176 ms          |  |  |  |  |

| 00 <sub>H</sub>                    | 5.46 ms                                | 350 ms          |  |  |  |  |

needed for the handshaking between the master and slave tasks is provided by the master task through the header portion of the frame.

The header consists of a break and synch pattern followed by an identifier. Among these three fields, only the break pattern cannot be transmitted as a normal 8-bit UART data. The break must contain a dominant value of 13 bits or more to ensure proper synchronization of slave nodes.

In the LIN communication, a slave task is required to be synchronized at the beginning of the protected identifier field of frame. For this purpose, every frame starts with a sequence consisting of a break field followed by a synch byte field. This sequence is unique and provides enough information for any slave task to detect the beginning of a new frame and be synchronized at the start of the identifier field.

Upon entering LIN communication, a connection is established and the transfer speed (baud rate) of the serial communication partner (host) is automatically synchronized in the following steps:

STEP 1: Initialize interface for reception and timer for baud rate measurement

STEP 2: Wait for an incoming LIN frame from host

STEP 3: Synchronize the baud rate to the host

- STEP 4: Enter for Master Request Frame or for Slave Response Frame

- Note: Re-synchronization and setup of baud rate are always done for **every** Master Request Header or Slave Response Header LIN frame.

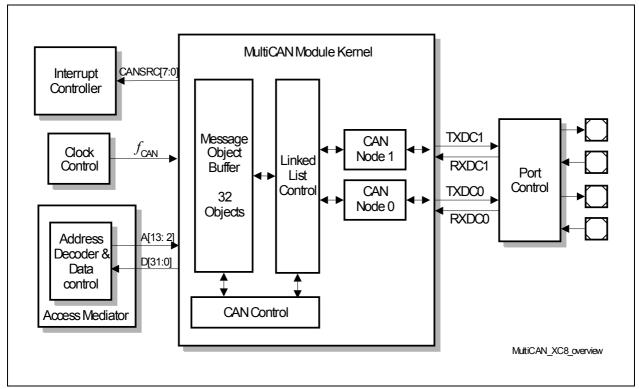

# 3.20 Controller Area Network (MultiCAN)

The MultiCAN module contains two Full-CAN nodes operating independently or exchanging data and remote frames via a gateway function. Transmission and reception of CAN frames is handled in accordance to CAN specification V2.0 B active. Each CAN node can receive and transmit standard frames with 11-bit identifiers as well as extended frames with 29-bit identifiers.

Both CAN nodes share a common set of message objects, where each message object may be individually allocated to one of the CAN nodes. Besides serving as a storage container for incoming and outgoing frames, message objects may be combined to build gateways between the CAN nodes or to setup a FIFO buffer.

The message objects are organized in double chained lists, where each CAN node has it's own list of message objects. A CAN node stores frames only into message objects that are allocated to the list of the CAN node. It only transmits messages from objects of this list. A powerful, command driven list controller performs all list operations.

The bit timings for the CAN nodes are derived from the peripheral clock ( $f_{CAN}$ ) and are programmable up to a data rate of 1 MBaud. A pair of receive and transmit pins connects each CAN node to a bus transceiver.

Figure 34 Overview of the MultiCAN

## Features

Compliant to ISO 11898.

#### **Electrical Parameters**

# 4.1.2 Absolute Maximum Rating

Maximum ratings are the extreme limits to which the XC886/888 can be subjected to without permanent damage.

| Parameter                                                    | Symbol            | Limi | it Values                              | Unit | Notes                               |  |

|--------------------------------------------------------------|-------------------|------|----------------------------------------|------|-------------------------------------|--|

|                                                              |                   | min. | max.                                   |      |                                     |  |

| Ambient temperature                                          | T <sub>A</sub>    | -40  | 125                                    | °C   | under bias                          |  |

| Storage temperature                                          | T <sub>ST</sub>   | -65  | 150                                    | °C   | 1)                                  |  |

| Junction temperature                                         | T <sub>J</sub>    | -40  | 150                                    | °C   | under bias <sup>1)</sup>            |  |

| Voltage on power supply pin with respect to $V_{\rm SS}$     | V <sub>DDP</sub>  | -0.5 | 6                                      | V    | 1)                                  |  |

| Voltage on any pin with respect to $V_{\rm SS}$              | V <sub>IN</sub>   | -0.5 | V <sub>DDP</sub> +<br>0.5 or<br>max. 6 | V    | whichever is<br>lower <sup>1)</sup> |  |

| Input current on any pin during overload condition           | I <sub>IN</sub>   | -10  | 10                                     | mA   | 1)                                  |  |

| Absolute sum of all input currents during overload condition | $\Sigma  I_{IN} $ | -    | 50                                     | mA   | 1)                                  |  |

| Table 4-1 | Absolute Maximum Rating Parameters |

|-----------|------------------------------------|

|-----------|------------------------------------|

1) Not subjected to production test, verified by design/characterization.

Note: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. During absolute maximum rating overload conditions ( $V_{IN} > V_{DDP}$  or  $V_{IN} < V_{SS}$ ) the voltage on  $V_{DDP}$  pin with respect to ground ( $V_{SS}$ ) must not exceed the values defined by the absolute maximum ratings.

Table 37

#### **Electrical Parameters**

#### **Operating Conditions** 4.1.3

The following operating conditions must not be exceeded in order to ensure correct operation of the XC886/888. All parameters mentioned in the following table refer to these operating conditions, unless otherwise noted.

| Parameter   |  | Symbol | Limit | Values | Unit | Notes/    |  |

|-------------|--|--------|-------|--------|------|-----------|--|

|             |  |        | min.  | max.   |      | Condition |  |

| Distigation |  | 17     | 4 5   |        | 11   |           |  |

**Operating Condition Parameters**

|                                      | •                |      |       |     |                   |

|--------------------------------------|------------------|------|-------|-----|-------------------|

|                                      |                  | min. | max.  |     | Conditions        |

| Digital power supply voltage         | $V_{DDP}$        | 4.5  | 5.5   | V   | 5V Device         |

| Digital power supply voltage         | V <sub>DDP</sub> | 3.0  | 3.6   | V   | 3.3V Device       |

| Digital ground voltage               | V <sub>SS</sub>  | 0    |       | V   |                   |

| Digital core supply voltage          | V <sub>DDC</sub> | 2.3  | 2.7   | V   |                   |

| System Clock Frequency <sup>1)</sup> | $f_{\rm SYS}$    | 88.8 | 103.2 | MHz |                   |

| Ambient temperature                  | T <sub>A</sub>   | -40  | 85    | °C  | SAF-<br>XC886/888 |

|                                      |                  | -40  | 125   | °C  | SAK-<br>XC886/888 |

1)  $f_{SYS}$  is the PLL output clock. During normal operating mode, CPU clock is  $f_{SYS}$  / 4. Please refer to Figure 26 for detailed description.

#### **Electrical Parameters**

## 4.3 AC Parameters

The electrical characteristics of the AC Parameters are detailed in this section.

## 4.3.1 Testing Waveforms

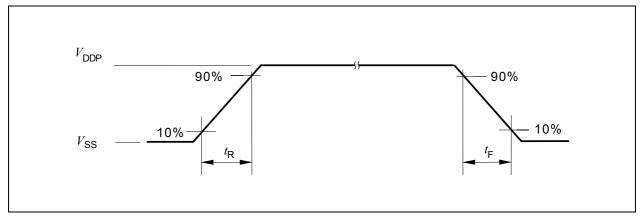

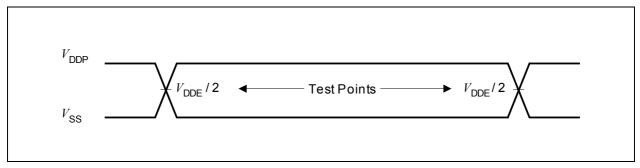

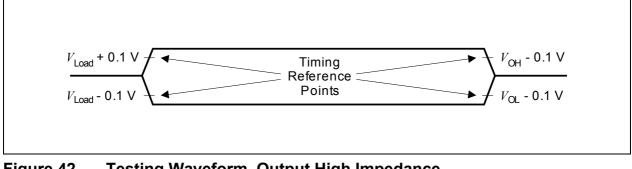

The testing waveforms for rise/fall time, output delay and output high impedance are shown in **Figure 40**, **Figure 41** and **Figure 42**.

Figure 40 Rise/Fall Time Parameters

Figure 41 Testing Waveform, Output Delay

Figure 42 Testing Waveform, Output High Impedance

### Package and Quality Declaration

# 5 Package and Quality Declaration

Chapter 5 provides the information of the XC886/888 package and reliability section.

## 5.1 Package Parameters

Table 1 provides the thermal characteristics of the package used in XC886 and XC888.

| Parameter                        | Symbol           |    | Limit Values |      | Unit | Notes |

|----------------------------------|------------------|----|--------------|------|------|-------|

|                                  |                  |    | Min.         | Max. |      |       |

| PG-TQFP-48 (XC886)               | 1                |    |              | - I  | l    |       |

| Thermal resistance junction case | R <sub>TJC</sub> | CC | -            | 13   | K/W  | 1)2)  |

| Thermal resistance junction lead | R <sub>TJL</sub> | CC | -            | 32.5 | K/W  | 1)2)_ |

| PG-TQFP-64 (XC888)               | •                |    |              |      |      |       |

| Thermal resistance junction case | R <sub>TJC</sub> | CC | -            | 12.6 | K/W  | 1)2)  |

| Thermal resistance junction lead | $R_{TJL}$        | CC | -            | 33.4 | K/W  | 1)2)  |

#### Table 1 Thermal Characteristics of the Packages

1) The thermal resistances between the case and the ambient  $(R_{TCA})$ , the lead and the ambient  $(R_{TLA})$  are to be combined with the thermal resistances between the junction and the case  $(R_{TJC})$ , the junction and the lead  $(R_{TJL})$  given above, in order to calculate the total thermal resistance between the junction and the ambient  $(R_{TJA})$ . The thermal resistances between the case and the ambient  $(R_{TCA})$ , the lead and the ambient  $(R_{TLA})$ . The thermal resistances between the case and the ambient  $(R_{TCA})$ , the lead and the ambient  $(R_{TLA})$  depend on the external system (PCB, case) characteristics, and are under user responsibility.

The junction temperature can be calculated using the following equation:  $T_J = T_A + R_{TJA} \times P_D$ , where the  $R_{TJA}$  is the total thermal resistance between the junction and the ambient. This total junction ambient resistance  $R_{TJA}$  can be obtained from the upper four partial thermal resistances, by

a) simply adding only the two thermal resistances (junction lead and lead ambient), or

b) by taking all four resistances into account, depending on the precision needed.

2) Not all parameters are 100% tested, but are verified by design/characterization and test correlation.