Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                         |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | XC800                                                                            |

| Core Size                  | 8-Bit                                                                            |

| Speed                      | 24MHz                                                                            |

| Connectivity               | SSI, UART/USART                                                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 34                                                                               |

| Program Memory Size        | 32KB (32K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 1.75К х 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 8x10b                                                                        |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 48-LQFP                                                                          |

| Supplier Device Package    | PG-TQFP-48                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/saf-xc886-8ffi-3v3-ac |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Summary of Features

Features: (continued)

- Power-on reset generation

- Brownout detection for core logic supply

- On-chip OSC and PLL for clock generation

- PLL loss-of-lock detection

- Power saving modes

- slow-down mode

- idle mode

- power-down mode with wake-up capability via RXD or EXINT0

- clock gating control to each peripheral

- Programmable 16-bit Watchdog Timer (WDT)

- Six ports

- Up to 48 pins as digital I/O

- 8 pins as digital/analog input

- 8-channel, 10-bit ADC

- Four 16-bit timers

- Timer 0 and Timer 1 (T0 and T1)

- Timer 2 and Timer 21 (T2 and T21)

- Multiplication/Division Unit for arithmetic operations (MDU)

- Software libraries to support floating point and MDU calculations

- CORDIC Coprocessor for computation of trigonometric, hyperbolic and linear functions

- MultiCAN with 2 nodes, 32 message objects

- Capture/compare unit for PWM signal generation (CCU6)

- Two full-duplex serial interfaces (UART and UART1)

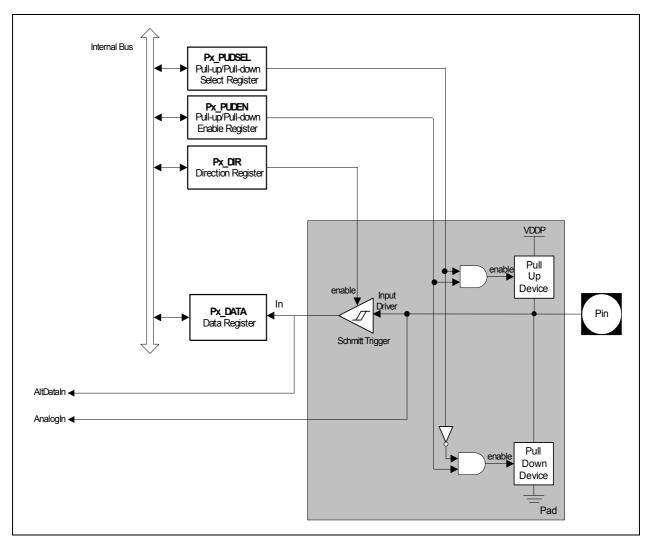

- Synchronous serial channel (SSC)

- On-chip debug support

- 1 Kbyte of monitor ROM (part of the 12-Kbyte Boot ROM)

- 64 bytes of monitor RAM

- Packages:

- PG-TQFP-48

- PG-TQFP-64

- Temperature range *T*<sub>A</sub>:

- SAF (-40 to 85 °C)

- SAK (-40 to 125 °C)

## **Summary of Features**

| Table 2Device Profile (cont'd) |

|--------------------------------|

|--------------------------------|

| Sales Type               | Device<br>Type | Program<br>Memory<br>(Kbytes) | Power<br>Supply<br>(V) | Temp-<br>erature<br>(°C) | Quality<br>Profile |

|--------------------------|----------------|-------------------------------|------------------------|--------------------------|--------------------|

| SAK-XC886*/888*-8FFA 3V3 | Flash          | 32                            | 3.3                    | -40 to 125               | Automotive         |

| SAK-XC886*/888*-6FFA 3V3 | Flash          | 24                            | 3.3                    | -40 to 125               | Automotive         |

| SAF-XC886*/888*-8FFA 3V3 | Flash          | 32                            | 3.3                    | -40 to 85                | Automotive         |

| SAF-XC886*/888*-6FFA 3V3 | Flash          | 24                            | 3.3                    | -40 to 85                | Automotive         |

| SAF-XC886*/888*-8FFI 3V3 | Flash          | 32                            | 3.3                    | -40 to 85                | Industrial         |

| SAF-XC886*/888*-6FFI 3V3 | Flash          | 24                            | 3.3                    | -40 to 85                | Industrial         |

- Note: The asterisk (\*) above denotes the device configuration letters from **Table 1**. Corresponding ROM derivatives will be available on request.

- Note: For variants with LIN BSL support, only LIN BSL is available regardless of the availability of the CAN module.

As this document refers to all the derivatives, some description may not apply to a specific product. For simplicity, all versions are referred to by the term XC886/888 throughout this document.

#### **Ordering Information**

The ordering code for Infineon Technologies microcontrollers provides an exact reference to the required product. This ordering code identifies:

- The derivative itself, i.e. its function set, the temperature range, and the supply voltage

- The package and the type of delivery

For the available ordering codes for the XC886/888, please refer to your responsible sales representative or your local distributor.

Note: The ordering codes for the Mask-ROM versions are defined for each product after verification of the respective ROM code.

#### **General Device Information**

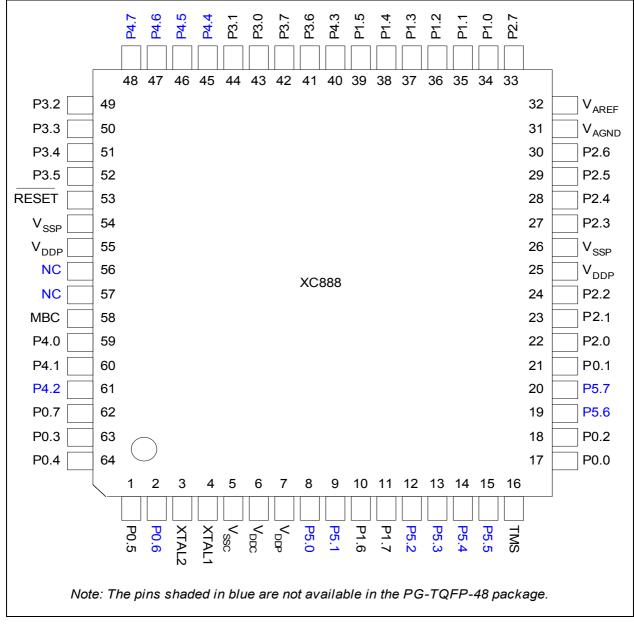

Figure 5 XC888 Pin Configuration, PG-TQFP-64 Package (top view)

# XC886/888CLM

## **General Device Information**

| Symbol | Pin Number<br>(TQFP-48/64) | Туре | Reset<br>State | Function                                 |                                                                                                                                                           |

|--------|----------------------------|------|----------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Р3     |                            | I/O  |                | I/O port. It ca                          | B-bit bidirectional general purpose<br>an be used as alternate functions<br>ART1, Timer 21 and MultiCAN.                                                  |

| P3.0   | 35/43                      |      | Hi-Z           | CCPOS1_2<br>CC60_0<br>RXDO1_1            | CCU6 Hall Input 1<br>Input/Output of<br>Capture/Compare channel 0<br>UART1 Transmit Data Output                                                           |

| P3.1   | 36/44                      |      | Hi-Z           | CCPOS0_2<br>CC61_2<br>COUT60_0<br>TXD1_1 | CCU6 Hall Input 0<br>Input/Output of<br>Capture/Compare channel 1<br>Output of Capture/Compare<br>channel 0<br>UART1 Transmit Data<br>Output/Clock Output |

| P3.2   | 37/49                      |      | Hi-Z           | CCPOS2_2<br>RXDC1_1<br>RXD1_1<br>CC61_0  | CCU6 Hall Input 2<br>MultiCAN Node 1 Receiver Input<br>UART1 Receive Data Input<br>Input/Output of<br>Capture/Compare channel 1                           |

| P3.3   | 38/50                      |      | Hi-Z           | COUT61_0<br>TXDC1_1                      | Output of Capture/Compare<br>channel 1<br>MultiCAN Node 1 Transmitter<br>Output                                                                           |

| P3.4   | 39/51                      |      | Hi-Z           | CC62_0<br>RXDC0_1<br>T2EX1_0             | Input/Output of<br>Capture/Compare channel 2<br>MultiCAN Node 0 Receiver Input<br>Timer 21 External Trigger Input                                         |

| P3.5   | 40/52                      |      | Hi-Z           | COUT62_0<br>EXF21_0<br>TXDC0_1           | Output of Capture/Compare<br>channel 2<br>Timer 21 External Flag Output<br>MultiCAN Node 0 Transmitter<br>Output                                          |

| P3.6   | 33/41                      |      | PD             | CTRAP_0                                  | CCU6 Trap Input                                                                                                                                           |

## Table 3Pin Definitions and Functions (cont'd)

## **General Device Information**

| Symbol | Pin Number<br>(TQFP-48/64) | Туре | Reset<br>State | Function         |                                                                                             |

|--------|----------------------------|------|----------------|------------------|---------------------------------------------------------------------------------------------|

| P5     |                            | I/O  |                | I/O port. It ca  | 8-bit bidirectional general purpose<br>an be used as alternate functions<br>IART1 and JTAG. |

| P5.0   | -/8                        |      | PU             | EXINT1_1         | External Interrupt Input 1                                                                  |

| P5.1   | -/9                        |      | PU             | EXINT2_1         | External Interrupt Input 2                                                                  |

| P5.2   | -/12                       |      | PU             | RXD_2            | UART Receive Data Input                                                                     |

| P5.3   | -/13                       |      | PU             | TXD_2            | UART Transmit Data<br>Output/Clock Output                                                   |

| P5.4   | _/14                       |      | PU             | RXDO_2           | UART Transmit Data Output                                                                   |

| P5.5   | -/15                       |      | PU             | TDO_2<br>TXD1_2  | JTAG Serial Data Output<br>UART1 Transmit Data Output/<br>Clock Output                      |

| P5.6   | -/19                       |      | PU             | TCK_2<br>RXDO1_2 | JTAG Clock Input<br>UART1 Transmit Data Output                                              |

| P5.7   | -/20                       |      | PU             | TDI_2<br>RXD1_2  | JTAG Serial Data Input<br>UART1 Receive Data Input                                          |

## Table 3Pin Definitions and Functions (cont'd)

## XC886/888CLM

#### **General Device Information**

| Symbol            | Pin Number<br>(TQFP-48/64) | Туре | Reset<br>State | Function                                                                                                     |

|-------------------|----------------------------|------|----------------|--------------------------------------------------------------------------------------------------------------|

| V <sub>DDP</sub>  | 7, 17, 43/<br>7, 25, 55    | _    | -              | <b>I/O Port Supply (3.3 or 5.0 V)</b><br>Also used by EVR and analog modules. All<br>pins must be connected. |

| $V_{\rm SSP}$     | 18, 42/26, 54              | _    | -              | I/O Port Ground<br>All pins must be connected.                                                               |

| $V_{DDC}$         | 6/6                        | _    | _              | Core Supply Monitor (2.5 V)                                                                                  |

| V <sub>SSC</sub>  | 5/5                        | _    | _              | Core Supply Ground                                                                                           |

| $V_{AREF}$        | 24/32                      | _    | _              | ADC Reference Voltage                                                                                        |

| $V_{AGND}$        | 23/31                      | _    | _              | ADC Reference Ground                                                                                         |

| XTAL1             | 4/4                        | I    | Hi-Z           | External Oscillator Input<br>(backup for on-chip OSC, normally NC)                                           |

| XTAL2             | 3/3                        | 0    | Hi-Z           | External Oscillator Output<br>(backup for on-chip OSC, normally NC)                                          |

| TMS               | 10/16                      | 1    | PD             | Test Mode Select                                                                                             |

| RESET             | 41/53                      | 1    | PU             | Reset Input                                                                                                  |

| MBC <sup>1)</sup> | 44/58                      | 1    | PU             | Monitor & BootStrap Loader Control                                                                           |

| NC                | -/56, 57                   | _    | -              | No Connection                                                                                                |

#### Table 3Pin Definitions and Functions (cont'd)

1) An external pull-up device in the range of 4.7 k $\Omega$  to 100 k $\Omega$ . is required to enter user mode. Alternatively MBC can be tied to high if alternate functions (for debugging) of the pin are not utilized.

## 3.2.2 Special Function Register

The Special Function Registers (SFRs) occupy direct internal data memory space in the range  $80_{H}$  to FF<sub>H</sub>. All registers, except the program counter, reside in the SFR area. The SFRs include pointers and registers that provide an interface between the CPU and the on-chip peripherals. As the 128-SFR range is less than the total number of registers required, address extension mechanisms are required to increase the number of addressable SFRs. The address extension mechanisms include:

- Mapping

- Paging

## 3.2.2.1 Address Extension by Mapping

Address extension is performed at the system level by mapping. The SFR area is extended into two portions: the standard (non-mapped) SFR area and the mapped SFR area. Each portion supports the same address range  $80_H$  to FF<sub>H</sub>, bringing the number of addressable SFRs to 256. The extended address range is not directly controlled by the CPU instruction itself, but is derived from bit RMAP in the system control register SYSCON0 at address  $8F_H$ . To access SFRs in the mapped area, bit RMAP in SFR SYSCON0 must be set. Alternatively, the SFRs in the standard area can be accessed by clearing bit RMAP. The SFR area can be selected as shown in **Figure 8**.

As long as bit RMAP is set, the mapped SFR area can be accessed. This bit is not cleared automatically by hardware. Thus, before standard/mapped registers are accessed, bit RMAP must be cleared/set, respectively, by software.

SYSCON0

## **Functional Description**

#### System Control Register 0 Reset Value: 04 7 5 4 3 2 1 0 6 IMODE 1 RMAP 0 0 0 r r r r rw rw

| Field | Bits          | Туре | Description                                                                                                                                                    |

|-------|---------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RMAP  | 0             | rw   | <ul> <li>Interrupt Node XINTR0 Enable</li> <li>The access to the standard SFR area is enabled</li> <li>The access to the mapped SFR area is enabled</li> </ul> |

| 1     | 2             | r    | <b>Reserved</b><br>Returns 1 if read; should be written with 1.                                                                                                |

| 0     | [7:5],<br>3,1 | r    | <b>Reserved</b><br>Returns 0 if read; should be written with 0.                                                                                                |

Note: The RMAP bit should be cleared/set by ANL or ORL instructions.

## 3.2.2.2 Address Extension by Paging

Address extension is further performed at the module level by paging. With the address extension by mapping, the XC886/888 has a 256-SFR address range. However, this is still less than the total number of SFRs needed by the on-chip peripherals. To meet this requirement, some peripherals have a built-in local address extension mechanism for increasing the number of addressable SFRs. The extended address range is not directly controlled by the CPU instruction itself, but is derived from bit field PAGE in the module page register MOD\_PAGE. Hence, the bit field PAGE must be programmed before accessing the SFR of the target module. Each module may contain a different number of pages and a different number of SFRs per page, depending on the specific requirement. Besides setting the correct RMAP bit value to select the SFR area, the user must also ensure that a valid PAGE is selected to target the desired SFR. A page inside the extended address range can be selected as shown in **Figure 9**.

#### Table 7CORDIC Register Overview (cont'd)

| Addr            | Register Name                                            | Bit       | 7         | 6         | 5           | 4           | 3          | 2   | 1         | 0   |

|-----------------|----------------------------------------------------------|-----------|-----------|-----------|-------------|-------------|------------|-----|-----------|-----|

| A0 <sub>H</sub> | CORDIC Status and Data                                   |           | KEEP<br>Z | KEEP<br>Y | KEEP<br>X   | DMAP        | INT_E<br>N | EOC | ERRO<br>R | BSY |

|                 | Control Register                                         | Туре      | rw        | rw        | rw          | rw          | rw         | rwh | rh        | rh  |

| А1 <sub>Н</sub> | CD_CON Reset: 00 <sub>H</sub><br>CORDIC Control Register | Bit Field | MPS       |           | X_USI<br>GN | ST_M<br>ODE | ROTV<br>EC | MC  | DE        | ST  |

|                 |                                                          | Туре      | r         | N         | rw          | rw          | rw         | rw  |           | rwh |

## 3.2.4.4 System Control Registers

The system control SFRs can be accessed in the mapped memory area (RMAP = 0).

#### Addr Bit 7 3 2 1 **Register Name** 6 5 4 0 RMAP = 0 or 1 IMOD 8F<sub>H</sub> SYSCON0 Reset: 04<sub>H</sub> Bit Field 0 0 1 0 RMAP System Control Register 0 F r r r r rw Туре rw RMAP = 0 SCU\_PAGE STNR PAGE BFH Reset: 00<sub>H</sub> Bit Field OP 0 Page Register Туре w w r rw RMAP = 0, PAGE 0 Reset: 00<sub>H</sub> Bit Field URRIS JTAGT JTAGT EXINT EXINT EXINT URRIS MODPISEL 0 B3<sub>H</sub> Peripheral Input Select Register Н DIS CKS 2IS 1IS 0IS rw Туре r rw rw rw rw rw rw Reset: 00<sub>H</sub> B4<sub>H</sub> **IRCON0** Bit Field 0 **EXINT** EXINT EXINT EXINT EXINT EXINT EXINT Interrupt Request Register 0 4 3 0 6 5 2 1 rwh Туре r rwh rwh rwh rwh rwh rwh Reset: 00<sub>H</sub> в5<sub>Н</sub> CANS **IRCON1** Bit Field 0 CANS ADCS ADCS RIR TIR EIR Interrupt Request Register 1 RC2 RC1 R0 R1 Туре r rwh rwh rwh rwh rwh rwh rwh B6<sub>H</sub> Reset: 00<sub>H</sub> 0 CANS 0 CANS **IRCON2** Bit Field Interrupt Request Register 2 RC3 RC0 Туре rwh rwh r r B7<sub>H</sub> EXICON0 EXINT3 EXINT2 EXINT1 EXINT0 Reset: F0µ Bit Field External Interrupt Control Туре rw rw rw rw Register 0 Reset: 3F<sub>H</sub> BAH EXICON1 Bit Field 0 EXINT6 EXINT5 EXINT4 External Interrupt Control rw rw rw Туре r Register 1 ввн NMICON Reset: 00<sub>H</sub> Bit Field 0 NMI NMI NMI NMI NMI NMI NMI NMI Control Register ECC VDDP VDD OCDS FLASH PLL WDT Туре r rw rw rw rw rw rw rw

#### Table 8SCU Register Overview

# XC886/888CLM

## **Functional Description**

## Table 10Port Register Overview (cont'd)

| Addr            | Register Name                                                       | Bit       | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|-----------------|---------------------------------------------------------------------|-----------|----|----|----|----|----|----|----|----|

| RMAP =          | = 0, PAGE 1                                                         |           |    |    |    |    |    |    | L  |    |

| 80 <sub>H</sub> | P0_PUDSEL Reset: FF <sub>H</sub>                                    | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P0 Pull-Up/Pull-Down Select Register                                | Туре      | rw |

| 86 <sub>H</sub> | P0_PUDEN Reset: C4 <sub>H</sub>                                     | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P0 Pull-Up/Pull-Down Enable Register                                | Туре      | rw |

| 90 <sub>H</sub> | P1_PUDSEL Reset: FF <sub>H</sub>                                    | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P1 Pull-Up/Pull-Down Select<br>Register                             | Туре      | rw |

| 91 <sub>H</sub> | P1_PUDEN Reset: FF <sub>H</sub>                                     | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P1 Pull-Up/Pull-Down Enable Register                                | Туре      | rw |

| 92 <sub>H</sub> | P5_PUDSEL Reset: FF <sub>H</sub>                                    | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P5 Pull-Up/Pull-Down Select<br>Register                             | Туре      | rw |

| 93 <sub>H</sub> | P5_PUDEN Reset: FF <sub>H</sub>                                     | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P5 Pull-Up/Pull-Down Enable Register                                | Туре      | rw |

| A0 <sub>H</sub> | P2_PUDSEL Reset: FF <sub>H</sub>                                    | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P2 Pull-Up/Pull-Down Select<br>Register                             | Туре      | rw |

| A1 <sub>H</sub> | P2_PUDEN Reset: 00 <sub>H</sub>                                     | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P2 Pull-Up/Pull-Down Enable<br>Register                             | Туре      | rw |

| во <sub>Н</sub> | P3_PUDSEL Reset: BF <sub>H</sub>                                    | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P3 Pull-Up/Pull-Down Select<br>Register                             | Туре      | rw |

| в1 <sub>Н</sub> | P3_PUDEN Reset: 40 <sub>H</sub>                                     | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P3 Pull-Up/Pull-Down Enable<br>Register                             | Туре      | rw |

| C8 <sub>H</sub> | P4_PUDSEL Reset: FF <sub>H</sub>                                    | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P4 Pull-Up/Pull-Down Select<br>Register                             | Туре      | rw |

| C9 <sub>H</sub> | P4_PUDEN Reset: 04 <sub>H</sub>                                     | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P4 Pull-Up/Pull-Down Enable<br>Register                             | Туре      | rw |

| RMAP =          | = 0, PAGE 2                                                         |           |    |    |    |    |    |    |    |    |

| <sup>80</sup> H | P0_ALTSEL0 Reset: 00 <sub>H</sub>                                   | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P0 Alternate Select 0 Register                                      | Туре      | rw |

| 86 <sub>H</sub> | P0_ALTSEL1 Reset: 00 <sub>H</sub><br>P0 Alternate Select 1 Register | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 |                                                                     | Туре      | rw |

| 90 <sub>H</sub> | P1_ALTSEL0 Reset: 00 <sub>H</sub><br>P1 Alternate Select 0 Register | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 |                                                                     | Туре      | rw |

| 91 <sub>H</sub> | P1_ALTSEL1 Reset: 00 <sub>H</sub><br>P1 Alternate Select 1 Register | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 |                                                                     | Туре      | rw |

| 92 <sub>H</sub> | P5_ALTSEL0 Reset: 00 <sub>H</sub><br>P5 Alternate Select 0 Register | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 |                                                                     | Туре      | rw |

# 3.2.4.12 SSC Registers

The SSC SFRs can be accessed in the standard memory area (RMAP = 0).

| Addr            | Register Name                                                                               | Bit       | 7                 | 6  | 5  | 4    | 3    | 2   | 1   | 0   |  |

|-----------------|---------------------------------------------------------------------------------------------|-----------|-------------------|----|----|------|------|-----|-----|-----|--|

| RMAP =          | = 0                                                                                         |           |                   |    |    |      |      |     |     |     |  |

| A9 <sub>H</sub> | SSC_PISEL Reset: 00 <sub>H</sub>                                                            | Bit Field |                   |    | 0  |      |      | CIS | SIS | MIS |  |

|                 | Port Input Select Register                                                                  | Туре      |                   |    | r  |      |      | rw  | rw  | rw  |  |

| AA <sub>H</sub> | SSC_CONL Reset: 00 <sub>H</sub>                                                             | Bit Field | LB                | PO | PH | HB   |      | В   | М   |     |  |

|                 | Control Register Low<br>Programming Mode                                                    | Туре      | rw                | rw | rw | rw   | rw   |     |     |     |  |

| AA <sub>H</sub> | SSC_CONL Reset: 00 <sub>H</sub>                                                             | Bit Field |                   | (  | )  |      |      | В   | С   |     |  |

|                 | Control Register Low<br>Operating Mode                                                      | Туре      |                   | l  | r  |      | rh   |     |     |     |  |

| ав <sub>Н</sub> | B <sub>H</sub> SSC_CONH Reset: 00 <sub>H</sub><br>Control Register High<br>Programming Mode | Bit Field | EN                | MS | 0  | AREN | BEN  | PEN | REN | TEN |  |

|                 |                                                                                             | Туре      | rw                | rw | r  | rw   | rw   | rw  | rw  | rw  |  |

| ав <sub>Н</sub> | SSC_CONH Reset: 00 <sub>H</sub>                                                             | Bit Field | EN                | MS | 0  | BSY  | BE   | PE  | RE  | TE  |  |

|                 | Control Register High<br>Operating Mode                                                     | Туре      | rw                | rw | r  | rh   | rwh  | rwh | rwh | rwh |  |

| ac <sub>h</sub> | SSC_TBL Reset: 00 <sub>H</sub>                                                              | Bit Field |                   |    |    | TB_V | ALUE |     |     |     |  |

|                 | Transmitter Buffer Register Low                                                             | Туре      |                   |    |    | n    | N    |     |     |     |  |

| ad <sub>H</sub> | SSC_RBL Reset: 00 <sub>H</sub>                                                              | Bit Field |                   |    |    | RB_V | ALUE |     |     |     |  |

|                 | Receiver Buffer Register Low                                                                | Туре      |                   |    |    | rl   | า    |     |     |     |  |

| ае <sub>Н</sub> | SSC_BRL Reset: 00 <sub>H</sub>                                                              | Bit Field | it Field BR_VALUE |    |    |      |      |     |     |     |  |

|                 | Baud Rate Timer Reload<br>Register Low                                                      | Туре      | rw                |    |    |      |      |     |     |     |  |

| af <sub>h</sub> | SSC_BRH Reset: 00 <sub>H</sub>                                                              | Bit Field |                   |    |    | BR_V | ALUE |     |     |     |  |

|                 | Baud Rate Timer Reload<br>Register High                                                     | Туре      |                   |    |    | n    | N    |     |     |     |  |

## Table 16 SSC Register Overview

## 3.2.4.13 MultiCAN Registers

The MultiCAN SFRs can be accessed in the standard memory area (RMAP = 0).

| Addr            | Register Name                                           | Bit       | 7   | 6   | 5   | 4   | 3    | 2    | 1    | 0    |

|-----------------|---------------------------------------------------------|-----------|-----|-----|-----|-----|------|------|------|------|

| RMAP =          | : 0                                                     |           |     |     |     |     |      |      |      |      |

| D8 <sub>H</sub> | ADCON Reset: 00 <sub>H</sub>                            | Bit Field | V3  | V2  | V1  | V0  | AU   | AD   | BSY  | RWEN |

|                 | CAN Address/Data Control<br>Register                    | Туре      | rw  | rw  | rw  | rw  | r    | W    | rh   | rw   |

| D9 <sub>H</sub> | ADL Reset: 00 <sub>H</sub>                              | Bit Field | CA9 | CA8 | CA7 | CA6 | CA5  | CA4  | CA3  | CA2  |

|                 | CAN Address Register Low                                | Туре      | rwh | rwh | rwh | rwh | rwh  | rwh  | rwh  | rwh  |

| da <sub>h</sub> | ADH Reset: 00 <sub>H</sub><br>CAN Address Register High | Bit Field |     | (   | )   |     | CA13 | CA12 | CA11 | CA10 |

|                 |                                                         | Туре      |     |     | ſ   |     | rwh  | rwh  | rwh  | rwh  |

## 3.4 Interrupt System

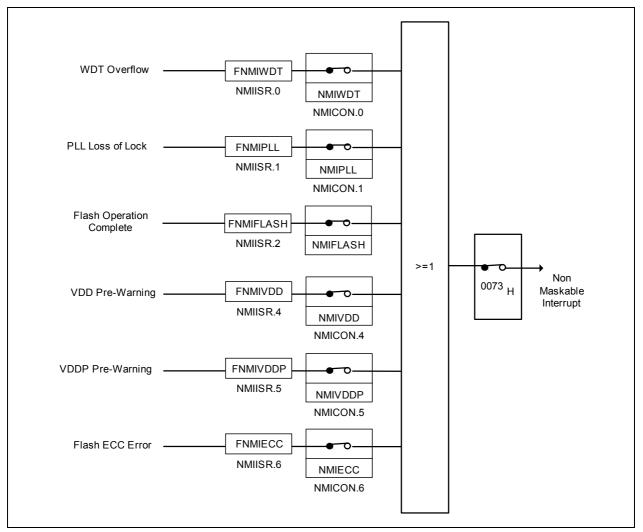

The XC800 Core supports one non-maskable interrupt (NMI) and 14 maskable interrupt requests. In addition to the standard interrupt functions supported by the core, e.g., configurable interrupt priority and interrupt masking, the XC886/888 interrupt system provides extended interrupt support capabilities such as the mapping of each interrupt vector to several interrupt sources to increase the number of interrupt sources supported, and additional status registers for detecting and determining the interrupt source.

## 3.4.1 Interrupt Source

**Figure 13** to **Figure 17** give a general overview of the interrupt sources and nodes, and their corresponding control and status flags.

Figure 13 Non-Maskable Interrupt Request Sources

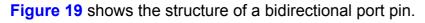

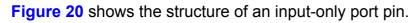

Figure 19 General Structure of Bidirectional Port

Figure 20 General Structure of Input Port

## XC886/888CLM

**Functional Description**

Figure 32 SSC Block Diagram

## 3.23 Chip Identification Number

The XC886/888 identity (ID) register is located at Page 1 of address  $B3_{H}$ . The value of ID register is  $09_{H}$  for Flash devices and  $22_{H}$  for ROM devices. However, for easy identification of product variants, the Chip Identification Number, which is an unique number assigned to each product variant, is available. The differentiation is based on the product, variant type and device step information.

Two methods are provided to read a device's chip identification number:

- In-application subroutine, GET\_CHIP\_INFO

- Bootstrap loader (BSL) mode A

**Table 36** lists the chip identification numbers of available XC886/888 Flash and ROM device variants.

| Product Variant   | Chip Identification Number |                       |                       |  |  |  |  |  |

|-------------------|----------------------------|-----------------------|-----------------------|--|--|--|--|--|

|                   | AA-Step                    | AB-Step               | AC-Step               |  |  |  |  |  |

| Flash Devices     |                            |                       |                       |  |  |  |  |  |

| XC886CLM-8FFA 3V3 | -                          | 09500102 <sub>H</sub> | 0B500102 <sub>H</sub> |  |  |  |  |  |

| XC888CLM-8FFA 3V3 | -                          | 09500103 <sub>H</sub> | 0B500103 <sub>H</sub> |  |  |  |  |  |

| XC886LM-8FFA 3V3  | -                          | 09500122 <sub>H</sub> | 0B500122 <sub>H</sub> |  |  |  |  |  |

| XC888LM-8FFA 3V3  | -                          | 09500123 <sub>H</sub> | 0B500123 <sub>H</sub> |  |  |  |  |  |

| XC886CLM-6FFA 3V3 | -                          | 09551502 <sub>H</sub> | 0B551502 <sub>H</sub> |  |  |  |  |  |

| XC888CLM-6FFA 3V3 | -                          | 09551503 <sub>H</sub> | 0B551503 <sub>H</sub> |  |  |  |  |  |

| XC886LM-6FFA 3V3  | -                          | 09551522 <sub>H</sub> | 0B551522 <sub>H</sub> |  |  |  |  |  |

| XC888LM-6FFA 3V3  | -                          | 09551523 <sub>н</sub> | 0B551523 <sub>H</sub> |  |  |  |  |  |

| XC886CM-8FFA 3V3  | -                          | 09580102 <sub>H</sub> | 0B580102 <sub>H</sub> |  |  |  |  |  |

| XC888CM-8FFA 3V3  | -                          | 09580103 <sub>H</sub> | 0B580103 <sub>H</sub> |  |  |  |  |  |

| XC886C-8FFA 3V3   | -                          | 09580142 <sub>H</sub> | 0B580142 <sub>H</sub> |  |  |  |  |  |

| XC888C-8FFA 3V3   | -                          | 09580143 <sub>H</sub> | 0B580143 <sub>H</sub> |  |  |  |  |  |

| XC886-8FFA 3V3    | -                          | 09580162 <sub>H</sub> | 0B580162 <sub>H</sub> |  |  |  |  |  |

| XC888-8FFA 3V3    | -                          | 09580163 <sub>H</sub> | 0B580163 <sub>H</sub> |  |  |  |  |  |

| XC886CM-6FFA 3V3  | -                          | 095D1502 <sub>H</sub> | 0B5D1502 <sub>H</sub> |  |  |  |  |  |

| XC888CM-6FFA 3V3  | -                          | 095D1503 <sub>H</sub> | 0B5D1503 <sub>H</sub> |  |  |  |  |  |

| XC886C-6FFA 3V3   | -                          | 095D1542 <sub>H</sub> | 0B5D1542 <sub>H</sub> |  |  |  |  |  |

| XC888C-6FFA 3V3   | -                          | 095D1543 <sub>H</sub> | 0B5D1543 <sub>H</sub> |  |  |  |  |  |

#### Table 36 Chip Identification Number

## 4.1.2 Absolute Maximum Rating

Maximum ratings are the extreme limits to which the XC886/888 can be subjected to without permanent damage.

| Parameter                                                    | Symbol            | Limi | it Values                              | Unit | Notes                               |  |

|--------------------------------------------------------------|-------------------|------|----------------------------------------|------|-------------------------------------|--|

|                                                              |                   | min. | max.                                   |      |                                     |  |

| Ambient temperature                                          | T <sub>A</sub>    | -40  | 125                                    | °C   | under bias                          |  |

| Storage temperature                                          | T <sub>ST</sub>   | -65  | 150                                    | °C   | 1)                                  |  |

| Junction temperature                                         | T <sub>J</sub>    | -40  | 150                                    | °C   | under bias <sup>1)</sup>            |  |

| Voltage on power supply pin with respect to $V_{\rm SS}$     | V <sub>DDP</sub>  | -0.5 | 6                                      | V    | 1)                                  |  |

| Voltage on any pin with respect to $V_{\rm SS}$              | V <sub>IN</sub>   | -0.5 | V <sub>DDP</sub> +<br>0.5 or<br>max. 6 | V    | whichever is<br>lower <sup>1)</sup> |  |

| Input current on any pin during overload condition           | I <sub>IN</sub>   | -10  | 10                                     | mA   | 1)                                  |  |

| Absolute sum of all input currents during overload condition | $\Sigma  I_{IN} $ | -    | 50                                     | mA   | 1)                                  |  |

| Table 4-1 | Absolute Maximum Rating Parameters |

|-----------|------------------------------------|

|-----------|------------------------------------|

1) Not subjected to production test, verified by design/characterization.

Note: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. During absolute maximum rating overload conditions ( $V_{IN} > V_{DDP}$  or  $V_{IN} < V_{SS}$ ) the voltage on  $V_{DDP}$  pin with respect to ground ( $V_{SS}$ ) must not exceed the values defined by the absolute maximum ratings.

## 4.2 DC Parameters

The electrical characteristics of the DC Parameters are detailed in this section.

## 4.2.1 Input/Output Characteristics

Table 38 provides the characteristics of the input/output pins of the XC886/888.

| Table 38 | Input/Output Characteristics | s (Operating Conditions apply) |

|----------|------------------------------|--------------------------------|

|----------|------------------------------|--------------------------------|

| Parameter                                                      | Symbol            |    | Limit Values                |                             | Unit | Test Conditions                                             |

|----------------------------------------------------------------|-------------------|----|-----------------------------|-----------------------------|------|-------------------------------------------------------------|

|                                                                |                   |    | min.                        | max.                        |      |                                                             |

| V <sub>DDP</sub> = 5 V Range                                   |                   |    |                             |                             |      | ·                                                           |

| Output low voltage                                             | V <sub>OL</sub>   | CC | -                           | 1.0                         | V    | I <sub>OL</sub> = 15 mA                                     |

|                                                                |                   |    | -                           | 1.0                         | V    | $I_{\rm OL}$ = 5 mA, current into<br>all pins > 60 mA       |

|                                                                |                   |    | -                           | 0.4                         | V    | $I_{\rm OL}$ = 5 mA, current into all pins $\leq$ 60 mA     |

| Output high voltage                                            | V <sub>OH</sub>   | CC | V <sub>DDP</sub> -<br>1.0   | -                           | V    | I <sub>ОН</sub> = -15 mA                                    |

|                                                                |                   |    | V <sub>DDP</sub> -<br>1.0   | -                           | V    | $I_{\rm OH}$ = -5 mA, current<br>from all pins > 60 mA      |

|                                                                |                   |    | V <sub>DDP</sub> - 0.4      | -                           | V    | $I_{\rm OH}$ = -5 mA, current<br>from all pins $\leq$ 60 mA |

| Input low voltage on<br>port pins<br>(all except P0.0 & P0.1)  | V <sub>ILP</sub>  | SR | -                           | $0.3 \times V_{\text{DDP}}$ | V    | CMOS Mode                                                   |

| Input low voltage on P0.0 & P0.1                               | V <sub>ILP0</sub> | SR | -0.2                        | $0.3 \times V_{ m DDP}$     | V    | CMOS Mode                                                   |

| Input low voltage on<br>RESET pin                              | V <sub>ILR</sub>  | SR | -                           | $0.3 \times V_{\text{DDP}}$ | V    | CMOS Mode                                                   |

| Input low voltage on<br>TMS pin                                | V <sub>ILT</sub>  | SR | -                           | $0.3 \times V_{ m DDP}$     | V    | CMOS Mode                                                   |

| Input high voltage on<br>port pins<br>(all except P0.0 & P0.1) | V <sub>IHP</sub>  | SR | $0.7 \times V_{\text{DDP}}$ | -                           | V    | CMOS Mode                                                   |

| Input high voltage on P0.0 & P0.1                              | V <sub>IHP0</sub> | SR | $0.7 \times V_{ m DDP}$     | V <sub>DDP</sub>            | V    | CMOS Mode                                                   |

## Table 38 Input/Output Characteristics (Operating Conditions apply) (cont'd)

| Parameter                                                                      | Symbol                |    | Limit Values                |                         | Unit | Test Conditions                                        |

|--------------------------------------------------------------------------------|-----------------------|----|-----------------------------|-------------------------|------|--------------------------------------------------------|

|                                                                                |                       |    | min.                        | max.                    |      |                                                        |

| Input high voltage on RESET pin                                                | V <sub>IHR</sub>      | SR | $0.7 \times V_{\text{DDP}}$ | -                       | V    | CMOS Mode                                              |

| Input high voltage on TMS pin                                                  | V <sub>IHT</sub>      | SR | $0.75 \times V_{ m DDP}$    | -                       | V    | CMOS Mode                                              |

| Input Hysteresis on port<br>pins                                               | HYSP                  | CC | $0.07 \times V_{ m DDP}$    | -                       | V    | CMOS Mode <sup>1)</sup>                                |

| Input Hysteresis on<br>XTAL1                                                   | HYSX                  | CC | $0.07 \times V_{ m DDC}$    | -                       | V    | 1)                                                     |

| Input low voltage at<br>XTAL1                                                  | $V_{ILX}$             | SR | V <sub>SS</sub> -<br>0.5    | $0.3 \times V_{ m DDC}$ | V    |                                                        |

| Input high voltage at XTAL1                                                    | V <sub>IHX</sub>      | SR | $0.7 \times V_{ m DDC}$     | V <sub>DDC</sub> + 0.5  | V    |                                                        |

| Pull-up current                                                                | $I_{\rm PU}$          | SR | -                           | -10                     | μA   | V <sub>IHP,min</sub>                                   |

|                                                                                |                       |    | -150                        | _                       | μA   | $V_{\rm ILP,max}$                                      |

| Pull-down current                                                              | $I_{\rm PD}$          | SR | -                           | 10                      | μA   | $V_{ILP,max}$                                          |

|                                                                                |                       |    | 150                         | -                       | μA   | V <sub>IHP,min</sub>                                   |

| Input leakage current                                                          | I <sub>OZ1</sub>      | CC | -1                          | 1                       | μA   | $0 < V_{IN} < V_{DDP},$<br>$T_A \le 125^{\circ}C^{2)}$ |

| Input current at XTAL1                                                         | $I_{ILX}$             | CC | -10                         | 10                      | μA   |                                                        |

| Overload current on any pin                                                    | I <sub>OV</sub>       | SR | -5                          | 5                       | mA   |                                                        |

| Absolute sum of overload currents                                              | $\Sigma  I_{\rm OV} $ | SR | -                           | 25                      | mA   | 3)                                                     |

| Voltage on any pin during $V_{\text{DDP}}$ power off                           | V <sub>PO</sub>       | SR | -                           | 0.3                     | V    | 4)                                                     |

| Maximum current per pin (excluding $V_{\text{DDP}}$ and $V_{\text{SS}}$ )      | $I_{\rm M}{ m SR}$    | SR | -                           | 15                      | mA   |                                                        |

| Maximum current for all pins (excluding $V_{\text{DDP}}$ and $V_{\text{SS}}$ ) | $\Sigma  I_{M} $      | SR | -                           | 90                      | mA   |                                                        |

| Maximum current into $V_{\text{DDP}}$                                          | I <sub>mvddp</sub>    | SR | -                           | 120                     | mA   | 3)                                                     |

| Parameter                                                      | Symbol            |    | Limit Values                |                             | Unit | Test Conditions           |

|----------------------------------------------------------------|-------------------|----|-----------------------------|-----------------------------|------|---------------------------|

|                                                                |                   |    | min.                        | max.                        |      |                           |

| Maximum current out of $V_{\rm SS}$                            | I <sub>MVSS</sub> | SR | -                           | 120                         | mA   | 3)                        |

| $V_{\text{DDP}}$ = 3.3 V Range                                 |                   |    |                             |                             |      |                           |

| Output low voltage                                             | $V_{OL}$          | CC | _                           | 1.0                         | V    | I <sub>OL</sub> = 8 mA    |

|                                                                |                   |    | —                           | 0.4                         | V    | I <sub>OL</sub> = 2.5 mA  |

| Output high voltage                                            | V <sub>OH</sub>   | CC | V <sub>DDP</sub> -<br>1.0   | -                           | V    | I <sub>OH</sub> = -8 mA   |

|                                                                |                   |    | V <sub>DDP</sub> - 0.4      | -                           | V    | I <sub>ОН</sub> = -2.5 mA |

| Input low voltage on<br>port pins<br>(all except P0.0 & P0.1)  | V <sub>ILP</sub>  | SR | _                           | $0.3 \times V_{\text{DDP}}$ | V    | CMOS Mode                 |

| Input low voltage on P0.0 & P0.1                               | V <sub>ILP0</sub> | SR | -0.2                        | $0.3 \times V_{ m DDP}$     | V    | CMOS Mode                 |

| Input low voltage on RESET pin                                 | $V_{ILR}$         | SR | -                           | $0.3 \times V_{\text{DDP}}$ | V    | CMOS Mode                 |

| Input low voltage on<br>TMS pin                                | V <sub>ILT</sub>  | SR | -                           | $0.3 \times V_{\text{DDP}}$ | V    | CMOS Mode                 |

| Input high voltage on<br>port pins<br>(all except P0.0 & P0.1) | V <sub>IHP</sub>  | SR | $0.7 \times V_{\text{DDP}}$ | -                           | V    | CMOS Mode                 |

| Input high voltage on P0.0 & P0.1                              | V <sub>IHP0</sub> | SR | $0.7 \times V_{\text{DDP}}$ | V <sub>DDP</sub>            | V    | CMOS Mode                 |

| Input high voltage on RESET pin                                | $V_{IHR}$         | SR | $0.7 \times V_{ m DDP}$     | -                           | V    | CMOS Mode                 |

| Input high voltage on<br>TMS pin                               | V <sub>IHT</sub>  | SR | $0.75 \times V_{ m DDP}$    | -                           | V    | CMOS Mode                 |

| Input Hysteresis                                               | HYS               | CC | $0.03 \times V_{ m DDP}$    | _                           | V    | CMOS Mode <sup>1)</sup>   |

| Input Hysteresis on XTAL1                                      | HYSX              | CC | $0.07 \times V_{ m DDC}$    | -                           | V    | 1)                        |

| Input low voltage at XTAL1                                     | V <sub>ILX</sub>  | SR | V <sub>SS</sub> -<br>0.5    | $0.3 \times V_{ m DDC}$     | V    |                           |