Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| LINbus, SSI, UART/USART                                                   |

|---------------------------------------------------------------------------|

| ut Detect/Reset, POR, PWM, WDT                                            |

|                                                                           |

| K x 8)                                                                    |

|                                                                           |

|                                                                           |

| 3                                                                         |

| 5V                                                                        |

| b                                                                         |

|                                                                           |

| 85°C (TA)                                                                 |

| Nount                                                                     |

|                                                                           |

| 48                                                                        |

| ww.e-xfl.com/product-detail/infineon-technologies/saf-xc886clm-8ffa-5v-ac |

|                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Summary of Features

#### XC886/888 Variant Devices

The XC886/888 product family features devices with different configurations, program memory sizes, package options, power supply voltage, temperature and quality profiles (Automotive or Industrial), to offer cost-effective solutions for different application requirements.

The list of XC886/888 device configurations are summarized in **Table 1**. For each configuration, 2 types of packages are available:

- PG-TQFP-48, which is denoted by XC886 and;

- PG-TQFP-64, which is denoted by XC888.

| Device Name  | CAN<br>Module | LIN BSL<br>Support | MDU<br>Module |

|--------------|---------------|--------------------|---------------|

| XC886/888    | No            | No                 | No            |

| XC886/888C   | Yes           | No                 | No            |

| XC886/888CM  | Yes           | No                 | Yes           |

| XC886/888LM  | No            | Yes                | Yes           |

| XC886/888CLM | Yes           | Yes                | Yes           |

#### Table 1Device Configuration

Note: For variants with LIN BSL support, only LIN BSL is available regardless of the availability of the CAN module.

From these 10 different combinations of configuration and package type, each are further made available in many sales types, which are grouped according to device type, program memory sizes, power supply voltage, temperature and quality profile (Automotive or Industrial), as shown in Table 2.

#### Table 2Device Profile

| Sales Type              | Device<br>Type | Program<br>Memory<br>(Kbytes) | Power<br>Supply<br>(V) | Temp-<br>erature<br>(°C) | Quality<br>Profile |

|-------------------------|----------------|-------------------------------|------------------------|--------------------------|--------------------|

| SAK-XC886*/888*-8FFA 5V | Flash          | 32                            | 5.0                    | -40 to 125               | Automotive         |

| SAK-XC886*/888*-6FFA 5V | Flash          | 24                            | 5.0                    | -40 to 125               | Automotive         |

| SAF-XC886*/888*-8FFA 5V | Flash          | 32                            | 5.0                    | -40 to 85                | Automotive         |

| SAF-XC886*/888*-6FFA 5V | Flash          | 24                            | 5.0                    | -40 to 85                | Automotive         |

| SAF-XC886*/888*-8FFI 5V | Flash          | 32                            | 5.0                    | -40 to 85                | Industrial         |

| SAF-XC886*/888*-6FFI 5V | Flash          | 24                            | 5.0                    | -40 to 85                | Industrial         |

### **General Device Information**

# 2.4 Pin Definitions and Functions

The functions and default states of the XC886/888 external pins are provided in Table 3.

| Symbol | Pin Number<br>(TQFP-48/64) | Туре | Reset<br>State | Function                                                                                                                                                                                     |                                                                                                                                                                                                      |  |  |  |

|--------|----------------------------|------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| P0     |                            | I/O  |                | <b>Port 0</b><br>Port 0 is an 8-bit bidirectional general purpose<br>I/O port. It can be used as alternate function<br>for the JTAG, CCU6, UART, UART1, Timer<br>Timer 21, MultiCAN and SSC. |                                                                                                                                                                                                      |  |  |  |

| P0.0   | 11/17                      |      | Hi-Z           | TCK_0<br>T12HR_1<br>CC61_1<br>CLKOUT_0<br>RXDO_1                                                                                                                                             | JTAG Clock Input<br>CCU6 Timer 12 Hardware Run<br>Input<br>Input/Output of<br>Capture/Compare channel 1<br>Clock Output<br>UART Transmit Data Output                                                 |  |  |  |

| P0.1   | 13/21                      |      | Hi-Z           | TDI_0<br>T13HR_1<br>RXD_1<br>RXDC1_0<br>COUT61_1<br>EXF2_1                                                                                                                                   | JTAG Serial Data Input<br>CCU6 Timer 13 Hardware Run<br>Input<br>UART Receive Data Input<br>MultiCAN Node 1 Receiver Input<br>Output of Capture/Compare<br>channel 1<br>Timer 2 External Flag Output |  |  |  |

| P0.2   | 12/18                      |      | PU             | CTRAP_2<br>TDO_0<br>TXD_1<br>TXDC1_0                                                                                                                                                         | CCU6 Trap Input<br>JTAG Serial Data Output<br>UART Transmit Data<br>Output/Clock Output<br>MultiCAN Node 1 Transmitter<br>Output                                                                     |  |  |  |

| P0.3   | 48/63                      |      | Hi-Z           | SCK_1<br>COUT63_1<br>RXDO1_0                                                                                                                                                                 | SSC Clock Input/Output<br>Output of Capture/Compare<br>channel 3<br>UART1 Transmit Data Output                                                                                                       |  |  |  |

Table 3

Pin Definitions and Functions

### **General Device Information**

| Table 0 | T III Belli                |      |                |                                                     | u)                                                                                                                                                                                       |

|---------|----------------------------|------|----------------|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol  | Pin Number<br>(TQFP-48/64) | Туре | Reset<br>State | Function                                            |                                                                                                                                                                                          |

| P0.4    | 1/64                       |      | Hi-Z           | MTSR_1                                              | SSC Master Transmit Output/<br>Slave Receive Input                                                                                                                                       |

|         |                            |      |                | CC62_1                                              | Input/Output of<br>Capture/Compare channel 2                                                                                                                                             |

|         |                            |      |                | TXD1_0                                              | UART1 Transmit Data<br>Output/Clock Output                                                                                                                                               |

| P0.5    | 2/1                        |      | Hi-Z           | MRST_1<br>EXINT0_0<br>T2EX1_1<br>RXD1_0<br>COUT62_1 | SSC Master Receive Input/Slave<br>Transmit Output<br>External Interrupt Input 0<br>Timer 21 External Trigger Input<br>UART1 Receive Data Input<br>Output of Capture/Compare<br>channel 2 |

| P0.6    | -/2                        |      | PU             | GPIO                                                |                                                                                                                                                                                          |

| P0.7    | 47/62                      |      | PU             | CLKOUT_1                                            | Clock Output                                                                                                                                                                             |

#### Pin Definitions and Functions (cont'd) Table 3

### **General Device Information**

| Symbol | Pin Number<br>(TQFP-48/64) | Туре | Reset<br>State | Function                                                                                                                                                                            |                                                                                                                                                              |  |  |  |

|--------|----------------------------|------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| P1     |                            | I/O  |                | <b>Port 1</b><br>Port 1 is an 8-bit bidirectional general pull/O port. It can be used as alternate function for the JTAG, CCU6, UART, Timer 0, Timer 2, Timer 21, MultiCAN and SSC. |                                                                                                                                                              |  |  |  |

| P1.0   | 26/34                      |      | PU             | RXD_0<br>T2EX<br>RXDC0_0                                                                                                                                                            | UART Receive Data Input<br>Timer 2 External Trigger Input<br>MultiCAN Node 0 Receiver Input                                                                  |  |  |  |

| P1.1   | 27/35                      |      | PU             | EXINT3<br>T0_1<br>TDO_1<br>TXD_0<br>TXDC0_0                                                                                                                                         | External Interrupt Input 3<br>Timer 0 Input<br>JTAG Serial Data Output<br>UART Transmit Data<br>Output/Clock Output<br>MultiCAN Node 0 Transmitter<br>Output |  |  |  |

| P1.2   | 28/36                      |      | PU             | SCK_0                                                                                                                                                                               | SSC Clock Input/Output                                                                                                                                       |  |  |  |

| P1.3   | 29/37                      |      | PU             | MTSR_0<br>TXDC1_3                                                                                                                                                                   | SSC Master Transmit<br>Output/Slave Receive Input<br>MultiCAN Node 1 Transmitter<br>Output                                                                   |  |  |  |

| P1.4   | 30/38                      |      | PU             | MRST_0<br>EXINT0_1<br>RXDC1_3                                                                                                                                                       | SSC Master Receive Input/<br>Slave Transmit Output<br>External Interrupt Input 0<br>MultiCAN Node 1 Receiver Input                                           |  |  |  |

| P1.5   | 31/39                      |      | PU             | CCPOS0_1<br>EXINT5<br>T1_1<br>EXF2_0<br>RXDO_0                                                                                                                                      | CCU6 Hall Input 0<br>External Interrupt Input 5<br>Timer 1 Input<br>Timer 2 External Flag Output<br>UART Transmit Data Output                                |  |  |  |

### Table 3Pin Definitions and Functions (cont'd)

code or data. Therefore, even though the ROM device contains either a 24-Kbyte or 32-Kbyte ROM, the maximum size of code that can be placed in the ROM is the given size less four bytes.

### 3.2.1 Memory Protection Strategy

The XC886/888 memory protection strategy includes:

- Read-out protection: The user is able to protect the contents in the Flash (for Flash devices) and ROM (for ROM devices) memory from being read

- Flash protection is enabled by programming a valid password (8-bit non-zero value) via BSL mode 6.

- ROM protection is fixed with the ROM mask and is always enabled.

- Flash program and erase protection: This feature is available only for Flash devices.

### 3.2.1.1 Flash Memory Protection

As long as a valid password is available, all external access to the device, including the Flash, will be blocked.

For additional security, the Flash hardware protection can be enabled to implement a second layer of read-out protection, as well as to enable program and erase protection.

Flash hardware protection is available only for Flash devices and comes in two modes:

- Mode 0: Only the P-Flash is protected; the D-Flash is unprotected

- Mode 1: Both the P-Flash and D-Flash are protected

The selection of each protection mode and the restrictions imposed are summarized in **Table 4**.

| Flash Protection                      | Without hardware protection             | With hardware protection                     |                                                 |  |  |  |  |  |  |

|---------------------------------------|-----------------------------------------|----------------------------------------------|-------------------------------------------------|--|--|--|--|--|--|

| Hardware<br>Protection Mode           | -                                       | 0                                            | 1                                               |  |  |  |  |  |  |

| Activation                            | Program a valid password via BSL mode 6 |                                              |                                                 |  |  |  |  |  |  |

| Selection                             | Bit 4 of password = 0                   | Bit 4 of password = 1<br>MSB of password = 0 | Bit 4 of password = 1<br>MSB of password = 1    |  |  |  |  |  |  |

| P-Flash<br>contents can be<br>read by | Read instructions in any program memory | Read instructions in the P-Flash             | Read instructions in the P-Flash or D-<br>Flash |  |  |  |  |  |  |

| External access<br>to P-Flash         | Not possible                            | Not possible                                 | Not possible                                    |  |  |  |  |  |  |

#### Table 4Flash Protection Modes

SYSCON0

#### **Functional Description**

#### System Control Register 0 Reset Value: 04 7 5 4 3 2 1 0 6 IMODE 1 RMAP 0 0 0 r r r r rw rw

| Field | Bits          | Туре | Description                                                                                                                                                    |

|-------|---------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RMAP  | 0             | rw   | <ul> <li>Interrupt Node XINTR0 Enable</li> <li>The access to the standard SFR area is enabled</li> <li>The access to the mapped SFR area is enabled</li> </ul> |

| 1     | 2             | r    | <b>Reserved</b><br>Returns 1 if read; should be written with 1.                                                                                                |

| 0     | [7:5],<br>3,1 | r    | <b>Reserved</b><br>Returns 0 if read; should be written with 0.                                                                                                |

Note: The RMAP bit should be cleared/set by ANL or ORL instructions.

### 3.2.2.2 Address Extension by Paging

Address extension is further performed at the module level by paging. With the address extension by mapping, the XC886/888 has a 256-SFR address range. However, this is still less than the total number of SFRs needed by the on-chip peripherals. To meet this requirement, some peripherals have a built-in local address extension mechanism for increasing the number of addressable SFRs. The extended address range is not directly controlled by the CPU instruction itself, but is derived from bit field PAGE in the module page register MOD\_PAGE. Hence, the bit field PAGE must be programmed before accessing the SFR of the target module. Each module may contain a different number of pages and a different number of SFRs per page, depending on the specific requirement. Besides setting the correct RMAP bit value to select the SFR area, the user must also ensure that a valid PAGE is selected to target the desired SFR. A page inside the extended address range can be selected as shown in **Figure 9**.

# 3.2.3.1 Password Register

# PASSWD

| Pass       | Password Register Reset Value: 07 <sub>H</sub> |   |    |   |    |               |    |    |  |  |  |  |  |

|------------|------------------------------------------------|---|----|---|----|---------------|----|----|--|--|--|--|--|

|            | 7                                              | 6 | 5  | 4 | 3  | 2             | 1  | 0  |  |  |  |  |  |

|            | PASS                                           |   |    |   |    | PROTECT<br>_S | МС | DE |  |  |  |  |  |

| . <u> </u> |                                                |   | wh |   | rh | r             | W  |    |  |  |  |  |  |

| Field     | Bits  | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------|-------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MODE      | [1:0] | rw   | <ul> <li>Bit Protection Scheme Control Bits</li> <li>00 Scheme disabled - direct access to the protected bits is allowed.</li> <li>11 Scheme enabled - the bit field PASS has to be written with the passwords to open and close the access to protected bits. (default)</li> <li>Others:Scheme Enabled.</li> <li>These two bits cannot be written directly. To change the value between 11<sub>B</sub> and 00<sub>B</sub>, the bit field PASS must be written with 11000<sub>B</sub>; only then, will the MODE[1:0] be registered.</li> </ul> |

| PROTECT_S | 2     | rh   | <ul> <li>Bit Protection Signal Status Bit</li> <li>This bit shows the status of the protection.</li> <li>0 Software is able to write to all protected bits.</li> <li>1 Software is unable to write to any protected bits.</li> </ul>                                                                                                                                                                                                                                                                                                           |

| PASS      | [7:3] | wh   | Password BitsThe Bit Protection Scheme only recognizes threepatterns. $11000_B$ Enables writing of the bit field MODE. $10011_B$ Opens access to writing of all protected bits. $10101_B$ Closes access to writing of all protected bits                                                                                                                                                                                                                                                                                                       |

### 3.2.4.8 Timer 2 Registers

The Timer 2 SFRs can be accessed in the standard memory area (RMAP = 0).

| Addr            | Register Name                                            | Bit       | 7          | 6          | 5           | 4    | 3         | 2     | 1    | 0          |

|-----------------|----------------------------------------------------------|-----------|------------|------------|-------------|------|-----------|-------|------|------------|

| RMAP =          | = 0                                                      |           |            |            |             |      |           |       |      |            |

| с₀ <sub>Н</sub> | T2_T2CONReset: 00HTimer 2 Control Register               | Bit Field | TF2        | EXF2       | 0           |      | EXEN<br>2 | TR2   | C/T2 | CP/<br>RL2 |

|                 |                                                          | Туре      | rwh        | rwh        | I           | r    | rw        | rwh   | rw   | rw         |

|                 | T2_T2MOD Reset: 00 <sub>H</sub><br>Timer 2 Mode Register | Bit Field | T2RE<br>GS | T2RH<br>EN | EDGE<br>SEL | PREN |           | T2PRE |      | DCEN       |

|                 |                                                          | Туре      | rw         | rw         | rw          | rw   | rw        | rw    | rw   | rw         |

| C2 <sub>H</sub> | T2_RC2L Reset: 00 <sub>H</sub>                           | Bit Field |            |            |             | R    | C2        |       |      |            |

|                 | Timer 2 Reload/Capture<br>Register Low                   | Туре      |            |            |             | rv   | vh        |       |      |            |

| C3 <sub>H</sub> | T2_RC2H Reset: 00 <sub>H</sub>                           | Bit Field |            |            |             | R    | C2        |       |      |            |

|                 | Timer 2 Reload/Capture<br>Register High                  | Туре      |            |            |             | rv   | vh        | 'n    |      |            |

| C4 <sub>H</sub> | T2_T2L Reset: 00 <sub>H</sub>                            | Bit Field |            |            |             | TH   | IL2       |       |      |            |

|                 | Timer 2 Register Low                                     | Туре      | rwh        |            |             |      |           |       |      |            |

| C5 <sub>H</sub> | T2_T2H Reset: 00 <sub>H</sub>                            | Bit Field |            |            |             | T⊦   | IL2       |       |      |            |

|                 | Timer 2 Register High                                    | Туре      | rwh        |            |             |      |           |       |      |            |

### Table 12T2 Register Overview

## 3.2.4.9 Timer 21 Registers

The Timer 21 SFRs can be accessed in the mapped memory area (RMAP = 1).

#### Table 13T21 Register Overview

|                 | 0                                                     |           |            |            |             |      |           |     |      |            |

|-----------------|-------------------------------------------------------|-----------|------------|------------|-------------|------|-----------|-----|------|------------|

| Addr            | Register Name                                         | Bit       | 7          | 6          | 5           | 4    | 3         | 2   | 1    | 0          |

| RMAP =          | = 1                                                   |           |            |            |             |      |           |     |      |            |

| c₀H             | T21_T2CONReset: 00HTimer 2 Control Register           | Bit Field | TF2        | EXF2       | (           | 0    | EXEN<br>2 | TR2 | C/T2 | CP/<br>RL2 |

|                 |                                                       | Туре      | rwh        | rwh        | I           | r    | rw        | rwh | rw   | rw         |

| C1 <sub>H</sub> | T21_T2MODReset: 00Timer 2 Mode Register               | Bit Field | T2RE<br>GS | T2RH<br>EN | EDGE<br>SEL | PREN | T2PI      |     |      | DCEN       |

|                 |                                                       | Туре      | rw         | rw         | rw          | rw   | rw        | rw  | rw   | rw         |

| C2 <sub>H</sub> | T21_RC2L     Reset: 00 <sub>H</sub> Bit Field     RC2 |           |            |            |             |      |           |     |      |            |

|                 | Timer 2 Reload/Capture<br>Register Low                | Туре      |            |            | rwh         |      |           |     |      |            |

| C3 <sub>H</sub> | T21_RC2H Reset: 00 <sub>H</sub>                       | Bit Field |            |            |             | R    | C2        |     |      |            |

|                 | Timer 2 Reload/Capture<br>Register High               | Туре      | rwh        |            |             |      |           |     |      |            |

| C4 <sub>H</sub> | T21_T2L Reset: 00 <sub>H</sub>                        | Bit Field |            |            |             | TH   | IL2       |     |      |            |

|                 | Timer 2 Register Low                                  | Туре      |            |            |             | ٢٧   | vh        |     |      |            |

## Table 14CCU6 Register Overview (cont'd)

| Addr                                  | Register Name                                                        | Bit       | 7          | 6          | 5          | 4          | 3          | 2          | 1           | 0           |  |

|---------------------------------------|----------------------------------------------------------------------|-----------|------------|------------|------------|------------|------------|------------|-------------|-------------|--|

| FB <sub>H</sub>                       | CCU6_CC60RH Reset: 00 <sub>H</sub>                                   | Bit Field |            | 1          | 1          | CC6        | 60VH       | 1          | 1           | 1           |  |

|                                       | Capture/Compare Register for<br>Channel CC60 High                    | Туре      | rh         |            |            |            |            |            |             |             |  |

| FC <sub>H</sub>                       | CCU6_CC61RL Reset: 00 <sub>H</sub>                                   | Bit Field | CC61VL     |            |            |            |            |            |             |             |  |

|                                       | Capture/Compare Register for<br>Channel CC61 Low                     | Туре      |            |            |            | r          | 'n         |            |             |             |  |

| FD <sub>H</sub>                       | CCU6_CC61RH Reset: 00 <sub>H</sub>                                   | Bit Field |            |            |            | CC6        | 61VH       |            |             |             |  |

|                                       | Capture/Compare Register for<br>Channel CC61 High                    | Туре      |            |            |            | r          | 'n         |            |             |             |  |

| FE <sub>H</sub>                       | CCU6_CC62RL Reset: 00 <sub>H</sub>                                   | Bit Field |            |            |            | CC6        | 62VL       |            |             |             |  |

|                                       | Capture/Compare Register for<br>Channel CC62 Low                     | Туре      |            |            |            | r          | h          |            |             |             |  |

| FF <sub>H</sub>                       | CCU6_CC62RH Reset: 00 <sub>H</sub>                                   | Bit Field |            |            |            | CC6        | 62VH       |            |             |             |  |

|                                       | Capture/Compare Register for<br>Channel CC62 High                    | Туре      |            |            |            | r          | 'n         |            |             |             |  |

| RMAP =                                | 0, PAGE 2                                                            | _         |            |            |            |            | _          |            |             |             |  |

| 9A <sub>H</sub>                       | CCU6_T12MSELL Reset: 00 <sub>H</sub>                                 | Bit Field |            | MS         | EL61       |            |            | MS         | EL60        |             |  |

|                                       | T12 Capture/Compare Mode Select<br>Register Low                      | Туре      |            | r          | w          |            |            | r          | w           |             |  |

| 9В <sub>Н</sub>                       | CCU6_T12MSELH Reset: 00 <sub>H</sub>                                 | Bit Field | DBYP       |            | HSYNC      |            |            | MSEL62     |             |             |  |

|                                       | T12 Capture/Compare Mode Select<br>Register High                     | Туре      | rw         |            | rw         |            | rw         |            |             |             |  |

| 9CH                                   | CU6_IENL Reset: 00 <sub>H</sub>                                      | Bit Field | ENT1       | ENT1       | ENCC       | ENCC       | ENCC       | ENCC       | ENCC        | ENCC        |  |

| Capture/Compare Inter<br>Register Low | Capture/Compare Interrupt Enable<br>Register Low                     |           | 2<br>PM    | 2<br>OM    | 62F        | 62R        | 61F        | 61R        | 60F         | 60R         |  |

|                                       |                                                                      | Туре      | rw          | rw          |  |

| 9D <sub>H</sub>                       | CCU6_IENH Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Enable | Bit Field | EN<br>STR  | EN<br>IDLE | EN<br>WHE  | EN<br>CHE  | 0          | EN<br>TRPF | ENT1<br>3PM | ENT1<br>3CM |  |

|                                       | Register High                                                        | Туре      | rw         | rw         | rw         | rw         | r          | rw         | rw          | rw          |  |

| 9E <sub>H</sub>                       | CCU6_INPL Reset: 40 <sub>H</sub>                                     | Bit Field | INP        | CHE        | INPCC62    |            | INPCC61    |            | INPCC60     |             |  |

|                                       | Capture/Compare Interrupt Node<br>Pointer Register Low               | Туре      | r          | w          | rw         |            | rw         |            | rw          |             |  |

| 9F <sub>H</sub>                       | CCU6_INPH Reset: 39 <sub>H</sub>                                     | Bit Field | (          | 0 INPT13   |            | T13        | INPT12     |            | INPERR      |             |  |

|                                       | Capture/Compare Interrupt Node<br>Pointer Register High              | Туре      |            | r          | r          | w          | r          | w          | rw          |             |  |

| A4 <sub>H</sub>                       | CCU6_ISSL Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Status | Bit Field | ST12<br>PM | ST12<br>OM | SCC6<br>2F | SCC6<br>2R | SCC6<br>1F | SCC6<br>1R | SCC6<br>0F  | SCC6<br>0R  |  |

|                                       | Set Register Low                                                     | Туре      | w          | w          | w          | w          | w          | w          | w           | w           |  |

| A5 <sub>H</sub>                       | CCU6_ISSH Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Status | Bit Field | SSTR       | SIDLE      | SWHE       | SCHE       | SWH<br>C   | STRP<br>F  | ST13<br>PM  | ST13<br>CM  |  |

|                                       | Set Register High                                                    | Туре      | w          | w          | w          | w          | w          | w          | w           | w           |  |

| A6 <sub>H</sub>                       | CCU6_PSLR Reset: 00 <sub>H</sub>                                     | Bit Field | PSL63      | 0          |            |            | P          | SL         |             |             |  |

|                                       | Passive State Level Register                                         | Туре      | rwh        | r          | rwh        |            |            |            |             |             |  |

| а7 <sub>Н</sub>                       | CCU6_MCMCTR Reset: 00 <sub>H</sub>                                   | Bit Field | 0 SWSYN    |            |            | SYN        | 0          |            | SWSEL       |             |  |

|                                       | Multi-Channel Mode Control Register                                  | Туре      |            | r          | rw r       |            | rw         |            |             |             |  |

| FA <sub>H</sub>                       | CCU6_TCTR2LReset: 00HTimer Control Register 2 Low                    | Bit Field | 0          | T13        | TED        |            | T13TEC     |            | T13<br>SSC  | T12<br>SSC  |  |

|                                       |                                                                      | Туре      | r          | r          | W          |            | rw         |            | rw          | rw          |  |

## 3.2.4.12 SSC Registers

The SSC SFRs can be accessed in the standard memory area (RMAP = 0).

| Addr            | Register Name                                  | Bit       | 7                | 6  | 5  | 4    | 3    | 2   | 1   | 0   |  |

|-----------------|------------------------------------------------|-----------|------------------|----|----|------|------|-----|-----|-----|--|

| RMAP =          | = 0                                            |           |                  |    |    |      |      |     |     |     |  |

| A9 <sub>H</sub> | SSC_PISEL Reset: 00 <sub>H</sub>               | Bit Field | 0                |    |    |      |      | CIS | SIS | MIS |  |

|                 | Port Input Select Register                     | Туре      |                  |    | r  |      |      | rw  | rw  | rw  |  |

| AA <sub>H</sub> | SSC_CONL Reset: 00 <sub>H</sub>                | Bit Field | LB               | PO | PH | HB   |      | В   | М   |     |  |

|                 | Control Register Low<br>Programming Mode       | Туре      | rw               | rw | rw | rw   | rw   |     |     |     |  |

| AA <sub>H</sub> | SSC_CONL Reset: 00 <sub>H</sub>                | Bit Field |                  | (  | )  |      |      | В   | С   |     |  |

|                 | Control Register Low<br>Operating Mode         | Туре      | r                |    |    |      | rh   |     |     |     |  |

| ав <sub>Н</sub> | B <sub>H</sub> SSC_CONH Reset: 00 <sub>H</sub> |           | EN               | MS | 0  | AREN | BEN  | PEN | REN | TEN |  |

|                 | Control Register High<br>Programming Mode      | Туре      | rw               | rw | r  | rw   | rw   | rw  | rw  | rw  |  |

| ав <sub>Н</sub> | SSC_CONH Reset: 00 <sub>H</sub>                | Bit Field | EN               | MS | 0  | BSY  | BE   | PE  | RE  | TE  |  |

|                 | Control Register High<br>Operating Mode        | Туре      | rw               | rw | r  | rh   | rwh  | rwh | rwh | rwh |  |

| ac <sub>h</sub> | SSC_TBL Reset: 00 <sub>H</sub>                 | Bit Field | t Field TB_VALUE |    |    |      |      |     |     |     |  |

|                 | Transmitter Buffer Register Low                | Туре      | rw               |    |    |      |      |     |     |     |  |

| ad <sub>H</sub> | SSC_RBL Reset: 00 <sub>H</sub>                 | Bit Field | Field RB_VALUE   |    |    |      |      |     |     |     |  |

|                 | Receiver Buffer Register Low                   | Туре      | rh               |    |    |      |      |     |     |     |  |

| ае <sub>Н</sub> | SSC_BRL Reset: 00 <sub>H</sub>                 | Bit Field | BR_VALUE         |    |    |      |      |     |     |     |  |

|                 | Baud Rate Timer Reload<br>Register Low         | Туре      | rw               |    |    |      |      |     |     |     |  |

| af <sub>h</sub> | SSC_BRH Reset: 00 <sub>H</sub>                 | Bit Field |                  |    |    | BR_V | ALUE |     |     |     |  |

|                 | Baud Rate Timer Reload<br>Register High        | Туре      |                  |    |    | n    | N    |     |     |     |  |

### Table 16 SSC Register Overview

### 3.2.4.13 MultiCAN Registers

The MultiCAN SFRs can be accessed in the standard memory area (RMAP = 0).

| Addr            | Register Name                        | Bit       | 7   | 6   | 5   | 4    | 3    | 2    | 1    | 0    |

|-----------------|--------------------------------------|-----------|-----|-----|-----|------|------|------|------|------|

| RMAP =          | RMAP = 0                             |           |     |     |     |      |      |      |      |      |

| D8 <sub>H</sub> | ADCON Reset: 00 <sub>H</sub>         | Bit Field | V3  | V2  | V1  | V0   | AUAD |      | BSY  | RWEN |

|                 | CAN Address/Data Control<br>Register | Туре      | rw  | rw  | rw  | rw   | rw   |      | rh   | rw   |

| D9 <sub>H</sub> | ADL Reset: 00 <sub>H</sub>           | Bit Field | CA9 | CA8 | CA7 | CA6  | CA5  | CA4  | CA3  | CA2  |

|                 | CAN Address Register Low             | Туре      | rwh | rwh | rwh | rwh  | rwh  | rwh  | rwh  | rwh  |

| da <sub>h</sub> | ADH Reset: 00 <sub>H</sub>           | Bit Field | 0   |     |     | CA13 | CA12 | CA11 | CA10 |      |

|                 | CAN Address Register High            | Туре      |     |     | ſ   |      | rwh  | rwh  | rwh  | rwh  |

| Table 19    | Table 19Flash Data Retention and Endurance (Operating Conditions apply) |                               |                      |  |  |  |  |  |  |

|-------------|-------------------------------------------------------------------------|-------------------------------|----------------------|--|--|--|--|--|--|

| Retention   | Endurance <sup>1)</sup>                                                 | Size                          | Remarks              |  |  |  |  |  |  |

| Program Fla | ash                                                                     |                               | · ·                  |  |  |  |  |  |  |

| 20 years    | 1,000 cycles                                                            | up to 32 Kbytes <sup>2)</sup> | for 32-Kbyte Variant |  |  |  |  |  |  |

| 20 years    | 1,000 cycles                                                            | up to 24 Kbytes <sup>2)</sup> | for 24-Kbyte Variant |  |  |  |  |  |  |

| Data Flash  | ·                                                                       |                               | · ·                  |  |  |  |  |  |  |

| 20 years    | 1,000 cycles                                                            | 4 Kbytes                      |                      |  |  |  |  |  |  |

| 5 years     | 10,000 cycles                                                           | 1 Kbyte                       |                      |  |  |  |  |  |  |

| 2 years     | 70,000 cycles                                                           | 512 bytes                     |                      |  |  |  |  |  |  |

| 2 years     | 100,000 cycles                                                          | 128 bytes                     |                      |  |  |  |  |  |  |

Table 19 shows the Flash data retention and endurance targets.

1) One cycle refers to the programming of all wordlines in a sector and erasing of sector. The Flash endurance data specified in Table 19 is valid only if the following conditions are fulfilled:

- the maximum number of erase cycles per Flash sector must not exceed 100,000 cycles.

- the maximum number of erase cycles per Flash bank must not exceed 300,000 cycles.

- the maximum number of program cycles per Flash bank must not exceed 2,500,000 cycles.

2) If no Flash is used for data, the Program Flash size can be up to the maximum Flash size available in the device variant. Having more Data Flash will mean less Flash is available for Program Flash.

## 3.3.1 Flash Bank Sectorization

The XC886/888 product family offers Flash devices with either 24 Kbytes or 32 Kbytes of embedded Flash memory. Each Flash device consists of Program Flash (P-Flash) and Data Flash (D-Flash) bank(s) with different sectorization shown in **Figure 11**. Both types can be used for code and data storage. The label "Data" neither implies that the D-Flash is mapped to the data memory region, nor that it can only be used for data storage. It is used to distinguish the different Flash bank sectorizations.

The 32-Kbyte Flash device consists of 6 P-Flash and 2 D-Flash banks, while the 24-Kbyte Flash device consists of also of 6 P-Flash banks but with the upper 2 banks only 2 Kbytes each, and only 1 D-Flash bank. The XC886/888 ROM devices offer a single 4-Kbyte D-Flash bank.

The P-Flash banks are always grouped in pairs. As such, the P-Flash banks are also sometimes referred to as P-Flash bank pair. Each sector in a P-Flash bank is grouped with the corresponding sector from the other bank within a bank pair to form a P-Flash bank pair sector.

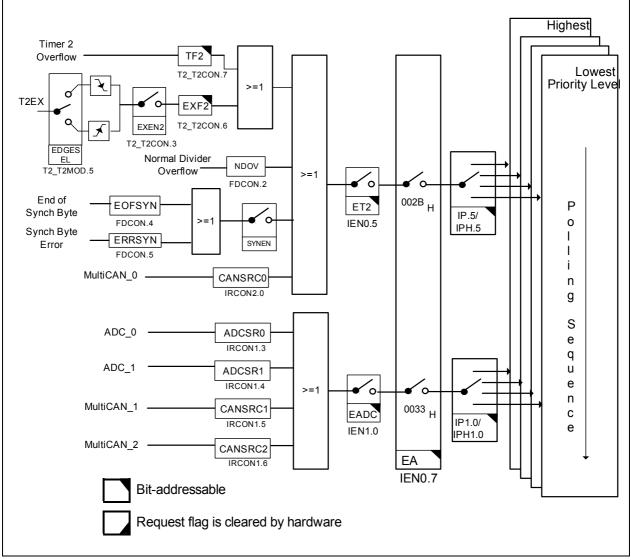

Figure 15 Interrupt Request Sources (Part 2)

### 3.11 Multiplication/Division Unit

The Multiplication/Division Unit (MDU) provides fast 16-bit multiplication, 16-bit and 32-bit division as well as shift and normalize features. It has been integrated to support the XC886/888 Core in real-time control applications, which require fast mathematical computations.

#### Features

- Fast signed/unsigned 16-bit multiplication

- Fast signed/unsigned 32-bit divide by 16-bit and 16-bit divide by 16-bit operations

- 32-bit unsigned normalize operation

- 32-bit arithmetic/logical shift operations

Table 28 specifies the number of clock cycles used for calculation in various operations.

| Operation                | Result | Remainder | No. of Clock Cycles<br>used for calculation |

|--------------------------|--------|-----------|---------------------------------------------|

| Signed 32-bit/16-bit     | 32-bit | 16-bit    | 33                                          |

| Signed 16-bit/16bit      | 16-bit | 16-bit    | 17                                          |

| Signed 16-bit x 16-bit   | 32-bit | -         | 16                                          |

| Unsigned 32-bit/16-bit   | 32-bit | 16-bit    | 32                                          |

| Unsigned 16-bit/16-bit   | 16-bit | 16-bit    | 16                                          |

| Unsigned 16-bit x 16-bit | 32-bit | -         | 16                                          |

| 32-bit normalize         | -      | -         | No. of shifts + 1 (Max. 32)                 |

| 32-bit shift L/R         | -      | -         | No. of shifts + 1 (Max. 32)                 |

Table 28

MDU Operation Characteristics

### 3.15 LIN Protocol

The UART module can be used to support the Local Interconnect Network (LIN) protocol for both master and slave operations. The LIN baud rate detection feature, which consists of the hardware logic for Break and Synch Byte detection, provides the capability to detect the baud rate within LIN protocol using Timer 2. This allows the UART to be synchronized to the LIN baud rate for data transmission and reception.

Note: The LIN baud rate detection feature is available for use only with UART. To use UART1 for LIN communication, software has to be implemented to detect the Break and Synch Byte.

LIN is a holistic communication concept for local interconnected networks in vehicles. The communication is based on the SCI (UART) data format, a single-master/multipleslave concept, a clock synchronization for nodes without stabilized time base. An attractive feature of LIN is self-synchronization of the slave nodes without a crystal or ceramic resonator, which significantly reduces the cost of hardware platform. Hence, the baud rate must be calculated and returned with every message frame.

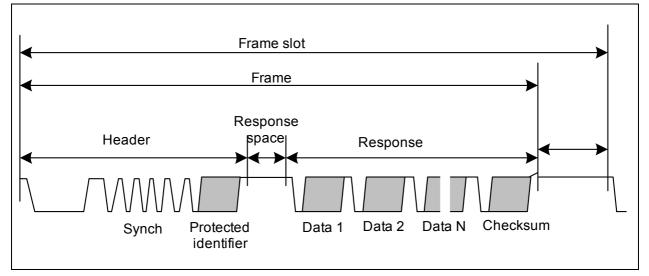

The structure of a LIN frame is shown in **Figure 31**. The frame consists of the:

- Header, which comprises a Break (13-bit time low), Synch Byte (55<sub>H</sub>), and ID field

- Response time

- Data bytes (according to UART protocol)

- Checksum

Figure 31 Structure of LIN Frame

### 3.15.1 LIN Header Transmission

LIN header transmission is only applicable in master mode. In the LIN communication, a master task decides when and which frame is to be transferred on the bus. It also identifies a slave task to provide the data transported by each frame. The information

### XC886/888CLM

### **Functional Description**

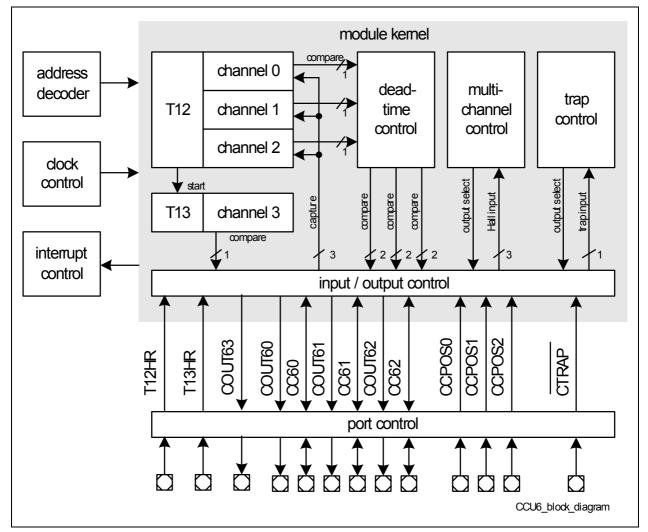

Figure 33 CCU6 Block Diagram

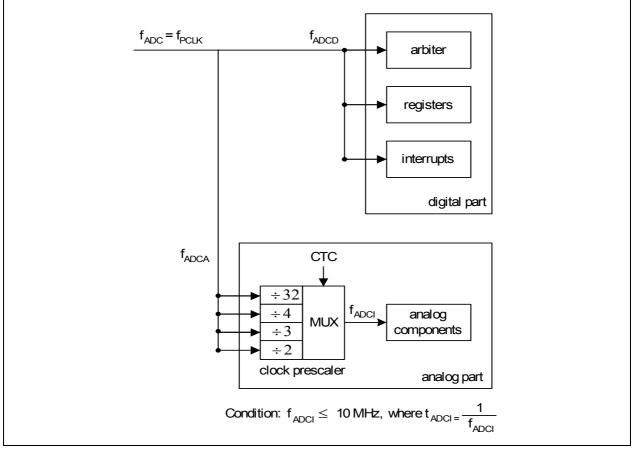

GLOBCTR. A prescaling ratio of 32 can be selected when the maximum performance of the ADC is not required.

#### Figure 35 ADC Clocking Scheme

For module clock  $f_{ADC}$  = 24 MHz, the analog clock  $f_{ADCI}$  frequency can be selected as shown in **Table 34**.

| Table 34 | f <sub>ADCI</sub> Frequency Selection |

|----------|---------------------------------------|

|----------|---------------------------------------|

| Module Clock $f_{ADC}$ | СТС                       | Prescaling Ratio | Analog Clock $f_{ADCI}$ |

|------------------------|---------------------------|------------------|-------------------------|

| 24 MHz                 | 00 <sub>B</sub>           | ÷ 2              | 12 MHz (N.A)            |

|                        | 01 <sub>B</sub>           | ÷ 3              | 8 MHz                   |

|                        | 10 <sub>B</sub>           | ÷ 4              | 6 MHz                   |

|                        | 11 <sub>B</sub> (default) | ÷ 32             | 750 kHz                 |

As  $f_{\rm ADCI}$  cannot exceed 10 MHz, bit field CTC should not be set to  $00_{\rm B}$  when  $f_{\rm ADC}$  is 24 MHz. During slow-down mode where  $f_{\rm ADC}$  may be reduced to 12 MHz, 6 MHz etc., CTC can be set to  $00_{\rm B}$  as long as the divided analog clock  $f_{\rm ADCI}$  does not exceed 10 MHz.

### **Electrical Parameters**

### 4.1.2 Absolute Maximum Rating

Maximum ratings are the extreme limits to which the XC886/888 can be subjected to without permanent damage.

| Parameter                                                    | Symbol            | Limi | it Values                              | Unit | Notes                               |  |

|--------------------------------------------------------------|-------------------|------|----------------------------------------|------|-------------------------------------|--|

|                                                              |                   | min. | max.                                   |      |                                     |  |

| Ambient temperature                                          | T <sub>A</sub>    | -40  | 125                                    | °C   | under bias                          |  |

| Storage temperature                                          | T <sub>ST</sub>   | -65  | 150                                    | °C   | 1)                                  |  |

| Junction temperature                                         | T <sub>J</sub>    | -40  | 150                                    | °C   | under bias <sup>1)</sup>            |  |

| Voltage on power supply pin with respect to $V_{\rm SS}$     | V <sub>DDP</sub>  | -0.5 | 6                                      | V    | 1)                                  |  |

| Voltage on any pin with respect to $V_{\rm SS}$              | V <sub>IN</sub>   | -0.5 | V <sub>DDP</sub> +<br>0.5 or<br>max. 6 | V    | whichever is<br>lower <sup>1)</sup> |  |

| Input current on any pin during overload condition           | I <sub>IN</sub>   | -10  | 10                                     | mA   | 1)                                  |  |

| Absolute sum of all input currents during overload condition | $\Sigma  I_{IN} $ | -    | 50                                     | mA   | 1)                                  |  |

| Table 4-1 | Absolute Maximum Rating Parameters |

|-----------|------------------------------------|

|-----------|------------------------------------|

1) Not subjected to production test, verified by design/characterization.

Note: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. During absolute maximum rating overload conditions ( $V_{IN} > V_{DDP}$  or  $V_{IN} < V_{SS}$ ) the voltage on  $V_{DDP}$  pin with respect to ground ( $V_{SS}$ ) must not exceed the values defined by the absolute maximum ratings.

#### **Electrical Parameters**

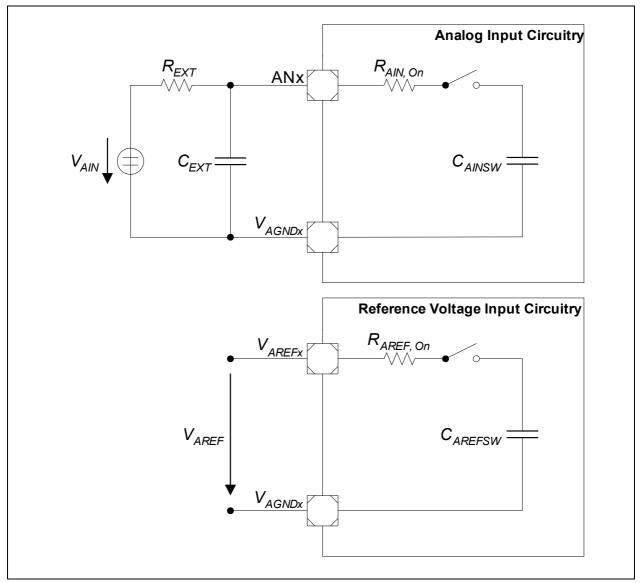

Figure 39 ADC Input Circuits

### Package and Quality Declaration

### 5.3 Quality Declaration

Table 2 shows the characteristics of the quality parameters in the XC886/888.

### Table 2Quality Parameters

| Parameter                                                             | Symbol           | Limit V | alues | Unit | Notes                                                |  |

|-----------------------------------------------------------------------|------------------|---------|-------|------|------------------------------------------------------|--|

|                                                                       |                  | Min.    | Max.  |      |                                                      |  |

| ESD susceptibility<br>according to Human Body<br>Model (HBM)          | V <sub>HBM</sub> | -       | 2000  | V    | Conforming to<br>EIA/JESD22-<br>A114-B <sup>1)</sup> |  |

| ESD susceptibility<br>according to Charged<br>Device Model (CDM) pins | V <sub>CDM</sub> | -       | 500   | V    | Conforming to JESD22-C101-C <sup>1)</sup>            |  |

1) Not all parameters are 100% tested, but are verified by design/characterization and test correlation.

www.infineon.com

Published by Infineon Technologies AG