Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                          |

| Core Processor             | XC800                                                                             |

| Core Size                  | 8-Bit                                                                             |

| Speed                      | 24MHz                                                                             |

| Connectivity               | CANbus, SSI, UART/USART                                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                             |

| Number of I/O              | 34                                                                                |

| Program Memory Size        | 32KB (32K x 8)                                                                    |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | ·                                                                                 |

| RAM Size                   | 1.75K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                       |

| Data Converters            | A/D 8x10b                                                                         |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 48-LQFP                                                                           |

| Supplier Device Package    | PG-TQFP-48                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/saf-xc886cm-8ffa-5v-ac |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Edition 2009-07 Published by Infineon Technologies AG 81726 Munich, Germany © 2009 Infineon Technologies AG All Rights Reserved.

#### Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

#### Summary of Features

Features: (continued)

- Power-on reset generation

- Brownout detection for core logic supply

- On-chip OSC and PLL for clock generation

- PLL loss-of-lock detection

- Power saving modes

- slow-down mode

- idle mode

- power-down mode with wake-up capability via RXD or EXINT0

- clock gating control to each peripheral

- Programmable 16-bit Watchdog Timer (WDT)

- Six ports

- Up to 48 pins as digital I/O

- 8 pins as digital/analog input

- 8-channel, 10-bit ADC

- Four 16-bit timers

- Timer 0 and Timer 1 (T0 and T1)

- Timer 2 and Timer 21 (T2 and T21)

- Multiplication/Division Unit for arithmetic operations (MDU)

- Software libraries to support floating point and MDU calculations

- CORDIC Coprocessor for computation of trigonometric, hyperbolic and linear functions

- MultiCAN with 2 nodes, 32 message objects

- Capture/compare unit for PWM signal generation (CCU6)

- Two full-duplex serial interfaces (UART and UART1)

- Synchronous serial channel (SSC)

- On-chip debug support

- 1 Kbyte of monitor ROM (part of the 12-Kbyte Boot ROM)

- 64 bytes of monitor RAM

- Packages:

- PG-TQFP-48

- PG-TQFP-64

- Temperature range *T*<sub>A</sub>:

- SAF (-40 to 85 °C)

- SAK (-40 to 125 °C)

# **General Device Information**

# 2 General Device Information

**Chapter 2** contains the block diagram, pin configurations, definitions and functions of the XC886/888.

# 2.1 Block Diagram

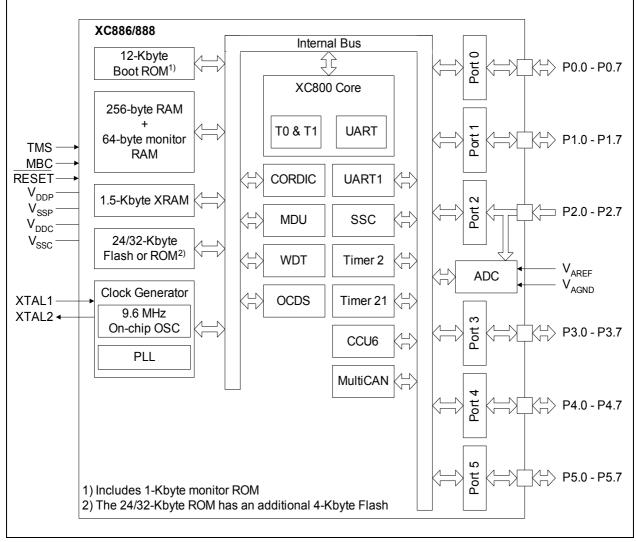

The block diagram of the XC886/888 is shown in Figure 2.

Figure 2 XC886/888 Block Diagram

#### **General Device Information**

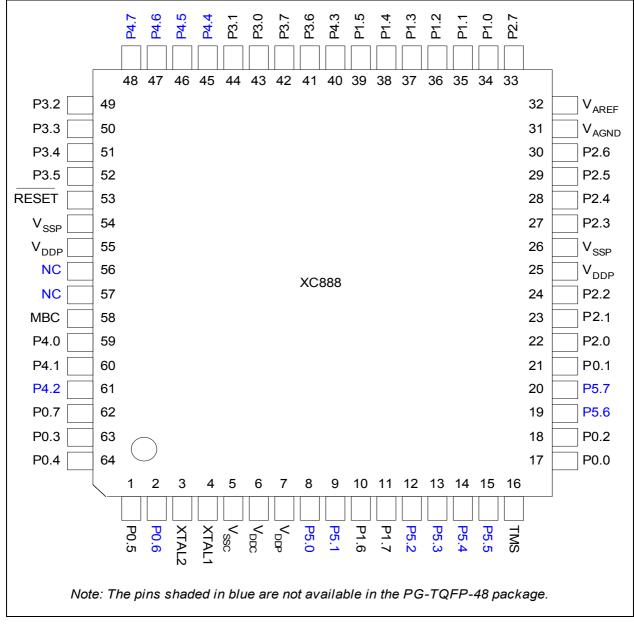

Figure 5 XC888 Pin Configuration, PG-TQFP-64 Package (top view)

# **General Device Information**

# 2.4 Pin Definitions and Functions

The functions and default states of the XC886/888 external pins are provided in Table 3.

| Symbol | Pin Number<br>(TQFP-48/64) | Туре | Reset<br>State | Function                                                                                                                                                                                        |                                                                                                                                                                                                      |  |  |  |

|--------|----------------------------|------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| P0     |                            | I/O  |                | <b>Port 0</b><br>Port 0 is an 8-bit bidirectional general purpose<br>I/O port. It can be used as alternate functions<br>for the JTAG, CCU6, UART, UART1, Timer 2<br>Timer 21, MultiCAN and SSC. |                                                                                                                                                                                                      |  |  |  |

| P0.0   | 11/17                      |      | Hi-Z           | TCK_0<br>T12HR_1<br>CC61_1<br>CLKOUT_0<br>RXDO_1                                                                                                                                                | JTAG Clock Input<br>CCU6 Timer 12 Hardware Run<br>Input<br>Input/Output of<br>Capture/Compare channel 1<br>Clock Output<br>UART Transmit Data Output                                                 |  |  |  |

| P0.1   | 13/21                      |      | Hi-Z           | TDI_0<br>T13HR_1<br>RXD_1<br>RXDC1_0<br>COUT61_1<br>EXF2_1                                                                                                                                      | JTAG Serial Data Input<br>CCU6 Timer 13 Hardware Run<br>Input<br>UART Receive Data Input<br>MultiCAN Node 1 Receiver Input<br>Output of Capture/Compare<br>channel 1<br>Timer 2 External Flag Output |  |  |  |

| P0.2   | 12/18                      |      | PU             | CTRAP_2<br>TDO_0<br>TXD_1<br>TXDC1_0                                                                                                                                                            | CCU6 Trap Input<br>JTAG Serial Data Output<br>UART Transmit Data<br>Output/Clock Output<br>MultiCAN Node 1 Transmitter<br>Output                                                                     |  |  |  |

| P0.3   | 48/63                      |      | Hi-Z           | SCK_1<br>COUT63_1<br>RXDO1_0                                                                                                                                                                    | SSC Clock Input/Output<br>Output of Capture/Compare<br>channel 3<br>UART1 Transmit Data Output                                                                                                       |  |  |  |

Table 3

Pin Definitions and Functions

Table 3

#### **General Device Information**

#### Pin Definitions and Functions (cont'd) Type Reset Function Pin Number Symbol (TQFP-48/64) State **P2** I Port 2 Port 2 is an 8-bit general purpose input-only port. It can be used as alternate functions for

|       |       |      | the digital inputs of the JTAG and CCU6. It is also used as the analog inputs for the ADC. |                                                                                        |  |  |  |

|-------|-------|------|--------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--|--|--|

| P2.0  | 14/22 | Hi-Z | CCPOS0_0<br>EXINT1_0<br>T12HR_2                                                            | CCU6 Hall Input 0<br>External Interrupt Input 1<br>CCU6 Timer 12 Hardware Run<br>Input |  |  |  |

|       |       |      | TCK_1                                                                                      | JTAG Clock Input                                                                       |  |  |  |

|       |       |      | CC61_3                                                                                     | Input of Capture/Compare<br>channel 1                                                  |  |  |  |

|       |       |      | AN0                                                                                        | Analog Input 0                                                                         |  |  |  |

| P2.1  | 15/23 | Hi-Z | CCPOS1_0<br>EXINT2_0<br>T13HR_2                                                            | CCU6 Hall Input 1<br>External Interrupt Input 2<br>CCU6 Timer 13 Hardware Run<br>Input |  |  |  |

|       |       |      | TDI_1<br>CC62_3<br>AN1                                                                     | JTAG Serial Data Input<br>Input of Capture/Compare<br>channel 2<br>Analog Input 1      |  |  |  |

| P2.2  | 16/24 | Hi-Z | CCPOS2_0                                                                                   | CCU6 Hall Input 2                                                                      |  |  |  |

| 1 2.2 | 10/24 |      | CTRAP_1                                                                                    | CCU6 Trap Input                                                                        |  |  |  |

|       |       |      | CC60_3                                                                                     | Input of Capture/Compare<br>channel 0                                                  |  |  |  |

|       |       |      | AN2                                                                                        | Analog Input 2                                                                         |  |  |  |

| P2.3  | 19/27 | Hi-Z | AN3                                                                                        | Analog Input 3                                                                         |  |  |  |

| P2.4  | 20/28 | Hi-Z | AN4                                                                                        | Analog Input 4                                                                         |  |  |  |

| P2.5  | 21/29 | Hi-Z | AN5                                                                                        | Analog Input 5                                                                         |  |  |  |

| P2.6  | 22/30 | Hi-Z | AN6                                                                                        | Analog Input 6                                                                         |  |  |  |

| P2.7  | 25/33 | Hi-Z | AN7                                                                                        | Analog Input 7                                                                         |  |  |  |

code or data. Therefore, even though the ROM device contains either a 24-Kbyte or 32-Kbyte ROM, the maximum size of code that can be placed in the ROM is the given size less four bytes.

# 3.2.1 Memory Protection Strategy

The XC886/888 memory protection strategy includes:

- Read-out protection: The user is able to protect the contents in the Flash (for Flash devices) and ROM (for ROM devices) memory from being read

- Flash protection is enabled by programming a valid password (8-bit non-zero value) via BSL mode 6.

- ROM protection is fixed with the ROM mask and is always enabled.

- Flash program and erase protection: This feature is available only for Flash devices.

# 3.2.1.1 Flash Memory Protection

As long as a valid password is available, all external access to the device, including the Flash, will be blocked.

For additional security, the Flash hardware protection can be enabled to implement a second layer of read-out protection, as well as to enable program and erase protection.

Flash hardware protection is available only for Flash devices and comes in two modes:

- Mode 0: Only the P-Flash is protected; the D-Flash is unprotected

- Mode 1: Both the P-Flash and D-Flash are protected

The selection of each protection mode and the restrictions imposed are summarized in **Table 4**.

| Flash Protection                      | Without hardware protection             | With hardware protection                     |                                                 |  |  |  |  |

|---------------------------------------|-----------------------------------------|----------------------------------------------|-------------------------------------------------|--|--|--|--|

| Hardware<br>Protection Mode           | -                                       | 0                                            | 1                                               |  |  |  |  |

| Activation                            | Program a valid password via BSL mode 6 |                                              |                                                 |  |  |  |  |

| Selection Bit 4 of password = 0       |                                         | Bit 4 of password = 1<br>MSB of password = 0 | Bit 4 of password = 1<br>MSB of password = 1    |  |  |  |  |

| P-Flash<br>contents can be<br>read by | Read instructions in any program memory | Read instructions in the P-Flash             | Read instructions in the P-Flash or D-<br>Flash |  |  |  |  |

| External access<br>to P-Flash         | Not possible                            | Not possible                                 | Not possible                                    |  |  |  |  |

#### Table 4Flash Protection Modes

| Flash Protection                      | Without hardware protection             | With hardware protection                                                                                               |                                             |  |  |  |  |

|---------------------------------------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|--|--|--|--|

| P-Flash program and erase             | Possible                                | Not possible                                                                                                           | Not possible                                |  |  |  |  |

| D-Flash<br>contents can be<br>read by | Read instructions in any program memory | Read instructions in any program memory                                                                                | Read instructions in the P-Flash or D-Flash |  |  |  |  |

| External access to D-Flash            | Not possible                            | Not possible                                                                                                           | Not possible                                |  |  |  |  |

| D-Flash<br>program                    | Possible                                | Possible                                                                                                               | Not possible                                |  |  |  |  |

| D-Flash erase                         | Possible                                | Possible, on<br>condition that bit<br>DFLASHEN in<br>register MISC_CON<br>is set to 1 prior to<br>each erase operation | Not possible                                |  |  |  |  |

#### Table 4Flash Protection Modes (cont'd)

BSL mode 6, which is used for enabling Flash protection, can also be used for disabling Flash protection. Here, the programmed password must be provided by the user. A password match triggers an automatic erase of the protected P-Flash and D-Flash contents, including the programmed password. The Flash protection is then disabled upon the next reset.

For the ROM device, the ROM is protected at all times and BSL mode 6 is used only to block external access to the device. However, unlike the Flash device, it is not possible to disable the memory protection of the ROM device. Here, entering BSL mode 6 will result in a protection error.

Note: If ROM read-out protection is enabled, only read instructions in the ROM memory can target the ROM contents.

Although no protection scheme can be considered infallible, the XC886/888 memory protection strategy provides a very high level of protection for a general purpose microcontroller.

# Table 11ADC Register Overview (cont'd)

| Addr            | Register Name                                                                   | Bit       | 7          | 6          | 5          | 4          | 3            | 2          | 1          | 0          |

|-----------------|---------------------------------------------------------------------------------|-----------|------------|------------|------------|------------|--------------|------------|------------|------------|

| cc <sup>H</sup> | ADC_CHINSR Reset: 00 <sub>H</sub><br>Channel Interrupt Set Register             | Bit Field | CHINS<br>7 | CHINS<br>6 | CHINS<br>5 | CHINS<br>4 | CHINS<br>3   | CHINS<br>2 | CHINS<br>1 | CHINS<br>0 |

|                 |                                                                                 |           | w          | w          | w          | w          | w            | w          | w          | w          |

| CDH             | ADC_CHINPR Reset: 00 <sub>H</sub><br>Channel Interrupt Node Pointer<br>Register | Bit Field | CHINP<br>7 | CHINP<br>6 | CHINP<br>5 | CHINP<br>4 | CHINP<br>3   | CHINP<br>2 | CHINP<br>1 | CHINP<br>0 |

|                 | Register                                                                        | Туре      | rw         | rw         | rw         | rw         | rw           | rw         | rw         | rw         |

| Ceh             | ADC_EVINFR Reset: 00 <sub>H</sub><br>Event Interrupt Flag Register              | Bit Field | EVINF<br>7 | EVINF<br>6 | EVINF<br>5 | EVINF<br>4 | (            | )          | EVINF<br>1 | EVINF<br>0 |

|                 |                                                                                 | Туре      | rh         | rh         | rh         | rh         |              | r          | rh         | rh         |

| CF <sub>H</sub> | ADC_EVINCR Reset: 00 <sub>H</sub><br>Event Interrupt Clear Flag                 | Bit Field | EVINC<br>7 | EVINC<br>6 | EVINC<br>5 | EVINC<br>4 | (            | )          | EVINC<br>1 | EVINC<br>0 |

|                 | Register                                                                        | Туре      | w          | w          | w          | w          |              | r          | w          | w          |

| D2 <sub>H</sub> | ADC_EVINSR Reset: 00 <sub>H</sub><br>Event Interrupt Set Flag Register          | Bit Field | EVINS<br>7 | EVINS<br>6 | EVINS<br>5 | EVINS<br>4 | (            | )          | EVINS<br>1 | EVINS<br>0 |

|                 |                                                                                 | Туре      | w          | w          | w          | w          |              | r          | w          | w          |

| D3 <sub>H</sub> | ADC_EVINPR Reset: 00 <sub>H</sub><br>Event Interrupt Node Pointer               | Bit Field | EVINP<br>7 | EVINP<br>6 | EVINP<br>5 | EVINP<br>4 | 0 EVINP<br>1 |            | EVINP<br>0 |            |

|                 | Register                                                                        | Туре      | rw         | rw         | rw         | rw         |              | r          | rw         | rw         |

| RMAP =          | = 0, PAGE 6                                                                     |           |            |            |            |            |              |            |            |            |

| CA <sub>H</sub> | ADC_CRCR1 Reset: 00 <sub>H</sub>                                                | Bit Field | CH7        | CH6        | CH5        | CH4        | 0            |            |            |            |

|                 | Conversion Request Control<br>Register 1                                        | Туре      | rwh        | rwh        | rwh        | rwh        |              | r          |            |            |

| св <sub>Н</sub> | ADC_CRPR1 Reset: 00 <sub>H</sub>                                                | Bit Field | CHP7       | CHP6       | CHP5       | CHP4       | 0            |            |            |            |

|                 | Conversion Request Pending<br>Register 1                                        | Туре      | rwh        | rwh        | rwh        | rwh        |              | I          | r          |            |

| сс <sup>н</sup> | ADC_CRMR1 Reset: 00 <sub>H</sub><br>Conversion Request Mode                     | Bit Field | Rsv        | LDEV       | CLRP<br>ND | SCAN       | ENSI         | ENTR       | 0          | ENGT       |

|                 | Register 1                                                                      | Туре      | r          | w          | w          | rw         | rw           | rw         | r          | rw         |

| CD <sub>H</sub> | ADC_QMR0 Reset: 00 <sub>H</sub><br>Queue Mode Register 0                        | Bit Field | CEV        | TREV       | FLUS<br>H  | CLRV       | 0            | ENTR       | 0          | ENGT       |

|                 |                                                                                 | Туре      | w          | w          | w          | w          | r            | rw         | r          | rw         |

| Ceh             | ADC_QSR0 Reset: 20 <sub>H</sub><br>Queue Status Register 0                      | Bit Field | Rsv        | 0          | EMPT<br>Y  | EV         | 0 FILL       |            | LL         |            |

|                 |                                                                                 | Туре      | r          | r          | rh         | rh         |              | r          | r          | h          |

| CF <sub>H</sub> | ADC_Q0R0 Reset: 00 <sub>H</sub>                                                 | Bit Field | EXTR       | ENSI       | RF         | V          | 0            | F          | REQCHN     | २          |

|                 | Queue 0 Register 0                                                              | Туре      | rh         | rh         | rh         | rh         | r            |            | rh         |            |

| D2 <sub>H</sub> | ADC_QBUR0 Reset: 00 <sub>H</sub>                                                | Bit Field | EXTR       | ENSI       | RF         | V          | 0            | F          | REQCHN     | ۲          |

|                 | Queue Backup Register 0                                                         | Туре      | rh         | rh         | rh         | rh         | r            |            | rh         |            |

| D2 <sub>H</sub> | ADC_QINR0 Reset: 00 <sub>H</sub>                                                | Bit Field | EXTR       | ENSI       | RF         | (          | )            | F          | REQCHN     | २          |

|                 | Queue Input Register 0                                                          | Туре      | w          | w          | w          |            | r            |            | w          |            |

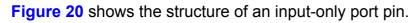

Figure 20 General Structure of Input Port

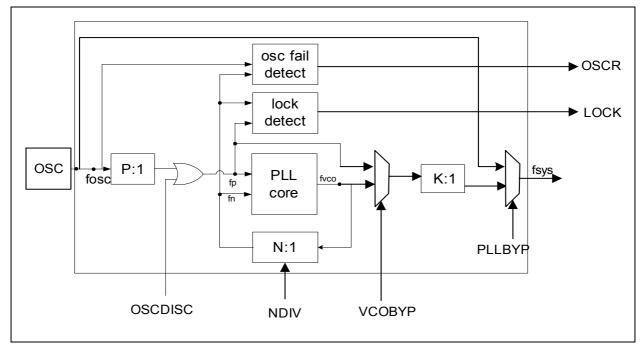

### Figure 24 CGU Block Diagram

#### **PLL Base Mode**

When the oscillator is disconnected from the PLL, the system clock is derived from the VCO base (free running) frequency clock (**Table 25**) divided by the K factor.

$$f_{SYS} = f_{VCObase} \times \frac{1}{K}$$

(3.1)

# Prescaler Mode (VCO Bypass Operation)

In VCO bypass operation, the system clock is derived from the oscillator clock, divided by the P and K factors.

$$f_{SYS} = f_{OSC} \times \frac{1}{P \times K}$$

(3.2)

Table 25 shows the VCO range for the XC886/888.

| <i>f</i> <sub>vcomin</sub> | f <sub>VCOmax</sub> | $f_{\sf VCOFREEmin}$ | <b><i>f</i></b> <sub>VCOFREEmax</sub> | Unit |

|----------------------------|---------------------|----------------------|---------------------------------------|------|

| 150                        | 200                 | 20                   | 80                                    | MHz  |

| 100                        | 150                 | 10                   | 80                                    | MHz  |

# 3.8.1 Recommended External Oscillator Circuits

The oscillator circuit, a Pierce oscillator, is designed to work with both, an external crystal oscillator or an external stable clock source. It basically consists of an inverting amplifier and a feedback element with XTAL1 as input, and XTAL2 as output.

When using a crystal, a proper external oscillator circuitry must be connected to both pins, XTAL1 and XTAL2. The crystal frequency can be within the range of 4 MHz to 12 MHz. Additionally, it is necessary to have two load capacitances  $C_{X1}$  and  $C_{X2}$ , and depending on the crystal type, a series resistor  $R_{X2}$ , to limit the current. A test resistor  $R_Q$  may be temporarily inserted to measure the oscillation allowance (negative resistance) of the oscillator circuitry.  $R_Q$  values are typically specified by the crystal vendor. The  $C_{X1}$  and  $C_{X2}$  values shown in **Figure 25** can be used as starting points for the negative resistance evaluation and for non-productive systems. The exact values and related operating range are dependent on the crystal frequency and have to be determined and optimized together with the final target system is strongly recommended to verify the input amplitude at XTAL1 and to determine the actual oscillation allowance (margin negative resistance) for the oscillator-crystal system.

When using an external clock signal, the signal must be connected to XTAL1. XTAL2 is left open (unconnected).

The oscillator can also be used in combination with a ceramic resonator. The final circuitry must also be verified by the resonator vendor. **Figure 25** shows the recommended external oscillator circuitries for both operating modes, external crystal mode and external input clock mode.

For power saving purposes, the clocks may be disabled or slowed down according to **Table 26**.

# Table 26System frequency ( $f_{sys}$ = 96 MHz)

| Power Saving Mode | Action                                                                                                                   |  |  |  |  |  |  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Idle              | Clock to the CPU is disabled.                                                                                            |  |  |  |  |  |  |

| Slow-down         | Clocks to the CPU and all the peripherals are divided by a common programmable factor defined by bit field CMCON.CLKREL. |  |  |  |  |  |  |

| Power-down        | Oscillator and PLL are switched off.                                                                                     |  |  |  |  |  |  |

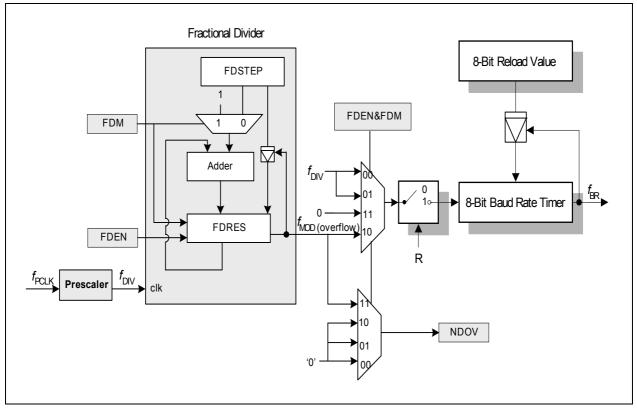

fractional divider) for generating a wide range of baud rates based on its input clock  $f_{PCLK}$ , see **Figure 30**.

#### Figure 30 Baud-rate Generator Circuitry

The baud rate timer is a count-down timer and is clocked by either the output of the fractional divider ( $f_{MOD}$ ) if the fractional divider is enabled (FDCON.FDEN = 1), or the output of the prescaler ( $f_{DIV}$ ) if the fractional divider is disabled (FDEN = 0). For baud rate generation, the fractional divider must be configured to fractional divider mode (FDCON.FDM = 0). This allows the baud rate control run bit BCON.R to be used to start or stop the baud rate timer. At each timer underflow, the timer is reloaded with the 8-bit reload value in register BG and one clock pulse is generated for the serial channel.

Enabling the fractional divider in normal divider mode (FDEN = 1 and FDM = 1) stops the baud rate timer and nullifies the effect of bit BCON.R. See **Section 3.14**.

The baud rate ( $f_{BR}$ ) value is dependent on the following parameters:

- Input clock  $f_{PCLK}$

- Prescaling factor (2<sup>BRPRE</sup>) defined by bit field BRPRE in register BCON

- Fractional divider (STEP/256) defined by register FDSTEP (to be considered only if fractional divider is enabled and operating in fractional divider mode)

- 8-bit reload value (BR\_VALUE) for the baud rate timer defined by register BG

# 3.18 Timer 2 and Timer 21

Timer 2 and Timer 21 are 16-bit general purpose timers (THL2) that are fully compatible and have two modes of operation, a 16-bit auto-reload mode and a 16-bit one channel capture mode, see **Table 33**. As a timer, the timers count with an input clock of PCLK/12 (if prescaler is disabled). As a counter, they count 1-to-0 transitions on pin T2. In the counter mode, the maximum resolution for the count is PCLK/24 (if prescaler is disabled).

| Table 33           | Timer 2 Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Mode               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| Auto-reload        | <ul> <li>Up/Down Count Disabled</li> <li>Count up only</li> <li>Start counting from 16-bit reload value, overflow at FFFF<sub>H</sub></li> <li>Reload event configurable for trigger by overflow condition only, or by negative/positive edge at input pin T2EX as well</li> <li>Programmble reload value in register RC2</li> <li>Interrupt is generated with reload event</li> </ul>                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

|                    | <ul> <li>Up/Down Count Enabled</li> <li>Count up or down, direction determined by level at input pin T2EX</li> <li>No interrupt is generated</li> <li>Count up <ul> <li>Start counting from 16-bit reload value, overflow at FFFF<sub>H</sub></li> <li>Reload event triggered by overflow condition</li> <li>Programmble reload value in register RC2</li> </ul> </li> <li>Count down <ul> <li>Start counting from FFFF<sub>H</sub>, underflow at value defined in register RC2</li> <li>Reload event triggered by underflow condition <ul> <li>Reload event triggered by underflow condition</li> <li>Reload event triggered by underflow condition</li> </ul> </li> </ul></li></ul> |  |  |  |  |  |  |

| Channel<br>capture | <ul> <li>Count up only</li> <li>Start counting from 0000<sub>H</sub>, overflow at FFFF<sub>H</sub></li> <li>Reload event triggered by overflow condition</li> <li>Reload value fixed at 0000<sub>H</sub></li> <li>Capture event triggered by falling/rising edge at pin T2EX</li> <li>Captured timer value stored in register RC2</li> <li>Interrupt is generated with reload or capture event</li> </ul>                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

#### **Electrical Parameters**

| Parameter                                                      | Symbol            |    | Limit                       | Values                      | Unit | Test Conditions           |  |

|----------------------------------------------------------------|-------------------|----|-----------------------------|-----------------------------|------|---------------------------|--|

|                                                                |                   |    | min.                        | max.                        |      |                           |  |

| Maximum current out of $V_{\rm SS}$                            | I <sub>MVSS</sub> | SR | -                           | 120                         | mA   | 3)                        |  |

| $V_{\text{DDP}}$ = 3.3 V Range                                 |                   |    |                             |                             |      |                           |  |

| Output low voltage                                             | $V_{OL}$          | CC | _                           | 1.0                         | V    | I <sub>OL</sub> = 8 mA    |  |

|                                                                |                   |    | -                           | 0.4                         | V    | I <sub>OL</sub> = 2.5 mA  |  |

| Output high voltage                                            | V <sub>OH</sub>   | CC | V <sub>DDP</sub> -<br>1.0   | -                           | V    | I <sub>OH</sub> = -8 mA   |  |

|                                                                |                   |    | V <sub>DDP</sub> - 0.4      | -                           | V    | I <sub>ОН</sub> = -2.5 mA |  |

| Input low voltage on<br>port pins<br>(all except P0.0 & P0.1)  | V <sub>ILP</sub>  | SR | _                           | $0.3 \times V_{\text{DDP}}$ | V    | CMOS Mode                 |  |

| Input low voltage on P0.0 & P0.1                               | V <sub>ILP0</sub> | SR | -0.2                        | $0.3 \times V_{ m DDP}$     | V    | CMOS Mode                 |  |

| Input low voltage on RESET pin                                 | $V_{ILR}$         | SR | -                           | $0.3 \times V_{\text{DDP}}$ | V    | CMOS Mode                 |  |

| Input low voltage on<br>TMS pin                                | V <sub>ILT</sub>  | SR | -                           | $0.3 \times V_{\text{DDP}}$ | V    | CMOS Mode                 |  |

| Input high voltage on<br>port pins<br>(all except P0.0 & P0.1) | V <sub>IHP</sub>  | SR | $0.7 \times V_{\text{DDP}}$ | -                           | V    | CMOS Mode                 |  |

| Input high voltage on P0.0 & P0.1                              | V <sub>IHP0</sub> | SR | $0.7 \times V_{\text{DDP}}$ | V <sub>DDP</sub>            | V    | CMOS Mode                 |  |

| Input high voltage on RESET pin                                | $V_{IHR}$         | SR | $0.7 \times V_{ m DDP}$     | -                           | V    | CMOS Mode                 |  |

| Input high voltage on<br>TMS pin                               | V <sub>IHT</sub>  | SR | $0.75 \times V_{ m DDP}$    | -                           | V    | CMOS Mode                 |  |

| Input Hysteresis                                               | HYS               | CC | $0.03 \times V_{ m DDP}$    | -                           | V    | CMOS Mode <sup>1)</sup>   |  |

| Input Hysteresis on XTAL1                                      | HYSX              | CC | $0.07 \times V_{ m DDC}$    | -                           | V    | 1)                        |  |

| Input low voltage at XTAL1                                     | V <sub>ILX</sub>  | SR | V <sub>SS</sub> -<br>0.5    | $0.3 \times V_{ m DDC}$     | V    |                           |  |

### **Electrical Parameters**

#### Table 40ADC Characteristics (Operating Conditions apply; $V_{DDP}$ = 5V Range)

|                                                              |                    |    |      | ~            |                           | -  |                         |

|--------------------------------------------------------------|--------------------|----|------|--------------|---------------------------|----|-------------------------|

| Parameter                                                    | Symbol             |    | Liı  | Limit Values |                           |    | Test Conditions/        |

|                                                              |                    |    | min. | typ .        | max.                      |    | Remarks                 |

| Overload current coupling factor for                         | K <sub>OVD</sub>   | CC | -    | -            | 5.0 x<br>10 <sup>-3</sup> | -  | $I_{\rm OV} > 0^{1)3)$  |

| digital I/O pins                                             |                    |    | -    | -            | 1.0 x<br>10 <sup>-2</sup> | -  | $I_{\rm OV} < 0^{1)3)}$ |

| Switched<br>capacitance at the<br>reference voltage<br>input | CAREFSW            | CC | _    | 10           | 20                        | pF | 1)4)                    |

| Switched<br>capacitance at the<br>analog voltage<br>inputs   | C <sub>AINSW</sub> | CC | _    | 5            | 7                         | pF | 1)5)                    |

| Input resistance of the reference input                      | R <sub>AREF</sub>  | CC | -    | 1            | 2                         | kΩ | 1)                      |

| Input resistance of<br>the selected analog<br>channel        | R <sub>AIN</sub>   | CC | _    | 1            | 1.5                       | kΩ | 1)                      |

1) Not subjected to production test, verified by design/characterization

2) TUE is tested at  $V_{\text{AREF}}$  = 5.0 V,  $V_{\text{AGND}}$  = 0 V,  $V_{\text{DDP}}$  = 5.0 V.

- 3) An overload current  $(I_{OV})$  through a pin injects a certain error current  $(I_{INJ})$  into the adjacent pins. This error current adds to the respective pin's leakage current  $(I_{OZ})$ . The amount of error current depends on the overload current and is defined by the overload coupling factor  $K_{OV}$ . The polarity of the injected error current is inverse compared to the polarity of the overload current that produces it. The total current through a pin is  $|I_{TOT}| = |I_{OZ1}| + (|I_{OV}| \times K_{OV})$ . The additional error current may distort the input voltage on analog inputs.

- 4) This represents an equivalent switched capacitance. This capacitance is not switched to the reference voltage at once. Instead of this, smaller capacitances are successively switched to the reference voltage.

- 5) The sampling capacity of the conversion C-Network is pre-charged to  $V_{AREF}/2$  before connecting the input to the C-Network. Because of the parasitic elements, the voltage measured at ANx is lower than  $V_{AREF}/2$ .

#### **Electrical Parameters**

# 4.2.3.1 ADC Conversion Timing

Conversion time,  $t_{\rm C} = t_{\rm ADC} \times (1 + r \times (3 + n + STC))$ , where r = CTC + 2 for CTC =  $00_{\rm B}$ ,  $01_{\rm B}$  or  $10_{\rm B}$ , r = 32 for CTC =  $11_{\rm B}$ , CTC = Conversion Time Control (GLOBCTR.CTC), STC = Sample Time Control (INPCR0.STC), n = 8 or 10 (for 8-bit and 10-bit conversion respectively),  $t_{\rm ADC} = 1 / f_{\rm ADC}$

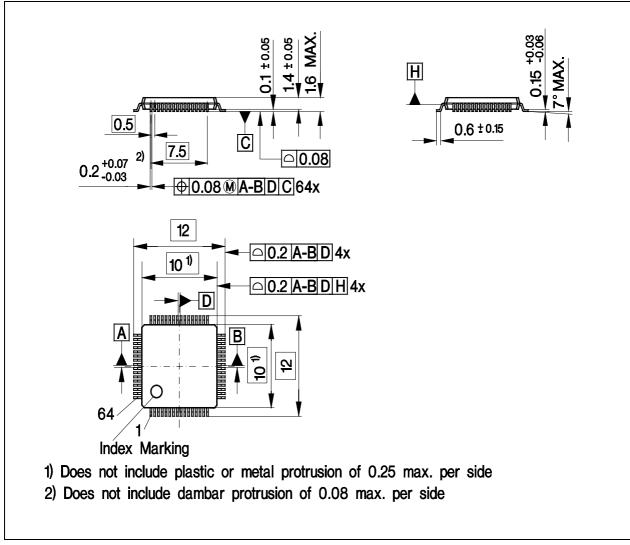

#### Package and Quality Declaration

### Figure 49 PG-TQFP-64 Package Outline

### Package and Quality Declaration

# 5.3 Quality Declaration

Table 2 shows the characteristics of the quality parameters in the XC886/888.

### Table 2Quality Parameters

| Parameter                                                             | Symbol           | Limit Values |      | Unit | Notes                                                |

|-----------------------------------------------------------------------|------------------|--------------|------|------|------------------------------------------------------|

|                                                                       |                  | Min.         | Max. |      |                                                      |

| ESD susceptibility<br>according to Human Body<br>Model (HBM)          | V <sub>HBM</sub> | -            | 2000 | V    | Conforming to<br>EIA/JESD22-<br>A114-B <sup>1)</sup> |

| ESD susceptibility<br>according to Charged<br>Device Model (CDM) pins | V <sub>CDM</sub> | -            | 500  | V    | Conforming to JESD22-C101-C <sup>1)</sup>            |

1) Not all parameters are 100% tested, but are verified by design/characterization and test correlation.