Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Details                    |                                                                                    |

|----------------------------|------------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                           |

| Core Processor             | XC800                                                                              |

| Core Size                  | 8-Bit                                                                              |

| Speed                      | 24MHz                                                                              |

| Connectivity               | CANbus, SSI, UART/USART                                                            |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                              |

| Number of I/O              | 34                                                                                 |

| Program Memory Size        | 32KB (32K x 8)                                                                     |

| Program Memory Type        | FLASH                                                                              |

| EEPROM Size                |                                                                                    |

| RAM Size                   | 1.75K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                          |

| Data Converters            | A/D 8x10b                                                                          |

| Oscillator Type            | Internal                                                                           |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                  |

| Mounting Type              | Surface Mount                                                                      |

| Package / Case             | 48-LQFP                                                                            |

| Supplier Device Package    | PG-TQFP-48                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/saf-xc886cm-8ffi-3v3-ac |

|                            |                                                                                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **General Device Information**

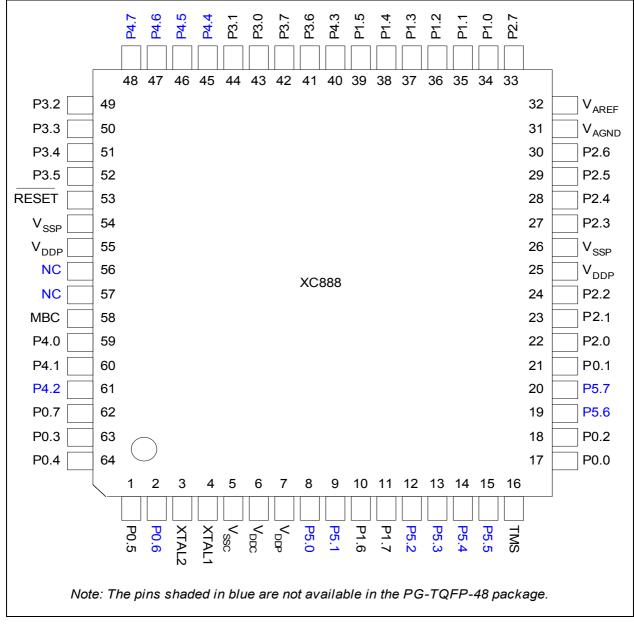

Figure 5 XC888 Pin Configuration, PG-TQFP-64 Package (top view)

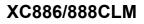

Address Extension by Mapping

SYSCON0

### **Functional Description**

#### System Control Register 0 Reset Value: 04 7 5 4 3 2 1 0 6 IMODE 1 RMAP 0 0 0 r r r r rw rw

| Field | Bits          | Туре | Description                                                                                                                                                    |

|-------|---------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RMAP  | 0             | rw   | <ul> <li>Interrupt Node XINTR0 Enable</li> <li>The access to the standard SFR area is enabled</li> <li>The access to the mapped SFR area is enabled</li> </ul> |

| 1     | 2             | r    | <b>Reserved</b><br>Returns 1 if read; should be written with 1.                                                                                                |

| 0     | [7:5],<br>3,1 | r    | <b>Reserved</b><br>Returns 0 if read; should be written with 0.                                                                                                |

Note: The RMAP bit should be cleared/set by ANL or ORL instructions.

## 3.2.2.2 Address Extension by Paging

Address extension is further performed at the module level by paging. With the address extension by mapping, the XC886/888 has a 256-SFR address range. However, this is still less than the total number of SFRs needed by the on-chip peripherals. To meet this requirement, some peripherals have a built-in local address extension mechanism for increasing the number of addressable SFRs. The extended address range is not directly controlled by the CPU instruction itself, but is derived from bit field PAGE in the module page register MOD\_PAGE. Hence, the bit field PAGE must be programmed before accessing the SFR of the target module. Each module may contain a different number of pages and a different number of SFRs per page, depending on the specific requirement. Besides setting the correct RMAP bit value to select the SFR area, the user must also ensure that a valid PAGE is selected to target the desired SFR. A page inside the extended address range can be selected as shown in **Figure 9**.

# 3.2.3.1 Password Register

# PASSWD

| Pass       | word | Register |      |   |   |               | Reset | Value: 07 <sub>H</sub> |

|------------|------|----------|------|---|---|---------------|-------|------------------------|

|            | 7    | 6        | 5    | 4 | 3 | 2             | 1     | 0                      |

|            |      | 1        | PASS | 1 |   | PROTECT<br>_S | МС    | DE                     |

| . <u> </u> |      |          | wh   |   |   | rh            | r     | W                      |

| Field     | Bits  | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------|-------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MODE      | [1:0] | rw   | <ul> <li>Bit Protection Scheme Control Bits</li> <li>00 Scheme disabled - direct access to the protected bits is allowed.</li> <li>11 Scheme enabled - the bit field PASS has to be written with the passwords to open and close the access to protected bits. (default)</li> <li>Others:Scheme Enabled.</li> <li>These two bits cannot be written directly. To change the value between 11<sub>B</sub> and 00<sub>B</sub>, the bit field PASS must be written with 11000<sub>B</sub>; only then, will the MODE[1:0] be registered.</li> </ul> |

| PROTECT_S | 2     | rh   | <ul> <li>Bit Protection Signal Status Bit</li> <li>This bit shows the status of the protection.</li> <li>0 Software is able to write to all protected bits.</li> <li>1 Software is unable to write to any protected bits.</li> </ul>                                                                                                                                                                                                                                                                                                           |

| PASS      | [7:3] | wh   | Password BitsThe Bit Protection Scheme only recognizes threepatterns. $11000_B$ Enables writing of the bit field MODE. $10011_B$ Opens access to writing of all protected bits. $10101_B$ Closes access to writing of all protected bits                                                                                                                                                                                                                                                                                                       |

| Addr            | Register Name                                                     | Bit       | 7           | 6           | 5           | 4           | 3    | 2    | 1         | 0         |

|-----------------|-------------------------------------------------------------------|-----------|-------------|-------------|-------------|-------------|------|------|-----------|-----------|

| A8 <sub>H</sub> | IEN0 Reset: 00 <sub>H</sub>                                       | Bit Field | EA          | 0           | ET2         | ES          | ET1  | EX1  | ET0       | EX0       |

|                 | Interrupt Enable Register 0                                       | Туре      | rw          | r           | rw          | rw          | rw   | rw   | rw        | rw        |

| B8 <sub>H</sub> | IP Reset: 00 <sub>H</sub>                                         | Bit Field | (           | )           | PT2         | PS          | PT1  | PX1  | PT0       | PX0       |

|                 | Interrupt Priority Register                                       | Туре      |             | r           | rw          | rw          | rw   | rw   | rw        | rw        |

| в9 <sub>Н</sub> | IPH Reset: 00 <sub>H</sub>                                        | Bit Field | (           | )           | PT2H        | PSH         | PT1H | PX1H | PT0H      | PX0H      |

|                 | Interrupt Priority High Register                                  | Туре      |             | r           | rw          | rw          | rw   | rw   | rw        | rw        |

| D0 <sub>H</sub> | PSW Reset: 00 <sub>H</sub>                                        | Bit Field | CY          | AC          | F0          | RS1         | RS0  | OV   | F1        | Р         |

|                 | Program Status Word Register                                      | Туре      | rwh         | rwh         | rw          | rw          | rw   | rwh  | rw        | rh        |

| E0 <sub>H</sub> | ACC Reset: 00 <sub>H</sub>                                        | Bit Field | ACC7        | ACC6        | ACC5        | ACC4        | ACC3 | ACC2 | ACC1      | ACC0      |

|                 | Accumulator Register                                              | Туре      | rw          | rw          | rw          | rw          | rw   | rw   | rw        | rw        |

| E8 <sub>H</sub> | IEN1 Reset: 00 <sub>H</sub><br>Interrupt Enable Register 1        | Bit Field | ECCIP<br>3  | ECCIP<br>2  | ECCIP<br>1  | ECCIP<br>0  | EXM  | EX2  | ESSC      | EADC      |

|                 |                                                                   | Туре      | rw          | rw          | rw          | rw          | rw   | rw   | rw        | rw        |

| F0 <sub>H</sub> | B Reset: 00 <sub>H</sub>                                          | Bit Field | B7          | B6          | B5          | B4          | B3   | B2   | B1        | B0        |

|                 | B Register                                                        | Туре      | rw          | rw          | rw          | rw          | rw   | rw   | rw        | rw        |

| F8 <sub>H</sub> | IP1 Reset: 00 <sub>H</sub><br>Interrupt Priority 1 Register       | Bit Field | PCCIP<br>3  | PCCIP<br>2  | PCCIP<br>1  | PCCIP<br>0  | PXM  | PX2  | PSSC      | PADC      |

|                 |                                                                   | Туре      | rw          | rw          | rw          | rw          | rw   | rw   | rw        | rw        |

| F9 <sub>H</sub> | IPH1 Reset: 00 <sub>H</sub><br>Interrupt Priority 1 High Register | Bit Field | PCCIP<br>3H | PCCIP<br>2H | PCCIP<br>1H | PCCIP<br>0H | PXMH | PX2H | PSSC<br>H | PADC<br>H |

|                 |                                                                   | Туре      | rw          | rw          | rw          | rw          | rw   | rw   | rw        | rw        |

#### Table 5CPU Register Overview (cont'd)

## 3.2.4.2 MDU Registers

The MDU SFRs can be accessed in the mapped memory area (RMAP = 1).

### Table 6MDU Register Overview

| Addr            | Register Name                                         | Bit       | 7                           | 6 | 5 | 4  | 3  | 2   | 1    | 0    |  |

|-----------------|-------------------------------------------------------|-----------|-----------------------------|---|---|----|----|-----|------|------|--|

| RMAP =          | MAP = 1                                               |           |                             |   |   |    |    |     |      |      |  |

| в0 <sub>Н</sub> | MDUSTAT Reset: 00 <sub>H</sub>                        | Bit Field |                             |   | 0 |    |    | BSY | IERR | IRDY |  |

|                 | MDU Status Register                                   | Туре      |                             |   | r |    |    | rh  | rwh  | rwh  |  |

| в1 <sub>Н</sub> | MDUCON Reset: 00 <sub>H</sub><br>MDU Control Register | Bit Field | IE IR RSEL STAR OPCODE<br>T |   |   |    |    |     |      |      |  |

|                 |                                                       | Туре      | rw rw rw rwh rw             |   |   |    |    |     |      |      |  |

| B2 <sub>H</sub> | MD0 Reset: 00 <sub>H</sub>                            | Bit Field | ield DATA                   |   |   |    |    |     |      |      |  |

|                 | MDU Operand Register 0                                | Туре      | rw                          |   |   |    |    |     |      |      |  |

| B2 <sub>H</sub> | MR0 Reset: 00 <sub>H</sub>                            | Bit Field |                             |   |   | DA | TA |     |      |      |  |

|                 | MDU Result Register 0                                 | Туре      | rh                          |   |   |    |    |     |      |      |  |

| вз <sub>Н</sub> | MD1 Reset: 00 <sub>H</sub>                            | Bit Field | DATA                        |   |   |    |    |     |      |      |  |

|                 | MDU Operand Register 1                                | Туре      |                             |   |   | r  | W  |     |      |      |  |

### Table 7CORDIC Register Overview (cont'd)

| Addr            | Register Name                                             | Bit       | 7         | 6         | 5           | 4           | 3          | 2    | 1         | 0   |

|-----------------|-----------------------------------------------------------|-----------|-----------|-----------|-------------|-------------|------------|------|-----------|-----|

| A0 <sub>H</sub> | CD_STATC Reset: 00 <sub>H</sub><br>CORDIC Status and Data | Bit Field | KEEP<br>Z | KEEP<br>Y | KEEP<br>X   | DMAP        | INT_E<br>N | EOC  | ERRO<br>R | BSY |

|                 | Control Register                                          | Туре      | rw        | rw        | rw          | rw          | rw         | rwh  | rh        | rh  |

| А1 <sub>Н</sub> | CD_CON Reset: 00 <sub>H</sub><br>CORDIC Control Register  | Bit Field | MPS       |           | X_USI<br>GN | ST_M<br>ODE | ROTV<br>EC | MODE |           | ST  |

|                 |                                                           | Туре      | r         | N         | rw          | rw          | rw         | r    | v         | rwh |

## 3.2.4.4 System Control Registers

The system control SFRs can be accessed in the mapped memory area (RMAP = 0).

#### Addr Bit 7 3 2 1 **Register Name** 6 5 4 0 RMAP = 0 or 1 IMOD 8F<sub>H</sub> SYSCON0 Reset: 04<sub>H</sub> Bit Field 0 0 1 0 RMAP System Control Register 0 F r r r r rw Туре rw RMAP = 0 SCU\_PAGE STNR PAGE BFH Reset: 00<sub>H</sub> Bit Field OP 0 Page Register Туре w w r rw RMAP = 0, PAGE 0 Reset: 00<sub>H</sub> Bit Field URRIS JTAGT JTAGT EXINT EXINT EXINT URRIS MODPISEL 0 B3<sub>H</sub> Peripheral Input Select Register Н DIS CKS 2IS 1IS 0IS rw Туре r rw rw rw rw rw rw Reset: 00<sub>H</sub> B4<sub>H</sub> **IRCON0** Bit Field 0 **EXINT** EXINT EXINT EXINT EXINT EXINT EXINT Interrupt Request Register 0 4 3 0 6 5 2 1 rwh Туре r rwh rwh rwh rwh rwh rwh Reset: 00<sub>H</sub> в5<sub>Н</sub> CANS **IRCON1** Bit Field 0 CANS ADCS ADCS RIR TIR EIR Interrupt Request Register 1 RC2 RC1 R0 R1 Туре r rwh rwh rwh rwh rwh rwh rwh B6<sub>H</sub> Reset: 00<sub>H</sub> 0 CANS 0 CANS **IRCON2** Bit Field Interrupt Request Register 2 RC3 RC0 Туре rwh rwh r r B7<sub>H</sub> EXICON0 EXINT3 EXINT2 EXINT1 EXINT0 Reset: F0µ Bit Field External Interrupt Control Туре rw rw rw rw Register 0 Reset: 3F<sub>H</sub> BAH EXICON1 Bit Field 0 EXINT6 EXINT5 EXINT4 External Interrupt Control rw rw rw Туре r Register 1 ввн NMICON Reset: 00<sub>H</sub> Bit Field 0 NMI NMI NMI NMI NMI NMI NMI NMI Control Register ECC VDDP VDD OCDS FLASH PLL WDT Туре r rw rw rw rw rw rw rw

#### Table 8SCU Register Overview

# Table 14CCU6 Register Overview (cont'd)

| Addr            | Register Name                                                         | Bit       | 7                                           | 6    | 5        | 4    | 3      | 2        | 1        | 0    |  |

|-----------------|-----------------------------------------------------------------------|-----------|---------------------------------------------|------|----------|------|--------|----------|----------|------|--|

| FA <sub>H</sub> | CCU6_CC60SRL Reset: 00 <sub>H</sub>                                   | Bit Field |                                             |      | <u> </u> | CC6  | OSL    | <u> </u> | <u> </u> |      |  |

|                 | Capture/Compare Shadow Register<br>for Channel CC60 Low               | Туре      |                                             |      |          | rv   | vh     |          |          |      |  |

| FB <sub>H</sub> | CCU6_CC60SRH Reset: 00 <sub>H</sub>                                   | Bit Field | CC60SH                                      |      |          |      |        |          |          |      |  |

|                 | Capture/Compare Shadow Register<br>for Channel CC60 High              | Туре      | rwh                                         |      |          |      |        |          |          |      |  |

| FC <sub>H</sub> | CCU6_CC61SRL Reset: 00 <sub>H</sub>                                   | Bit Field | CC61SL                                      |      |          |      |        |          |          |      |  |

|                 | Capture/Compare Shadow Register<br>for Channel CC61 Low               | Туре      | Type rwh                                    |      |          |      |        |          |          |      |  |

| FD <sub>H</sub> | CCU6_CC61SRH Reset: 00 <sub>H</sub>                                   | Bit Field |                                             |      |          | CC6  | 1SH    |          |          |      |  |

|                 | Capture/Compare Shadow Register<br>for Channel CC61 High              | Туре      |                                             |      |          | rv   | vh     |          |          |      |  |

| Fe <sub>H</sub> | CCU6_CC62SRL Reset: 00 <sub>H</sub>                                   | Bit Field |                                             |      |          | CC6  | 2SL    |          |          |      |  |

|                 | Capture/Compare Shadow Register<br>for Channel CC62 Low               | Туре      |                                             |      |          | rv   | vh     |          |          |      |  |

| FF <sub>H</sub> | CCU6_CC62SRH Reset: 00 <sub>H</sub>                                   | Bit Field |                                             |      |          | CC6  | 2SH    |          |          |      |  |

|                 | Capture/Compare Shadow Register<br>for Channel CC62 High              | Туре      |                                             |      |          | rv   | vh     |          |          |      |  |

| RMAP =          | 0, PAGE 1                                                             |           |                                             |      |          |      |        |          |          |      |  |

| 9A <sub>H</sub> | CCU6_CC63RL Reset: 00 <sub>H</sub>                                    | Bit Field |                                             |      |          | CC6  | 3VL    |          |          |      |  |

|                 | Capture/Compare Register for<br>Channel CC63 Low                      | Туре      |                                             |      |          | r    | h      |          |          |      |  |

| 98 <sub>H</sub> | CCU6_CC63RH Reset: 00 <sub>H</sub>                                    | Bit Field | CC63VH                                      |      |          |      |        |          |          |      |  |

|                 | Capture/Compare Register for<br>Channel CC63 High                     | Туре      | rh                                          |      |          |      |        |          |          |      |  |

| 9CH             | CCU6_T12PRL Reset: 00 <sub>H</sub>                                    | Bit Field | d T12PVL                                    |      |          |      |        |          |          |      |  |

|                 | Timer T12 Period Register Low                                         | Туре      | rwh                                         |      |          |      |        |          |          |      |  |

| 9D <sub>H</sub> | CCU6_T12PRH Reset: 00 <sub>H</sub><br>Timer T12 Period Register High  | Bit Field | T12PVH                                      |      |          |      |        |          |          |      |  |

|                 |                                                                       | Туре      | rwh                                         |      |          |      |        |          |          |      |  |

| 9E <sub>H</sub> | CCU6_T13PRLReset: 00HTimer T13 Period Register Low                    | Bit Field | T13PVL                                      |      |          |      |        |          |          |      |  |

|                 |                                                                       | Туре      |                                             |      |          | rv   | vh     |          |          |      |  |

| 9F <sub>H</sub> | CCU6_T13PRH Reset: 00 <sub>H</sub><br>Timer T13 Period Register High  | Bit Field |                                             |      |          | T13  | PVH    |          |          |      |  |

|                 |                                                                       | Туре      |                                             |      |          | rv   | vh     |          |          |      |  |

| A4 <sub>H</sub> | CCU6_T12DTCL Reset: 00 <sub>H</sub><br>Dead-Time Control Register for | Bit Field |                                             |      |          | D    | ΓM     |          |          |      |  |

|                 | Timer T12 Low                                                         | Туре      |                                             |      |          | r    | N      |          |          |      |  |

| А5 <sub>Н</sub> | CCU6_T12DTCH Reset: 00 <sub>H</sub><br>Dead-Time Control Register for | Bit Field | 0                                           | DTR2 | DTR1     | DTR0 | 0      | DTE2     | DTE1     | DTE0 |  |

|                 | Timer T12 High                                                        | Туре      | r                                           | rh   | rh       | rh   | r      | rw       | rw       | rw   |  |

| A6 <sub>H</sub> | CCU6_TCTR0L Reset: 00 <sub>H</sub><br>Timer Control Register 0 Low    | Bit Field | CTM CDIR STE1 T12R T12 T12CL<br>2 PRE T12CL |      |          |      | T12CLK |          |          |      |  |

|                 |                                                                       | Туре      | rw rh rh rh rw rw                           |      |          |      |        |          |          |      |  |

| А7 <sub>Н</sub> | CCU6_TCTR0H Reset: 00 <sub>H</sub><br>Timer Control Register 0 High   | Bit Field |                                             |      |          |      |        |          |          |      |  |

|                 |                                                                       | Туре      |                                             | r    | rh       | rh   | rw     |          | rw       |      |  |

| FA <sub>H</sub> | CCU6_CC60RL Reset: 00 <sub>H</sub>                                    | Bit Field |                                             |      |          | CC6  | 60VL   |          |          |      |  |

|                 | Capture/Compare Register for<br>Channel CC60 Low                      | Туре      |                                             |      |          | r    | h      |          |          |      |  |

#### Table 17CAN Register Overview (cont'd)

| Addr            | Register Name                | Bit       | 7           | 6 | 5  | 4 | 3 | 2 | 1 | 0 |  |  |

|-----------------|------------------------------|-----------|-------------|---|----|---|---|---|---|---|--|--|

| db <sub>h</sub> | DATA0 Reset: 00 <sub>H</sub> | Bit Field | CD          |   |    |   |   |   |   |   |  |  |

|                 | CAN Data Register 0          | Туре      | rwh         |   |    |   |   |   |   |   |  |  |

| DC <sub>H</sub> | DATA1 Reset: 00 <sub>H</sub> | Bit Field |             |   | CD |   |   |   |   |   |  |  |

|                 | CAN Data Register 1          | Туре      | e rwh       |   |    |   |   |   |   |   |  |  |

| dd <sub>H</sub> | DATA2 Reset: 00 <sub>H</sub> | Bit Field |             |   |    | С | D |   |   |   |  |  |

|                 | CAN Data Register 2          | Туре      | rwh         |   |    |   |   |   |   |   |  |  |

| de <sub>h</sub> | DATA3 Reset: 00 <sub>H</sub> | Bit Field | it Field CD |   | D  |   |   |   |   |   |  |  |

|                 | CAN Data Register 3          | Туре      | /pe rwh     |   |    |   |   |   |   |   |  |  |

## 3.2.4.14 OCDS Registers

The OCDS SFRs can be accessed in the mapped memory area (RMAP = 1).

### Table 18 OCDS Register Overview

| Addr            | Register Name                                                  | Bit       | 7              | 6         | 5           | 4          | 3           | 2         | 1          | 0         |  |  |

|-----------------|----------------------------------------------------------------|-----------|----------------|-----------|-------------|------------|-------------|-----------|------------|-----------|--|--|

| RMAP =          | = 1                                                            | 1         |                |           |             |            |             |           |            |           |  |  |

| E9 <sub>H</sub> | MMCR2 Reset: 1U <sub>H</sub><br>Monitor Mode Control 2         | Bit Field | STMO<br>DE     | EXBC      | DSUS<br>P   | MBCO<br>N  | ALTDI       | MMEP      | MMOD<br>E  | JENA      |  |  |

|                 | Register                                                       | Туре      | rw             | rw        | rw          | rwh        | rw          | rwh       | rh         | rh        |  |  |

| F1 <sub>H</sub> | MMCR Reset: 00 <sub>H</sub><br>Monitor Mode Control Register   | Bit Field | MEXIT<br>_P    | MEXIT     | 0           | MSTE<br>P  | MRAM<br>S_P | MRAM<br>S | TRF        | RRF       |  |  |

|                 |                                                                | Туре      | w              | rwh       | r           | rw         | w           | rwh       | rh         | rh        |  |  |

| F2 <sub>H</sub> | MMSR Reset: 00 <sub>H</sub><br>Monitor Mode Status Register    | Bit Field | MBCA<br>M      | MBCIN     | EXBF        | SWBF       | HWB3<br>F   | HWB2<br>F | HWB1<br>F  | HWB0<br>F |  |  |

|                 |                                                                | Туре      | rw             | rwh       | rwh         | rwh        | rwh         | rwh       | rwh        | rwh       |  |  |

| F3 <sub>H</sub> | MMBPCR Reset: 00 <sub>H</sub><br>Breakpoints Control Register  |           |                | B3C       | HWB2C       |            | HWB1<br>C   | HWB0C     |            |           |  |  |

|                 |                                                                | Туре      | rw             | rw        |             | rw         |             | rw        | rw         |           |  |  |

| F4 <sub>H</sub> | MMICR Reset: 00 <sub>H</sub><br>Monitor Mode Interrupt Control | Bit Field | DVEC<br>T      | DRET<br>R | COMR<br>ST  | MSTS<br>EL | MMUI<br>E_P | MMUI<br>E | RRIE_<br>P | RRIE      |  |  |

|                 | Register                                                       | Туре      | rwh            | rwh       | rwh         | rh         | w           | rw        | w          | rw        |  |  |

| F5 <sub>H</sub> | MMDR Reset: 00 <sub>H</sub>                                    | Bit Field | Bit Field MMRR |           |             |            |             |           |            |           |  |  |

|                 | Monitor Mode Data Transfer<br>Register<br>Receive              | Туре      |                |           |             | r          | h           |           |            |           |  |  |

| F6 <sub>H</sub> | HWBPSR Reset: 00 <sub>H</sub><br>Hardware Breakpoints Select   | Bit Field | 0              |           | BPSEL<br>_P | BPSEL      |             | SEL       |            |           |  |  |

|                 | Register                                                       | Туре      | r              |           | w           |            | r           | w         |            |           |  |  |

| F7 <sub>H</sub> | HWBPDR Reset: 00 <sub>H</sub>                                  | Bit Field | eld            |           | HWE         | BPxx       |             |           |            |           |  |  |

|                 | Hardware Breakpoints Data<br>Register                          | Туре      | rw             |           |             |            |             |           |            |           |  |  |

| EB <sub>H</sub> | MMWR1 Reset: 00 <sub>H</sub>                                   | Bit Field |                |           |             | MM         | NR1         |           |            |           |  |  |

|                 | Monitor Work Register 1                                        | Туре      |                |           |             | r          | W           |           |            |           |  |  |

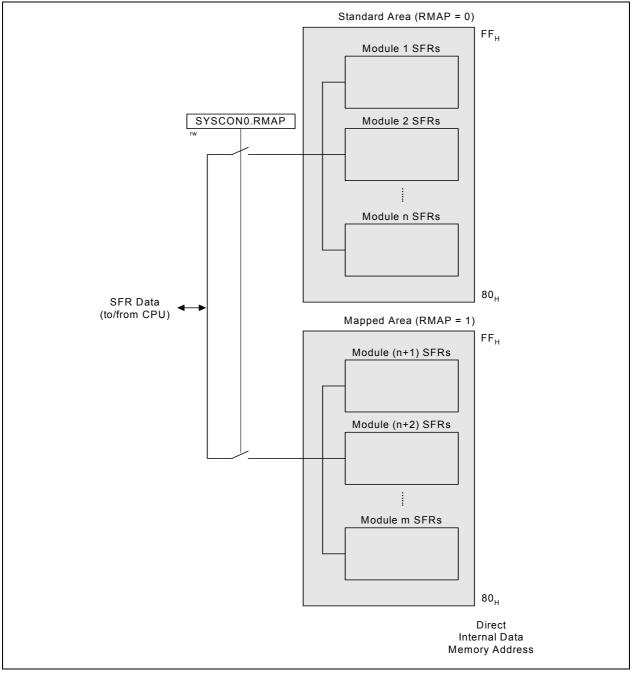

Figure 11 Flash Bank Sectorization

The internal structure of each Flash bank represents a sector architecture for flexible erase capability. The minimum erase width is always a complete sector, and sectors can be erased separately or in parallel. Contrary to standard EPROMs, erased Flash memory cells contain 0s.

The D-Flash bank is divided into more physical sectors for extended erasing and reprogramming capability; even numbers for each sector size are provided to allow greater flexibility and the ability to adapt to a wide range of application requirements.

# 3.3.2 Parallel Read Access of P-Flash

To enhance system performance, the P-Flash banks are configured for parallel read to allow two bytes of linear code to be read in 4 x CCLK cycles, compared to 6 x CCLK cycles if serial read is performed. This is achieved by reading two bytes in parallel from a P-Flash bank pair within the 3 x CCLK cycles access time and storing them in a cache. Subsequent read from the cache by the CPU does not require a wait state and can be completed within 1 x CCLK cycle. The result is the average instruction fetch time from the P-Flash banks is reduced and thus, the MIPS (Mega Instruction Per Second) of the system is increased.

However, if the parallel read feature is not desired due to certain timing constraints, it can be disabled by calling the parallel read disable subroutine.

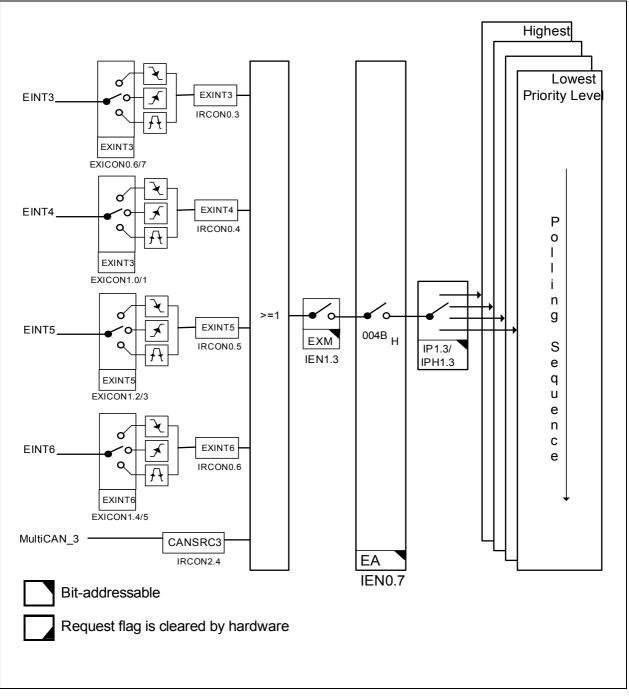

Figure 17 Interrupt Request Sources (Part 4)

## 3.4.3 Interrupt Priority

An interrupt that is currently being serviced can only be interrupted by a higher-priority interrupt, but not by another interrupt of the same or lower priority. Hence, an interrupt of the highest priority cannot be interrupted by any other interrupt request.

If two or more requests of different priority levels are received simultaneously, the request of the highest priority is serviced first. If requests of the same priority are received simultaneously, then an internal polling sequence determines which request is serviced first. Thus, within each priority level, there is a second priority structure determined by the polling sequence shown in **Table 21**.

| rrupt Level |  |  |  |  |  |

|-------------|--|--|--|--|--|

| Level       |  |  |  |  |  |

| (highest)   |  |  |  |  |  |

| 1           |  |  |  |  |  |

| 2           |  |  |  |  |  |

| 3           |  |  |  |  |  |

| 4           |  |  |  |  |  |

| 5           |  |  |  |  |  |

| 6           |  |  |  |  |  |

| 7           |  |  |  |  |  |

| 8           |  |  |  |  |  |

| 9           |  |  |  |  |  |

| 10          |  |  |  |  |  |

| 11          |  |  |  |  |  |

| 12          |  |  |  |  |  |

| 13          |  |  |  |  |  |

| 14          |  |  |  |  |  |

|             |  |  |  |  |  |

#### Table 21 Priority Structure within Interrupt Level

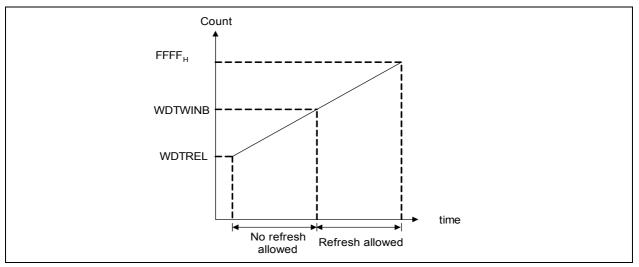

### Figure 29 WDT Timing Diagram

**Table 27** lists the possible watchdog time ranges that can be achieved using a certain module clock. Some numbers are rounded to 3 significant digits.

#### Table 27Watchdog Time Ranges

| Reload value                       | Prescaler for <i>f</i> <sub>PCLK</sub> |                 |  |  |  |  |  |  |  |

|------------------------------------|----------------------------------------|-----------------|--|--|--|--|--|--|--|

| In WDTREL                          | 2 (WDTIN = 0)                          | 128 (WDTIN = 1) |  |  |  |  |  |  |  |

|                                    | 24 MHz                                 | 24 MHz          |  |  |  |  |  |  |  |

| FF <sub>H</sub>                    | 21.3 μs                                | 1.37 ms         |  |  |  |  |  |  |  |

| FF <sub>H</sub><br>7F <sub>H</sub> | 2.75 ms                                | 176 ms          |  |  |  |  |  |  |  |

| 00 <sub>H</sub>                    | 5.46 ms                                | 350 ms          |  |  |  |  |  |  |  |

## XC886/888CLM

**Functional Description**

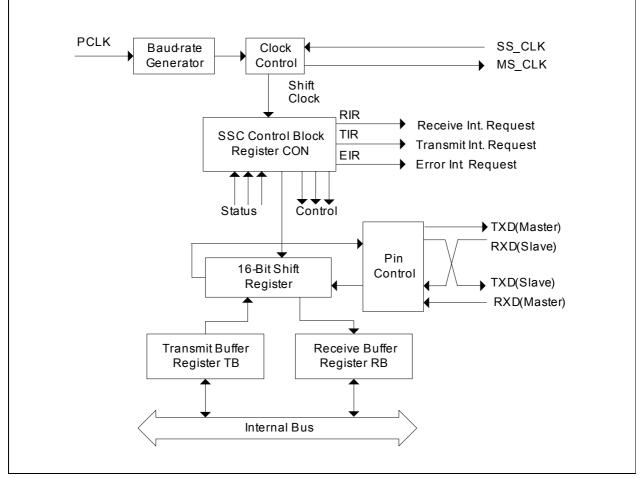

Figure 32 SSC Block Diagram

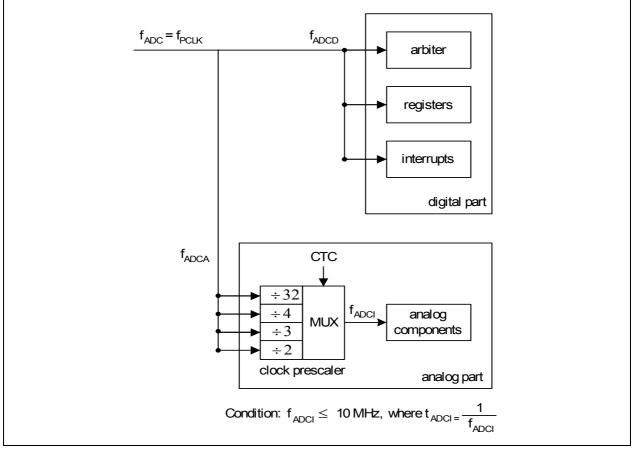

GLOBCTR. A prescaling ratio of 32 can be selected when the maximum performance of the ADC is not required.

### Figure 35 ADC Clocking Scheme

For module clock  $f_{ADC}$  = 24 MHz, the analog clock  $f_{ADCI}$  frequency can be selected as shown in **Table 34**.

| Table 34 | f <sub>ADCI</sub> Frequency Selection |

|----------|---------------------------------------|

|----------|---------------------------------------|

| Module Clock $f_{ADC}$ | СТС                       | Prescaling Ratio | Analog Clock $f_{ADCI}$ |  |  |

|------------------------|---------------------------|------------------|-------------------------|--|--|

| 24 MHz                 | 00 <sub>B</sub>           | ÷ 2              | 12 MHz (N.A)            |  |  |

|                        | 01 <sub>B</sub>           | ÷ 3              | 8 MHz                   |  |  |

|                        | 10 <sub>B</sub>           | ÷ 4              | 6 MHz                   |  |  |

|                        | 11 <sub>B</sub> (default) | ÷ 32             | 750 kHz                 |  |  |

As  $f_{\rm ADCI}$  cannot exceed 10 MHz, bit field CTC should not be set to  $00_{\rm B}$  when  $f_{\rm ADC}$  is 24 MHz. During slow-down mode where  $f_{\rm ADC}$  may be reduced to 12 MHz, 6 MHz etc., CTC can be set to  $00_{\rm B}$  as long as the divided analog clock  $f_{\rm ADCI}$  does not exceed 10 MHz.

## Table 36Chip Identification Number (cont'd)

| Product Variant   | Chip Identification Number |                       |                       |  |  |  |  |

|-------------------|----------------------------|-----------------------|-----------------------|--|--|--|--|

|                   | AA-Step                    | AB-Step               | AC-Step               |  |  |  |  |

| XC886-6FFA 3V3    | -                          | 095D1562 <sub>H</sub> | 0B5D1562 <sub>H</sub> |  |  |  |  |

| XC888-6FFA 3V3    | -                          | 095D1563 <sub>н</sub> | 0B5D1563 <sub>H</sub> |  |  |  |  |

| XC886CLM-8FFA 5V  | -                          | 09900102 <sub>H</sub> | 0B900102 <sub>H</sub> |  |  |  |  |

| XC888CLM-8FFA 5V  | -                          | 09900103 <sub>H</sub> | 0B900103 <sub>H</sub> |  |  |  |  |

| XC886LM-8FFA 5V   | -                          | 09900122 <sub>H</sub> | 0B900122 <sub>H</sub> |  |  |  |  |

| XC888LM-8FFA 5V   | -                          | 09900123 <sub>H</sub> | 0B900123 <sub>H</sub> |  |  |  |  |

| XC886CLM-6FFA 5V  | -                          | 09951502 <sub>H</sub> | 0B951502 <sub>H</sub> |  |  |  |  |

| XC888CLM-6FFA 5V  | -                          | 09951503 <sub>Н</sub> | 0B951503 <sub>H</sub> |  |  |  |  |

| XC886LM-6FFA 5V   | -                          | 09951522 <sub>Н</sub> | 0B951522 <sub>H</sub> |  |  |  |  |

| XC888LM-6FFA 5V   | -                          | 09951523 <sub>Н</sub> | 0B951523 <sub>H</sub> |  |  |  |  |

| XC886CM-8FFA 5V   | -                          | 09980102 <sub>H</sub> | 0B980102 <sub>H</sub> |  |  |  |  |

| XC888CM-8FFA 5V   | -                          | 09980103 <sub>H</sub> | 0B980103 <sub>H</sub> |  |  |  |  |

| XC886C-8FFA 5V    | -                          | 09980142 <sub>H</sub> | 0B980142 <sub>H</sub> |  |  |  |  |

| XC888C-8FFA 5V    | -                          | 09980143 <sub>H</sub> | 0B980143 <sub>H</sub> |  |  |  |  |

| XC886-8FFA 5V     | -                          | 09980162 <sub>H</sub> | 0B980162 <sub>H</sub> |  |  |  |  |

| XC888-8FFA 5V     | -                          | 09980163 <sub>H</sub> | 0B980163 <sub>H</sub> |  |  |  |  |

| XC886CM-6FFA 5V   | -                          | 099D1502 <sub>H</sub> | 0B9D1502 <sub>H</sub> |  |  |  |  |

| XC888CM-6FFA 5V   | -                          | 099D1503 <sub>H</sub> | 0B9D1503 <sub>H</sub> |  |  |  |  |

| XC886C-6FFA 5V    | -                          | 099D1542 <sub>H</sub> | 0B9D1542 <sub>H</sub> |  |  |  |  |

| XC888C-6FFA 5V    | -                          | 099D1543 <sub>H</sub> | 0B9D1543 <sub>H</sub> |  |  |  |  |

| XC886-6FFA 5V     | -                          | 099D1562 <sub>H</sub> | 0B9D1562 <sub>H</sub> |  |  |  |  |

| XC888-6FFA 5V     | -                          | 099D1563 <sub>H</sub> | 0B9D1563 <sub>H</sub> |  |  |  |  |

| ROM Devices       | ·                          |                       | ·                     |  |  |  |  |

| XC886CLM-8RFA 3V3 | 22400502 <sub>H</sub>      | -                     | -                     |  |  |  |  |

| XC888CLM-8RFA 3V3 | 22400503 <sub>H</sub>      | -                     | -                     |  |  |  |  |

| XC886LM-8RFA 3V3  | 22400522 <sub>H</sub>      | -                     | -                     |  |  |  |  |

| XC888LM-8RFA 3V3  | 22400523 <sub>H</sub>      | -                     | -                     |  |  |  |  |

| XC886CLM-6RFA 3V3 | 22411502 <sub>H</sub>      | -                     | -                     |  |  |  |  |

| XC888CLM-6RFA 3V3 | 22411503 <sub>H</sub>      | -                     | -                     |  |  |  |  |

#### **Electrical Parameters**

# 4 Electrical Parameters

**Chapter 4** provides the characteristics of the electrical parameters which are implementation-specific for the XC886/888.

## 4.1 General Parameters

The general parameters are described here to aid the users in interpreting the parameters mainly in **Section 4.2** and **Section 4.3**.

## 4.1.1 Parameter Interpretation

The parameters listed in this section represent partly the characteristics of the XC886/888 and partly its requirements on the system. To aid interpreting the parameters easily when evaluating them for a design, they are indicated by the abbreviations in the "Symbol" column:

• CC

These parameters indicate **C**ontroller **C**haracteristics, which are distinctive features of the XC886/888 and must be regarded for a system design.

• SR

These parameters indicate **S**ystem **R**equirements, which must be provided by the microcontroller system in which the XC886/888 is designed in.

### **Electrical Parameters**

| Parameter                                                      | Symbol            |    | Limit Values                |                             | Unit | Test Conditions           |

|----------------------------------------------------------------|-------------------|----|-----------------------------|-----------------------------|------|---------------------------|

|                                                                |                   |    | min.                        | max.                        |      |                           |

| Maximum current out of $V_{\rm SS}$                            | I <sub>MVSS</sub> | SR | -                           | 120                         | mA   | 3)                        |

| $V_{\text{DDP}}$ = 3.3 V Range                                 |                   |    |                             |                             |      |                           |

| Output low voltage                                             | $V_{OL}$          | CC | _                           | 1.0                         | V    | I <sub>OL</sub> = 8 mA    |

|                                                                |                   |    | _                           | 0.4                         | V    | I <sub>OL</sub> = 2.5 mA  |

| Output high voltage                                            | V <sub>OH</sub>   | CC | V <sub>DDP</sub> -<br>1.0   | -                           | V    | I <sub>OH</sub> = -8 mA   |

|                                                                |                   |    | V <sub>DDP</sub> - 0.4      | -                           | V    | I <sub>ОН</sub> = -2.5 mA |

| Input low voltage on<br>port pins<br>(all except P0.0 & P0.1)  | V <sub>ILP</sub>  | SR | _                           | $0.3 \times V_{\text{DDP}}$ | V    | CMOS Mode                 |

| Input low voltage on P0.0 & P0.1                               | V <sub>ILP0</sub> | SR | -0.2                        | $0.3 \times V_{ m DDP}$     | V    | CMOS Mode                 |

| Input low voltage on RESET pin                                 | $V_{ILR}$         | SR | -                           | $0.3 \times V_{\text{DDP}}$ | V    | CMOS Mode                 |

| Input low voltage on<br>TMS pin                                | V <sub>ILT</sub>  | SR | -                           | $0.3 \times V_{\text{DDP}}$ | V    | CMOS Mode                 |

| Input high voltage on<br>port pins<br>(all except P0.0 & P0.1) | V <sub>IHP</sub>  | SR | $0.7 \times V_{\text{DDP}}$ | -                           | V    | CMOS Mode                 |

| Input high voltage on P0.0 & P0.1                              | V <sub>IHP0</sub> | SR | $0.7 \times V_{\text{DDP}}$ | V <sub>DDP</sub>            | V    | CMOS Mode                 |

| Input high voltage on RESET pin                                | $V_{IHR}$         | SR | $0.7 \times V_{ m DDP}$     | -                           | V    | CMOS Mode                 |

| Input high voltage on<br>TMS pin                               | V <sub>IHT</sub>  | SR | $0.75 \times V_{ m DDP}$    | -                           | V    | CMOS Mode                 |

| Input Hysteresis                                               | HYS               | CC | $0.03 \times V_{ m DDP}$    | _                           | V    | CMOS Mode <sup>1)</sup>   |

| Input Hysteresis on XTAL1                                      | HYSX              | CC | $0.07 \times V_{ m DDC}$    | -                           | V    | 1)                        |

| Input low voltage at XTAL1                                     | V <sub>ILX</sub>  | SR | V <sub>SS</sub> -<br>0.5    | $0.3 \times V_{ m DDC}$     | V    |                           |

## XC886/888CLM

**Electrical Parameters**

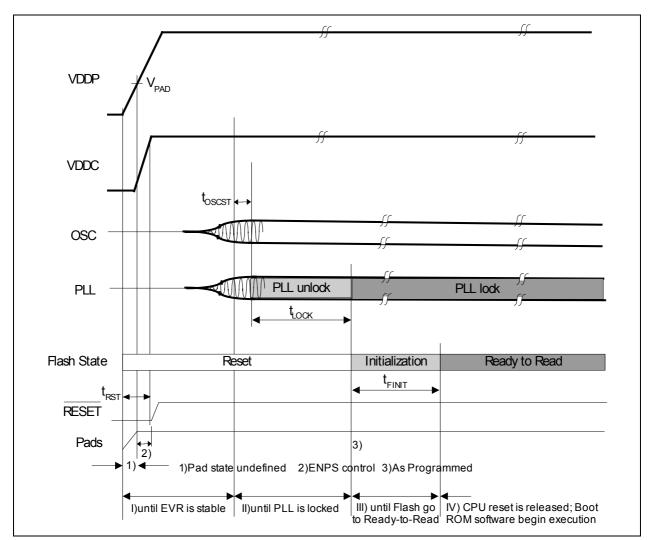

Figure 44 Power-on Reset Timing

#### **Electrical Parameters**

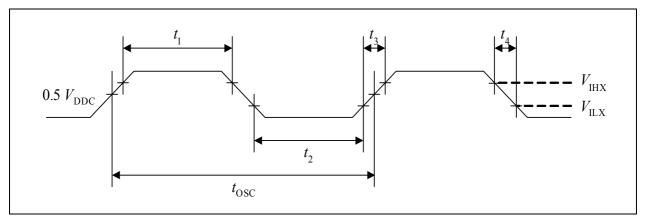

## 4.3.5 External Clock Drive XTAL1

**Table 48** shows the parameters that define the external clock supply for XC886/888. These timing parameters are based on the direct XTAL1 drive of clock input signals. They are not applicable if an external crystal or ceramic resonator is considered.

| Parameter         | Symbo                 | Symbol |      | it Values | Unit | Test Conditions |

|-------------------|-----------------------|--------|------|-----------|------|-----------------|

|                   |                       |        | Min. | Max.      |      |                 |

| Oscillator period | t <sub>osc</sub>      | SR     | 83.3 | 250       | ns   | 1)2)            |

| High time         | <i>t</i> <sub>1</sub> | SR     | 25   | -         | ns   | 2)3)            |

| Low time          | <i>t</i> <sub>2</sub> | SR     | 25   | -         | ns   | 2)3)            |

| Rise time         | t <sub>3</sub>        | SR     | -    | 20        | ns   | 2)3)            |

| Fall time         | $t_4$                 | SR     | -    | 20        | ns   | 2)3)            |

Table 48

External Clock Drive Characteristics (Operating Conditions apply)

1) The clock input signals with 45-55% duty cycle are used.

2) Not all parameters are 100% tested, but are verified by design/characterization and test correlation.

3) The clock input signal must reach the defined levels  $V_{\rm ILX}$  and  $V_{\rm IHX}$ .

Figure 45 External Clock Drive XTAL1

## Package and Quality Declaration

## 5.3 Quality Declaration

Table 2 shows the characteristics of the quality parameters in the XC886/888.

## Table 2Quality Parameters

| Parameter                                                             | Symbol           | Limit Values |      | Unit | Notes                                                |

|-----------------------------------------------------------------------|------------------|--------------|------|------|------------------------------------------------------|

|                                                                       |                  | Min.         | Max. |      |                                                      |

| ESD susceptibility<br>according to Human Body<br>Model (HBM)          | V <sub>HBM</sub> | -            | 2000 | V    | Conforming to<br>EIA/JESD22-<br>A114-B <sup>1)</sup> |

| ESD susceptibility<br>according to Charged<br>Device Model (CDM) pins | V <sub>CDM</sub> | -            | 500  | V    | Conforming to JESD22-C101-C <sup>1)</sup>            |

1) Not all parameters are 100% tested, but are verified by design/characterization and test correlation.