Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                          |

| Core Processor             | XC800                                                                             |

| Core Size                  | 8-Bit                                                                             |

| Speed                      | 24MHz                                                                             |

| Connectivity               | LINbus, SSI, UART/USART                                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                             |

| Number of I/O              | 34                                                                                |

| Program Memory Size        | 24KB (24K x 8)                                                                    |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 1.75K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                       |

| Data Converters            | A/D 8x10b                                                                         |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 48-LQFP                                                                           |

| Supplier Device Package    | PG-TQFP-48                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/saf-xc886lm-6ffa-5v-ac |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

XC886/888CLM

# 8-Bit Single Chip Microcontroller

# **1** Summary of Features

The XC886/888 has the following features:

- High-performance XC800 Core

- compatible with standard 8051 processor

- two clocks per machine cycle architecture (for memory access without wait state)

- two data pointers

- On-chip memory

- 12 Kbytes of Boot ROM

- 256 bytes of RAM

- 1.5 Kbytes of XRAM

- 24/32 Kbytes of Flash; or

24/32 Kbytes of ROM, with additional 4 Kbytes of Flash (includes memory protection strategy)

- I/O port supply at 3.3 V or 5.0 V and core logic supply at 2.5 V (generated by embedded voltage regulator)

(more features on next page)

|                     | <sup>-</sup> ROM <sup>1)</sup><br>2K x 8 | On-Chin Debug Support |                    | UART                           | SSC                        | Port 0 | 8-bit Digital I/O              |

|---------------------|------------------------------------------|-----------------------|--------------------|--------------------------------|----------------------------|--------|--------------------------------|

| Boot ROM<br>12K x 8 |                                          | XC800 Core            |                    | Capture/Compare Unit<br>16-bit |                            | Port 1 | 8-bit Digital I/O              |

| XRAM<br>1.5K x 8    |                                          |                       |                    |                                | are Unit<br>-bit           | Port 2 | 8-bit Digital/<br>Analog Input |

| RAM<br>256 x 8      | Timer 0<br>16-bit                        | Timer 1<br>16-bit     | Timer 2<br>16-bit  | Watchdog<br>Timer              | ADC<br>10-bit<br>8-channel | Port 3 | 8-bit Digital I/O              |

| MDU                 | CORDIC                                   | MultiCAN              | Timer 21<br>16-bit | UART1                          | Port 5                     | Port 4 | 8-bit Digital I/O              |

|                     |                                          |                       |                    |                                |                            |        | -                              |

| 1) All ROM          | devices com                              | e with an add         | litional 4K x 8    | Flash                          | B-bit Digital I/0          | C      |                                |

Figure 1 XC886/888 Functional Units

#### **General Device Information**

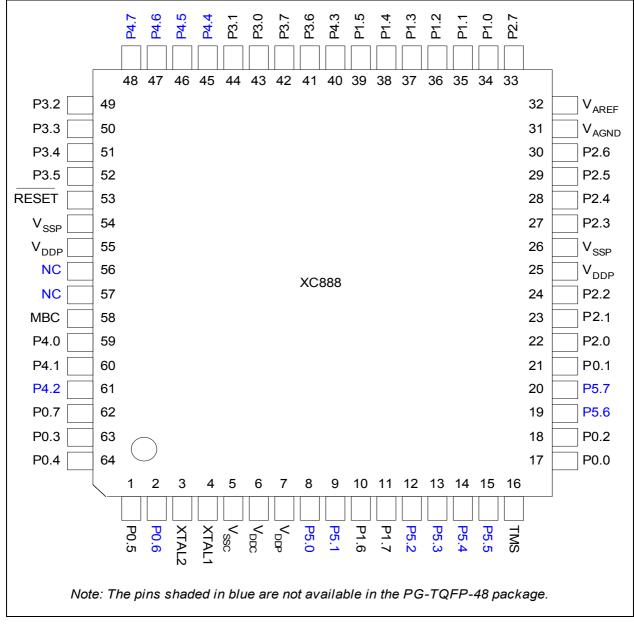

Figure 5 XC888 Pin Configuration, PG-TQFP-64 Package (top view)

# XC886/888CLM

#### **General Device Information**

| Symbol | Pin Number<br>(TQFP-48/64) | Туре | Reset<br>State | Function                                 |                                                                                                                                                           |

|--------|----------------------------|------|----------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Р3     |                            | I/O  |                | I/O port. It ca                          | B-bit bidirectional general purpose<br>an be used as alternate functions<br>ART1, Timer 21 and MultiCAN.                                                  |

| P3.0   | 35/43                      |      | Hi-Z           | CCPOS1_2<br>CC60_0<br>RXDO1_1            | CCU6 Hall Input 1<br>Input/Output of<br>Capture/Compare channel 0<br>UART1 Transmit Data Output                                                           |

| P3.1   | 36/44                      |      | Hi-Z           | CCPOS0_2<br>CC61_2<br>COUT60_0<br>TXD1_1 | CCU6 Hall Input 0<br>Input/Output of<br>Capture/Compare channel 1<br>Output of Capture/Compare<br>channel 0<br>UART1 Transmit Data<br>Output/Clock Output |

| P3.2   | 37/49                      |      | Hi-Z           | CCPOS2_2<br>RXDC1_1<br>RXD1_1<br>CC61_0  | CCU6 Hall Input 2<br>MultiCAN Node 1 Receiver Input<br>UART1 Receive Data Input<br>Input/Output of<br>Capture/Compare channel 1                           |

| P3.3   | 38/50                      |      | Hi-Z           | COUT61_0<br>TXDC1_1                      | Output of Capture/Compare<br>channel 1<br>MultiCAN Node 1 Transmitter<br>Output                                                                           |

| P3.4   | 39/51                      |      | Hi-Z           | CC62_0<br>RXDC0_1<br>T2EX1_0             | Input/Output of<br>Capture/Compare channel 2<br>MultiCAN Node 0 Receiver Input<br>Timer 21 External Trigger Input                                         |

| P3.5   | 40/52                      |      | Hi-Z           | COUT62_0<br>EXF21_0<br>TXDC0_1           | Output of Capture/Compare<br>channel 2<br>Timer 21 External Flag Output<br>MultiCAN Node 0 Transmitter<br>Output                                          |

| P3.6   | 33/41                      |      | PD             | CTRAP_0                                  | CCU6 Trap Input                                                                                                                                           |

# Table 3Pin Definitions and Functions (cont'd)

#### **General Device Information**

# Table 3Pin Definitions and Functions (cont'd)

| Symbol | Pin Number<br>(TQFP-48/64) | Reset<br>State | Function           |                                                                      |

|--------|----------------------------|----------------|--------------------|----------------------------------------------------------------------|

| P3.7   | 34/42                      | Hi-Z           | EXINT4<br>COUT63_0 | External Interrupt Input 4<br>Output of Capture/Compare<br>channel 3 |

The page register has the following definition:

#### MOD\_PAGE Page Register for module MOD

Reset Value: 00<sub>H</sub>

| 7 | 6 | 5  | 4  | 3 | 2 | 1    | 0 |

|---|---|----|----|---|---|------|---|

| 0 | Ρ | ST | NR | 0 |   | PAGE |   |

| v | V | V  | V  | r |   | rw   | I |

| Field | Bits  | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------|-------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PAGE  | [2:0] | rw   | <b>Page Bits</b><br>When written, the value indicates the new page.<br>When read, the value indicates the currently active<br>page.                                                                                                                                                                                                                                                                                                                                        |

| STNR  | [5:4] | W    | Storage NumberThis number indicates which storage bit field is the<br>target of the operation defined by bit field OP.If $OP = 10_B$ ,<br>the contents of PAGE are saved in STx before being<br>overwritten with the new value.If $OP = 11_B$ ,<br>the contents of PAGE are overwritten by the<br>contents of STx. The value written to the bit positions<br>of PAGE is ignored.00ST0 is selected.<br>0101ST1 is selected.<br>1010ST2 is selected.<br>1111ST3 is selected. |

# 3.2.3.1 Password Register

# PASSWD

| Pass       | word | Register |      |   |   |               | Reset | Value: 07 <sub>H</sub> |

|------------|------|----------|------|---|---|---------------|-------|------------------------|

|            | 7    | 6        | 5    | 4 | 3 | 2             | 1     | 0                      |

|            |      | 1        | PASS | 1 |   | PROTECT<br>_S | МС    | DE                     |

| . <u> </u> |      |          | wh   |   |   | rh            | r     | W                      |

| Field     | Bits  | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------|-------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MODE      | [1:0] | rw   | <ul> <li>Bit Protection Scheme Control Bits</li> <li>00 Scheme disabled - direct access to the protected bits is allowed.</li> <li>11 Scheme enabled - the bit field PASS has to be written with the passwords to open and close the access to protected bits. (default)</li> <li>Others:Scheme Enabled.</li> <li>These two bits cannot be written directly. To change the value between 11<sub>B</sub> and 00<sub>B</sub>, the bit field PASS must be written with 11000<sub>B</sub>; only then, will the MODE[1:0] be registered.</li> </ul> |

| PROTECT_S | 2     | rh   | <ul> <li>Bit Protection Signal Status Bit</li> <li>This bit shows the status of the protection.</li> <li>0 Software is able to write to all protected bits.</li> <li>1 Software is unable to write to any protected bits.</li> </ul>                                                                                                                                                                                                                                                                                                           |

| PASS      | [7:3] | wh   | Password BitsThe Bit Protection Scheme only recognizes threepatterns. $11000_B$ Enables writing of the bit field MODE. $10011_B$ Opens access to writing of all protected bits. $10101_B$ Closes access to writing of all protected bits                                                                                                                                                                                                                                                                                                       |

# XC886/888CLM

# **Functional Description**

# Table 10Port Register Overview (cont'd)

| Addr            | Register Name                                                       | Bit       | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|-----------------|---------------------------------------------------------------------|-----------|----|----|----|----|----|----|----|----|

| RMAP =          | = 0, PAGE 1                                                         |           |    |    |    |    |    |    | I  |    |

| 80 <sub>H</sub> | P0_PUDSEL Reset: FF <sub>H</sub>                                    | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P0 Pull-Up/Pull-Down Select Register                                | Туре      | rw |

| 86 <sub>H</sub> | P0_PUDEN Reset: C4 <sub>H</sub>                                     | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P0 Pull-Up/Pull-Down Enable Register                                | Туре      | rw |

| 90 <sub>H</sub> | P1_PUDSEL Reset: FF <sub>H</sub>                                    | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P1 Pull-Up/Pull-Down Select<br>Register                             | Туре      | rw |

| 91 <sub>H</sub> | P1_PUDEN Reset: FF <sub>H</sub>                                     | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P1 Pull-Up/Pull-Down Enable Register                                | Туре      | rw |

| 92 <sub>H</sub> | P5_PUDSEL Reset: FF <sub>H</sub>                                    | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P5 Pull-Up/Pull-Down Select<br>Register                             | Туре      | rw |

| 93 <sub>H</sub> | P5_PUDEN Reset: FF <sub>H</sub>                                     | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P5 Pull-Up/Pull-Down Enable Register                                | Туре      | rw |

| A0 <sub>H</sub> | P2_PUDSEL Reset: FF <sub>H</sub>                                    | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P2 Pull-Up/Pull-Down Select<br>Register                             | Туре      | rw |

| A1 <sub>H</sub> | P2_PUDEN Reset: 00 <sub>H</sub>                                     | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P2 Pull-Up/Pull-Down Enable<br>Register                             | Туре      | rw |

| во <sub>Н</sub> | P3_PUDSEL Reset: BF <sub>H</sub>                                    | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P3 Pull-Up/Pull-Down Select<br>Register                             | Туре      | rw |

| в1 <sub>Н</sub> | P3_PUDEN Reset: 40 <sub>H</sub>                                     | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P3 Pull-Up/Pull-Down Enable<br>Register                             | Туре      | rw |

| C8 <sub>H</sub> | P4_PUDSEL Reset: FF <sub>H</sub>                                    | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P4 Pull-Up/Pull-Down Select<br>Register                             | Туре      | rw |

| C9 <sub>H</sub> | P4_PUDEN Reset: 04 <sub>H</sub>                                     | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P4 Pull-Up/Pull-Down Enable<br>Register                             | Туре      | rw |

| RMAP =          | = 0, PAGE 2                                                         |           |    |    |    |    |    |    |    |    |

| <sup>80</sup> H | P0_ALTSEL0 Reset: 00 <sub>H</sub>                                   | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P0 Alternate Select 0 Register                                      | Туре      | rw |

| 86 <sub>H</sub> | P0_ALTSEL1 Reset: 00 <sub>H</sub><br>P0 Alternate Select 1 Register | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 |                                                                     | Туре      | rw |

| 90 <sub>H</sub> | P1_ALTSEL0 Reset: 00 <sub>H</sub><br>P1 Alternate Select 0 Register | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 |                                                                     | Туре      | rw |

| 91 <sub>H</sub> | P1_ALTSEL1 Reset: 00 <sub>H</sub><br>P1 Alternate Select 1 Register | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 |                                                                     | Туре      | rw |

| 92 <sub>H</sub> | P5_ALTSEL0 Reset: 00 <sub>H</sub><br>P5 Alternate Select 0 Register | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 |                                                                     | Туре      | rw |

# Table 11ADC Register Overview (cont'd)

| Addr            | Register Name                                                | Bit       | 7          | 6          | 5    | 4      | 3    | 2       | 1    | 0    |

|-----------------|--------------------------------------------------------------|-----------|------------|------------|------|--------|------|---------|------|------|

| CDH             | ADC_LCBR Reset: B7 <sub>H</sub>                              | Bit Field |            | BOU        | IND1 |        |      | BOL     | JND0 |      |

|                 | Limit Check Boundary Register                                | Туре      |            | r          | N    |        |      | r       | w    |      |

| CEH             | ADC_INPCR0 Reset: 00 <sub>H</sub>                            | Bit Field |            |            |      | S      | тс   |         |      |      |

|                 | Input Class 0 Register                                       | Туре      |            |            |      | r      | w    |         |      |      |

| CF <sub>H</sub> | ADC_ETRCR Reset: 00 <sub>H</sub><br>External Trigger Control | Bit Field | SYNE<br>N1 | SYNE<br>N0 |      | ETRSEL | 1    | ETRSEL0 |      |      |

|                 | Register                                                     | Туре      | rw         | rw         |      | rw     |      |         | rw   |      |

| RMAP =          | 0, PAGE 1                                                    |           |            |            | •    |        |      |         |      |      |

| CAH             | ADC_CHCTR0 Reset: 00 <sub>H</sub>                            | Bit Field | 0          |            | LCC  |        | (    | )       | RESE | RSEL |

|                 | Channel Control Register 0                                   | Туре      | r          |            | rw   |        |      | r       | n    | N    |

| св <sub>Н</sub> | ADC_CHCTR1 Reset: 00 <sub>H</sub>                            | Bit Field | 0          |            | LCC  |        | 0    |         | RESE | RSEL |

|                 | Channel Control Register 1                                   | Туре      | r          |            | rw   |        |      | r       | n    | N    |

| сс <sub>Н</sub> | ADC_CHCTR2 Reset: 00 <sub>H</sub>                            | Bit Field | 0          |            | LCC  |        | (    | )       | RESE | RSEL |

|                 | Channel Control Register 2                                   | Туре      | r          |            | rw   |        |      | r       | n    | N    |

| CDH             | ADC_CHCTR3 Reset: 00 <sub>H</sub>                            | Bit Field | 0          |            | LCC  |        | (    | C       | RESE | RSEL |

|                 | Channel Control Register 3                                   | Туре      | r          |            | rw   |        |      | r       | n    | N    |

| CEH             | ADC_CHCTR4 Reset: 00 <sub>H</sub>                            | Bit Field | 0          |            | LCC  |        | (    | )       | RESE | RSEL |

|                 | Channel Control Register 4                                   | Туре      | r          |            | rw   |        |      | r       | n    | N    |

| CFH             | ADC_CHCTR5 Reset: 00 <sub>H</sub>                            | Bit Field | 0          |            | LCC  |        | (    | )       | RESE | RSEL |

|                 | Channel Control Register 5                                   | Туре      | r          |            | rw   |        |      | r       | n    | N    |

| D2 <sub>H</sub> | ADC_CHCTR6 Reset: 00 <sub>H</sub>                            | Bit Field | 0          |            | LCC  |        | (    | C       | RESE | RSEL |

|                 | Channel Control Register 6                                   | Туре      | r          |            | rw   |        |      | r       | n    | N    |

| D3 <sub>H</sub> | ADC_CHCTR7 Reset: 00 <sub>H</sub>                            | Bit Field | 0          |            | LCC  |        | (    | )       | RESE | RSEL |

|                 | Channel Control Register 7                                   | Туре      | r          |            | rw   |        |      | r       | n    | N    |

| RMAP =          | 0, PAGE 2                                                    |           | •          |            |      |        |      |         |      |      |

| CA <sub>H</sub> | ADC_RESR0L Reset: 00 <sub>H</sub>                            | Bit Field | RES        | SULT       | 0    | VF     | DRC  |         | CHNR |      |

|                 | Result Register 0 Low                                        | Туре      | r          | h          | r    | rh     | rh   |         | rh   |      |

| св <sub>Н</sub> | ADC_RESR0H Reset: 00 <sub>H</sub>                            | Bit Field |            |            |      | RES    | SULT |         |      |      |

|                 | Result Register 0 High                                       | Туре      |            |            |      | I      | ħ    |         |      |      |

| сс <sub>Н</sub> | ADC_RESR1L Reset: 00 <sub>H</sub>                            | Bit Field | RES        | SULT       | 0    | VF     | DRC  |         | CHNR |      |

|                 | Result Register 1 Low                                        | Туре      | r          | 'n         | r    | rh     | rh   |         | rh   |      |

| CDH             | ADC_RESR1H Reset: 00 <sub>H</sub>                            | Bit Field |            |            |      | RES    | SULT |         |      |      |

|                 | Result Register 1 High                                       | Туре      |            |            |      | I      | 'n   |         |      |      |

| CEH             | ADC_RESR2L Reset: 00 <sub>H</sub>                            | Bit Field | RES        | SULT       | 0    | VF     | DRC  |         | CHNR |      |

|                 | Result Register 2 Low                                        | Туре      | r          | 'n         | r    | rh     | rh   |         | rh   |      |

| CF <sub>H</sub> | ADC_RESR2H Reset: 00 <sub>H</sub>                            | Bit Field |            |            |      | RES    | SULT |         |      |      |

|                 | Result Register 2 High                                       | Туре      |            |            |      |        | ħ    |         |      |      |

| D2 <sub>H</sub> | ADC_RESR3L Reset: 00 <sub>H</sub>                            | Bit Field | RES        | SULT       | 0    | VF     | DRC  |         | CHNR |      |

|                 | Result Register 3 Low                                        | Туре      | r          | 'n         | r    | rh     | rh   |         | rh   |      |

# Table 14CCU6 Register Overview (cont'd)

| Addr            | Register Name                                                         | Bit       | 7   | 6    | 5         | 4    | 3          | 2        | 1        | 0    |

|-----------------|-----------------------------------------------------------------------|-----------|-----|------|-----------|------|------------|----------|----------|------|

| FA <sub>H</sub> | CCU6_CC60SRL Reset: 00 <sub>H</sub>                                   | Bit Field |     |      | <u> </u>  | CC6  | OSL        | <u> </u> | <u> </u> |      |

|                 | Capture/Compare Shadow Register<br>for Channel CC60 Low               | Туре      |     |      |           | rv   | vh         |          |          |      |

| FB <sub>H</sub> | CCU6_CC60SRH Reset: 00 <sub>H</sub>                                   | Bit Field |     |      |           | CC6  | 0SH        |          |          |      |

|                 | Capture/Compare Shadow Register<br>for Channel CC60 High              | Туре      |     |      |           | rv   | vh         |          |          |      |

| FC <sub>H</sub> | CCU6_CC61SRL Reset: 00 <sub>H</sub>                                   | Bit Field |     |      |           | CC6  | 51SL       |          |          |      |

|                 | Capture/Compare Shadow Register<br>for Channel CC61 Low               | Туре      |     |      |           | rv   | vh         |          |          |      |

| FD <sub>H</sub> | CCU6_CC61SRH Reset: 00 <sub>H</sub>                                   | Bit Field |     |      |           | CC6  | 1SH        |          |          |      |

|                 | Capture/Compare Shadow Register<br>for Channel CC61 High              | Туре      |     |      |           | rv   | vh         |          |          |      |

| Fe <sub>H</sub> | CCU6_CC62SRL Reset: 00 <sub>H</sub>                                   | Bit Field |     |      |           | CC6  | 2SL        |          |          |      |

|                 | Capture/Compare Shadow Register<br>for Channel CC62 Low               | Туре      |     |      |           | rv   | vh         |          |          |      |

| FF <sub>H</sub> | CCU6_CC62SRH Reset: 00 <sub>H</sub>                                   | Bit Field |     |      |           | CC6  | 2SH        |          |          |      |

|                 | Capture/Compare Shadow Register<br>for Channel CC62 High              | Туре      |     |      |           | rv   | vh         |          |          |      |

| RMAP =          | 0, PAGE 1                                                             |           |     |      |           |      |            |          |          |      |

| 9A <sub>H</sub> | CCU6_CC63RL Reset: 00 <sub>H</sub>                                    | Bit Field |     |      |           | CC6  | 3VL        |          |          |      |

|                 | Capture/Compare Register for<br>Channel CC63 Low                      | Туре      |     |      |           | r    | h          |          |          |      |

| 98 <sub>H</sub> | CCU6_CC63RH Reset: 00 <sub>H</sub>                                    | Bit Field |     |      |           | CC6  | 3VH        |          |          |      |

|                 | Capture/Compare Register for<br>Channel CC63 High                     | Туре      |     |      |           | r    | h          |          |          |      |

| 9CH             | CCU6_T12PRL Reset: 00 <sub>H</sub>                                    | Bit Field |     |      |           | T12  | PVL        |          |          |      |

|                 | Timer T12 Period Register Low                                         | Туре      |     |      |           | rv   | vh         |          |          |      |

| 9D <sub>H</sub> | CCU6_T12PRH Reset: 00 <sub>H</sub><br>Timer T12 Period Register High  | Bit Field |     |      |           | T12  | PVH        |          |          |      |

|                 |                                                                       | Туре      |     |      |           | rv   | vh         |          |          |      |

| 9E <sub>H</sub> | CCU6_T13PRLReset: 00HTimer T13 Period Register Low                    | Bit Field |     |      |           | T13  | PVL        |          |          |      |

|                 |                                                                       | Туре      |     |      |           | rv   | vh         |          |          |      |

| 9F <sub>H</sub> | CCU6_T13PRH Reset: 00 <sub>H</sub><br>Timer T13 Period Register High  | Bit Field |     |      |           | T13  | PVH        |          |          |      |

|                 |                                                                       | Туре      |     |      |           | rv   | vh         |          |          |      |

| A4 <sub>H</sub> | CCU6_T12DTCL Reset: 00 <sub>H</sub><br>Dead-Time Control Register for | Bit Field |     |      |           | D    | ГM         |          |          |      |

|                 | Timer T12 Low                                                         | Туре      |     |      |           | r    | N          |          |          |      |

| А5 <sub>Н</sub> | CCU6_T12DTCH Reset: 00 <sub>H</sub><br>Dead-Time Control Register for | Bit Field | 0   | DTR2 | DTR1      | DTR0 | 0          | DTE2     | DTE1     | DTE0 |

|                 | Timer T12 High                                                        | Туре      | r   | rh   | rh        | rh   | r          | rw       | rw       | rw   |

| A6 <sub>H</sub> | CCU6_TCTR0L Reset: 00 <sub>H</sub><br>Timer Control Register 0 Low    | Bit Field | СТМ | CDIR | STE1<br>2 | T12R | T12<br>PRE |          | T12CLK   |      |

|                 |                                                                       | Туре      | rw  | rh   | rh        | rh   | rw         |          | rw       |      |

| А7 <sub>Н</sub> | CCU6_TCTR0H Reset: 00 <sub>H</sub><br>Timer Control Register 0 High   | Bit Field |     | 0    | STE1<br>3 | T13R | T13<br>PRE |          | T13CLK   |      |

|                 |                                                                       | Туре      |     | r    | rh        | rh   | rw         |          | rw       |      |

| FA <sub>H</sub> | CCU6_CC60RL Reset: 00 <sub>H</sub>                                    | Bit Field |     |      |           | CC6  | 60VL       |          |          |      |

|                 | Capture/Compare Register for<br>Channel CC60 Low                      | Туре      |     |      |           | r    | h          |          |          |      |

# 3.3 Flash Memory

The Flash memory provides an embedded user-programmable non-volatile memory, allowing fast and reliable storage of user code and data. It is operated from a single 2.5 V supply from the Embedded Voltage Regulator (EVR) and does not require additional programming or erasing voltage. The sectorization of the Flash memory allows each sector to be erased independently.

#### Features

- In-System Programming (ISP) via UART

- In-Application Programming (IAP)

- Error Correction Code (ECC) for dynamic correction of single-bit errors

- Background program and erase operations for CPU load minimization

- Support for aborting erase operation

- Minimum program width<sup>1)</sup> of 32-byte for D-Flash and 64-byte for P-Flash

- 1-sector minimum erase width

- 1-byte read access

- Flash is delivered in erased state (read all zeros)

- Operating supply voltage: 2.5 V ± 7.5 %

- Read access time:  $3 \times t_{CCLK} = 125 \text{ ns}^{2}$

- Program time: 248256 /  $f_{SYS}^{(3)}$  = 2.6 ms<sup>3)</sup>

- Erase time: 9807360 / f<sub>SYS</sub> = 102 ms<sup>3)</sup>

<sup>1)</sup> P-Flash: 64-byte wordline can only be programmed once, i.e., one gate disturb allowed. D-Flash: 32-byte wordline can be programmed twice, i.e., two gate disturbs allowed.

<sup>2)</sup> Values shown here are typical values.  $f_{sys}$  = 96 MHz ± 7.5% ( $f_{CCLK}$  = 24 MHz ± 7.5 %) is the maximum frequency range for Flash read access.

<sup>3)</sup> Values shown here are typical values.  $f_{sys} = 96 \text{ MHz} \pm 7.5\%$  is the only frequency range for Flash programming and erasing.  $f_{sysmin}$  is used for obtaining the worst case timing.

# **Functional Description**

| Interrupt<br>Source | Vector<br>Address | Assignment for<br>XC886/888                           | Enable Bit | SFR  |

|---------------------|-------------------|-------------------------------------------------------|------------|------|

| XINTR6              | 0033 <sub>H</sub> | MultiCAN Nodes 1 and 2                                | EADC       | IEN1 |

|                     |                   | ADC[1:0]                                              |            |      |

| XINTR7              | 003B <sub>H</sub> | SSC                                                   | ESSC       |      |

| XINTR8              | 0043 <sub>H</sub> | External Interrupt 2                                  | EX2        |      |

|                     |                   | T21                                                   |            |      |

|                     |                   | CORDIC                                                |            |      |

|                     |                   | UART1                                                 | ]          |      |

|                     |                   | UART1 Fractional Divider<br>(Normal Divider Overflow) |            |      |

|                     |                   | MDU[1:0]                                              | 1          |      |

| XINTR9              | 004B <sub>H</sub> | 004B <sub>H</sub> External Interrupt 3                |            |      |

|                     |                   | External Interrupt 4                                  | 1          |      |

|                     |                   | External Interrupt 5                                  |            |      |

|                     |                   | External Interrupt 6                                  |            |      |

|                     |                   | MultiCAN Node 3                                       |            |      |

| XINTR10             | 0053 <sub>H</sub> | CCU6 INP0                                             | ECCIP0     |      |

|                     |                   | MultiCAN Node 4                                       |            |      |

| XINTR11             | 005B <sub>H</sub> | CCU6 INP1                                             | ECCIP1     |      |

|                     |                   | MultiCAN Node 5                                       |            |      |

| XINTR12             | 0063 <sub>H</sub> | CCU6 INP2                                             | ECCIP2     |      |

|                     |                   | MultiCAN Node 6                                       |            |      |

| XINTR13             | 006B <sub>H</sub> | CCU6 INP3                                             | ECCIP3     |      |

|                     |                   | MultiCAN Node 7                                       |            |      |

# 3.5 Parallel Ports

The XC886 has 34 port pins organized into five parallel ports, Port 0 (P0) to Port 4 (P4), while the XC888 has 48 port pins organized into six parallel ports, Port 0 (P0) to Port 5 (P5). Each pin has a pair of internal pull-up and pull-down devices that can be individually enabled or disabled. Ports P0, P1, P3, P4 and P5 are bidirectional and can be used as general purpose input/output (GPIO) or to perform alternate input/output functions for the on-chip peripherals. When configured as an output, the open drain mode can be selected. Port P2 is an input-only port, providing general purpose input functions, alternate input functions for the on-chip peripherals. Converter (ADC).

#### **Bidirectional Port Features**

- Configurable pin direction

- Configurable pull-up/pull-down devices

- Configurable open drain mode

- Transfer of data through digital inputs and outputs (general purpose I/O)

- Alternate input/output for on-chip peripherals

#### Input Port Features

- Configurable input driver

- Configurable pull-up/pull-down devices

- Receive of data through digital input (general purpose input)

- Alternate input for on-chip peripherals

- Analog input for ADC module

Table 25 shows the VCO range for the XC886/888.

| Table 25 VC | O Range |

|-------------|---------|

|-------------|---------|

| <i>f</i> <sub>vcomin</sub> | f <sub>VCOmax</sub> | $f_{\sf VCOFREEmin}$ | <b><i>f</i></b> <sub>VCOFREEmax</sub> | Unit |

|----------------------------|---------------------|----------------------|---------------------------------------|------|

| 150                        | 200                 | 20                   | 80                                    | MHz  |

| 100                        | 150                 | 10                   | 80                                    | MHz  |

#### 3.8.1 Recommended External Oscillator Circuits

The oscillator circuit, a Pierce oscillator, is designed to work with both, an external crystal oscillator or an external stable clock source. It basically consists of an inverting amplifier and a feedback element with XTAL1 as input, and XTAL2 as output.

When using a crystal, a proper external oscillator circuitry must be connected to both pins, XTAL1 and XTAL2. The crystal frequency can be within the range of 4 MHz to 12 MHz. Additionally, it is necessary to have two load capacitances  $C_{X1}$  and  $C_{X2}$ , and depending on the crystal type, a series resistor  $R_{X2}$ , to limit the current. A test resistor  $R_Q$  may be temporarily inserted to measure the oscillation allowance (negative resistance) of the oscillator circuitry.  $R_Q$  values are typically specified by the crystal vendor. The  $C_{X1}$  and  $C_{X2}$  values shown in **Figure 25** can be used as starting points for the negative resistance evaluation and for non-productive systems. The exact values and related operating range are dependent on the crystal frequency and have to be determined and optimized together with the final target system is strongly recommended to verify the input amplitude at XTAL1 and to determine the actual oscillation allowance (margin negative resistance) for the oscillator-crystal system.

When using an external clock signal, the signal must be connected to XTAL1. XTAL2 is left open (unconnected).

The oscillator can also be used in combination with a ceramic resonator. The final circuitry must also be verified by the resonator vendor. **Figure 25** shows the recommended external oscillator circuitries for both operating modes, external crystal mode and external input clock mode.

For power saving purposes, the clocks may be disabled or slowed down according to **Table 26**.

# Table 26System frequency ( $f_{sys}$ = 96 MHz)

| Power Saving Mode | e Action                                                                                                                 |  |  |  |  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Idle              | Clock to the CPU is disabled.                                                                                            |  |  |  |  |

| Slow-down         | Clocks to the CPU and all the peripherals are divided by a common programmable factor defined by bit field CMCON.CLKREL. |  |  |  |  |

| Power-down        | Oscillator and PLL are switched off.                                                                                     |  |  |  |  |

# XC886/888CLM

#### **Functional Description**

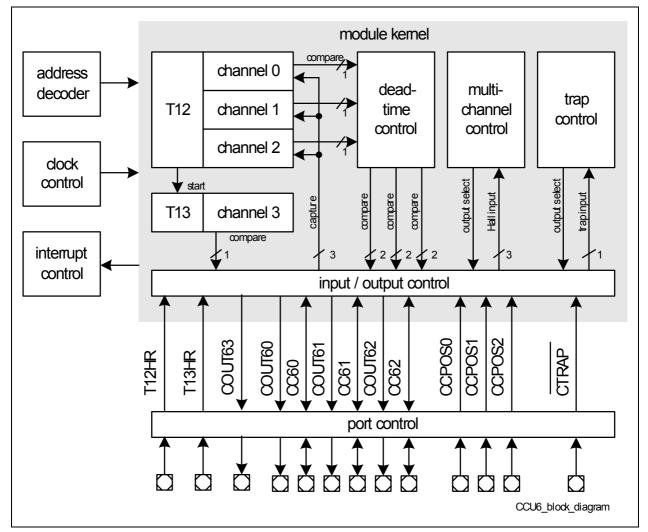

Figure 33 CCU6 Block Diagram

# 3.21 Analog-to-Digital Converter

The XC886/888 includes a high-performance 10-bit Analog-to-Digital Converter (ADC) with eight multiplexed analog input channels. The ADC uses a successive approximation technique to convert the analog voltage levels from up to eight different sources. The analog input channels of the ADC are available at Port 2.

#### Features

- Successive approximation

- 8-bit or 10-bit resolution (TUE of ± 1 LSB and ± 2 LSB, respectively)

- Eight analog channels

- Four independent result registers

- Result data protection for slow CPU access (wait-for-read mode)

- Single conversion mode

- Autoscan functionality

- Limit checking for conversion results

- Data reduction filter (accumulation of up to 2 conversion results)

- Two independent conversion request sources with programmable priority

- · Selectable conversion request trigger

- · Flexible interrupt generation with configurable service nodes

- Programmable sample time

- Programmable clock divider

- · Cancel/restart feature for running conversions

- Integrated sample and hold circuitry

- Compensation of offset errors

- Low power modes

# 3.21.1 ADC Clocking Scheme

A common module clock  $f_{ADC}$  generates the various clock signals used by the analog and digital parts of the ADC module:

- $f_{ADCA}$  is input clock for the analog part.

- $f_{ADCI}$  is internal clock for the analog part (defines the time base for conversion length and the sample time). This clock is generated internally in the analog part, based on the input clock  $f_{ADCA}$  to generate a correct duty cycle for the analog components.

- $f_{ADCD}$  is input clock for the digital part.

The internal clock for the analog part  $f_{ADCI}$  is limited to a maximum frequency of 10 MHz. Therefore, the ADC clock prescaler must be programmed to a value that ensures  $f_{ADCI}$  does not exceed 10 MHz. The prescaler ratio is selected by bit field CTC in register

#### **Electrical Parameters**

# Table 38 Input/Output Characteristics (Operating Conditions apply) (cont'd)

| Parameter                                                                      | Symbol                |    | Limit Values                |                         | Unit | Test Conditions                                        |  |

|--------------------------------------------------------------------------------|-----------------------|----|-----------------------------|-------------------------|------|--------------------------------------------------------|--|

|                                                                                |                       |    | min.                        | max.                    |      |                                                        |  |

| Input high voltage on RESET pin                                                | V <sub>IHR</sub>      | SR | $0.7 \times V_{\text{DDP}}$ | -                       | V    | CMOS Mode                                              |  |

| Input high voltage on TMS pin                                                  | V <sub>IHT</sub>      | SR | $0.75 \times V_{ m DDP}$    | -                       | V    | CMOS Mode                                              |  |

| Input Hysteresis on port<br>pins                                               | HYSP                  | CC | $0.07 \times V_{ m DDP}$    | -                       | V    | CMOS Mode <sup>1)</sup>                                |  |

| Input Hysteresis on<br>XTAL1                                                   | HYSX                  | CC | $0.07 \times V_{ m DDC}$    | -                       | V    | 1)                                                     |  |

| Input low voltage at<br>XTAL1                                                  | $V_{ILX}$             | SR | V <sub>SS</sub> -<br>0.5    | $0.3 \times V_{ m DDC}$ | V    |                                                        |  |

| Input high voltage at XTAL1                                                    | V <sub>IHX</sub>      | SR | $0.7 \times V_{ m DDC}$     | V <sub>DDC</sub> + 0.5  | V    |                                                        |  |

| Pull-up current                                                                | $I_{\rm PU}$          | SR | -                           | -10                     | μA   | V <sub>IHP,min</sub>                                   |  |

|                                                                                |                       |    | -150                        | _                       | μA   | $V_{\rm ILP,max}$                                      |  |

| Pull-down current                                                              | $I_{\rm PD}$          | SR | -                           | 10                      | μA   | $V_{ILP,max}$                                          |  |

|                                                                                |                       |    | 150                         | -                       | μA   | V <sub>IHP,min</sub>                                   |  |

| Input leakage current                                                          | I <sub>OZ1</sub>      | CC | -1                          | 1                       | μA   | $0 < V_{IN} < V_{DDP},$<br>$T_A \le 125^{\circ}C^{2)}$ |  |

| Input current at XTAL1                                                         | $I_{ILX}$             | CC | -10                         | 10                      | μA   |                                                        |  |

| Overload current on any pin                                                    | I <sub>OV</sub>       | SR | -5                          | 5                       | mA   |                                                        |  |

| Absolute sum of overload currents                                              | $\Sigma  I_{\rm OV} $ | SR | -                           | 25                      | mA   | 3)                                                     |  |

| Voltage on any pin during $V_{\text{DDP}}$ power off                           | V <sub>PO</sub>       | SR | -                           | 0.3                     | V    | 4)                                                     |  |

| Maximum current per pin (excluding $V_{\text{DDP}}$ and $V_{\text{SS}}$ )      | $I_{\rm M}{ m SR}$    | SR | -                           | 15                      | mA   |                                                        |  |

| Maximum current for all pins (excluding $V_{\text{DDP}}$ and $V_{\text{SS}}$ ) | $\Sigma  I_{M} $      | SR | -                           | 90                      | mA   |                                                        |  |

| Maximum current into $V_{\text{DDP}}$                                          | I <sub>mvddp</sub>    | SR | -                           | 120                     | mA   | 3)                                                     |  |

#### **Electrical Parameters**

# 4.2.3.1 ADC Conversion Timing

Conversion time,  $t_{\rm C} = t_{\rm ADC} \times (1 + r \times (3 + n + STC))$ , where r = CTC + 2 for CTC =  $00_{\rm B}$ ,  $01_{\rm B}$  or  $10_{\rm B}$ , r = 32 for CTC =  $11_{\rm B}$ , CTC = Conversion Time Control (GLOBCTR.CTC), STC = Sample Time Control (INPCR0.STC), n = 8 or 10 (for 8-bit and 10-bit conversion respectively),  $t_{\rm ADC} = 1 / f_{\rm ADC}$

#### **Electrical Parameters**

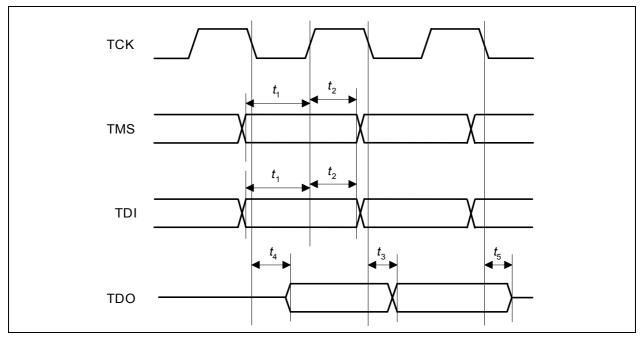

| Table 50JTAG Timing (Operating Conditions apply; CL = 50 pF) (cont'd) |                       |      |        |     |      |                           |

|-----------------------------------------------------------------------|-----------------------|------|--------|-----|------|---------------------------|

| Parameter                                                             | Symbol                |      | Limits |     | Unit | Test                      |

|                                                                       |                       |      | min    | max |      | Conditions                |

| TDO high impedance to valid                                           | <i>t</i> <sub>4</sub> | CC   | -      | 27  | ns   | 5V Device <sup>1)</sup>   |

| output from TCK                                                       |                       |      | -      | 36  | ns   | 3.3V Device <sup>1)</sup> |

| TDO valid output to high<br>impedance from TCK                        | $t_5$                 | 5 CC | -      | 22  | ns   | 5V Device <sup>1)</sup>   |

|                                                                       |                       |      | -      | 28  | ns   | 3.3V Device <sup>1)</sup> |

1) Not all parameters are 100% tested, but are verified by design/characterization and test correlation.

#### Package and Quality Declaration

# 5.2 Package Outline

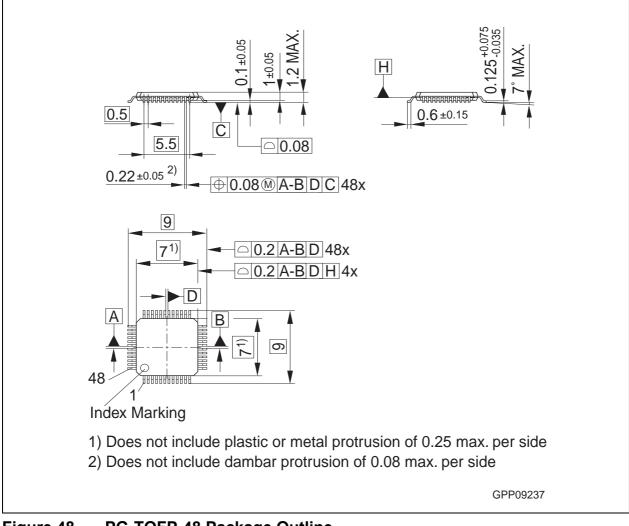

Figure 48 shows the package outlines of the XC886.

Figure 48 PG-TQFP-48 Package Outline