Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | XC800                                                                            |

| Core Size                  | 8-Bit                                                                            |

| Speed                      | 24MHz                                                                            |

| Connectivity               | CANbus, SSI, UART/USART                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 48                                                                               |

| Program Memory Size        | 24KB (24K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 1.75K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                      |

| Data Converters            | A/D 8x10b                                                                        |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-LQFP                                                                          |

| Supplier Device Package    | PG-TQFP-64                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/saf-xc888c-6ffa-5v-ac |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **General Device Information**

# 2 General Device Information

**Chapter 2** contains the block diagram, pin configurations, definitions and functions of the XC886/888.

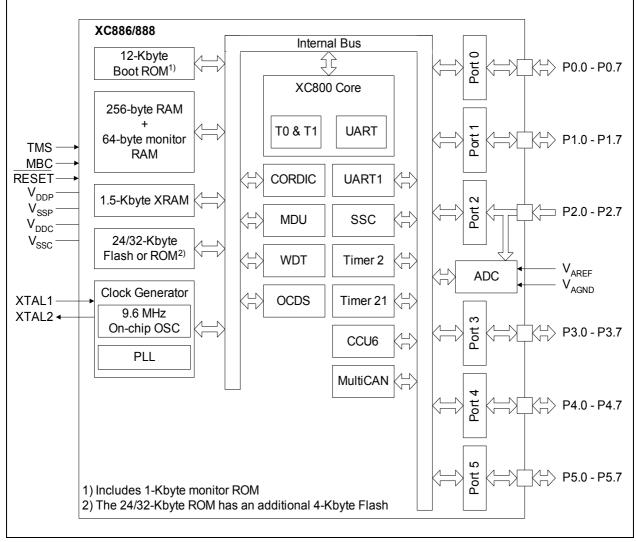

## 2.1 Block Diagram

The block diagram of the XC886/888 is shown in Figure 2.

Figure 2 XC886/888 Block Diagram

## XC886/888CLM

## **General Device Information**

## Table 3Pin Definitions and Functions (cont'd)

| Symbol | Pin Number<br>(TQFP-48/64) | Туре | Reset<br>State | Function                     |                                                                           |

|--------|----------------------------|------|----------------|------------------------------|---------------------------------------------------------------------------|

| P1.6   | 8/10                       |      | PU             | CCPOS1_1<br>T12HR_0          | •                                                                         |

|        |                            |      |                | EXINT6_0<br>RXDC0_2<br>T21_1 | • •                                                                       |

| P1.7   | 9/11                       |      | PU             | CCPOS2_1<br>T13HR_0<br>T2 1  | CCU6 Hall Input 2<br>CCU6 Timer 13 Hardware Run<br>Input<br>Timer 2 Input |

|        |                            |      |                | TXDC0_2                      | •                                                                         |

|        |                            |      |                |                              | .6 can be used as a software chip<br>t for the SSC.                       |

## Table 9WDT Register Overview (cont'd)

| Addr            | Register Name                | Bit       | 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-----------------|------------------------------|-----------|-----|---|---|---|---|---|---|---|

| ве <sub>Н</sub> | WDTL Reset: 00 <sub>H</sub>  | Bit Field | WDT |   |   |   |   |   |   |   |

|                 | Watchdog Timer Register Low  | Туре      | rh  |   |   |   |   |   |   |   |

| bf <sub>h</sub> | WDTH Reset: 00 <sub>H</sub>  | Bit Field | WDT |   |   |   |   |   |   |   |

|                 | Watchdog Timer Register High | Туре      | rh  |   |   |   |   |   |   |   |

## 3.2.4.6 Port Registers

The Port SFRs can be accessed in the standard memory area (RMAP = 0).

## Table 10Port Register Overview

| Addr            | Register Name                    | Bit       | 7  | 6  | 5  | 4  | 3  | 2  | 1    | 0        |

|-----------------|----------------------------------|-----------|----|----|----|----|----|----|------|----------|

| RMAP =          | = 0                              | 1         |    |    |    |    |    |    |      | <u>.</u> |

| B2 <sub>H</sub> | PORT_PAGE Reset: 00 <sub>H</sub> | Bit Field | C  | P  | ST | NR | 0  |    | PAGE |          |

|                 | Page Register                    | Туре      | ١  | N  | ١  | N  | r  |    | rw   |          |

| RMAP =          | = 0, PAGE 0                      |           |    |    | •  |    | •  |    |      |          |

| 80 <sub>H</sub> | P0_DATA Reset: 00 <sub>H</sub>   | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1   | P0       |

|                 | P0 Data Register                 | Туре      | rw   | rw       |

| 86 <sub>H</sub> | P0_DIR Reset: 00 <sub>H</sub>    | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1   | P0       |

|                 | P0 Direction Register            | Туре      | rw   | rw       |

| 90 <sub>H</sub> | P1_DATA Reset: 00 <sub>H</sub>   | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1   | P0       |

|                 | P1 Data Register                 | Туре      | rw   | rw       |

| 91 <sub>H</sub> | P1_DIR Reset: 00 <sub>H</sub>    | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1   | P0       |

|                 | P1 Direction Register            | Туре      | rw   | rw       |

| 92 <sub>H</sub> | P5_DATA Reset: 00 <sub>H</sub>   | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1   | P0       |

|                 | P5 Data Register                 | Туре      | rw   | rw       |

| 93 <sub>H</sub> | P5_DIR Reset: 00 <sub>H</sub>    | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1   | P0       |

|                 | P5 Direction Register            | Туре      | rw   | rw       |

| A0 <sub>H</sub> | P2_DATA Reset: 00 <sub>H</sub>   | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1   | P0       |

|                 | P2 Data Register                 | Туре      | rw   | rw       |

| A1 <sub>H</sub> | P2_DIR Reset: 00 <sub>H</sub>    | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1   | P0       |

|                 | P2 Direction Register            | Туре      | rw   | rw       |

| во <sub>Н</sub> | P3_DATA Reset: 00 <sub>H</sub>   | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1   | P0       |

|                 | P3 Data Register                 | Туре      | rw   | rw       |

| в1 <sub>Н</sub> | P3_DIR Reset: 00 <sub>H</sub>    | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1   | P0       |

|                 | P3 Direction Register            | Туре      | rw   | rw       |

| C8 <sub>H</sub> | P4_DATA Reset: 00 <sub>H</sub>   | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1   | P0       |

|                 | P4 Data Register                 | Туре      | rw   | rw       |

| C9 <sub>H</sub> | P4_DIR Reset: 00 <sub>H</sub>    | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1   | P0       |

|                 | P4 Direction Register            | Туре      | rw   | rw       |

## Table 11ADC Register Overview (cont'd)

| Addr            | Register Name                                                          | Bit       | 7          | 6          | 5          | 4          | 3          | 2          | 1          | 0          |  |

|-----------------|------------------------------------------------------------------------|-----------|------------|------------|------------|------------|------------|------------|------------|------------|--|

| cc <sup>H</sup> | ADC_CHINSR Reset: 00 <sub>H</sub><br>Channel Interrupt Set Register    | Bit Field | CHINS<br>7 | CHINS<br>6 | CHINS<br>5 | CHINS<br>4 | CHINS<br>3 | CHINS<br>2 | CHINS<br>1 | CHINS<br>0 |  |

|                 |                                                                        | Туре      | w          | w          | w          | w          | w          | W          | w          | w          |  |

| CDH             | ADC_CHINPR Reset: 00 <sub>H</sub><br>Channel Interrupt Node Pointer    | Bit Field | CHINP<br>7 | CHINP<br>6 | CHINP<br>5 | CHINP<br>4 | CHINP<br>3 | CHINP<br>2 | CHINP<br>1 | CHINP<br>0 |  |

|                 | Register                                                               | Туре      | rw         |  |

| Ceh             | ADC_EVINFR Reset: 00 <sub>H</sub><br>Event Interrupt Flag Register     | Bit Field | EVINF<br>7 | EVINF<br>6 | EVINF<br>5 | EVINF<br>4 | (          | )          | EVINF<br>1 | EVINF<br>0 |  |

|                 |                                                                        | Туре      | rh         | rh         | rh         | rh         |            | r          | rh         | rh         |  |

| CF <sub>H</sub> | ADC_EVINCR Reset: 00 <sub>H</sub><br>Event Interrupt Clear Flag        | Bit Field | EVINC<br>7 | EVINC<br>6 | EVINC<br>5 | EVINC<br>4 | (          | )          | EVINC<br>1 | EVINC<br>0 |  |

|                 | Register                                                               | Туре      | w          | w          | w          | w          |            | r          | w          | w          |  |

| D2 <sub>H</sub> | ADC_EVINSR Reset: 00 <sub>H</sub><br>Event Interrupt Set Flag Register | Bit Field | EVINS<br>7 | EVINS<br>6 | EVINS<br>5 | EVINS<br>4 | (          | )          | EVINS<br>1 | EVINS<br>0 |  |

|                 |                                                                        | Туре      | w          | w          | w          | w          |            | r          | w          | w          |  |

| D3 <sub>H</sub> | ADC_EVINPR Reset: 00 <sub>H</sub><br>Event Interrupt Node Pointer      | Bit Field | EVINP<br>7 | EVINP<br>6 | EVINP<br>5 | EVINP<br>4 | (          | )          | EVINP<br>0 |            |  |

|                 | Register                                                               | Туре      | rw         | rw         | rw         | rw         |            | r rw r     |            |            |  |

| RMAP =          | = 0, PAGE 6                                                            |           |            |            |            |            |            |            |            |            |  |

| CA <sub>H</sub> | ADC_CRCR1 Reset: 00 <sub>H</sub>                                       | Bit Field | CH7        | CH6        | CH5        | CH4        |            | (          | )          |            |  |

|                 | Conversion Request Control<br>Register 1                               | Туре      | rwh        | rwh        | rwh        | rwh        |            | I          | r          |            |  |

| св <sub>Н</sub> | ADC_CRPR1 Reset: 00 <sub>H</sub>                                       | Bit Field | CHP7       | CHP6       | CHP5       | CHP4       |            | (          | )          |            |  |

|                 | Conversion Request Pending<br>Register 1                               | Туре      | rwh        | rwh        | rwh        | rwh        |            | I          | r          |            |  |

| сс <sup>н</sup> | ADC_CRMR1 Reset: 00 <sub>H</sub><br>Conversion Request Mode            | Bit Field | Rsv        | LDEV       | CLRP<br>ND | SCAN       | ENSI       | ENTR       | 0          | ENGT       |  |

|                 | Register 1                                                             | Туре      | r          | w          | w          | rw         | rw         | rw         | r          | rw         |  |

| CD <sub>H</sub> | ADC_QMR0 Reset: 00 <sub>H</sub><br>Queue Mode Register 0               | Bit Field | CEV        | TREV       | FLUS<br>H  | CLRV       | 0          | ENTR       | 0          | ENGT       |  |

|                 |                                                                        | Туре      | w          | w          | w          | w          | r          | rw         | r          | rw         |  |

| Ceh             | ADC_QSR0 Reset: 20 <sub>H</sub><br>Queue Status Register 0             | Bit Field | Rsv        | 0          | EMPT<br>Y  | EV         | (          | )          | FI         | LL         |  |

|                 |                                                                        | Туре      | r          | r          | rh         | rh         |            | r rh       |            |            |  |

| CF <sub>H</sub> | ADC_Q0R0 Reset: 00 <sub>H</sub>                                        | Bit Field | EXTR       | ENSI       | RF         | V          | 0          | REQCHNR    |            |            |  |

|                 | Queue 0 Register 0                                                     | Туре      | rh         | rh         | rh         | rh         | r          | rh         |            |            |  |

| D2 <sub>H</sub> | ADC_QBUR0 Reset: 00 <sub>H</sub>                                       | Bit Field | EXTR       | ENSI       | RF         | V          | 0          | REQCHNR    |            |            |  |

|                 | Queue Backup Register 0                                                | Туре      | rh         | rh         | rh         | rh         | r          | rh         |            |            |  |

| D2 <sub>H</sub> | ADC_QINR0 Reset: 00 <sub>H</sub>                                       | Bit Field | EXTR       | ENSI       | RF         | (          | )          | REQCHNR    |            |            |  |

|                 | Queue Input Register 0                                                 | Туре      | w          | w          | w          |            | r          |            | w          |            |  |

#### Table 13T21 Register Overview (cont'd)

| Addr            | Register Name         | Bit       | 7   | 6 | 5 | 4  | 3   | 2 | 1 | 0 |

|-----------------|-----------------------|-----------|-----|---|---|----|-----|---|---|---|

| C5 <sub>H</sub> | - 1                   | Bit Field |     |   |   | TH | IL2 |   |   |   |

|                 | Timer 2 Register High | Туре      | rwh |   |   |    |     |   |   |   |

## 3.2.4.10 CCU6 Registers

The CCU6 SFRs can be accessed in the standard memory area (RMAP = 0).

#### Table 14 CCU6 Register Overview

| Addr            | Register Name                                                                | Bit       | 7          | 6          | 5          | 4          | 3                              | 2                | 1          | 0          |

|-----------------|------------------------------------------------------------------------------|-----------|------------|------------|------------|------------|--------------------------------|------------------|------------|------------|

| RMAP =          | = 0                                                                          |           |            |            |            |            |                                |                  |            |            |

| A3 <sub>H</sub> | CCU6_PAGE Reset: 00 <sub>H</sub>                                             | Bit Field | C          | P          | ST         | NR         | 0                              |                  | PAGE       |            |

|                 | Page Register                                                                | Туре      | ١          | N          | ۱          | N          | r                              |                  | rw         |            |

| RMAP =          | = 0, PAGE 0                                                                  |           |            |            |            |            |                                |                  |            |            |

| 9A <sub>H</sub> | CCU6_CC63SRL Reset: 00 <sub>H</sub><br>Capture/Compare Shadow Register       | Bit Field |            |            |            | CC6        | 63SL                           |                  |            |            |

|                 | for Channel CC63 Low                                                         | Туре      |            | ſW         |            |            |                                |                  |            |            |

| 9B <sub>H</sub> | CCU6_CC63SRH Reset: 00 <sub>H</sub>                                          | Bit Field |            |            |            | CC63SH     |                                |                  |            |            |

|                 | Capture/Compare Shadow Register<br>for Channel CC63 High                     | Туре      |            |            | rw         |            |                                |                  |            |            |

| 9CH             | CCU6_TCTR4L Reset: 00 <sub>H</sub><br>Timer Control Register 4 Low           | Bit Field | T12<br>STD | T12<br>STR | (          | 0          | DT T12 T12R T12<br>RES RES S R |                  |            |            |

|                 |                                                                              | Туре      | w          | w          |            | r w w w    |                                |                  |            | w          |

| 9D <sub>H</sub> | CCU6_TCTR4H Reset: 00 <sub>H</sub><br>Timer Control Register 4 High          | Bit Field | T13<br>STD | T13<br>STR |            |            |                                |                  |            | T13R<br>R  |

|                 |                                                                              | Туре      | w          | w          |            | r          |                                | w w w            |            |            |

| 9E <sub>H</sub> | CCU6_MCMOUTSL Reset: 00 <sub>H</sub><br>Multi-Channel Mode Output Shadow     | Bit Field | STRM<br>CM | 0          |            |            | MC                             | MPS              |            |            |

|                 | Register Low                                                                 | Туре      | w          | r          |            |            | r                              | w                |            |            |

| 9F <sub>H</sub> | CCU6_MCMOUTSH Reset: 00 <sub>H</sub><br>Multi-Channel Mode Output Shadow     | Bit Field | STRH<br>P  | 0          |            | CURHS      |                                |                  | EXPHS      |            |

|                 | Register High                                                                | Туре      | w          | r          |            | rw         |                                |                  | rw         |            |

| A4 <sub>H</sub> | CCU6_ISRL Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Status         | Bit Field | RT12<br>PM | RT12<br>OM | RCC6<br>2F | RCC6<br>2R | RCC6<br>1F                     | RCC6<br>1R       | RCC6<br>0F | RCC6<br>0R |

|                 | Reset Register Low                                                           | Туре      | w          | w          | w          | w          | w                              | w                | w          | w          |

| A5 <sub>H</sub> | CCU6_ISRH Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Status         | Bit Field | RSTR       | RIDLE      | RWH<br>E   | RCHE       | 0                              | RTRP<br>F        | RT13<br>PM | RT13<br>CM |

|                 | Reset Register High                                                          | Туре      | w          | w          | w          | w          | r                              | w                | w          | w          |

| A6 <sub>H</sub> | CCU6_CMPMODIFL Reset: 00 <sub>H</sub><br>Compare State Modification Register | Bit Field | 0          | MCC6<br>3S |            |            |                                |                  |            | MCC6<br>0S |

|                 | Low                                                                          | Туре      | r          | w          |            | r          |                                | w                | w          | w          |

| а7 <sub>Н</sub> | CCU6_CMPMODIFH Reset: 00 <sub>H</sub><br>Compare State Modification Register | Bit Field | 0          | MCC6<br>3R |            | 0          |                                | MCC6<br>2R 1R 0F |            |            |

|                 | High                                                                         | Туре      | r          | w          |            | r          |                                | w                | w          | w          |

# Table 14CCU6 Register Overview (cont'd)

| Addr            | Register Name                                                         | Bit       | 7   | 6    | 5         | 4    | 3          | 2        | 1        | 0    |

|-----------------|-----------------------------------------------------------------------|-----------|-----|------|-----------|------|------------|----------|----------|------|

| FA <sub>H</sub> | CCU6_CC60SRL Reset: 00 <sub>H</sub>                                   | Bit Field |     |      | <u> </u>  | CC6  | OSL        | <u> </u> | <u> </u> |      |

|                 | Capture/Compare Shadow Register<br>for Channel CC60 Low               | Туре      |     |      |           | rv   | vh         |          |          |      |

| FB <sub>H</sub> | CCU6_CC60SRH Reset: 00 <sub>H</sub>                                   | Bit Field |     |      |           | CC6  | 0SH        |          |          |      |

|                 | Capture/Compare Shadow Register<br>for Channel CC60 High              | Туре      |     |      |           | rv   | vh         |          |          |      |

| FC <sub>H</sub> | CCU6_CC61SRL Reset: 00 <sub>H</sub>                                   | Bit Field |     |      |           | CC6  | 51SL       |          |          |      |

|                 | Capture/Compare Shadow Register<br>for Channel CC61 Low               | Туре      |     |      |           | rv   | vh         |          |          |      |

| FD <sub>H</sub> | CCU6_CC61SRH Reset: 00 <sub>H</sub>                                   | Bit Field |     |      |           | CC6  | 1SH        |          |          |      |

|                 | Capture/Compare Shadow Register<br>for Channel CC61 High              | Туре      |     |      |           | rv   | vh         |          |          |      |

| Fe <sub>H</sub> | CCU6_CC62SRL Reset: 00 <sub>H</sub>                                   | Bit Field |     |      |           | CC6  | 2SL        |          |          |      |

|                 | Capture/Compare Shadow Register<br>for Channel CC62 Low               | Туре      |     |      |           | rv   | vh         |          |          |      |

| FF <sub>H</sub> | CCU6_CC62SRH Reset: 00 <sub>H</sub>                                   | Bit Field |     |      |           | CC6  | 2SH        |          |          |      |

|                 | Capture/Compare Shadow Register<br>for Channel CC62 High              | Туре      |     |      |           | rv   | vh         |          |          |      |

| RMAP =          | 0, PAGE 1                                                             |           |     |      |           |      |            |          |          |      |

| 9A <sub>H</sub> | CCU6_CC63RL Reset: 00 <sub>H</sub>                                    | Bit Field |     |      |           | CC6  | 3VL        |          |          |      |

|                 | Capture/Compare Register for<br>Channel CC63 Low                      | Туре      |     |      |           | r    | h          |          |          |      |

| 98 <sub>H</sub> | CCU6_CC63RH Reset: 00 <sub>H</sub>                                    | Bit Field |     |      |           | CC6  | 3VH        |          |          |      |

|                 | Capture/Compare Register for<br>Channel CC63 High                     | Туре      |     |      |           | r    | h          |          |          |      |

| 9CH             | CCU6_T12PRL Reset: 00 <sub>H</sub>                                    | Bit Field |     |      |           | T12  | PVL        |          |          |      |

|                 | Timer T12 Period Register Low                                         | Туре      |     |      |           | rv   | vh         |          |          |      |

| 9D <sub>H</sub> | CCU6_T12PRH Reset: 00 <sub>H</sub><br>Timer T12 Period Register High  | Bit Field |     |      |           | T12  | PVH        |          |          |      |

|                 |                                                                       | Туре      |     |      |           | rv   | vh         |          |          |      |

| 9E <sub>H</sub> | CCU6_T13PRLReset: 00HTimer T13 Period Register Low                    | Bit Field |     |      |           | T13  | PVL        |          |          |      |

|                 |                                                                       | Туре      |     |      |           | rv   | vh         |          |          |      |

| 9F <sub>H</sub> | CCU6_T13PRH Reset: 00 <sub>H</sub><br>Timer T13 Period Register High  | Bit Field |     |      |           | T13  | PVH        |          |          |      |

|                 |                                                                       | Туре      |     |      |           | rv   | vh         |          |          |      |

| A4 <sub>H</sub> | CCU6_T12DTCL Reset: 00 <sub>H</sub><br>Dead-Time Control Register for | Bit Field |     |      |           | D    | ΓM         |          |          |      |

|                 | Timer T12 Low                                                         | Туре      |     |      |           | r    | N          |          |          |      |

| А5 <sub>Н</sub> | CCU6_T12DTCH Reset: 00 <sub>H</sub><br>Dead-Time Control Register for | Bit Field | 0   | DTR2 | DTR1      | DTR0 | 0          | DTE2     | DTE1     | DTE0 |

|                 | Timer T12 High                                                        | Туре      | r   | rh   | rh        | rh   | r          | rw       | rw       | rw   |

| A6 <sub>H</sub> | CCU6_TCTR0L Reset: 00 <sub>H</sub><br>Timer Control Register 0 Low    | Bit Field | СТМ | CDIR | STE1<br>2 | T12R | T12<br>PRE |          | T12CLK   |      |

|                 |                                                                       | Туре      | rw  | rh   | rh        | rh   | rw         |          | rw       |      |

| А7 <sub>Н</sub> | CCU6_TCTR0H Reset: 00 <sub>H</sub><br>Timer Control Register 0 High   | Bit Field |     | 0    | STE1<br>3 | T13R | T13<br>PRE |          | T13CLK   |      |

|                 |                                                                       | Туре      |     | r    | rh        | rh   | rw         |          | rw       |      |

| FA <sub>H</sub> | CCU6_CC60RL Reset: 00 <sub>H</sub>                                    | Bit Field |     |      |           | CC6  | 60VL       |          |          |      |

|                 | Capture/Compare Register for<br>Channel CC60 Low                      | Туре      |     |      |           | r    | h          |          |          |      |

#### Table 14CCU6 Register Overview (cont'd)

| Addr            | Register Name                                                       | Bit       | 7     | 6            | 5            | 4          | 3            | 2          | 1            | 0          |

|-----------------|---------------------------------------------------------------------|-----------|-------|--------------|--------------|------------|--------------|------------|--------------|------------|

| Fe <sub>H</sub> | CCU6_CMPSTATL Reset: 00 <sub>H</sub><br>Compare State Register Low  | Bit Field | 0     | CC63<br>ST   | CC<br>POS2   | CC<br>POS1 | CC<br>POS0   | CC62<br>ST | CC61<br>ST   | CC60<br>ST |

|                 |                                                                     | Туре      | r     | rh           | rh           | rh         | rh           | rh         | rh           | rh         |

| FF <sub>H</sub> | CCU6_CMPSTATH Reset: 00 <sub>H</sub><br>Compare State Register High | Bit Field | T13IM | COUT<br>63PS | COUT<br>62PS | CC62<br>PS | COUT<br>61PS | CC61<br>PS | COUT<br>60PS | CC60<br>PS |

|                 |                                                                     | Туре      | rwh   | rwh          | rwh          | rwh        | rwh          | rwh        | rwh          | rwh        |

## 3.2.4.11 UART1 Registers

The UART1 SFRs can be accessed in the mapped memory area (RMAP = 1).

#### Table 15 UART1 Register Overview

| Addr            | Register Name                          | Bit       | 7   | 6      | 5   | 4    | 3     | 2       | 1   | 0    |  |  |

|-----------------|----------------------------------------|-----------|-----|--------|-----|------|-------|---------|-----|------|--|--|

| RMAP =          | = 1                                    | 1         |     |        |     |      |       |         |     | 1    |  |  |

| C8 <sub>H</sub> | SCON Reset: 00 <sub>H</sub>            | Bit Field | SM0 | SM1    | SM2 | REN  | TB8   | RB8     | TI  | RI   |  |  |

|                 | Serial Channel Control Register        | Туре      | rw  | rw     | rw  | rw   | rw    | rwh     | rwh | rwh  |  |  |

| C9 <sub>H</sub> | SBUF Reset: 00 <sub>H</sub>            | Bit Field |     |        |     | AL   |       |         |     |      |  |  |

|                 | Serial Data Buffer Register            | Туре      |     |        |     | rv   | vh    |         |     |      |  |  |

| са <sub>Н</sub> | BCON Reset: 00 <sub>H</sub>            | Bit Field | 0   |        |     |      |       | BRPRE R |     |      |  |  |

|                 | Baud Rate Control Register             | Туре      | r   |        |     |      |       | rw rw   |     |      |  |  |

| св <sub>Н</sub> | BG Reset: 00 <sub>H</sub>              | Bit Field |     |        |     | BR_V | 'ALUE |         |     |      |  |  |

|                 | Baud Rate Timer/Reload<br>Register     | Туре      |     |        |     | rv   | vh    |         |     |      |  |  |

| сс <sub>Н</sub> | FDCON Reset: 00 <sub>H</sub>           | Bit Field |     |        | 0   |      |       | NDOV    | FDM | FDEN |  |  |

|                 | Fractional Divider Control<br>Register | Туре      |     |        | r   |      |       | rwh     | rw  | rw   |  |  |

| CD <sub>H</sub> | FDSTEP Reset: 00 <sub>H</sub>          | Bit Field |     |        |     | ST   | ΈP    |         |     |      |  |  |

|                 | Fractional Divider Reload<br>Register  | Туре      | rw  |        |     |      |       |         |     |      |  |  |

| Ceh             | FDRES Reset: 00 <sub>H</sub>           | Bit Field |     | RESULT |     |      |       |         |     |      |  |  |

|                 | Fractional Divider Result<br>Register  | Туре      |     |        |     | r    | h     |         |     |      |  |  |

#### Table 17CAN Register Overview (cont'd)

| Addr            | Register Name                | Bit       | 7      | 6 | 5 | 4  | 3  | 2 | 1 | 0 |

|-----------------|------------------------------|-----------|--------|---|---|----|----|---|---|---|

| db <sub>h</sub> | DATA0 Reset: 00 <sub>H</sub> | Bit Field |        |   |   | С  | D  |   |   |   |

|                 | CAN Data Register 0          | Туре      |        |   |   | rv | vh |   |   |   |

| DC <sub>H</sub> | DATA1 Reset: 00 <sub>H</sub> | Bit Field | CD     |   |   |    |    |   |   |   |

|                 | CAN Data Register 1          | Туре      | pe rwh |   |   |    |    |   |   |   |

| dd <sub>H</sub> | DATA2 Reset: 00 <sub>H</sub> | Bit Field |        |   |   | С  | D  |   |   |   |

|                 | CAN Data Register 2          | Туре      |        |   |   | rv | vh |   |   |   |

| de <sub>h</sub> | DATA3 Reset: 00 <sub>H</sub> | Bit Field | d CD   |   |   |    |    |   |   |   |

|                 | CAN Data Register 3          | Туре      | rwh    |   |   |    |    |   |   |   |

## 3.2.4.14 OCDS Registers

The OCDS SFRs can be accessed in the mapped memory area (RMAP = 1).

#### Table 18 OCDS Register Overview

| Addr            | Register Name                                                  | Bit       | 7           | 6         | 5          | 4           | 3           | 2         | 1          | 0         |  |  |

|-----------------|----------------------------------------------------------------|-----------|-------------|-----------|------------|-------------|-------------|-----------|------------|-----------|--|--|

| RMAP =          | = 1                                                            | 1         |             |           |            |             |             |           |            |           |  |  |

| E9 <sub>H</sub> | MMCR2 Reset: 1U <sub>H</sub><br>Monitor Mode Control 2         | Bit Field | STMO<br>DE  | EXBC      | DSUS<br>P  | MBCO<br>N   | ALTDI       | MMEP      | MMOD<br>E  | JENA      |  |  |

|                 | Register                                                       | Туре      | rw          | rw        | rw         | rwh         | rw          | rwh       | rh         | rh        |  |  |

| F1 <sub>H</sub> | MMCR Reset: 00 <sub>H</sub><br>Monitor Mode Control Register   | Bit Field | MEXIT<br>_P | MEXIT     | 0          | MSTE<br>P   | MRAM<br>S_P | MRAM<br>S | TRF        | RRF       |  |  |

|                 |                                                                | Туре      | w           | rwh       | r          | rw          | w           | rwh       | rh         | rh        |  |  |

| F2 <sub>H</sub> | MMSR Reset: 00 <sub>H</sub><br>Monitor Mode Status Register    | Bit Field | MBCA<br>M   | MBCIN     | EXBF       | SWBF        | HWB3<br>F   | HWB2<br>F | HWB1<br>F  | HWB0<br>F |  |  |

|                 |                                                                | Туре      | rw          | rwh       | rwh        | rwh         | rwh         | rwh       | rwh        | rwh       |  |  |

| F3 <sub>H</sub> | MMBPCR Reset: 00 <sub>H</sub><br>Breakpoints Control Register  | Bit Field | SWBC        | HW        | B3C        | HW          | B2C         | HWB1<br>C |            |           |  |  |

|                 |                                                                | Туре      | rw          | n         | N          | r           | w           | rw        | r          | N         |  |  |

| F4 <sub>H</sub> | MMICR Reset: 00 <sub>H</sub><br>Monitor Mode Interrupt Control | Bit Field | DVEC<br>T   | DRET<br>R | COMR<br>ST | MSTS<br>EL  | MMUI<br>E_P | MMUI<br>E | RRIE_<br>P | RRIE      |  |  |

|                 | Register                                                       | Туре      | rwh         | rwh       | rwh        | rh          | w           | rw        | w          | rw        |  |  |

| F5 <sub>H</sub> | MMDR Reset: 00 <sub>H</sub>                                    | Bit Field |             |           |            | MN          | IRR         |           |            |           |  |  |

|                 | Monitor Mode Data Transfer<br>Register<br>Receive              | Туре      |             |           |            | r           | h           |           |            |           |  |  |

| F6 <sub>H</sub> | HWBPSR Reset: 00 <sub>H</sub><br>Hardware Breakpoints Select   | Bit Field |             | 0         |            | BPSEL<br>_P |             | BP        | SEL        |           |  |  |

|                 | Register                                                       | Туре      |             | r         |            | w           |             | r         | w          |           |  |  |

| F7 <sub>H</sub> | HWBPDR Reset: 00 <sub>H</sub>                                  | Bit Field |             |           |            | HWE         | BPxx        | x         |            |           |  |  |

|                 | Hardware Breakpoints Data<br>Register                          | Туре      |             |           |            | r           | w           |           |            |           |  |  |

| EB <sub>H</sub> | MMWR1 Reset: 00 <sub>H</sub>                                   | Bit Field |             |           |            | MM          | NR1         |           |            |           |  |  |

|                 | Monitor Work Register 1                                        | Туре      |             |           |            | r           | W           |           |            |           |  |  |

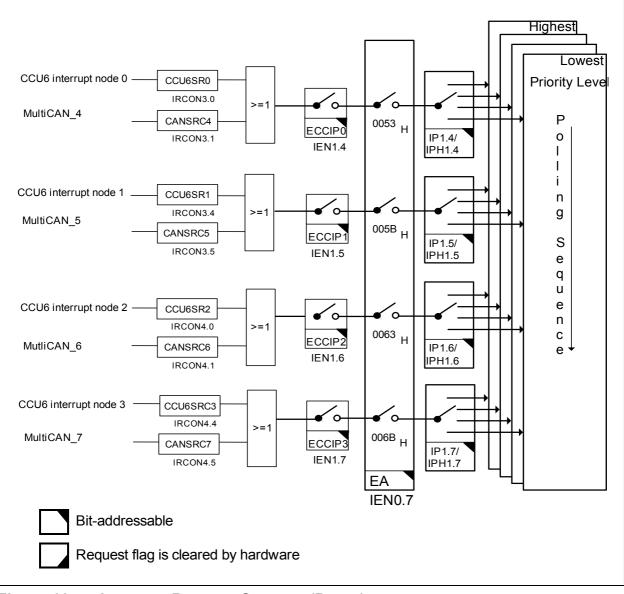

Figure 18 Interrupt Request Sources (Part 5)

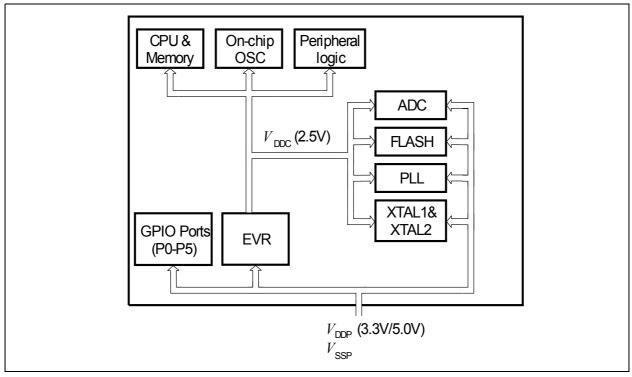

## 3.6 Power Supply System with Embedded Voltage Regulator

The XC886/888 microcontroller requires two different levels of power supply:

- 3.3 V or 5.0 V for the Embedded Voltage Regulator (EVR) and Ports

- 2.5 V for the core, memory, on-chip oscillator, and peripherals

**Figure 21** shows the XC886/888 power supply system. A power supply of 3.3 V or 5.0 V must be provided from the external power supply pin. The 2.5 V power supply for the logic is generated by the EVR. The EVR helps to reduce the power consumption of the whole chip and the complexity of the application board design.

The EVR consists of a main voltage regulator and a low power voltage regulator. In active mode, both voltage regulators are enabled. In power-down mode, the main voltage regulator is switched off, while the low power voltage regulator continues to function and provide power supply to the system with low power consumption.

Figure 21 XC886/888 Power Supply System

## **EVR Features**

- Input voltage ( $V_{\text{DDP}}$ ): 3.3 V/5.0 V

- Output voltage ( $V_{DDC}$ ): 2.5 V ± 7.5%

- · Low power voltage regulator provided in power-down mode

- $V_{\text{DDC}}$  and  $V_{\text{DDP}}$  prewarning detection

- $V_{\text{DDC}}$  brownout detection

- 1) BSL mode is automatically entered if no valid password is installed and data at memory address 0000H equals zero.

- 2) OSC is bypassed in MultiCAN BSL mode

- 3) Normal user mode with standard JTAG (TCK,TDI,TDO) pins for hot-attach purpose.

Note: The boot options are valid only with the default set of UART and JTAG pins.

## 3.8 Clock Generation Unit

The Clock Generation Unit (CGU) allows great flexibility in the clock generation for the XC886/888. The power consumption is indirectly proportional to the frequency, whereas the performance of the microcontroller is directly proportional to the frequency. During user program execution, the frequency can be programmed for an optimal ratio between performance and power consumption. Therefore the power consumption can be adapted to the actual application state.

#### Features

- Phase-Locked Loop (PLL) for multiplying clock source by different factors

- PLL Base Mode

- Prescaler Mode

- PLL Mode

- Power-down mode support

The CGU consists of an oscillator circuit and a PLL. In the XC886/888, the oscillator can be from either of these two sources: the on-chip oscillator (9.6 MHz) or the external oscillator (4 MHz to 12 MHz). The term "oscillator" is used to refer to both on-chip oscillator and external oscillator, unless otherwise stated. After the reset, the on-chip oscillator will be used by default. The external oscillator can be selected via software. In addition, the PLL provides a fail-safe logic to perform oscillator run and loss-of-lock detection. This allows emergency routines to be executed for system recovery or to perform system shut down.

| Table 31 Deviation Error for UART with Fractional Divider enabled |                               |                                |                        |                    |  |  |  |  |

|-------------------------------------------------------------------|-------------------------------|--------------------------------|------------------------|--------------------|--|--|--|--|

| f <sub>pclk</sub>                                                 | Prescaling Factor<br>(2BRPRE) | Reload Value<br>(BR_VALUE + 1) | STEP                   | Deviation<br>Error |  |  |  |  |

| 24 MHz                                                            | 1                             | 10 (A <sub>H</sub> )           | 197 (C5 <sub>H</sub> ) | +0.20 %            |  |  |  |  |

| 12 MHz                                                            | 1                             | 6 (6 <sub>H</sub> )            | 236 (EC <sub>H</sub> ) | +0.03 %            |  |  |  |  |

| 8 MHz                                                             | 1                             | 4 (4 <sub>H</sub> )            | 236 (EC <sub>H</sub> ) | +0.03 %            |  |  |  |  |

| 6 MHz                                                             | 1                             | 3 (3 <sub>H</sub> )            | 236 (EC <sub>H</sub> ) | +0.03 %            |  |  |  |  |

#### Deviation Error for UADT with Errotional Divider enabled Cable 24

#### 3.13.2 **Baud Rate Generation using Timer 1**

In UART modes 1 and 3 of UART module, Timer 1 can be used for generating the variable baud rates. In theory, this timer could be used in any of its modes. But in practice, it should be set into auto-reload mode (Timer 1 mode 2), with its high byte set to the appropriate value for the required baud rate. The baud rate is determined by the Timer 1 overflow rate and the value of SMOD as follows:

Mode 1, 3 baud rate=

$$\frac{2^{\text{SMOD}} \times f_{\text{PCLK}}}{32 \times 2 \times (256 - \text{TH1})}$$

(3.7)

#### 3.14 Normal Divider Mode (8-bit Auto-reload Timer)

Setting bit FDM in register FDCON to 1 configures the fractional divider to normal divider mode, while at the same time disables baud rate generation (see Figure 30). Once the fractional divider is enabled (FDEN = 1), it functions as an 8-bit auto-reload timer (with no relation to baud rate generation) and counts up from the reload value with each input clock pulse. Bit field RESULT in register FDRES represents the timer value, while bit field STEP in register FDSTEP defines the reload value. At each timer overflow, an overflow flag (FDCON.NDOV) will be set and an interrupt request generated. This gives an output clock  $f_{MOD}$  that is 1/n of the input clock  $f_{DIV}$ , where n is defined by 256 - STEP. The output frequency in normal divider mode is derived as follows:

$$f_{MOD} = f_{DIV} \times \frac{1}{256 - STEP}$$

(3.8)

needed for the handshaking between the master and slave tasks is provided by the master task through the header portion of the frame.

The header consists of a break and synch pattern followed by an identifier. Among these three fields, only the break pattern cannot be transmitted as a normal 8-bit UART data. The break must contain a dominant value of 13 bits or more to ensure proper synchronization of slave nodes.

In the LIN communication, a slave task is required to be synchronized at the beginning of the protected identifier field of frame. For this purpose, every frame starts with a sequence consisting of a break field followed by a synch byte field. This sequence is unique and provides enough information for any slave task to detect the beginning of a new frame and be synchronized at the start of the identifier field.

Upon entering LIN communication, a connection is established and the transfer speed (baud rate) of the serial communication partner (host) is automatically synchronized in the following steps:

STEP 1: Initialize interface for reception and timer for baud rate measurement

STEP 2: Wait for an incoming LIN frame from host

STEP 3: Synchronize the baud rate to the host

- STEP 4: Enter for Master Request Frame or for Slave Response Frame

- Note: Re-synchronization and setup of baud rate are always done for **every** Master Request Header or Slave Response Header LIN frame.

# 3.21 Analog-to-Digital Converter

The XC886/888 includes a high-performance 10-bit Analog-to-Digital Converter (ADC) with eight multiplexed analog input channels. The ADC uses a successive approximation technique to convert the analog voltage levels from up to eight different sources. The analog input channels of the ADC are available at Port 2.

## Features

- Successive approximation

- 8-bit or 10-bit resolution (TUE of ± 1 LSB and ± 2 LSB, respectively)

- Eight analog channels

- Four independent result registers

- Result data protection for slow CPU access (wait-for-read mode)

- Single conversion mode

- Autoscan functionality

- Limit checking for conversion results

- Data reduction filter (accumulation of up to 2 conversion results)

- Two independent conversion request sources with programmable priority

- · Selectable conversion request trigger

- · Flexible interrupt generation with configurable service nodes

- Programmable sample time

- Programmable clock divider

- · Cancel/restart feature for running conversions

- Integrated sample and hold circuitry

- Compensation of offset errors

- Low power modes

# 3.21.1 ADC Clocking Scheme

A common module clock  $f_{ADC}$  generates the various clock signals used by the analog and digital parts of the ADC module:

- $f_{ADCA}$  is input clock for the analog part.

- $f_{ADCI}$  is internal clock for the analog part (defines the time base for conversion length and the sample time). This clock is generated internally in the analog part, based on the input clock  $f_{ADCA}$  to generate a correct duty cycle for the analog components.

- $f_{ADCD}$  is input clock for the digital part.

The internal clock for the analog part  $f_{ADCI}$  is limited to a maximum frequency of 10 MHz. Therefore, the ADC clock prescaler must be programmed to a value that ensures  $f_{ADCI}$  does not exceed 10 MHz. The prescaler ratio is selected by bit field CTC in register

## Table 36Chip Identification Number (cont'd)

| Product Variant   | Chip Identification Number |                       |                       |  |  |  |  |  |

|-------------------|----------------------------|-----------------------|-----------------------|--|--|--|--|--|

|                   | AA-Step                    | AB-Step               | AC-Step               |  |  |  |  |  |

| XC886-6FFA 3V3    | -                          | 095D1562 <sub>H</sub> | 0B5D1562 <sub>H</sub> |  |  |  |  |  |

| XC888-6FFA 3V3    | -                          | 095D1563 <sub>н</sub> | 0B5D1563 <sub>H</sub> |  |  |  |  |  |

| XC886CLM-8FFA 5V  | -                          | 09900102 <sub>H</sub> | 0B900102 <sub>H</sub> |  |  |  |  |  |

| XC888CLM-8FFA 5V  | -                          | 09900103 <sub>H</sub> | 0B900103 <sub>H</sub> |  |  |  |  |  |

| XC886LM-8FFA 5V   | -                          | 09900122 <sub>H</sub> | 0B900122 <sub>H</sub> |  |  |  |  |  |

| XC888LM-8FFA 5V   | -                          | 09900123 <sub>H</sub> | 0B900123 <sub>H</sub> |  |  |  |  |  |

| XC886CLM-6FFA 5V  | -                          | 09951502 <sub>H</sub> | 0B951502 <sub>H</sub> |  |  |  |  |  |

| XC888CLM-6FFA 5V  | -                          | 09951503 <sub>Н</sub> | 0B951503 <sub>H</sub> |  |  |  |  |  |

| XC886LM-6FFA 5V   | -                          | 09951522 <sub>H</sub> | 0B951522 <sub>H</sub> |  |  |  |  |  |

| XC888LM-6FFA 5V   | -                          | 09951523 <sub>Н</sub> | 0B951523 <sub>H</sub> |  |  |  |  |  |

| XC886CM-8FFA 5V   | -                          | 09980102 <sub>H</sub> | 0B980102 <sub>H</sub> |  |  |  |  |  |

| XC888CM-8FFA 5V   | -                          | 09980103 <sub>H</sub> | 0B980103 <sub>H</sub> |  |  |  |  |  |

| XC886C-8FFA 5V    | -                          | 09980142 <sub>H</sub> | 0B980142 <sub>H</sub> |  |  |  |  |  |

| XC888C-8FFA 5V    | -                          | 09980143 <sub>H</sub> | 0B980143 <sub>H</sub> |  |  |  |  |  |

| XC886-8FFA 5V     | -                          | 09980162 <sub>H</sub> | 0B980162 <sub>H</sub> |  |  |  |  |  |

| XC888-8FFA 5V     | -                          | 09980163 <sub>H</sub> | 0B980163 <sub>H</sub> |  |  |  |  |  |

| XC886CM-6FFA 5V   | -                          | 099D1502 <sub>H</sub> | 0B9D1502 <sub>H</sub> |  |  |  |  |  |

| XC888CM-6FFA 5V   | -                          | 099D1503 <sub>H</sub> | 0B9D1503 <sub>H</sub> |  |  |  |  |  |

| XC886C-6FFA 5V    | -                          | 099D1542 <sub>H</sub> | 0B9D1542 <sub>H</sub> |  |  |  |  |  |

| XC888C-6FFA 5V    | -                          | 099D1543 <sub>H</sub> | 0B9D1543 <sub>H</sub> |  |  |  |  |  |

| XC886-6FFA 5V     | -                          | 099D1562 <sub>H</sub> | 0B9D1562 <sub>H</sub> |  |  |  |  |  |

| XC888-6FFA 5V     | -                          | 099D1563 <sub>H</sub> | 0B9D1563 <sub>H</sub> |  |  |  |  |  |

| ROM Devices       | ·                          |                       | ·                     |  |  |  |  |  |

| XC886CLM-8RFA 3V3 | 22400502 <sub>H</sub>      | -                     | -                     |  |  |  |  |  |

| XC888CLM-8RFA 3V3 | 22400503 <sub>H</sub>      | -                     | -                     |  |  |  |  |  |

| XC886LM-8RFA 3V3  | 22400522 <sub>H</sub>      | -                     | -                     |  |  |  |  |  |

| XC888LM-8RFA 3V3  | 22400523 <sub>H</sub>      | -                     | -                     |  |  |  |  |  |

| XC886CLM-6RFA 3V3 | 22411502 <sub>H</sub>      | -                     | -                     |  |  |  |  |  |

| XC888CLM-6RFA 3V3 | 22411503 <sub>H</sub>      | -                     | -                     |  |  |  |  |  |

## 4.2 DC Parameters

The electrical characteristics of the DC Parameters are detailed in this section.

## 4.2.1 Input/Output Characteristics

Table 38 provides the characteristics of the input/output pins of the XC886/888.

| Table 38 | Input/Output Characteristics | s (Operating Conditions apply) |

|----------|------------------------------|--------------------------------|

|----------|------------------------------|--------------------------------|

| Parameter                                                      | Symbol            |    | Limit Values                |                             | Unit | Test Conditions                                          |  |

|----------------------------------------------------------------|-------------------|----|-----------------------------|-----------------------------|------|----------------------------------------------------------|--|

|                                                                |                   |    | min.                        | max.                        |      |                                                          |  |

| V <sub>DDP</sub> = 5 V Range                                   |                   |    |                             |                             |      | ·                                                        |  |

| Output low voltage                                             | V <sub>OL</sub>   | CC | -                           | 1.0                         | V    | I <sub>OL</sub> = 15 mA                                  |  |

|                                                                |                   |    | -                           | 1.0                         | V    | $I_{OL}$ = 5 mA, current into<br>all pins > 60 mA        |  |

|                                                                |                   |    | -                           | 0.4                         | V    | $I_{\rm OL}$ = 5 mA, current into all pins $\leq$ 60 mA  |  |

| Output high voltage                                            | V <sub>OH</sub>   | CC | V <sub>DDP</sub> -<br>1.0   | -                           | V    | I <sub>ОН</sub> = -15 mA                                 |  |

|                                                                |                   |    | V <sub>DDP</sub> -<br>1.0   | -                           | V    | $I_{OH}$ = -5 mA, current<br>from all pins > 60 mA       |  |

|                                                                |                   |    | V <sub>DDP</sub> - 0.4      | -                           | V    | $I_{\rm OH}$ = -5 mA, current from all pins $\leq$ 60 mA |  |

| Input low voltage on<br>port pins<br>(all except P0.0 & P0.1)  | V <sub>ILP</sub>  | SR | -                           | $0.3 \times V_{\text{DDP}}$ | V    | CMOS Mode                                                |  |

| Input low voltage on P0.0 & P0.1                               | V <sub>ILP0</sub> | SR | -0.2                        | $0.3 \times V_{ m DDP}$     | V    | CMOS Mode                                                |  |

| Input low voltage on<br>RESET pin                              | $V_{ILR}$         | SR | -                           | $0.3 \times V_{\text{DDP}}$ | V    | CMOS Mode                                                |  |

| Input low voltage on<br>TMS pin                                | V <sub>ILT</sub>  | SR | -                           | $0.3 \times V_{ m DDP}$     | V    | CMOS Mode                                                |  |

| Input high voltage on<br>port pins<br>(all except P0.0 & P0.1) | V <sub>IHP</sub>  | SR | $0.7 \times V_{\text{DDP}}$ | -                           | V    | CMOS Mode                                                |  |

| Input high voltage on P0.0 & P0.1                              | V <sub>IHP0</sub> | SR | $0.7 \times V_{ m DDP}$     | V <sub>DDP</sub>            | V    | CMOS Mode                                                |  |

## Table 38 Input/Output Characteristics (Operating Conditions apply) (cont'd)

| Parameter                                                                      | Symbol             |    | Limit                       | Values                  | Unit | Test Conditions                                        |  |

|--------------------------------------------------------------------------------|--------------------|----|-----------------------------|-------------------------|------|--------------------------------------------------------|--|

|                                                                                |                    |    | min.                        | min. max.               |      |                                                        |  |

| Input high voltage on RESET pin                                                | V <sub>IHR</sub>   | SR | $0.7 \times V_{\text{DDP}}$ | -                       | V    | CMOS Mode                                              |  |

| Input high voltage on TMS pin                                                  | V <sub>IHT</sub>   | SR | $0.75 \times V_{ m DDP}$    | -                       | V    | CMOS Mode                                              |  |

| Input Hysteresis on port<br>pins                                               | HYSP               | CC | $0.07 \times V_{ m DDP}$    | -                       | V    | CMOS Mode <sup>1)</sup>                                |  |

| Input Hysteresis on XTAL1                                                      | HYSX               | CC | $0.07 \times V_{ m DDC}$    | -                       | V    | 1)                                                     |  |

| Input low voltage at<br>XTAL1                                                  | $V_{ILX}$          | SR | V <sub>SS</sub> -<br>0.5    | $0.3 \times V_{ m DDC}$ | V    |                                                        |  |

| Input high voltage at XTAL1                                                    | V <sub>IHX</sub>   | SR | $0.7 \times V_{ m DDC}$     | V <sub>DDC</sub> + 0.5  | V    |                                                        |  |

| Pull-up current                                                                | $I_{\rm PU}$       | SR | -                           | -10                     | μA   | V <sub>IHP,min</sub>                                   |  |

|                                                                                |                    |    | -150                        | _                       | μA   | $V_{\rm ILP,max}$                                      |  |

| Pull-down current                                                              | $I_{\rm PD}$       | SR | -                           | 10                      | μA   | $V_{ILP,max}$                                          |  |

|                                                                                |                    |    | 150                         | -                       | μA   | V <sub>IHP,min</sub>                                   |  |

| Input leakage current                                                          | I <sub>OZ1</sub>   | CC | -1                          | 1                       | μA   | $0 < V_{IN} < V_{DDP},$<br>$T_A \le 125^{\circ}C^{2)}$ |  |

| Input current at XTAL1                                                         | $I_{ILX}$          | CC | -10                         | 10                      | μA   |                                                        |  |

| Overload current on any pin                                                    | I <sub>OV</sub>    | SR | -5                          | 5                       | mA   |                                                        |  |

| Absolute sum of overload currents                                              | $\Sigma  I_{OV} $  | SR | -                           | 25                      | mA   | 3)                                                     |  |

| Voltage on any pin during $V_{\text{DDP}}$ power off                           | V <sub>PO</sub>    | SR | -                           | 0.3                     | V    | 4)                                                     |  |

| Maximum current per pin (excluding $V_{\text{DDP}}$ and $V_{\text{SS}}$ )      | I <sub>M</sub> SR  | SR | -                           | 15                      | mA   |                                                        |  |

| Maximum current for all pins (excluding $V_{\text{DDP}}$ and $V_{\text{SS}}$ ) | $\Sigma  I_{M} $   | SR | -                           | 90                      | mA   |                                                        |  |

| Maximum current into $V_{\text{DDP}}$                                          | I <sub>MVDDP</sub> | SR | -                           | 120                     | mA   | 3)                                                     |  |

#### Table 40ADC Characteristics (Operating Conditions apply; $V_{DDP}$ = 5V Range)

|                                                              |                     |    |      |           |                           | -    |                         |

|--------------------------------------------------------------|---------------------|----|------|-----------|---------------------------|------|-------------------------|

| Parameter                                                    | Symbol              |    | Liı  | nit Val   | ues                       | Unit | Test Conditions/        |

|                                                              |                     |    | min. | typ. max. |                           |      | Remarks                 |

| Overload current coupling factor for                         | K <sub>OVD</sub>    | CC | _    | -         | 5.0 x<br>10 <sup>-3</sup> | -    | $I_{\rm OV} > 0^{1)3)}$ |

| digital I/O pins                                             |                     |    | _    | -         | 1.0 x<br>10 <sup>-2</sup> | -    | $I_{\rm OV} < 0^{1)3)}$ |

| Switched<br>capacitance at the<br>reference voltage<br>input | C <sub>AREFSW</sub> | CC | _    | 10        | 20                        | pF   | 1)4)                    |

| Switched<br>capacitance at the<br>analog voltage<br>inputs   | C <sub>AINSW</sub>  | CC | _    | 5         | 7                         | pF   | 1)5)                    |

| Input resistance of the reference input                      | R <sub>AREF</sub>   | CC | _    | 1         | 2                         | kΩ   | 1)                      |

| Input resistance of<br>the selected analog<br>channel        | R <sub>AIN</sub>    | CC | _    | 1         | 1.5                       | kΩ   | 1)                      |

1) Not subjected to production test, verified by design/characterization

2) TUE is tested at  $V_{AREF}$  = 5.0 V,  $V_{AGND}$  = 0 V,  $V_{DDP}$  = 5.0 V.

- 3) An overload current  $(I_{OV})$  through a pin injects a certain error current  $(I_{INJ})$  into the adjacent pins. This error current adds to the respective pin's leakage current  $(I_{OZ})$ . The amount of error current depends on the overload current and is defined by the overload coupling factor  $K_{OV}$ . The polarity of the injected error current is inverse compared to the polarity of the overload current that produces it. The total current through a pin is  $|I_{TOT}| = |I_{OZ1}| + (|I_{OV}| \times K_{OV})$ . The additional error current may distort the input voltage on analog inputs.

- 4) This represents an equivalent switched capacitance. This capacitance is not switched to the reference voltage at once. Instead of this, smaller capacitances are successively switched to the reference voltage.

- 5) The sampling capacity of the conversion C-Network is pre-charged to  $V_{AREF}/2$  before connecting the input to the C-Network. Because of the parasitic elements, the voltage measured at ANx is lower than  $V_{AREF}/2$ .

## 4.3.4 On-Chip Oscillator Characteristics

Table 47 provides the characteristics of the on-chip oscillator in the XC886/888.

| Table 47 | On-chip Oscillator Characteristics (Operating Conditions apply) |

|----------|-----------------------------------------------------------------|

|----------|-----------------------------------------------------------------|

| Parameter                      | Symbol           |    | Limit Values |              |      | Unit | Test Conditions                                                                                                                    |  |

|--------------------------------|------------------|----|--------------|--------------|------|------|------------------------------------------------------------------------------------------------------------------------------------|--|

|                                |                  |    | min.         | n. typ. max. |      |      |                                                                                                                                    |  |

| Nominal frequency              | f <sub>nom</sub> | CC | 9.36         | 9.6          | 9.84 | MHz  | under nominal conditions <sup>1)</sup>                                                                                             |  |

| Long term frequency deviation  | Δf <sub>LT</sub> | CC | -5.0         | -            | 5.0  | %    | with respect to $f_{\text{NOM}}$ , over<br>lifetime and temperature<br>(-10°C to 125°C), for one<br>given device after<br>trimming |  |

|                                |                  |    | -6.0         | -            | 0    | %    | with respect to $f_{NOM}$ , over<br>lifetime and temperature<br>(-40°C to<br>-10°C), for one given<br>device after trimming        |  |

| Short term frequency deviation | $\Delta f_{ST}$  | CC | -1.0         | -            | 1.0  | %    | within one LIN message<br>(<10 ms 100 ms)                                                                                          |  |

1) Nominal condition:  $V_{\text{DDC}}$  = 2.5 V,  $T_{\text{A}}$  = + 25°C.

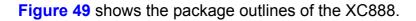

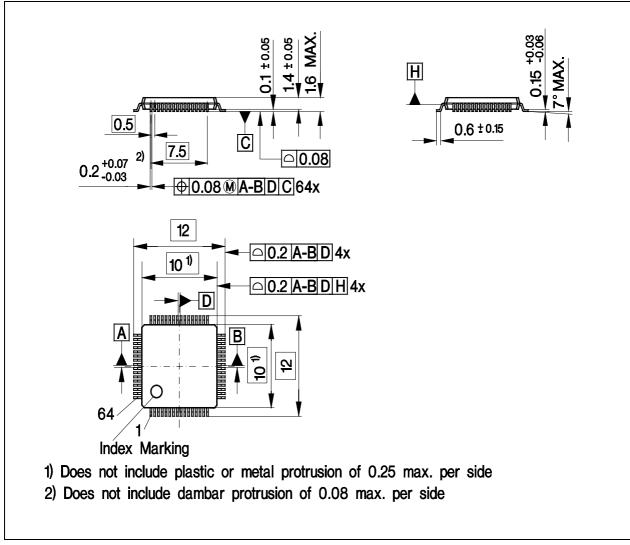

#### Package and Quality Declaration

## Figure 49 PG-TQFP-64 Package Outline