Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Betuils                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                          |

| Core Processor             | XC800                                                                             |

| Core Size                  | 8-Bit                                                                             |

| Speed                      | 24MHz                                                                             |

| Connectivity               | CANbus, SSI, UART/USART                                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                             |

| Number of I/O              | 48                                                                                |

| Program Memory Size        | 32KB (32K x 8)                                                                    |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 1.75K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 8x10b                                                                         |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-LQFP                                                                           |

| Supplier Device Package    | PG-TQFP-64                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/saf-xc888c-8ffi-3v3-ac |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **General Device Information**

# 2 General Device Information

**Chapter 2** contains the block diagram, pin configurations, definitions and functions of the XC886/888.

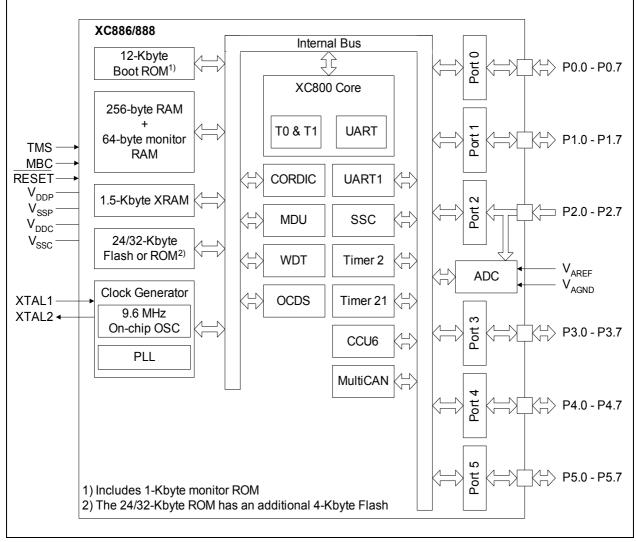

## 2.1 Block Diagram

The block diagram of the XC886/888 is shown in Figure 2.

Figure 2 XC886/888 Block Diagram

## **General Device Information**

## 2.4 Pin Definitions and Functions

The functions and default states of the XC886/888 external pins are provided in Table 3.

| Symbol | Pin Number<br>(TQFP-48/64) | Туре | Reset<br>State | Function                                                                                                                                                                                        |                                                                                                                                                                                                      |  |  |  |

|--------|----------------------------|------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| P0     |                            | I/O  |                | <b>Port 0</b><br>Port 0 is an 8-bit bidirectional general purpose<br>I/O port. It can be used as alternate functions<br>for the JTAG, CCU6, UART, UART1, Timer 2<br>Timer 21, MultiCAN and SSC. |                                                                                                                                                                                                      |  |  |  |

| P0.0   | 11/17                      |      | Hi-Z           | TCK_0<br>T12HR_1<br>CC61_1<br>CLKOUT_0<br>RXDO_1                                                                                                                                                | JTAG Clock Input<br>CCU6 Timer 12 Hardware Run<br>Input<br>Input/Output of<br>Capture/Compare channel 1<br>Clock Output<br>UART Transmit Data Output                                                 |  |  |  |

| P0.1   | 13/21                      |      | Hi-Z           | TDI_0<br>T13HR_1<br>RXD_1<br>RXDC1_0<br>COUT61_1<br>EXF2_1                                                                                                                                      | JTAG Serial Data Input<br>CCU6 Timer 13 Hardware Run<br>Input<br>UART Receive Data Input<br>MultiCAN Node 1 Receiver Input<br>Output of Capture/Compare<br>channel 1<br>Timer 2 External Flag Output |  |  |  |

| P0.2   | 12/18                      |      | PU             | CTRAP_2<br>TDO_0<br>TXD_1<br>TXDC1_0                                                                                                                                                            | CCU6 Trap Input<br>JTAG Serial Data Output<br>UART Transmit Data<br>Output/Clock Output<br>MultiCAN Node 1 Transmitter<br>Output                                                                     |  |  |  |

| P0.3   | 48/63                      |      | Hi-Z           | SCK_1<br>COUT63_1<br>RXDO1_0                                                                                                                                                                    | SSC Clock Input/Output<br>Output of Capture/Compare<br>channel 3<br>UART1 Transmit Data Output                                                                                                       |  |  |  |

Table 3

Pin Definitions and Functions

### **General Device Information**

| Table 0 | T III Belli                |      |                |                                                     |                                                                                                                                                                                          |  |  |  |  |  |  |  |

|---------|----------------------------|------|----------------|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Symbol  | Pin Number<br>(TQFP-48/64) | Туре | Reset<br>State | Function                                            |                                                                                                                                                                                          |  |  |  |  |  |  |  |

| P0.4    | 1/64                       |      | Hi-Z           | MTSR_1                                              | SSC Master Transmit Output/<br>Slave Receive Input                                                                                                                                       |  |  |  |  |  |  |  |

|         |                            |      |                | CC62_1                                              | Input/Output of<br>Capture/Compare channel 2                                                                                                                                             |  |  |  |  |  |  |  |

|         |                            |      |                | TXD1_0                                              | UART1 Transmit Data<br>Output/Clock Output                                                                                                                                               |  |  |  |  |  |  |  |

| P0.5    | 2/1                        |      | Hi-Z           | MRST_1<br>EXINT0_0<br>T2EX1_1<br>RXD1_0<br>COUT62_1 | SSC Master Receive Input/Slave<br>Transmit Output<br>External Interrupt Input 0<br>Timer 21 External Trigger Input<br>UART1 Receive Data Input<br>Output of Capture/Compare<br>channel 2 |  |  |  |  |  |  |  |

| P0.6    | -/2                        |      | PU             | GPIO                                                |                                                                                                                                                                                          |  |  |  |  |  |  |  |

| P0.7    | 47/62                      |      | PU             | CLKOUT_1                                            | Clock Output                                                                                                                                                                             |  |  |  |  |  |  |  |

#### Pin Definitions and Functions (cont'd) Table 3

## **General Device Information**

| Symbol | Pin Number<br>(TQFP-48/64) | Туре | Reset<br>State | Function         |                                                                                             |

|--------|----------------------------|------|----------------|------------------|---------------------------------------------------------------------------------------------|

| P5     |                            | I/O  |                | I/O port. It ca  | 8-bit bidirectional general purpose<br>an be used as alternate functions<br>IART1 and JTAG. |

| P5.0   | -/8                        |      | PU             | EXINT1_1         | External Interrupt Input 1                                                                  |

| P5.1   | -/9                        |      | PU             | EXINT2_1         | External Interrupt Input 2                                                                  |

| P5.2   | -/12                       |      | PU             | RXD_2            | UART Receive Data Input                                                                     |

| P5.3   | -/13                       |      | PU             | TXD_2            | UART Transmit Data<br>Output/Clock Output                                                   |

| P5.4   | _/14                       |      | PU             | RXDO_2           | UART Transmit Data Output                                                                   |

| P5.5   | -/15                       |      | PU             | TDO_2<br>TXD1_2  | JTAG Serial Data Output<br>UART1 Transmit Data Output/<br>Clock Output                      |

| P5.6   | -/19                       |      | PU             | TCK_2<br>RXDO1_2 | JTAG Clock Input<br>UART1 Transmit Data Output                                              |

| P5.7   | -/20                       |      | PU             | TDI_2<br>RXD1_2  | JTAG Serial Data Input<br>UART1 Receive Data Input                                          |

#### Table 3Pin Definitions and Functions (cont'd)

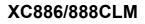

#### Figure 9 Address Extension by Paging

In order to access a register located in a page different from the actual one, the current page must be exited. This is done by reprogramming the bit field PAGE in the page register. Only then can the desired access be performed.

If an interrupt routine is initiated between the page register access and the module register access, and the interrupt needs to access a register located in another page, the current page setting can be saved, the new one programmed and the old page setting restored. This is possible with the storage fields STx (x = 0 - 3) for the save and restore action of the current page setting. By indicating which storage bit field should be used in parallel with the new page value, a single write operation can:

• Save the contents of PAGE in STx before overwriting with the new value (this is done in the beginning of the interrupt routine to save the current page setting and program the new page number); or

| Field | Bits  | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------|-------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OP    | [7:6] | w    | <ul> <li>Operation         <ul> <li>Manual page mode. The value of STNR is ignored and PAGE is directly written.</li> <li>New page programming with automatic page saving. The value written to the bit positions of PAGE is stored. In parallel, the previous contents of PAGE are saved in the storage bit field STx indicated by STNR.</li> </ul> </li> <li>Automatic restore page action. The value written to the bit positions of PAGE is ignored and instead, PAGE is overwritten by the contents of the storage bit field STx indicated by STNR.</li> </ul> |

| 0     | 3     | r    | <b>Reserved</b><br>Returns 0 if read; should be written with 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

## 3.2.3 Bit Protection Scheme

The bit protection scheme prevents direct software writing of selected bits (i.e., protected bits) using the PASSWD register. When the bit field MODE is  $11_B$ , writing  $10011_B$  to the bit field PASS opens access to writing of all protected bits, and writing  $10101_B$  to the bit field PASS closes access to writing of all protected bits. In both cases, the value of the bit field MODE is not changed even if PASSWD register is written with  $98_H$  or  $A8_H$ . It can only be changed when bit field PASS is written with  $11000_B$ , for example, writing D0<sub>H</sub> to PASSWD register disables the bit protection scheme.

Note that access is opened for maximum 32 CCLKs if the "close access" password is not written. If "open access" password is written again before the end of 32 CCLK cycles, there will be a recount of 32 CCLK cycles. The protected bits include the N- and K-Divider bits, NDIV and KDIV; the Watchdog Timer enable bit, WDTEN; and the power-down and slow-down enable bits, PD and SD.

## Table 14CCU6 Register Overview (cont'd)

| Addr            | Register Name                                                        | Bit       | 7          | 6          | 5          | 4          | 3          | 2          | 1           | 0           |  |

|-----------------|----------------------------------------------------------------------|-----------|------------|------------|------------|------------|------------|------------|-------------|-------------|--|

| FB <sub>H</sub> | CCU6_CC60RH Reset: 00 <sub>H</sub>                                   | Bit Field |            | 1          | 1          | CC6        | 60VH       | 1          | 1           | 1           |  |

|                 | Capture/Compare Register for<br>Channel CC60 High                    | Туре      | rh         |            |            |            |            |            |             |             |  |

| FC <sub>H</sub> | CCU6_CC61RL Reset: 00 <sub>H</sub>                                   | Bit Field | CC61VL     |            |            |            |            |            |             |             |  |

|                 | Capture/Compare Register for<br>Channel CC61 Low                     | Туре      |            |            |            | r          | 'n         |            |             |             |  |

| FD <sub>H</sub> | CCU6_CC61RH Reset: 00 <sub>H</sub>                                   | Bit Field |            |            |            | CC6        | 61VH       |            |             |             |  |

|                 | Capture/Compare Register for<br>Channel CC61 High                    | Туре      |            |            |            | r          | 'n         |            |             |             |  |

| FE <sub>H</sub> | CCU6_CC62RL Reset: 00 <sub>H</sub>                                   | Bit Field |            |            |            | CC6        | 62VL       |            |             |             |  |

|                 | Capture/Compare Register for<br>Channel CC62 Low                     | Туре      |            |            |            | r          | h          |            |             |             |  |

| FF <sub>H</sub> | CCU6_CC62RH Reset: 00 <sub>H</sub>                                   | Bit Field |            |            |            | CC6        | 62VH       |            |             |             |  |

|                 | Capture/Compare Register for<br>Channel CC62 High                    | Туре      |            |            |            | r          | 'n         |            |             |             |  |

| RMAP =          | 0, PAGE 2                                                            | _         |            |            |            |            | _          |            |             |             |  |

| 9A <sub>H</sub> | CCU6_T12MSELL Reset: 00 <sub>H</sub>                                 | Bit Field |            | MS         | EL61       |            |            | MSE        | EL60        |             |  |

|                 | T12 Capture/Compare Mode Select<br>Register Low                      | Туре      |            | r          | w          |            |            | r          | w           |             |  |

| 9В <sub>Н</sub> | CCU6_T12MSELH Reset: 00 <sub>H</sub>                                 | Bit Field | DBYP       |            | HSYNC      |            | MSEL62     |            |             |             |  |

|                 | T12 Capture/Compare Mode Select<br>Register High                     | Туре      | rw         |            | rw         |            | rw         |            | w           |             |  |

| 9CH             | CCU6_IENL Reset: 00 <sub>H</sub>                                     | Bit Field | ENT1       | ENT1       | ENCC       | ENCC       | ENCC       | ENCC       | ENCC        | ENCC        |  |

|                 | Capture/Compare Interrupt Enable<br>Register Low                     |           | 2<br>PM    | 2<br>OM    | 62F        | 62R        | 61F        | 61R        | 60F         | 60R         |  |

|                 |                                                                      | Туре      | rw          | rw          |  |

| 9D <sub>H</sub> | CCU6_IENH Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Enable | Bit Field | EN<br>STR  | EN<br>IDLE | EN<br>WHE  | EN<br>CHE  | 0          | EN<br>TRPF | ENT1<br>3PM | ENT1<br>3CM |  |

|                 | Register High                                                        | Туре      | rw         | rw         | rw         | rw         | r          | rw         | rw          | rw          |  |

| 9E <sub>H</sub> | CCU6_INPL Reset: 40 <sub>H</sub>                                     | Bit Field | INP        | CHE        | INPCC62    |            | INPCC61    |            | INPCC60     |             |  |

|                 | Capture/Compare Interrupt Node<br>Pointer Register Low               | Туре      | r          | w          | r          | rw         |            | rw         |             | rw          |  |

| 9F <sub>H</sub> | CCU6_INPH Reset: 39 <sub>H</sub>                                     | Bit Field | (          | 0          | INPT13     |            | INPT12     |            | INPERR      |             |  |

|                 | Capture/Compare Interrupt Node<br>Pointer Register High              | Туре      |            | r          | rw         |            | rw         |            | rw          |             |  |

| A4 <sub>H</sub> | CCU6_ISSL Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Status | Bit Field | ST12<br>PM | ST12<br>OM | SCC6<br>2F | SCC6<br>2R | SCC6<br>1F | SCC6<br>1R | SCC6<br>0F  | SCC6<br>0R  |  |

|                 | Set Register Low                                                     | Туре      | w          | w          | w          | w          | w          | w          | w           | w           |  |

| A5 <sub>H</sub> | CCU6_ISSH Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Status | Bit Field | SSTR       | SIDLE      | SWHE       | SCHE       | SWH<br>C   | STRP<br>F  | ST13<br>PM  | ST13<br>CM  |  |

|                 | Set Register High                                                    | Туре      | w          | w          | w          | w          | w          | w          | w           | w           |  |

| A6 <sub>H</sub> | CCU6_PSLR Reset: 00 <sub>H</sub>                                     | Bit Field | PSL63      | 0          |            |            | P          | SL         | •           |             |  |

|                 | Passive State Level Register                                         | Туре      | rwh        | r          |            | rwh        |            |            |             |             |  |

| а7 <sub>Н</sub> | CCU6_MCMCTR Reset: 00 <sub>H</sub>                                   | Bit Field | (          | 0          | SW         | SYN        | 0          |            | SWSEL       |             |  |

|                 | Multi-Channel Mode Control Register                                  | Туре      |            | r          | r          | w          | r          |            | rw          |             |  |

| FA <sub>H</sub> | CCU6_TCTR2LReset: 00HTimer Control Register 2 Low                    | Bit Field | 0          | T13        | TED        |            | T13TEC     |            | T13<br>SSC  | T12<br>SSC  |  |

|                 |                                                                      | Туре      | r          | r          | W          |            | rw         |            | rw          | rw          |  |

## 3.7.1 Module Reset Behavior

**Table 22** lists the functions of the XC886/888 and the various reset types that affect these functions. The symbol "■" signifies that the particular function is reset to its default state.

| Module/               | Wake-Up                              | Watchdog                  | Hardware                  | Power-On                  | Brownout                  |

|-----------------------|--------------------------------------|---------------------------|---------------------------|---------------------------|---------------------------|

| Function              | Reset                                | Reset                     | Reset                     | Reset                     | Reset                     |

| CPU Core              |                                      |                           |                           |                           |                           |

| Peripherals           |                                      |                           |                           |                           |                           |

| On-Chip<br>Static RAM | Not affected,<br>Reliable            | Not affected,<br>Reliable | Not affected,<br>Reliable | Affected, un-<br>reliable | Affected, un-<br>reliable |

| Oscillator,<br>PLL    |                                      | Not affected              |                           |                           |                           |

| Port Pins             |                                      |                           |                           |                           |                           |

| EVR                   | The voltage regulator is switched on | Not affected              |                           |                           |                           |

| FLASH                 |                                      |                           |                           |                           |                           |

| NMI                   | Disabled                             | Disabled                  |                           |                           |                           |

#### Table 22Effect of Reset on Device Functions

## 3.7.2 Booting Scheme

When the XC886/888 is reset, it must identify the type of configuration with which to start the different modes once the reset sequence is complete. Thus, boot configuration information that is required for activation of special modes and conditions needs to be applied by the external world through input pins. After power-on reset or hardware reset, the pins MBC, TMS and P0.0 collectively select the different boot options. Table 23 shows the available boot options in the XC886/888.

| Iable |     |      |                                                                            |                   |

|-------|-----|------|----------------------------------------------------------------------------|-------------------|

| MBC   | TMS | P0.0 | Type of Mode                                                               | PC Start Value    |

| 1     | 0   | Х    | User Mode <sup>1)</sup> ; on-chip OSC/PLL non-bypassed                     | 0000 <sub>H</sub> |

| 0     | 0   | Х    | BSL Mode; on-chip OSC/PLL non-bypassed <sup>2)</sup>                       | 0000 <sub>H</sub> |

| 0     | 1   | 0    | OCDS Mode; on-chip OSC/PLL non-<br>bypassed                                | 0000 <sub>H</sub> |

| 1     | 1   | 0    | User (JTAG) Mode <sup>3)</sup> ; on-chip OSC/PLL non-<br>bypassed (normal) | 0000 <sub>H</sub> |

| Table 23 | XC886/888 Boot Selection |

|----------|--------------------------|

|          |                          |

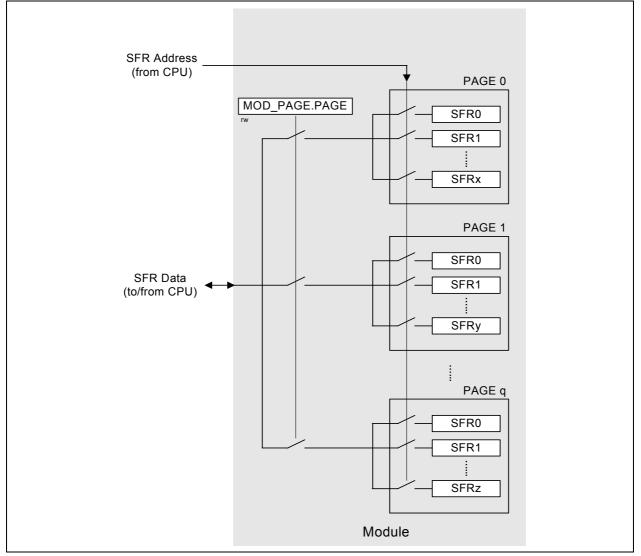

## 3.8.2 Clock Management

The CGU generates all clock signals required within the microcontroller from a single clock,  $f_{sys}$ . During normal system operation, the typical frequencies of the different modules are as follow:

- CPU clock: CCLK, SCLK = 24 MHz

- Fast clock (used by MultiCAN): FCLK = 24 or 48 MHz

- Peripheral clock: PCLK = 24 MHz

- Flash Interface clock: CCLK2 = 48 MHz and CCLK = 24 MHz

In addition, different clock frequencies can be output to pin CLKOUT (P0.0 or P0.7). The clock output frequency, which is derived from the clock output divider (bit COREL), can further be divided by 2 using toggle latch (bit TLEN is set to 1). The resulting output frequency has a 50% duty cycle. **Figure 26** shows the clock distribution of the XC886/888.

Figure 26 Clock Generation from  $f_{sys}$

## 3.9 Power Saving Modes

The power saving modes of the XC886/888 provide flexible power consumption through a combination of techniques, including:

- Stopping the CPU clock

- Stopping the clocks of individual system components

- Reducing clock speed of some peripheral components

- Power-down of the entire system with fast restart capability

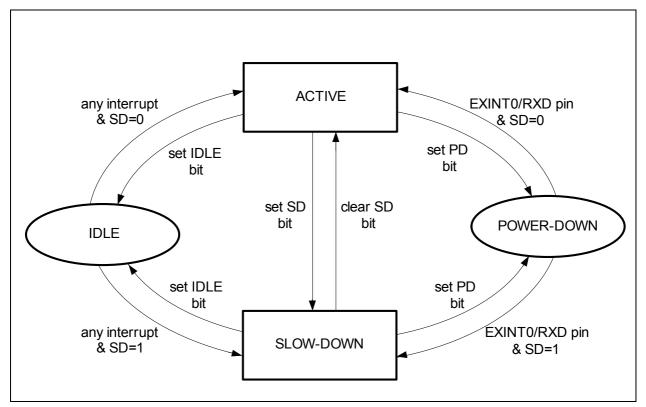

After a reset, the active mode (normal operating mode) is selected by default (see **Figure 27**) and the system runs in the main system clock frequency. From active mode, different power saving modes can be selected by software. They are:

- Idle mode

- Slow-down mode

- Power-down mode

Figure 27 Transition between Power Saving Modes

- Interrupt enabling and corresponding flag

## 3.13 UART and UART1

The XC886/888 provides two Universal Asynchronous Receiver/Transmitter (UART and UART1) modules for full-duplex asynchronous reception/transmission. Both are also receive-buffered, i.e., they can commence reception of a second byte before a previously received byte has been read from the receive register. However, if the first byte still has not been read by the time reception of the second byte is complete, one of the bytes will be lost.

#### Features

- Full-duplex asynchronous modes

- 8-bit or 9-bit data frames, LSB first

- Fixed or variable baud rate

- Receive buffered

- Multiprocessor communication

- Interrupt generation on the completion of a data transmission or reception

The UART modules can operate in the four modes shown in Table 29.

| f <sub>PCLK</sub> /2                               |

|----------------------------------------------------|

| Variable                                           |

| $f_{\rm PCLK}/32 \text{ or } f_{\rm PCLK}/64^{1)}$ |

| Variable                                           |

|                                                    |

#### Table 29UART Modes

1) For UART1 module, the baud rate is fixed at  $f_{PCLK}/64$ .

There are several ways to generate the baud rate clock for the serial port, depending on the mode in which it is operating. In mode 0, the baud rate for the transfer is fixed at  $f_{\rm PCLK}/2$ . In mode 2, the baud rate is generated internally based on the UART input clock and can be configured to either  $f_{\rm PCLK}/32$  or  $f_{\rm PCLK}/64$ . For UART1 module, only  $f_{\rm PCLK}/64$  is available. The variable baud rate is set by the underflow rate on the dedicated baud-rate generator. For UART module, the variable baud rate alternatively can be set by the overflow rate on Timer 1.

## 3.13.1 Baud-Rate Generator

Both UART modules have their own dedicated baud-rate generator, which is based on a programmable 8-bit reload value, and includes divider stages (i.e., prescaler and

However, it is important to note that the conversion error could increase due to loss of charges on the capacitors, if  $f_{ADC}$  becomes too low during slow-down mode.

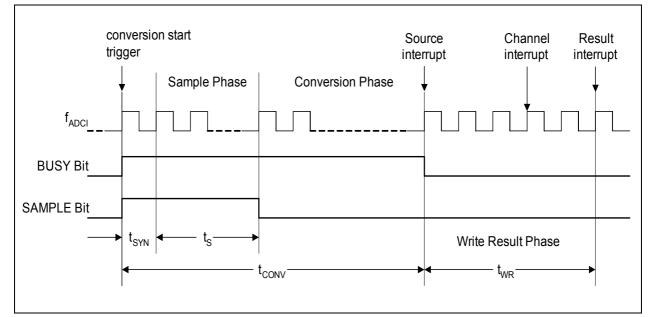

## 3.21.2 ADC Conversion Sequence

The analog-to-digital conversion procedure consists of the following phases:

- Synchronization phase (*t*<sub>SYN</sub>)

- Sample phase  $(t_S)$

- Conversion phase

- Write result phase (t<sub>WR</sub>)

Figure 36 ADC Conversion Timing

## 3.22 On-Chip Debug Support

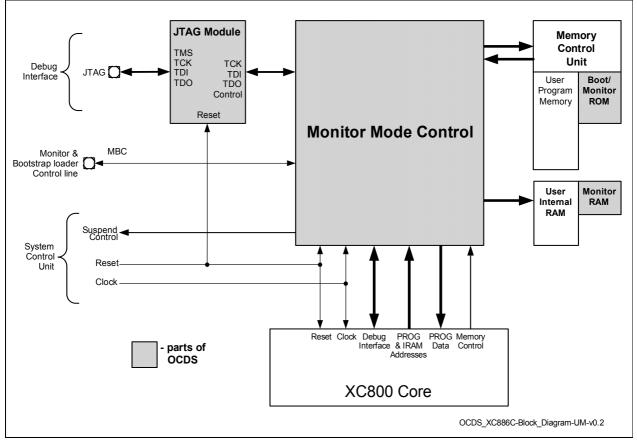

The On-Chip Debug Support (OCDS) provides the basic functionality required for the software development and debugging of XC800-based systems.

The OCDS design is based on these principles:

- Use the built-in debug functionality of the XC800 Core

- · Add a minimum of hardware overhead

- Provide support for most of the operations by a Monitor Program

- Use standard interfaces to communicate with the Host (a Debugger)

#### Features

- Set breakpoints on instruction address and on address range within the Program Memory

- Set breakpoints on internal RAM address range

- Support unlimited software breakpoints in Flash/RAM code region

- Process external breaks via JTAG and upon activating a dedicated pin

- Step through the program code

The OCDS functional blocks are shown in **Figure 37**. The Monitor Mode Control (MMC) block at the center of OCDS system brings together control signals and supports the overall functionality. The MMC communicates with the XC800 Core, primarily via the Debug Interface, and also receives reset and clock signals.

After processing memory address and control signals from the core, the MMC provides proper access to the dedicated extra-memories: a Monitor ROM (holding the code) and a Monitor RAM (for work-data and Monitor-stack).

The OCDS system is accessed through the JTAG<sup>1)</sup>, which is an interface dedicated exclusively for testing and debugging activities and is not normally used in an application. The dedicated MBC pin is used for external configuration and debugging control.

Note: All the debug functionality described here can normally be used only after XC886/888 has been started in OCDS mode.

<sup>1)</sup> The pins of the JTAG port can be assigned to either the primary port (Port 0) or either of the secondary ports (Ports 1 and 2/Port 5).

User must set the JTAG pins (TCK and TDI) as input during connection with the OCDS system.

## 3.22.1 JTAG ID Register

This is a read-only register located inside the JTAG module, and is used to recognize the device(s) connected to the JTAG interface. Its content is shifted out when INSTRUCTION register contains the IDCODE command (opcode  $04_H$ ), and the same is also true immediately after reset.

The JTAG ID register contents for the XC886/888 Flash devices are given in Table 35.

| Device Type | Device Name    | JTAG ID                |  |

|-------------|----------------|------------------------|--|

| Flash       | XC886/888*-8FF | 1012 0083 <sub>H</sub> |  |

|             | XC886/888*-6FF | 1012 5083 <sub>H</sub> |  |

| ROM         | XC886/888*-8RF | 1013 C083 <sub>H</sub> |  |

|             | XC886/888*-6RF | 1013 D083 <sub>H</sub> |  |

## Table 35JTAG ID Summary

Note: The asterisk (\*) above denotes all possible device configurations.

103

Table 37

#### **Electrical Parameters**

#### **Operating Conditions** 4.1.3

The following operating conditions must not be exceeded in order to ensure correct operation of the XC886/888. All parameters mentioned in the following table refer to these operating conditions, unless otherwise noted.

| Parameter   |  | Symbol | Limit | Values | Unit | Notes/    |  |  |

|-------------|--|--------|-------|--------|------|-----------|--|--|

|             |  |        | min.  | max.   |      | Condition |  |  |

| Distigation |  | 17     | 4 5   |        | 11   |           |  |  |

**Operating Condition Parameters**

|                                      | •                |      |       |     |                   |

|--------------------------------------|------------------|------|-------|-----|-------------------|

|                                      |                  | min. | max.  |     | Conditions        |

| Digital power supply voltage         | $V_{DDP}$        | 4.5  | 5.5   | V   | 5V Device         |

| Digital power supply voltage         | V <sub>DDP</sub> | 3.0  | 3.6   | V   | 3.3V Device       |

| Digital ground voltage               | V <sub>SS</sub>  | 0    |       | V   |                   |

| Digital core supply voltage          | V <sub>DDC</sub> | 2.3  | 2.7   | V   |                   |

| System Clock Frequency <sup>1)</sup> | $f_{\rm SYS}$    | 88.8 | 103.2 | MHz |                   |

| Ambient temperature                  | T <sub>A</sub>   | -40  | 85    | °C  | SAF-<br>XC886/888 |

|                                      |                  | -40  | 125   | °C  | SAK-<br>XC886/888 |

1)  $f_{SYS}$  is the PLL output clock. During normal operating mode, CPU clock is  $f_{SYS}$  / 4. Please refer to Figure 26 for detailed description.

#### **Electrical Parameters**

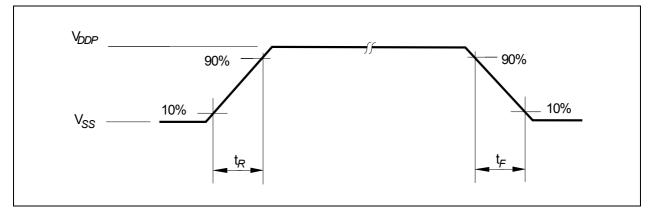

## 4.3.2 Output Rise/Fall Times

Table 45 provides the characteristics of the output rise/fall times in the XC886/888.

#### Table 45 Output Rise/Fall Times Parameters (Operating Conditions apply)

| Parameter                     | Symbol                          |      | imit<br>alues | Unit | Test Conditions          |

|-------------------------------|---------------------------------|------|---------------|------|--------------------------|

|                               |                                 | min. | max.          |      |                          |

| $V_{\rm DDP}$ = 5V Range      |                                 |      |               |      |                          |

| Rise/fall times               | t <sub>R</sub> , t <sub>F</sub> | _    | 10            | ns   | 20 pF. <sup>1)2)3)</sup> |

| V <sub>DDP</sub> = 3.3V Range | ·                               |      |               |      |                          |

| Rise/fall times               | t <sub>R</sub> , t <sub>F</sub> | _    | 10            | ns   | 20 pF. <sup>1)2)4)</sup> |

|                               |                                 | 400/ |               |      | •                        |

1) Rise/Fall time measurements are taken with 10% - 90% of pad supply.

2) Not all parameters are 100% tested, but are verified by design/characterization and test correlation.

3) Additional rise/fall time valid for  $C_{\rm L}$  = 20pF - 100pF @ 0.125 ns/pF.

4) Additional rise/fall time valid for  $C_{\rm L}$  = 20pF - 100pF @ 0.225 ns/pF.

Figure 43 Rise/Fall Times Parameters

#### **Electrical Parameters**

## 4.3.4 On-Chip Oscillator Characteristics

Table 47 provides the characteristics of the on-chip oscillator in the XC886/888.

| Table 47 | On-chip Oscillator Characteristics (Operating Conditions apply) |

|----------|-----------------------------------------------------------------|

|----------|-----------------------------------------------------------------|

| Parameter                      | Symbol           |    | Limit Values |      |      | Unit | Test Conditions                                                                                                                    |  |

|--------------------------------|------------------|----|--------------|------|------|------|------------------------------------------------------------------------------------------------------------------------------------|--|

|                                |                  |    | min.         | typ. | max. |      |                                                                                                                                    |  |

| Nominal frequency              | f <sub>nom</sub> | CC | 9.36         | 9.6  | 9.84 | MHz  | under nominal conditions <sup>1)</sup>                                                                                             |  |

| Long term frequency deviation  | Δf <sub>LT</sub> | CC | -5.0         | -    | 5.0  | %    | with respect to $f_{\text{NOM}}$ , over<br>lifetime and temperature<br>(-10°C to 125°C), for one<br>given device after<br>trimming |  |

|                                |                  |    | -6.0         | -    | 0    | %    | with respect to $f_{NOM}$ , over<br>lifetime and temperature<br>(-40°C to<br>-10°C), for one given<br>device after trimming        |  |

| Short term frequency deviation | $\Delta f_{ST}$  | CC | -1.0         | -    | 1.0  | %    | within one LIN message<br>(<10 ms 100 ms)                                                                                          |  |

1) Nominal condition:  $V_{\text{DDC}}$  = 2.5 V,  $T_{\text{A}}$  = + 25°C.

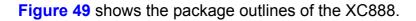

## Package and Quality Declaration

# 5 Package and Quality Declaration

Chapter 5 provides the information of the XC886/888 package and reliability section.

## 5.1 Package Parameters

Table 1 provides the thermal characteristics of the package used in XC886 and XC888.

| Parameter                        | Symbol           |    | Lin  | nit Values | Unit | Notes |

|----------------------------------|------------------|----|------|------------|------|-------|

|                                  |                  |    | Min. | Max.       |      |       |

| PG-TQFP-48 (XC886)               | 1                |    |      | L          | l    |       |

| Thermal resistance junction case | R <sub>TJC</sub> | CC | -    | 13         | K/W  | 1)2)  |

| Thermal resistance junction lead | R <sub>TJL</sub> | CC | -    | 32.5       | K/W  | 1)2)_ |

| PG-TQFP-64 (XC888)               | •                |    |      |            |      |       |

| Thermal resistance junction case | R <sub>TJC</sub> | CC | -    | 12.6       | K/W  | 1)2)  |

| Thermal resistance junction lead | $R_{TJL}$        | CC | -    | 33.4       | K/W  | 1)2)  |

#### Table 1 Thermal Characteristics of the Packages

1) The thermal resistances between the case and the ambient  $(R_{TCA})$ , the lead and the ambient  $(R_{TLA})$  are to be combined with the thermal resistances between the junction and the case  $(R_{TJC})$ , the junction and the lead  $(R_{TJL})$  given above, in order to calculate the total thermal resistance between the junction and the ambient  $(R_{TJA})$ . The thermal resistances between the case and the ambient  $(R_{TCA})$ , the lead and the ambient  $(R_{TLA})$ . The thermal resistances between the case and the ambient  $(R_{TCA})$ , the lead and the ambient  $(R_{TLA})$  depend on the external system (PCB, case) characteristics, and are under user responsibility.

The junction temperature can be calculated using the following equation:  $T_J = T_A + R_{TJA} \times P_D$ , where the  $R_{TJA}$  is the total thermal resistance between the junction and the ambient. This total junction ambient resistance  $R_{TJA}$  can be obtained from the upper four partial thermal resistances, by

a) simply adding only the two thermal resistances (junction lead and lead ambient), or

b) by taking all four resistances into account, depending on the precision needed.

2) Not all parameters are 100% tested, but are verified by design/characterization and test correlation.

#### Package and Quality Declaration

### Figure 49 PG-TQFP-64 Package Outline

### Package and Quality Declaration

## 5.3 Quality Declaration

Table 2 shows the characteristics of the quality parameters in the XC886/888.

#### Table 2Quality Parameters

| Parameter                                                             | Symbol           | Limit V | alues | Unit | Notes                                                |  |

|-----------------------------------------------------------------------|------------------|---------|-------|------|------------------------------------------------------|--|

|                                                                       |                  | Min.    | Max.  |      |                                                      |  |

| ESD susceptibility<br>according to Human Body<br>Model (HBM)          | V <sub>HBM</sub> | -       | 2000  | V    | Conforming to<br>EIA/JESD22-<br>A114-B <sup>1)</sup> |  |

| ESD susceptibility<br>according to Charged<br>Device Model (CDM) pins | V <sub>CDM</sub> | -       | 500   | V    | Conforming to JESD22-C101-C <sup>1)</sup>            |  |

1) Not all parameters are 100% tested, but are verified by design/characterization and test correlation.