Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Obsolete                                                                         |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | XC800                                                                            |

| Core Size                  | 8-Bit                                                                            |

| Speed                      | 24MHz                                                                            |

| Connectivity               | CANbus, SSI, UART/USART                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 48                                                                               |

| Program Memory Size        | 32KB (32K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 1.75K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                      |

| Data Converters            | A/D 8x10b                                                                        |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-LQFP                                                                          |

| Supplier Device Package    | PG-TQFP-64                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/saf-xc888c-8ffi-5v-ac |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Summary of Features

Features: (continued)

- Power-on reset generation

- Brownout detection for core logic supply

- On-chip OSC and PLL for clock generation

- PLL loss-of-lock detection

- Power saving modes

- slow-down mode

- idle mode

- power-down mode with wake-up capability via RXD or EXINT0

- clock gating control to each peripheral

- Programmable 16-bit Watchdog Timer (WDT)

- Six ports

- Up to 48 pins as digital I/O

- 8 pins as digital/analog input

- 8-channel, 10-bit ADC

- Four 16-bit timers

- Timer 0 and Timer 1 (T0 and T1)

- Timer 2 and Timer 21 (T2 and T21)

- Multiplication/Division Unit for arithmetic operations (MDU)

- Software libraries to support floating point and MDU calculations

- CORDIC Coprocessor for computation of trigonometric, hyperbolic and linear functions

- MultiCAN with 2 nodes, 32 message objects

- Capture/compare unit for PWM signal generation (CCU6)

- Two full-duplex serial interfaces (UART and UART1)

- Synchronous serial channel (SSC)

- On-chip debug support

- 1 Kbyte of monitor ROM (part of the 12-Kbyte Boot ROM)

- 64 bytes of monitor RAM

- Packages:

- PG-TQFP-48

- PG-TQFP-64

- Temperature range *T*<sub>A</sub>:

- SAF (-40 to 85 °C)

- SAK (-40 to 125 °C)

#### **General Device Information**

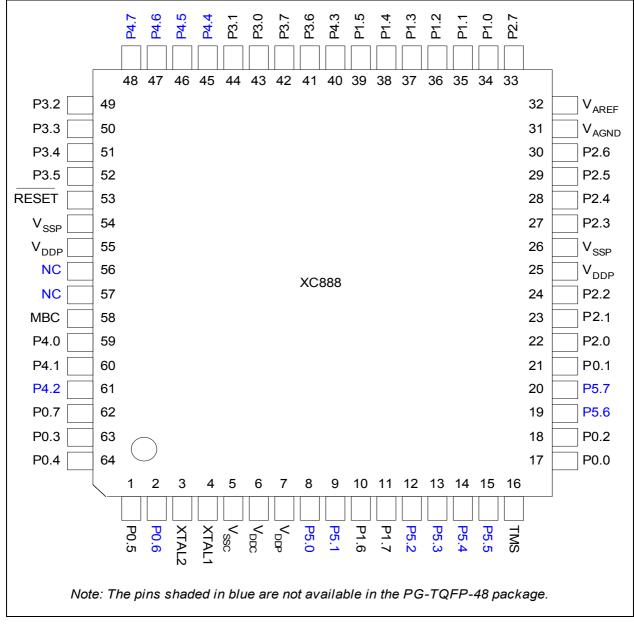

Figure 5 XC888 Pin Configuration, PG-TQFP-64 Package (top view)

### **General Device Information**

# 2.4 Pin Definitions and Functions

The functions and default states of the XC886/888 external pins are provided in Table 3.

| Symbol | Pin Number<br>(TQFP-48/64) | Туре | Reset<br>State | Function                                                                                                                                                                                        |                                                                                                                                                                                                      |  |

|--------|----------------------------|------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| P0     |                            | I/O  |                | <b>Port 0</b><br>Port 0 is an 8-bit bidirectional general purpose<br>I/O port. It can be used as alternate functions<br>for the JTAG, CCU6, UART, UART1, Timer 2<br>Timer 21, MultiCAN and SSC. |                                                                                                                                                                                                      |  |

| P0.0   | 11/17                      |      | Hi-Z           | TCK_0<br>T12HR_1<br>CC61_1<br>CLKOUT_0<br>RXDO_1                                                                                                                                                | JTAG Clock Input<br>CCU6 Timer 12 Hardware Run<br>Input<br>Input/Output of<br>Capture/Compare channel 1<br>Clock Output<br>UART Transmit Data Output                                                 |  |

| P0.1   | 13/21                      |      | Hi-Z           | TDI_0<br>T13HR_1<br>RXD_1<br>RXDC1_0<br>COUT61_1<br>EXF2_1                                                                                                                                      | JTAG Serial Data Input<br>CCU6 Timer 13 Hardware Run<br>Input<br>UART Receive Data Input<br>MultiCAN Node 1 Receiver Input<br>Output of Capture/Compare<br>channel 1<br>Timer 2 External Flag Output |  |

| P0.2   | 12/18                      |      | PU             | CTRAP_2<br>TDO_0<br>TXD_1<br>TXDC1_0                                                                                                                                                            | CCU6 Trap Input<br>JTAG Serial Data Output<br>UART Transmit Data<br>Output/Clock Output<br>MultiCAN Node 1 Transmitter<br>Output                                                                     |  |

| P0.3   | 48/63                      |      | Hi-Z           | SCK_1<br>COUT63_1<br>RXDO1_0                                                                                                                                                                    | SSC Clock Input/Output<br>Output of Capture/Compare<br>channel 3<br>UART1 Transmit Data Output                                                                                                       |  |

Table 3

Pin Definitions and Functions

### **General Device Information**

| Table 0 | T III Belli                |      |                |                                                     | u)                                                                                                                                                                                       |

|---------|----------------------------|------|----------------|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol  | Pin Number<br>(TQFP-48/64) | Туре | Reset<br>State | Function                                            |                                                                                                                                                                                          |

| P0.4    | 1/64                       |      | Hi-Z           | MTSR_1                                              | SSC Master Transmit Output/<br>Slave Receive Input                                                                                                                                       |

|         |                            |      |                | CC62_1                                              | Input/Output of<br>Capture/Compare channel 2                                                                                                                                             |

|         |                            |      |                | TXD1_0                                              | UART1 Transmit Data<br>Output/Clock Output                                                                                                                                               |

| P0.5    | 2/1                        |      | Hi-Z           | MRST_1<br>EXINT0_0<br>T2EX1_1<br>RXD1_0<br>COUT62_1 | SSC Master Receive Input/Slave<br>Transmit Output<br>External Interrupt Input 0<br>Timer 21 External Trigger Input<br>UART1 Receive Data Input<br>Output of Capture/Compare<br>channel 2 |

| P0.6    | -/2                        |      | PU             | GPIO                                                |                                                                                                                                                                                          |

| P0.7    | 47/62                      |      | PU             | CLKOUT_1                                            | Clock Output                                                                                                                                                                             |

#### Pin Definitions and Functions (cont'd) Table 3

# XC886/888CLM

### **General Device Information**

### Table 3Pin Definitions and Functions (cont'd)

| Symbol | Pin Number<br>(TQFP-48/64) | Туре | Reset<br>State | Function                     |                                                                           |

|--------|----------------------------|------|----------------|------------------------------|---------------------------------------------------------------------------|

| P1.6   | 8/10                       |      | PU             | CCPOS1_1<br>T12HR_0          | •                                                                         |

|        |                            |      |                | EXINT6_0<br>RXDC0_2<br>T21_1 | • •                                                                       |

| P1.7   | 9/11                       |      | PU             | CCPOS2_1<br>T13HR_0<br>T2 1  | CCU6 Hall Input 2<br>CCU6 Timer 13 Hardware Run<br>Input<br>Timer 2 Input |

|        |                            |      |                | TXDC0_2                      | •                                                                         |

|        |                            |      |                |                              | .6 can be used as a software chip<br>t for the SSC.                       |

Table 3

#### **General Device Information**

#### Pin Definitions and Functions (cont'd) Type Reset Function Pin Number Symbol (TQFP-48/64) State **P2** I Port 2 Port 2 is an 8-bit general purpose input-only port. It can be used as alternate functions for

|       |       |      | the digital inputs of the JTAG and CCU6. It is also used as the analog inputs for the ADC. |                                                                                        |  |

|-------|-------|------|--------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--|

| P2.0  | 14/22 | Hi-Z | CCPOS0_0<br>EXINT1_0<br>T12HR_2                                                            | CCU6 Hall Input 0<br>External Interrupt Input 1<br>CCU6 Timer 12 Hardware Run<br>Input |  |

|       |       |      | TCK_1                                                                                      | JTAG Clock Input                                                                       |  |

|       |       |      | CC61_3                                                                                     | Input of Capture/Compare<br>channel 1                                                  |  |

|       |       |      | AN0                                                                                        | Analog Input 0                                                                         |  |

| P2.1  | 15/23 | Hi-Z | CCPOS1_0<br>EXINT2_0<br>T13HR_2                                                            | CCU6 Hall Input 1<br>External Interrupt Input 2<br>CCU6 Timer 13 Hardware Run<br>Input |  |

|       |       |      | TDI_1<br>CC62_3<br>AN1                                                                     | JTAG Serial Data Input<br>Input of Capture/Compare<br>channel 2<br>Analog Input 1      |  |

| P2.2  | 16/24 | Hi-Z | CCPOS2_0                                                                                   | CCU6 Hall Input 2                                                                      |  |

| 1 2.2 | 10/24 |      | CTRAP_1                                                                                    | CCU6 Trap Input                                                                        |  |

|       |       |      | CC60_3                                                                                     | Input of Capture/Compare<br>channel 0                                                  |  |

|       |       |      | AN2                                                                                        | Analog Input 2                                                                         |  |

| P2.3  | 19/27 | Hi-Z | AN3                                                                                        | Analog Input 3                                                                         |  |

| P2.4  | 20/28 | Hi-Z | AN4                                                                                        | Analog Input 4                                                                         |  |

| P2.5  | 21/29 | Hi-Z | AN5                                                                                        | Analog Input 5                                                                         |  |

| P2.6  | 22/30 | Hi-Z | AN6                                                                                        | Analog Input 6                                                                         |  |

| P2.7  | 25/33 | Hi-Z | AN7                                                                                        | Analog Input 7                                                                         |  |

code or data. Therefore, even though the ROM device contains either a 24-Kbyte or 32-Kbyte ROM, the maximum size of code that can be placed in the ROM is the given size less four bytes.

### 3.2.1 Memory Protection Strategy

The XC886/888 memory protection strategy includes:

- Read-out protection: The user is able to protect the contents in the Flash (for Flash devices) and ROM (for ROM devices) memory from being read

- Flash protection is enabled by programming a valid password (8-bit non-zero value) via BSL mode 6.

- ROM protection is fixed with the ROM mask and is always enabled.

- Flash program and erase protection: This feature is available only for Flash devices.

### 3.2.1.1 Flash Memory Protection

As long as a valid password is available, all external access to the device, including the Flash, will be blocked.

For additional security, the Flash hardware protection can be enabled to implement a second layer of read-out protection, as well as to enable program and erase protection.

Flash hardware protection is available only for Flash devices and comes in two modes:

- Mode 0: Only the P-Flash is protected; the D-Flash is unprotected

- Mode 1: Both the P-Flash and D-Flash are protected

The selection of each protection mode and the restrictions imposed are summarized in **Table 4**.

| Flash Protection                      | Without hardware protection             | With hardware prote                          | e protection                                    |  |  |  |  |

|---------------------------------------|-----------------------------------------|----------------------------------------------|-------------------------------------------------|--|--|--|--|

| Hardware<br>Protection Mode           | -                                       | 0                                            | 1                                               |  |  |  |  |

| Activation                            | Program a valid password via BSL mode 6 |                                              |                                                 |  |  |  |  |

| Selection                             | Bit 4 of password = 0                   | Bit 4 of password = 1<br>MSB of password = 0 | Bit 4 of password = 1<br>MSB of password = 1    |  |  |  |  |

| P-Flash<br>contents can be<br>read by | Read instructions in any program memory | Read instructions in the P-Flash             | Read instructions in the P-Flash or D-<br>Flash |  |  |  |  |

| External access<br>to P-Flash         | Not possible                            | Not possible                                 | Not possible                                    |  |  |  |  |

#### Table 4Flash Protection Modes

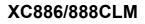

#### Figure 9 Address Extension by Paging

In order to access a register located in a page different from the actual one, the current page must be exited. This is done by reprogramming the bit field PAGE in the page register. Only then can the desired access be performed.

If an interrupt routine is initiated between the page register access and the module register access, and the interrupt needs to access a register located in another page, the current page setting can be saved, the new one programmed and the old page setting restored. This is possible with the storage fields STx (x = 0 - 3) for the save and restore action of the current page setting. By indicating which storage bit field should be used in parallel with the new page value, a single write operation can:

• Save the contents of PAGE in STx before overwriting with the new value (this is done in the beginning of the interrupt routine to save the current page setting and program the new page number); or

| Addr            | Register Name                                                     | Bit       | 7           | 6           | 5           | 4           | 3    | 2    | 1         | 0         |

|-----------------|-------------------------------------------------------------------|-----------|-------------|-------------|-------------|-------------|------|------|-----------|-----------|

| A8 <sub>H</sub> | IEN0 Reset: 00 <sub>H</sub>                                       | Bit Field | EA          | 0           | ET2         | ES          | ET1  | EX1  | ET0       | EX0       |

|                 | Interrupt Enable Register 0                                       | Туре      | rw          | r           | rw          | rw          | rw   | rw   | rw        | rw        |

| B8 <sub>H</sub> | IP Reset: 00 <sub>H</sub>                                         | Bit Field | (           | )           | PT2         | PS          | PT1  | PX1  | PT0       | PX0       |

|                 | Interrupt Priority Register                                       | Туре      |             | r           | rw          | rw          | rw   | rw   | rw        | rw        |

| в9 <sub>Н</sub> | IPH Reset: 00 <sub>H</sub>                                        | Bit Field | (           | )           | PT2H        | PSH         | PT1H | PX1H | PT0H      | PX0H      |

|                 | Interrupt Priority High Register                                  | Туре      |             | r           | rw          | rw          | rw   | rw   | rw        | rw        |

| D0 <sub>H</sub> | PSW Reset: 00 <sub>H</sub>                                        | Bit Field | CY          | AC          | F0          | RS1         | RS0  | OV   | F1        | Р         |

|                 | Program Status Word Register                                      | Туре      | rwh         | rwh         | rw          | rw          | rw   | rwh  | rw        | rh        |

| E0 <sub>H</sub> | ACC Reset: 00 <sub>H</sub><br>Accumulator Register                | Bit Field | ACC7        | ACC6        | ACC5        | ACC4        | ACC3 | ACC2 | ACC1      | ACC0      |

|                 |                                                                   | Туре      | rw          | rw          | rw          | rw          | rw   | rw   | rw        | rw        |

| E8 <sub>H</sub> | IEN1 Reset: 00 <sub>H</sub><br>Interrupt Enable Register 1        | Bit Field | ECCIP<br>3  | ECCIP<br>2  | ECCIP<br>1  | ECCIP<br>0  | EXM  | EX2  | ESSC      | EADC      |

|                 |                                                                   | Туре      | rw          | rw          | rw          | rw          | rw   | rw   | rw        | rw        |

| F0 <sub>H</sub> | B Reset: 00 <sub>H</sub>                                          | Bit Field | B7          | B6          | B5          | B4          | B3   | B2   | B1        | B0        |

|                 | B Register                                                        | Туре      | rw          | rw          | rw          | rw          | rw   | rw   | rw        | rw        |

| F8 <sub>H</sub> | IP1 Reset: 00 <sub>H</sub><br>Interrupt Priority 1 Register       | Bit Field | PCCIP<br>3  | PCCIP<br>2  | PCCIP<br>1  | PCCIP<br>0  | PXM  | PX2  | PSSC      | PADC      |

|                 |                                                                   | Туре      | rw          | rw          | rw          | rw          | rw   | rw   | rw        | rw        |

| F9 <sub>H</sub> | IPH1 Reset: 00 <sub>H</sub><br>Interrupt Priority 1 High Register | Bit Field | PCCIP<br>3H | PCCIP<br>2H | PCCIP<br>1H | PCCIP<br>0H | PXMH | PX2H | PSSC<br>H | PADC<br>H |

|                 |                                                                   | Туре      | rw          | rw          | rw          | rw          | rw   | rw   | rw        | rw        |

#### Table 5CPU Register Overview (cont'd)

# 3.2.4.2 MDU Registers

The MDU SFRs can be accessed in the mapped memory area (RMAP = 1).

#### Table 6MDU Register Overview

| Addr            | Register Name                                         | Bit       | 7    | 6  | 5    | 4         | 3      | 2   | 1    | 0    |

|-----------------|-------------------------------------------------------|-----------|------|----|------|-----------|--------|-----|------|------|

| RMAP =          | = 1                                                   | •         |      | •  | •    | •         | •      | •   | •    |      |

| в0 <sub>Н</sub> | 0 <sub>H</sub> MDUSTAT Reset: 00 <sub>H</sub>         |           |      |    | 0    |           |        | BSY | IERR | IRDY |

|                 | MDU Status Register                                   | Туре      |      |    | r    |           |        | rh  | rwh  | rwh  |

| в1 <sub>Н</sub> | MDUCON Reset: 00 <sub>H</sub><br>MDU Control Register | Bit Field | IE   | IR | RSEL | STAR<br>T | OPCODE |     |      |      |

|                 |                                                       |           | rw   | rw | rw   | rwh       |        | r   | w    |      |

| B2 <sub>H</sub> | MD0 Reset: 00 <sub>H</sub>                            | Bit Field | DATA |    |      |           |        |     |      |      |

|                 | MDU Operand Register 0                                | Туре      | rw   |    |      |           |        |     |      |      |

| B2 <sub>H</sub> | MR0 Reset: 00 <sub>H</sub>                            | Bit Field | DATA |    |      |           |        |     |      |      |

|                 | MDU Result Register 0                                 |           | rh   |    |      |           |        |     |      |      |

| вз <sub>Н</sub> | B3 <sub>H</sub> MD1 Reset: 00 <sub>H</sub>            | Bit Field |      |    |      | DA        | TA     |     |      |      |

|                 | MDU Operand Register 1                                | Туре      |      |    |      | r         | W      |     |      |      |

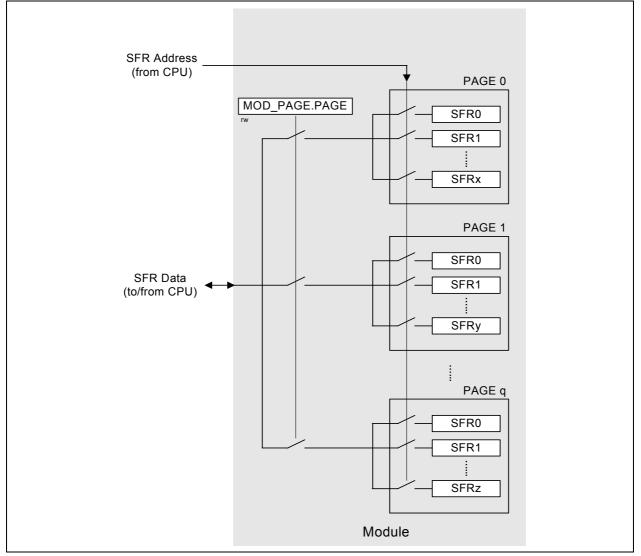

# 3.3.3 Flash Programming Width

For the P-Flash banks, a programmed wordline (WL) must be erased before it can be reprogrammed as the Flash cells can only withstand one gate disturb. This means that the entire sector containing the WL must be erased since it is impossible to erase a single WL.

For the D-Flash bank, the same WL can be programmed twice before erasing is required as the Flash cells are able to withstand two gate disturbs. This means if the number of data bytes that needs to be written is smaller than the 32-byte minimum programming width, the user can opt to program this number of data bytes (x; where x can be any integer from 1 to 31) first and program the remaining bytes (32 - x) later. Hence, it is possible to program the same WL, for example, with 16 bytes of data two times (see **Figure 12**)

#### Figure 12 D-Flash Programming

Note: When programming a D-Flash WL the second time, the previously programmed Flash memory cells (whether 0s or 1s) should be reprogrammed with 0s to retain its original contents and to prevent "over-programming".

### XC886/888CLM

### **Functional Description**

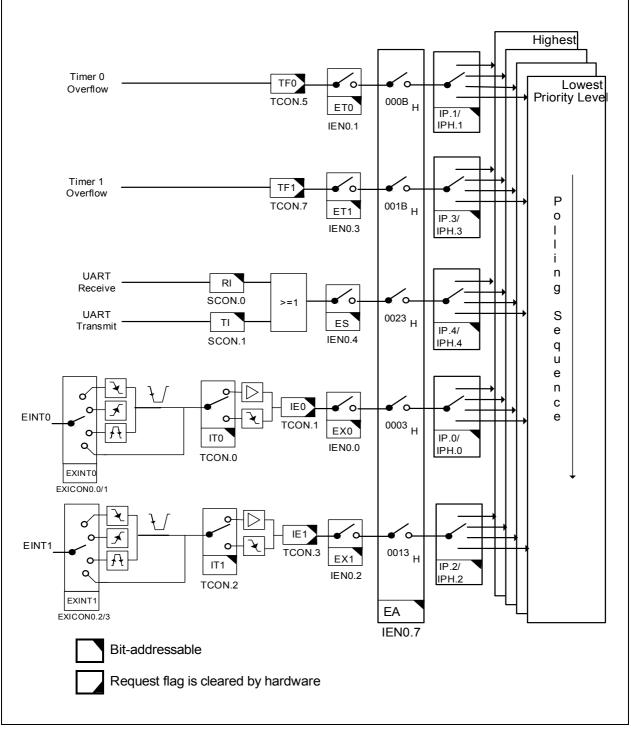

Figure 14 Interrupt Request Sources (Part 1)

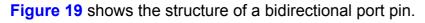

Figure 19 General Structure of Bidirectional Port

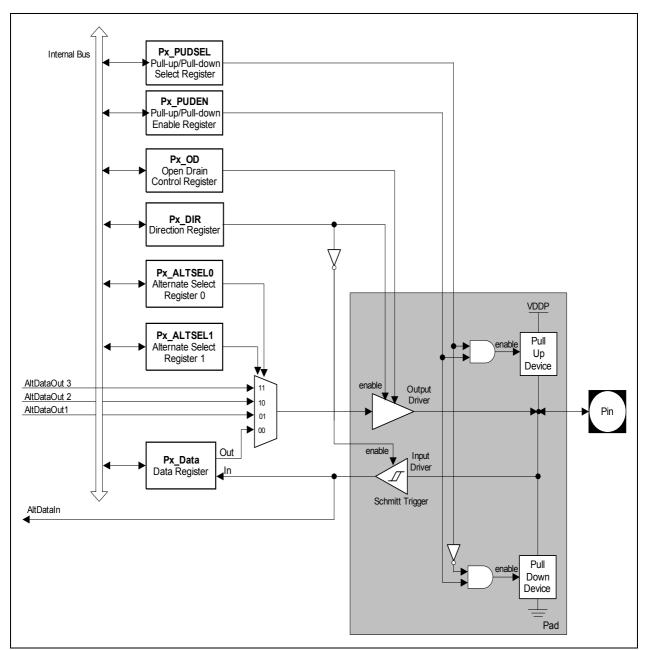

### Figure 23 $V_{\text{DDP}}$ , $V_{\text{DDC}}$ and $V_{\text{RESET}}$ during Power-on Reset

The second type of reset in XC886/888 is the hardware reset. This reset function can be used during normal operation or when the chip is in power-down mode. A reset input pin RESET is provided for the hardware reset.

The Watchdog Timer (WDT) module is also capable of resetting the device if it detects a malfunction in the system.

Another type of reset that needs to be detected is a reset while the device is in power-down mode (wake-up reset). While the contents of the static RAM are undefined after a power-on reset, they are well defined after a wake-up reset from power-down mode.

The following formulas calculate the final baud rate without and with the fractional divider respectively:

baud rate =

$$\frac{f_{PCLK}}{16 \times 2^{BRPRE} \times (BR VALUE + 1)}$$

where  $2^{BRPRE} \times (BR_VALUE + 1) > 1$

(3.5)

baud rate =  $\frac{f_{PCLK}}{16 \times 2^{BRPRE} \times (BR_VALUE + 1)} \times \frac{STEP}{256}$

(3.6)

The maximum baud rate that can be generated is limited to  $f_{\text{PCLK}}/32$ . Hence, for a module clock of 24 MHz, the maximum achievable baud rate is 0.75 MBaud.

Standard LIN protocol can support a maximum baud rate of 20 kHz, the baud rate accuracy is not critical and the fractional divider can be disabled. Only the prescaler is used for auto baud rate calculation. For LIN fast mode, which supports the baud rate of 20 kHz to 115.2 kHz, the higher baud rates require the use of the fractional divider for greater accuracy.

**Table 30** lists the various commonly used baud rates with their corresponding parameter settings and deviation errors. The fractional divider is disabled and a module clock of 24 MHz is used.

| Baud rate  | Prescaling Factor<br>(2BRPRE) | Reload Value<br>(BR_VALUE + 1) | Deviation Error |  |  |  |  |

|------------|-------------------------------|--------------------------------|-----------------|--|--|--|--|

| 19.2 kBaud | 1 (BRPRE=000 <sub>B</sub> )   | 78 (4E <sub>H</sub> )          | 0.17 %          |  |  |  |  |

| 9600 Baud  | 1 (BRPRE=000 <sub>B</sub> )   | 156 (9C <sub>H</sub> )         | 0.17 %          |  |  |  |  |

| 4800 Baud  | 2 (BRPRE=001 <sub>B</sub> )   | 156 (9C <sub>H</sub> )         | 0.17 %          |  |  |  |  |

| 2400 Baud  | 4 (BRPRE=010 <sub>B</sub> )   | 156 (9С <sub>Н</sub> )         | 0.17 %          |  |  |  |  |

Table 30

Typical Baud rates for UART with Fractional Divider disabled

The fractional divider allows baud rates of higher accuracy (lower deviation error) to be generated. **Table 31** lists the resulting deviation errors from generating a baud rate of 115.2 kHz, using different module clock frequencies. The fractional divider is enabled (fractional divider mode) and the corresponding parameter settings are shown.

# 3.16 High-Speed Synchronous Serial Interface

The High-Speed Synchronous Serial Interface (SSC) supports full-duplex and half-duplex synchronous communication. The serial clock signal can be generated by the SSC internally (master mode), using its own 16-bit baud-rate generator, or can be received from an external master (slave mode). Data width, shift direction, clock polarity and phase are programmable. This allows communication with SPI-compatible devices or devices using other synchronous serial interfaces.

#### Features

- Master and slave mode operation

- Full-duplex or half-duplex operation

- Transmit and receive buffered

- Flexible data format

- Programmable number of data bits: 2 to 8 bits

- Programmable shift direction: LSB or MSB shift first

- Programmable clock polarity: idle low or high state for the shift clock

- Programmable clock/data phase: data shift with leading or trailing edge of the shift clock

- Variable baud rate

- Compatible with Serial Peripheral Interface (SPI)

- Interrupt generation

- On a transmitter empty condition

- On a receiver full condition

- On an error condition (receive, phase, baud rate, transmit error)

Data is transmitted or received on lines TXD and RXD, which are normally connected to the pins MTSR (Master Transmit/Slave Receive) and MRST (Master Receive/Slave Transmit). The clock signal is output via line MS\_CLK (Master Serial Shift Clock) or input via line SS\_CLK (Slave Serial Shift Clock). Both lines are normally connected to the pin SCLK. Transmission and reception of data are double-buffered.

Figure 32 shows the block diagram of the SSC.

### 3.17 Timer 0 and Timer 1

Timer 0 and Timer 1 can function as both timers or counters. When functioning as a timer, Timer 0 and Timer 1 are incremented every machine cycle, i.e. every 2 input clocks (or 2 PCLKs). When functioning as a counter, Timer 0 and Timer 1 are incremented in response to a 1-to-0 transition (falling edge) at their respective external input pins, T0 or T1.

Timer 0 and 1 are fully compatible and can be configured in four different operating modes for use in a variety of applications, see **Table 32**. In modes 0, 1 and 2, the two timers operate independently, but in mode 3, their functions are specialized.

| Mode | Operation                                                                                                                                                                  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | <b>13-bit timer</b><br>The timer is essentially an 8-bit counter with a divide-by-32 prescaler.<br>This mode is included solely for compatibility with Intel 8048 devices. |

| 1    | <b>16-bit timer</b><br>The timer registers, TLx and THx, are concatenated to form a 16-bit counter.                                                                        |

| 2    | <b>8-bit timer with auto-reload</b><br>The timer register TLx is reloaded with a user-defined 8-bit value in THx upon overflow.                                            |

| 3    | Timer 0 operates as two 8-bit timersThe timer registers, TL0 and TH0, operate as two separate 8-bit counters.Timer 1 is halted and retains its count even if enabled.      |

#### Table 32Timer 0 and Timer 1 Modes

## 3.19 Capture/Compare Unit 6

The Capture/Compare Unit 6 (CCU6) provides two independent timers (T12, T13), which can be used for Pulse Width Modulation (PWM) generation, especially for AC-motor control. The CCU6 also supports special control modes for block commutation and multi-phase machines.

The timer T12 can function in capture and/or compare mode for its three channels. The timer T13 can work in compare mode only.

The multi-channel control unit generates output patterns, which can be modulated by T12 and/or T13. The modulation sources can be selected and combined for the signal modulation.

#### Timer T12 Features

- Three capture/compare channels, each channel can be used either as a capture or as a compare channel

- Supports generation of a three-phase PWM (six outputs, individual signals for highside and lowside switches)

- 16-bit resolution, maximum count frequency = peripheral clock frequency

- Dead-time control for each channel to avoid short-circuits in the power stage

- Concurrent update of the required T12/13 registers

- · Generation of center-aligned and edge-aligned PWM

- Supports single-shot mode

- Supports many interrupt request sources

- Hysteresis-like control mode

#### **Timer T13 Features**

- One independent compare channel with one output

- 16-bit resolution, maximum count frequency = peripheral clock frequency

- Can be synchronized to T12

- Interrupt generation at period-match and compare-match

- Supports single-shot mode

#### Additional Features

- Implements block commutation for Brushless DC-drives

- Position detection via Hall-sensor pattern

- Automatic rotational speed measurement for block commutation

- Integrated error handling

- Fast emergency stop without CPU load via external signal (CTRAP)

- · Control modes for multi-channel AC-drives

- Output levels can be selected and adapted to the power stage

The block diagram of the CCU6 module is shown in **Figure 33**.

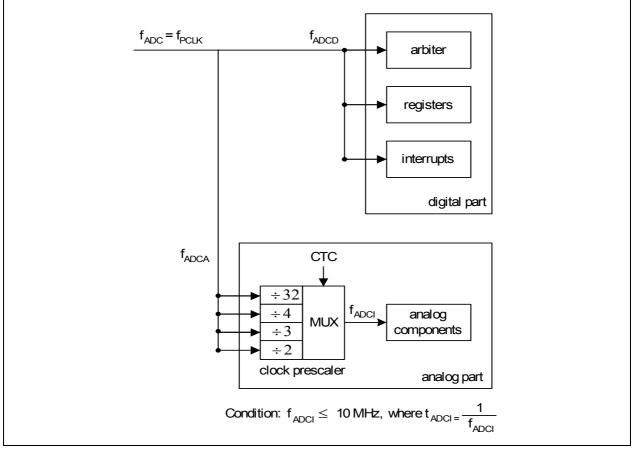

GLOBCTR. A prescaling ratio of 32 can be selected when the maximum performance of the ADC is not required.

#### Figure 35 ADC Clocking Scheme

For module clock  $f_{ADC}$  = 24 MHz, the analog clock  $f_{ADCI}$  frequency can be selected as shown in **Table 34**.

| Table 34 | f <sub>ADCI</sub> Frequency Selection |

|----------|---------------------------------------|

|----------|---------------------------------------|

| Module Clock $f_{ADC}$ | СТС                       | Prescaling Ratio | Analog Clock $f_{ADCI}$ |

|------------------------|---------------------------|------------------|-------------------------|

| 24 MHz                 | 00 <sub>B</sub>           | ÷ 2              | 12 MHz (N.A)            |

|                        | 01 <sub>B</sub>           | ÷ 3              | 8 MHz                   |

|                        | 10 <sub>B</sub>           | ÷ 4              | 6 MHz                   |

|                        | 11 <sub>B</sub> (default) | ÷ 32             | 750 kHz                 |

As  $f_{\rm ADCI}$  cannot exceed 10 MHz, bit field CTC should not be set to  $00_{\rm B}$  when  $f_{\rm ADC}$  is 24 MHz. During slow-down mode where  $f_{\rm ADC}$  may be reduced to 12 MHz, 6 MHz etc., CTC can be set to  $00_{\rm B}$  as long as the divided analog clock  $f_{\rm ADCI}$  does not exceed 10 MHz.

### Table 36Chip Identification Number (cont'd)

| Product Variant | Chip Identification Number |         |         |  |

|-----------------|----------------------------|---------|---------|--|

|                 | AA-Step                    | AB-Step | AC-Step |  |

| XC888CM-6RFA 5V | 22891503 <sub>H</sub>      | -       | -       |  |

| XC886C-6RFA 5V  | 22891542 <sub>H</sub>      | -       | -       |  |

| XC888C-6RFA 5V  | 22891543 <sub>H</sub>      | -       | -       |  |

| XC886-6RFA 5V   | 22891562 <sub>H</sub>      | -       | -       |  |

| XC888-6RFA 5V   | 22891563 <sub>H</sub>      | -       | -       |  |

#### **Electrical Parameters**

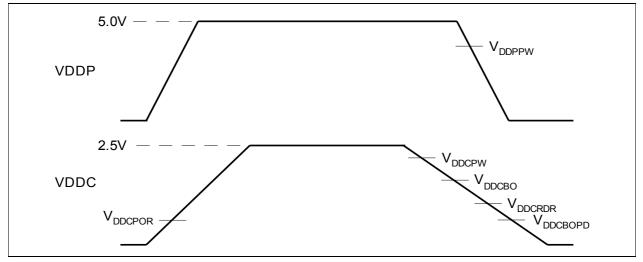

### 4.2.2 Supply Threshold Characteristics

Table 39 provides the characteristics of the supply threshold in the XC886/888.

Figure 38 Supply Threshold Parameters

| Table 39 | Supply Threshold Parameters | (Operating Conditions apply) |

|----------|-----------------------------|------------------------------|

|----------|-----------------------------|------------------------------|

| Parameters                                                         | Symbol               |    | Limit Values |          |      | Unit |

|--------------------------------------------------------------------|----------------------|----|--------------|----------|------|------|

|                                                                    |                      |    | min.         | in. typ. | max. |      |

| $V_{\rm DDC}$ prewarning voltage <sup>1)</sup>                     | V <sub>DDCPW</sub>   | CC | 2.2          | 2.3      | 2.4  | V    |

| $V_{\text{DDC}}$ brownout voltage in active mode <sup>1)</sup>     | V <sub>DDCBO</sub>   | СС | 2.0          | 2.1      | 2.2  | V    |

| RAM data retention voltage                                         | V <sub>DDCRDR</sub>  | CC | 0.9          | 1.0      | 1.1  | V    |

| $V_{\text{DDC}}$ brownout voltage in power-down mode <sup>2)</sup> | V <sub>DDCBOPD</sub> | СС | 1.3          | 1.5      | 1.7  | V    |

| $V_{\rm DDP}$ prewarning voltage <sup>3)</sup>                     | V <sub>DDPPW</sub>   | CC | 3.4          | 4.0      | 4.6  | V    |

| Power-on reset voltage <sup>2)4)</sup>                             | VDDCPOR              | CC | 1.3          | 1.5      | 1.7  | V    |

1) Detection is disabled in power-down mode.

2) Detection is enabled in both active and power-down mode.

Detection is enabled for external power supply of 5.0V. Detection must be disabled for external power supply of 3.3V.

4) The reset of EVR is extended by 300 µs typically after the VDDC reaches the power-on reset voltage.