Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                    |

|----------------------------|------------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                           |

| Core Processor             | XC800                                                                              |

| Core Size                  | 8-Bit                                                                              |

| Speed                      | 24MHz                                                                              |

| Connectivity               | CANbus, LINbus, SSI, UART/USART                                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                              |

| Number of I/O              | 48                                                                                 |

| Program Memory Size        | 32KB (32K x 8)                                                                     |

| Program Memory Type        | FLASH                                                                              |

| EEPROM Size                | -                                                                                  |

| RAM Size                   | 1.75K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                        |

| Data Converters            | A/D 8x10b                                                                          |

| Oscillator Type            | Internal                                                                           |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                  |

| Mounting Type              | Surface Mount                                                                      |

| Package / Case             | 64-LQFP                                                                            |

| Supplier Device Package    | PG-TQFP-64                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/saf-xc888clm-8ffa-5v-ac |

|                            |                                                                                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **General Device Information**

# 2.2 Logic Symbol

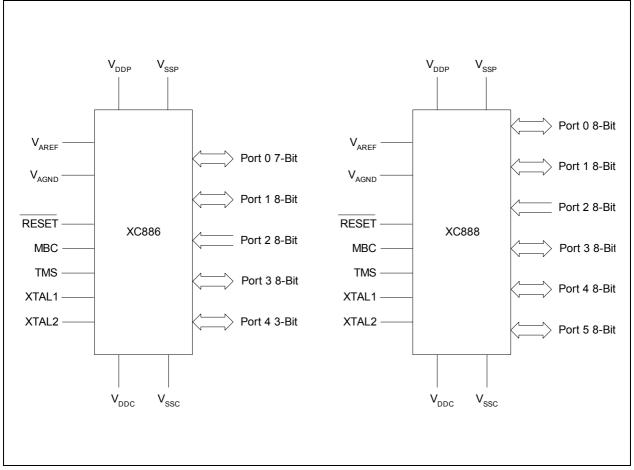

The logic symbols of the XC886/888 are shown in Figure 3.

Figure 3 XC886/888 Logic Symbol

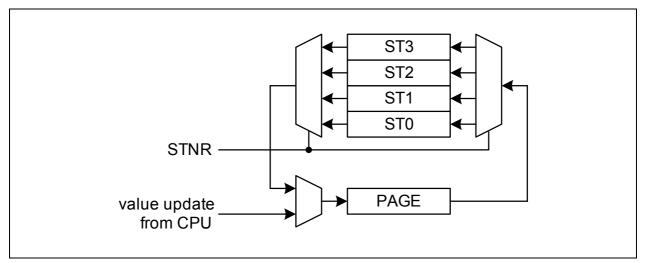

Overwrite the contents of PAGE with the contents of STx, ignoring the value written to the bit positions of PAGE

(this is done at the end of the interrupt routine to restore the previous page setting before the interrupt occurred)

## Figure 10 Storage Elements for Paging

With this mechanism, a certain number of interrupt routines (or other routines) can perform page changes without reading and storing the previously used page information. The use of only write operations makes the system simpler and faster. Consequently, this mechanism significantly improves the performance of short interrupt routines.

The XC886/888 supports local address extension for:

- Parallel Ports

- Analog-to-Digital Converter (ADC)

- Capture/Compare Unit 6 (CCU6)

- System Control Registers

| Field | Bits  | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------|-------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OP    | [7:6] | w    | <ul> <li>Operation         <ul> <li>Manual page mode. The value of STNR is ignored and PAGE is directly written.</li> <li>New page programming with automatic page saving. The value written to the bit positions of PAGE is stored. In parallel, the previous contents of PAGE are saved in the storage bit field STx indicated by STNR.</li> </ul> </li> <li>Automatic restore page action. The value written to the bit positions of PAGE is ignored and instead, PAGE is overwritten by the contents of the storage bit field STx indicated by STNR.</li> </ul> |

| 0     | 3     | r    | <b>Reserved</b><br>Returns 0 if read; should be written with 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

# 3.2.3 Bit Protection Scheme

The bit protection scheme prevents direct software writing of selected bits (i.e., protected bits) using the PASSWD register. When the bit field MODE is  $11_B$ , writing  $10011_B$  to the bit field PASS opens access to writing of all protected bits, and writing  $10101_B$  to the bit field PASS closes access to writing of all protected bits. In both cases, the value of the bit field MODE is not changed even if PASSWD register is written with  $98_H$  or  $A8_H$ . It can only be changed when bit field PASS is written with  $11000_B$ , for example, writing D0<sub>H</sub> to PASSWD register disables the bit protection scheme.

Note that access is opened for maximum 32 CCLKs if the "close access" password is not written. If "open access" password is written again before the end of 32 CCLK cycles, there will be a recount of 32 CCLK cycles. The protected bits include the N- and K-Divider bits, NDIV and KDIV; the Watchdog Timer enable bit, WDTEN; and the power-down and slow-down enable bits, PD and SD.

# 3.2.3.1 Password Register

# PASSWD

| Pass       | word | Register |      |   |   |               | Reset | Value: 07 <sub>H</sub> |

|------------|------|----------|------|---|---|---------------|-------|------------------------|

|            | 7    | 6        | 5    | 4 | 3 | 2             | 1     | 0                      |

|            |      | 1        | PASS | 1 |   | PROTECT<br>_S | МС    | DE                     |

| . <u> </u> |      |          | wh   |   |   | rh            | r     | W                      |

| Field     | Bits  | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------|-------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MODE      | [1:0] | rw   | <ul> <li>Bit Protection Scheme Control Bits</li> <li>00 Scheme disabled - direct access to the protected bits is allowed.</li> <li>11 Scheme enabled - the bit field PASS has to be written with the passwords to open and close the access to protected bits. (default)</li> <li>Others:Scheme Enabled.</li> <li>These two bits cannot be written directly. To change the value between 11<sub>B</sub> and 00<sub>B</sub>, the bit field PASS must be written with 11000<sub>B</sub>; only then, will the MODE[1:0] be registered.</li> </ul> |

| PROTECT_S | 2     | rh   | <ul> <li>Bit Protection Signal Status Bit</li> <li>This bit shows the status of the protection.</li> <li>0 Software is able to write to all protected bits.</li> <li>1 Software is unable to write to any protected bits.</li> </ul>                                                                                                                                                                                                                                                                                                           |

| PASS      | [7:3] | wh   | Password BitsThe Bit Protection Scheme only recognizes threepatterns. $11000_B$ Enables writing of the bit field MODE. $10011_B$ Opens access to writing of all protected bits. $10101_B$ Closes access to writing of all protected bits                                                                                                                                                                                                                                                                                                       |

# 3.2.4 XC886/888 Register Overview

The SFRs of the XC886/888 are organized into groups according to their functional units. The contents (bits) of the SFRs are summarized in **Chapter 3.2.4.1** to **Chapter 3.2.4.14**.

Note: The addresses of the bitaddressable SFRs appear in bold typeface.

# 3.2.4.1 CPU Registers

The CPU SFRs can be accessed in both the standard and mapped memory areas (RMAP = 0 or 1).

| Addr            | Register Name                                            | Bit       | 7         | 6    | 5    | 4           | 3         | 2    | 1    | 0          |

|-----------------|----------------------------------------------------------|-----------|-----------|------|------|-------------|-----------|------|------|------------|

| RMAP =          | = 0 or 1                                                 | I.        |           |      |      |             |           |      |      |            |

| 81 <sub>H</sub> | SP Reset: 07 <sub>H</sub>                                | Bit Field |           |      |      | S           | P         |      |      |            |

|                 | Stack Pointer Register                                   | Туре      |           |      |      | r           | W         |      |      |            |

| 82 <sub>H</sub> | DPL Reset: 00 <sub>H</sub>                               | Bit Field | DPL7      | DPL6 | DPL5 | DPL4        | DPL3      | DPL2 | DPL1 | DPL0       |

|                 | Data Pointer Register Low                                | Туре      | rw        | rw   | rw   | rw          | rw        | rw   | rw   | rw         |

| 83 <sub>H</sub> | DPH Reset: 00 <sub>H</sub>                               | Bit Field | DPH7      | DPH6 | DPH5 | DPH4        | DPH3      | DPH2 | DPH1 | DPH0       |

|                 | Data Pointer Register High                               | Туре      | rw        | rw   | rw   | rw          | rw        | rw   | rw   | rw         |

| 87 <sub>H</sub> | PCON Reset: 00 <sub>H</sub>                              | Bit Field | SMOD      |      | 0    |             | GF1       | GF0  | 0    | IDLE       |

|                 | Power Control Register                                   | Туре      | rw        |      | r    |             | rw        | rw   | r    | rw         |

| <sup>88</sup> H | TCON Reset: 00 <sub>H</sub>                              | Bit Field | TF1       | TR1  | TF0  | TR0         | IE1       | IT1  | IE0  | IT0        |

|                 | Timer Control Register                                   | Туре      | rwh       | rw   | rwh  | rw          | rwh       | rw   | rwh  | rw         |

| 89 <sub>H</sub> | TMOD Reset: 00 <sub>H</sub><br>Timer Mode Register       | Bit Field | GATE<br>1 | T1S  | T1M  |             | GATE<br>0 | TOS  | T    | M          |

|                 |                                                          | Туре      | rw        | rw   | r    | rw          |           | rw   | r    | w          |

| 8A <sub>H</sub> | TL0 Reset: 00 <sub>H</sub>                               | Bit Field | VAL       |      |      |             |           |      |      |            |

|                 | Timer 0 Register Low                                     | Туре      | rwh       |      |      |             |           |      |      |            |

| 8B <sub>H</sub> | TL1 Reset: 00 <sub>H</sub>                               | Bit Field | VAL       |      |      |             |           |      |      |            |

|                 | Timer 1 Register Low                                     | Туре      |           |      |      | rv          | vh        |      |      |            |

| 8C <sub>H</sub> | THO Reset: 00 <sub>H</sub>                               | Bit Field |           |      |      | V           | AL        |      |      |            |

|                 | Timer 0 Register High                                    | Туре      |           |      |      | rv          | vh        |      |      |            |

| 8D <sub>H</sub> | TH1 Reset: 00 <sub>H</sub>                               | Bit Field |           |      |      | V           | AL        |      |      |            |

|                 | Timer 1 Register High                                    | Туре      |           |      |      | rv          | vh        |      |      |            |

| 98 <sub>H</sub> | SCON Reset: 00 <sub>H</sub>                              | Bit Field | SM0       | SM1  | SM2  | REN         | TB8       | RB8  | TI   | RI         |

|                 | Serial Channel Control Register                          | Туре      | rw        | rw   | rw   | rw          | rw        | rwh  | rwh  | rwh        |

| 99 <sub>H</sub> | SBUF Reset: 00 <sub>H</sub>                              | Bit Field |           |      |      | V           | AL        |      |      |            |

|                 | Serial Data Buffer Register                              | Туре      |           |      |      | rv          | vh        |      |      |            |

| A2 <sub>H</sub> | EO Reset: 00 <sub>H</sub><br>Extended Operation Register | Bit Field |           | 0    |      | TRAP_<br>EN |           | 0    |      | DPSE<br>L0 |

|                 |                                                          | Туре      |           | r    |      | rw          |           | r    |      | rw         |

#### Table 5 CPU Register Overview

| Addr            | Register Name              | Bit       | 7              | 6  | 5 | 4  | 3  | 2 | 1 | 0 |

|-----------------|----------------------------|-----------|----------------|----|---|----|----|---|---|---|

| B3 <sub>H</sub> | MR1 Reset: 00 <sub>H</sub> | Bit Field | Bit Field DATA |    |   |    |    |   |   |   |

|                 | MDU Result Register 1      | Туре      |                |    |   | r  | h  |   |   |   |

| B4 <sub>H</sub> | MD2 Reset: 00 <sub>H</sub> | Bit Field |                |    |   | DA | TA |   |   |   |

|                 | MDU Operand Register 2     | Туре      |                |    |   | r  | w  |   |   |   |

| B4 <sub>H</sub> | MR2 Reset: 00 <sub>H</sub> | Bit Field |                |    |   | DA | TA |   |   |   |

|                 | MDU Result Register 2      | Туре      |                |    |   | r  | h  |   |   |   |

| в5 <sub>Н</sub> | MD3 Reset: 00 <sub>H</sub> | Bit Field |                |    |   | DA | TA |   |   |   |

|                 | MDU Operand Register 3     | Туре      | rw             |    |   |    |    |   |   |   |

| в5 <sub>Н</sub> | MR3 Reset: 00 <sub>H</sub> | Bit Field | DATA           |    |   |    |    |   |   |   |

|                 | MDU Result Register 3      | Туре      |                |    |   | r  | h  |   |   |   |

| B6 <sub>H</sub> | MD4 Reset: 00 <sub>H</sub> | Bit Field | DATA           |    |   |    |    |   |   |   |

|                 | MDU Operand Register 4     | Туре      | rw             |    |   |    |    |   |   |   |

| B6 <sub>H</sub> | MR4 Reset: 00 <sub>H</sub> | Bit Field |                |    |   | DA | TA |   |   |   |

|                 | MDU Result Register 4      | Туре      | rh             |    |   |    |    |   |   |   |

| в7 <sub>Н</sub> | MD5 Reset: 00 <sub>H</sub> | Bit Field | DATA           |    |   |    |    |   |   |   |

|                 | MDU Operand Register 5     | Type rw   |                | rw |   |    |    |   |   |   |

| в7 <sub>Н</sub> | MR5 Reset: 00 <sub>H</sub> | Bit Field |                |    |   | DA | TA |   |   |   |

|                 | MDU Result Register 5      | Туре      |                |    |   | r  | 'n |   |   |   |

#### Table 6MDU Register Overview (cont'd)

# 3.2.4.3 CORDIC Registers

The CORDIC SFRs can be accessed in the mapped memory area (RMAP = 1).

#### Table 7 CORDIC Register Overview

| Addr            | Register Name                    | Bit       | 7        | 6 | 5  | 4  | 3   | 2 | 1 | 0 |

|-----------------|----------------------------------|-----------|----------|---|----|----|-----|---|---|---|

| RMAP =          | = 1                              |           |          |   |    |    |     | 1 |   |   |

| 9A <sub>H</sub> | CD_CORDXL Reset: 00 <sub>H</sub> | Bit Field |          |   |    | DA | TAL |   |   |   |

|                 | CORDIC X Data Low Byte           | Туре      |          |   |    | r  | W   |   |   |   |

| 9B <sub>H</sub> | CD_CORDXH Reset: 00 <sub>H</sub> | Bit Field |          |   |    | DA | TAH |   |   |   |

|                 | CORDIC X Data High Byte          | Туре      | rw       |   |    |    |     |   |   |   |

| 9CH             | CD_CORDYL Reset: 00 <sub>H</sub> | Bit Field | ld DATAL |   |    |    |     |   |   |   |

|                 | CORDIC Y Data Low Byte           | Туре      |          |   |    | r  | W   |   |   |   |

| 9D <sub>H</sub> | CD_CORDYH Reset: 00 <sub>H</sub> | Bit Field | DATAH    |   |    |    |     |   |   |   |

|                 | CORDIC Y Data High Byte          | Туре      |          |   |    | r  | W   |   |   |   |

| 9E <sub>H</sub> | CD_CORDZL Reset: 00 <sub>H</sub> | Bit Field |          |   |    | DA | TAL |   |   |   |

|                 | CORDIC Z Data Low Byte           | Туре      | Туре     |   | rw |    |     |   |   |   |

| 9F <sub>H</sub> | CD_CORDZH Reset: 00 <sub>H</sub> | Bit Field |          |   |    | DA | ТАН |   |   |   |

|                 | CORDIC Z Data High Byte          | Туре      |          |   |    | r  | W   |   |   |   |

# Table 11ADC Register Overview (cont'd)

| Addr            | Register Name                                                         | Bit       | 7                   | 6          | 5          | 4          | 3          | 2          | 1          | 0          |  |

|-----------------|-----------------------------------------------------------------------|-----------|---------------------|------------|------------|------------|------------|------------|------------|------------|--|

| D3 <sub>H</sub> | ADC_RESR3H Reset: 00 <sub>H</sub>                                     | Bit Field |                     |            |            | RES        | ULT        |            |            |            |  |

|                 | Result Register 3 High                                                | Туре      |                     |            |            | r          | h          | <br>I      |            |            |  |

| RMAP =          | 0, PAGE 3                                                             |           |                     |            |            |            |            |            |            |            |  |

| CA <sub>H</sub> | ADC_RESRA0L Reset: 00 <sub>H</sub>                                    | Bit Field | Bit Field RESULT VF |            | DRC        | DRC CHNR   |            |            |            |            |  |

|                 | Result Register 0, View A Low                                         | Туре      |                     | rh         |            | rh         | rh         |            | rh         |            |  |

| св <sub>Н</sub> | ADC_RESRA0H Reset: 00 <sub>H</sub>                                    | Bit Field |                     |            |            | RES        | SULT       |            |            |            |  |

|                 | Result Register 0, View A High                                        | Туре      |                     |            |            | r          | h          |            |            |            |  |

| сс <sub>Н</sub> | ADC_RESRA1L Reset: 00 <sub>H</sub>                                    | Bit Field |                     | RESULT     |            | VF         | DRC        |            | CHNR       |            |  |

|                 | Result Register 1, View A Low                                         | Туре      |                     | rh         |            | rh         | rh         |            | rh         |            |  |

| CD <sub>H</sub> | ADC_RESRA1H Reset: 00 <sub>H</sub>                                    | Bit Field |                     |            |            | RES        | SULT       |            |            |            |  |

|                 | Result Register 1, View A High                                        | Туре      |                     |            |            | r          | h          |            |            |            |  |

| Ce <sub>H</sub> | ADC_RESRA2L Reset: 00 <sub>H</sub>                                    | Bit Field |                     | RESULT     |            | VF         | DRC        |            | CHNR       |            |  |

|                 | Result Register 2, View A Low                                         | Туре      |                     | rh         |            | rh         | rh         |            | rh         |            |  |

| CF <sub>H</sub> | ADC_RESRA2H Reset: 00 <sub>H</sub>                                    | Bit Field |                     |            |            | RES        | SULT       |            |            |            |  |

|                 | Result Register 2, View A High                                        | Туре      |                     |            |            | r          | h          |            |            |            |  |

| D2 <sub>H</sub> | ADC_RESRA3L Reset: 00 <sub>H</sub>                                    | Bit Field | RESULT VF           |            | DRC CHNR   |            |            |            |            |            |  |

|                 | Result Register 3, View A Low                                         | Туре      |                     | rh         |            | rh         | rh         |            | rh         |            |  |

| D3 <sub>H</sub> | ADC_RESRA3H Reset: 00 <sub>H</sub>                                    | Bit Field |                     |            |            | RES        | ULT        |            |            |            |  |

|                 | Result Register 3, View A High                                        | Туре      |                     |            |            | r          | h          |            |            |            |  |

| RMAP =          | = 0, PAGE 4                                                           |           |                     |            |            |            |            |            |            |            |  |

| CA <sub>H</sub> | ADC_RCR0 Reset: 00 <sub>H</sub><br>Result Control Register 0          | Bit Field | VFCT<br>R           | WFR        | 0          | IEN        |            | 0          |            | DRCT<br>R  |  |

|                 |                                                                       | Туре      | rw                  | rw         | r          | rw         |            | r          |            | rw         |  |

| св <sub>Н</sub> | ADC_RCR1 Reset: 00 <sub>H</sub><br>Result Control Register 1          | Bit Field | VFCT<br>R           | WFR        | 0          | IEN        |            | 0          |            | DRCT<br>R  |  |

|                 |                                                                       | Туре      | rw                  | rw         | r          | rw         |            | r          |            | rw         |  |

| сс <sup>н</sup> | ADC_RCR2 Reset: 00 <sub>H</sub><br>Result Control Register 2          | Bit Field | VFCT<br>R           | WFR        | 0          | IEN        |            | 0          |            | DRCT<br>R  |  |

|                 |                                                                       | Туре      | rw                  | rw         | r          | rw         |            | r          |            | rw         |  |

| CDH             | ADC_RCR3 Reset: 00 <sub>H</sub><br>Result Control Register 3          | Bit Field | VFCT<br>R           | WFR        | 0          | IEN        |            | 0          |            | DRCT<br>R  |  |

|                 |                                                                       | Туре      | rw                  | rw         | r          | rw         |            | r          |            | rw         |  |

| Ce <sub>H</sub> | ADC_VFCR Reset: 00 <sub>H</sub>                                       | Bit Field |                     |            | ט          |            | VFC3       | VFC2       | VFC1       | VFC0       |  |

|                 | Valid Flag Clear Register                                             | Туре      | e r                 |            |            |            | w          | w          | w          | w          |  |

| RMAP =          | = 0, PAGE 5                                                           |           |                     |            |            |            |            |            |            |            |  |

| CA <sub>H</sub> | ADC_CHINFR Reset: 00 <sub>H</sub><br>Channel Interrupt Flag Register  | Bit Field | CHINF<br>7          | CHINF<br>6 | CHINF<br>5 | CHINF<br>4 | CHINF<br>3 | CHINF<br>2 | CHINF<br>1 | CHINF<br>0 |  |

|                 |                                                                       | Туре      | rh                  | rh         | rh         | rh         | rh         | rh         | rh         | rh         |  |

| св <sub>Н</sub> | ADC_CHINCR Reset: 00 <sub>H</sub><br>Channel Interrupt Clear Register | Bit Field | CHINC<br>7          | CHINC<br>6 | CHINC<br>5 | CHINC<br>4 | CHINC<br>3 | CHINC<br>2 | CHINC<br>1 | CHINC<br>0 |  |

|                 |                                                                       | Туре      | w                   | w          | w          | w          | w          | w          | w          | w          |  |

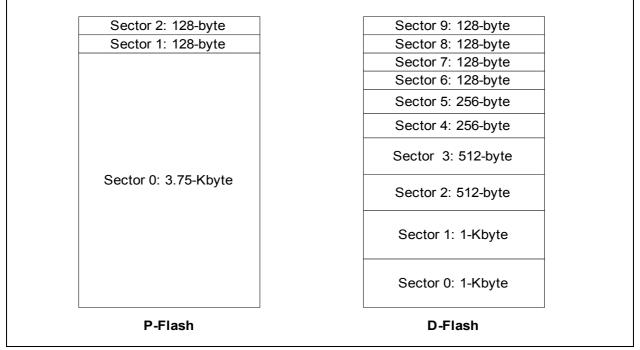

Figure 11 Flash Bank Sectorization

The internal structure of each Flash bank represents a sector architecture for flexible erase capability. The minimum erase width is always a complete sector, and sectors can be erased separately or in parallel. Contrary to standard EPROMs, erased Flash memory cells contain 0s.

The D-Flash bank is divided into more physical sectors for extended erasing and reprogramming capability; even numbers for each sector size are provided to allow greater flexibility and the ability to adapt to a wide range of application requirements.

# 3.3.2 Parallel Read Access of P-Flash

To enhance system performance, the P-Flash banks are configured for parallel read to allow two bytes of linear code to be read in 4 x CCLK cycles, compared to 6 x CCLK cycles if serial read is performed. This is achieved by reading two bytes in parallel from a P-Flash bank pair within the 3 x CCLK cycles access time and storing them in a cache. Subsequent read from the cache by the CPU does not require a wait state and can be completed within 1 x CCLK cycle. The result is the average instruction fetch time from the P-Flash banks is reduced and thus, the MIPS (Mega Instruction Per Second) of the system is increased.

However, if the parallel read feature is not desired due to certain timing constraints, it can be disabled by calling the parallel read disable subroutine.

# 3.3.3 Flash Programming Width

For the P-Flash banks, a programmed wordline (WL) must be erased before it can be reprogrammed as the Flash cells can only withstand one gate disturb. This means that the entire sector containing the WL must be erased since it is impossible to erase a single WL.

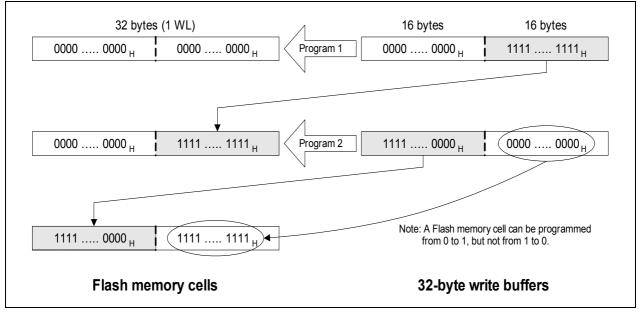

For the D-Flash bank, the same WL can be programmed twice before erasing is required as the Flash cells are able to withstand two gate disturbs. This means if the number of data bytes that needs to be written is smaller than the 32-byte minimum programming width, the user can opt to program this number of data bytes (x; where x can be any integer from 1 to 31) first and program the remaining bytes (32 - x) later. Hence, it is possible to program the same WL, for example, with 16 bytes of data two times (see **Figure 12**)

#### Figure 12 D-Flash Programming

Note: When programming a D-Flash WL the second time, the previously programmed Flash memory cells (whether 0s or 1s) should be reprogrammed with 0s to retain its original contents and to prevent "over-programming".

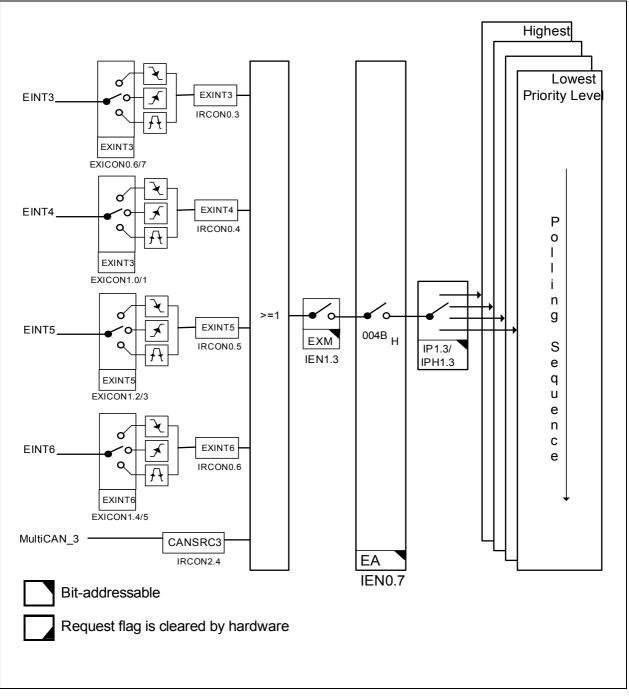

Figure 17 Interrupt Request Sources (Part 4)

# 3.4.2 Interrupt Source and Vector

Each interrupt event source has an associated interrupt vector address for the interrupt node it belongs to. This vector is accessed to service the corresponding interrupt node request. The interrupt service of each interrupt source can be individually enabled or disabled via an enable bit. The assignment of the XC886/888 interrupt sources to the interrupt vector address and the corresponding interrupt node enable bits are summarized in Table 20.

| Interrupt<br>Source | Vector<br>Address | Assignment for<br>XC886/888                          | Enable Bit | SFR    |

|---------------------|-------------------|------------------------------------------------------|------------|--------|

| NMI                 | 0073 <sub>H</sub> | Watchdog Timer NMI                                   | NMIWDT     | NMICON |

|                     |                   | PLL NMI                                              | NMIPLL     |        |

|                     |                   | Flash NMI                                            | NMIFLASH   |        |

|                     |                   | VDDC Prewarning NMI                                  | NMIVDD     |        |

|                     |                   | VDDP Prewarning NMI                                  | NMIVDDP    |        |

|                     |                   | Flash ECC NMI                                        | NMIECC     |        |

| XINTR0              | 0003 <sub>H</sub> | External Interrupt 0                                 | EX0        | IEN0   |

| XINTR1              | 000B <sub>H</sub> | Timer 0                                              | ET0        |        |

| XINTR2              | 0013 <sub>H</sub> | External Interrupt 1                                 | EX1        |        |

| XINTR3              | 001B <sub>H</sub> | Timer 1                                              | ET1        |        |

| XINTR4              | 0023 <sub>H</sub> | UART                                                 | ES         |        |

| XINTR5              | 002B <sub>H</sub> | T2                                                   | ET2        |        |

|                     |                   | UART Fractional Divider<br>(Normal Divider Overflow) |            |        |

|                     |                   | MultiCAN Node 0                                      |            |        |

|                     |                   | LIN                                                  | 1          |        |

#### Table 20 Interrupt Vector Addresses

Table 25 shows the VCO range for the XC886/888.

| <i>f</i> <sub>vcomin</sub> | f <sub>VCOmax</sub> | $f_{\sf VCOFREEmin}$ | fvcofreemax | Unit |

|----------------------------|---------------------|----------------------|-------------|------|

| 150                        | 200                 | 20                   | 80          | MHz  |

| 100                        | 150                 | 10                   | 80          | MHz  |

# 3.8.1 Recommended External Oscillator Circuits

The oscillator circuit, a Pierce oscillator, is designed to work with both, an external crystal oscillator or an external stable clock source. It basically consists of an inverting amplifier and a feedback element with XTAL1 as input, and XTAL2 as output.

When using a crystal, a proper external oscillator circuitry must be connected to both pins, XTAL1 and XTAL2. The crystal frequency can be within the range of 4 MHz to 12 MHz. Additionally, it is necessary to have two load capacitances  $C_{X1}$  and  $C_{X2}$ , and depending on the crystal type, a series resistor  $R_{X2}$ , to limit the current. A test resistor  $R_Q$  may be temporarily inserted to measure the oscillation allowance (negative resistance) of the oscillator circuitry.  $R_Q$  values are typically specified by the crystal vendor. The  $C_{X1}$  and  $C_{X2}$  values shown in **Figure 25** can be used as starting points for the negative resistance evaluation and for non-productive systems. The exact values and related operating range are dependent on the crystal frequency and have to be determined and optimized together with the final target system is strongly recommended to verify the input amplitude at XTAL1 and to determine the actual oscillation allowance (margin negative resistance) for the oscillator-crystal system.

When using an external clock signal, the signal must be connected to XTAL1. XTAL2 is left open (unconnected).

The oscillator can also be used in combination with a ceramic resonator. The final circuitry must also be verified by the resonator vendor. **Figure 25** shows the recommended external oscillator circuitries for both operating modes, external crystal mode and external input clock mode.

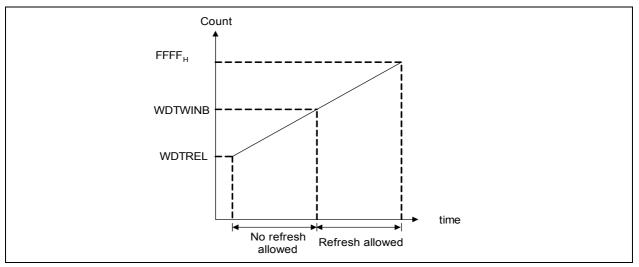

#### Figure 29 WDT Timing Diagram

**Table 27** lists the possible watchdog time ranges that can be achieved using a certain module clock. Some numbers are rounded to 3 significant digits.

#### Table 27Watchdog Time Ranges

| Reload value<br>In WDTREL          | Prescaler for $f_{PCLK}$ | Prescaler for $f_{PCLK}$ |  |  |  |  |  |  |

|------------------------------------|--------------------------|--------------------------|--|--|--|--|--|--|

|                                    | 2 (WDTIN = 0)            | 128 (WDTIN = 1)          |  |  |  |  |  |  |

|                                    | 24 MHz                   | 24 MHz                   |  |  |  |  |  |  |

| FF <sub>H</sub>                    | 21.3 μs                  | 1.37 ms                  |  |  |  |  |  |  |

| FF <sub>H</sub><br>7F <sub>H</sub> | 2.75 ms                  | 176 ms                   |  |  |  |  |  |  |

| 00 <sub>H</sub>                    | 5.46 ms                  | 350 ms                   |  |  |  |  |  |  |

# 3.23 Chip Identification Number

The XC886/888 identity (ID) register is located at Page 1 of address  $B3_{H}$ . The value of ID register is  $09_{H}$  for Flash devices and  $22_{H}$  for ROM devices. However, for easy identification of product variants, the Chip Identification Number, which is an unique number assigned to each product variant, is available. The differentiation is based on the product, variant type and device step information.

Two methods are provided to read a device's chip identification number:

- In-application subroutine, GET\_CHIP\_INFO

- Bootstrap loader (BSL) mode A

**Table 36** lists the chip identification numbers of available XC886/888 Flash and ROM device variants.

| Product Variant   | Chip Identification Number |                       |                       |  |  |  |  |  |

|-------------------|----------------------------|-----------------------|-----------------------|--|--|--|--|--|

|                   | AA-Step                    | AB-Step               | AC-Step               |  |  |  |  |  |

| Flash Devices     |                            |                       |                       |  |  |  |  |  |

| XC886CLM-8FFA 3V3 | -                          | 09500102 <sub>H</sub> | 0B500102 <sub>H</sub> |  |  |  |  |  |

| XC888CLM-8FFA 3V3 | -                          | 09500103 <sub>H</sub> | 0B500103 <sub>H</sub> |  |  |  |  |  |

| XC886LM-8FFA 3V3  | -                          | 09500122 <sub>H</sub> | 0B500122 <sub>H</sub> |  |  |  |  |  |

| XC888LM-8FFA 3V3  | -                          | 09500123 <sub>H</sub> | 0B500123 <sub>H</sub> |  |  |  |  |  |

| XC886CLM-6FFA 3V3 | -                          | 09551502 <sub>H</sub> | 0B551502 <sub>H</sub> |  |  |  |  |  |

| XC888CLM-6FFA 3V3 | -                          | 09551503 <sub>H</sub> | 0B551503 <sub>H</sub> |  |  |  |  |  |

| XC886LM-6FFA 3V3  | -                          | 09551522 <sub>H</sub> | 0B551522 <sub>H</sub> |  |  |  |  |  |

| XC888LM-6FFA 3V3  | -                          | 09551523 <sub>н</sub> | 0B551523 <sub>H</sub> |  |  |  |  |  |

| XC886CM-8FFA 3V3  | -                          | 09580102 <sub>H</sub> | 0B580102 <sub>H</sub> |  |  |  |  |  |

| XC888CM-8FFA 3V3  | -                          | 09580103 <sub>H</sub> | 0B580103 <sub>H</sub> |  |  |  |  |  |

| XC886C-8FFA 3V3   | -                          | 09580142 <sub>H</sub> | 0B580142 <sub>H</sub> |  |  |  |  |  |

| XC888C-8FFA 3V3   | -                          | 09580143 <sub>H</sub> | 0B580143 <sub>H</sub> |  |  |  |  |  |

| XC886-8FFA 3V3    | -                          | 09580162 <sub>H</sub> | 0B580162 <sub>H</sub> |  |  |  |  |  |

| XC888-8FFA 3V3    | -                          | 09580163 <sub>H</sub> | 0B580163 <sub>H</sub> |  |  |  |  |  |

| XC886CM-6FFA 3V3  | -                          | 095D1502 <sub>H</sub> | 0B5D1502 <sub>H</sub> |  |  |  |  |  |

| XC888CM-6FFA 3V3  | -                          | 095D1503 <sub>H</sub> | 0B5D1503 <sub>H</sub> |  |  |  |  |  |

| XC886C-6FFA 3V3   | -                          | 095D1542 <sub>H</sub> | 0B5D1542 <sub>H</sub> |  |  |  |  |  |

| XC888C-6FFA 3V3   | -                          | 095D1543 <sub>H</sub> | 0B5D1543 <sub>H</sub> |  |  |  |  |  |

#### Table 36 Chip Identification Number

# 4 Electrical Parameters

**Chapter 4** provides the characteristics of the electrical parameters which are implementation-specific for the XC886/888.

### 4.1 General Parameters

The general parameters are described here to aid the users in interpreting the parameters mainly in **Section 4.2** and **Section 4.3**.

### 4.1.1 Parameter Interpretation

The parameters listed in this section represent partly the characteristics of the XC886/888 and partly its requirements on the system. To aid interpreting the parameters easily when evaluating them for a design, they are indicated by the abbreviations in the "Symbol" column:

• CC

These parameters indicate **C**ontroller **C**haracteristics, which are distinctive features of the XC886/888 and must be regarded for a system design.

• SR

These parameters indicate **S**ystem **R**equirements, which must be provided by the microcontroller system in which the XC886/888 is designed in.

# Table 38 Input/Output Characteristics (Operating Conditions apply) (cont'd)

| Parameter                                                                      | Symbol             |    | Limit Values                |                         | Unit | Test Conditions                                        |  |

|--------------------------------------------------------------------------------|--------------------|----|-----------------------------|-------------------------|------|--------------------------------------------------------|--|

|                                                                                |                    |    | min.                        | max.                    |      |                                                        |  |

| Input high voltage on RESET pin                                                | V <sub>IHR</sub>   | SR | $0.7 \times V_{\text{DDP}}$ | -                       | V    | CMOS Mode                                              |  |

| Input high voltage on TMS pin                                                  | V <sub>IHT</sub>   | SR | $0.75 \times V_{ m DDP}$    | -                       | V    | CMOS Mode                                              |  |

| Input Hysteresis on port<br>pins                                               | HYSP               | CC | $0.07 \times V_{ m DDP}$    | -                       | V    | CMOS Mode <sup>1)</sup>                                |  |

| Input Hysteresis on XTAL1                                                      | HYSX               | CC | $0.07 \times V_{ m DDC}$    | -                       | V    | 1)                                                     |  |

| Input low voltage at<br>XTAL1                                                  | $V_{ILX}$          | SR | V <sub>SS</sub> -<br>0.5    | $0.3 \times V_{ m DDC}$ | V    |                                                        |  |

| Input high voltage at XTAL1                                                    | V <sub>IHX</sub>   | SR | $0.7 \times V_{ m DDC}$     | V <sub>DDC</sub> + 0.5  | V    |                                                        |  |

| Pull-up current                                                                | $I_{\rm PU}$       | SR | -                           | -10                     | μA   | V <sub>IHP,min</sub>                                   |  |

|                                                                                |                    |    | -150                        | _                       | μA   | $V_{\rm ILP,max}$                                      |  |

| Pull-down current                                                              | $I_{\rm PD}$       | SR | -                           | 10                      | μA   | $V_{ILP,max}$                                          |  |

|                                                                                |                    |    | 150                         | -                       | μA   | V <sub>IHP,min</sub>                                   |  |

| Input leakage current                                                          | I <sub>OZ1</sub>   | CC | -1                          | 1                       | μA   | $0 < V_{IN} < V_{DDP},$<br>$T_A \le 125^{\circ}C^{2)}$ |  |

| Input current at XTAL1                                                         | $I_{ILX}$          | CC | -10                         | 10                      | μA   |                                                        |  |

| Overload current on any pin                                                    | I <sub>OV</sub>    | SR | -5                          | 5                       | mA   |                                                        |  |

| Absolute sum of overload currents                                              | $\Sigma  I_{OV} $  | SR | -                           | 25                      | mA   | 3)                                                     |  |

| Voltage on any pin during $V_{\text{DDP}}$ power off                           | V <sub>PO</sub>    | SR | -                           | 0.3                     | V    | 4)                                                     |  |

| Maximum current per pin (excluding $V_{\text{DDP}}$ and $V_{\text{SS}}$ )      | I <sub>M</sub> SR  | SR | -                           | 15                      | mA   |                                                        |  |

| Maximum current for all pins (excluding $V_{\text{DDP}}$ and $V_{\text{SS}}$ ) | $\Sigma  I_{M} $   | SR | -                           | 90                      | mA   |                                                        |  |

| Maximum current into $V_{\text{DDP}}$                                          | I <sub>mvddp</sub> | SR | -                           | 120                     | mA   | 3)                                                     |  |

# Table 44Power Down Current (Operating Conditions apply; $V_{DDP} = 3.3V$ <br/>range)

| Parameter                     | Symbol           | Limit              | Values             | Unit | <b>Test Condition</b>                 |

|-------------------------------|------------------|--------------------|--------------------|------|---------------------------------------|

|                               |                  | typ. <sup>1)</sup> | max. <sup>2)</sup> | 1    |                                       |

| $V_{\text{DDP}}$ = 3.3V Range |                  | ·                  |                    |      |                                       |

| Power-Down Mode               | I <sub>PDP</sub> | 1                  | 10                 | μA   | $T_{\rm A}$ = + 25 °C <sup>3)4)</sup> |

|                               |                  | -                  | 30                 | μA   | $T_{\rm A}$ = + 85 °C <sup>4)5)</sup> |

1) The typical  $I_{PDP}$  values are measured at  $V_{DDP}$  = 3.3 V.

2) The maximum  $I_{\rm PDP}$  values are measured at  $V_{\rm DDP}$  = 3.6 V.

3)  $I_{PDP}$  has a maximum value of 200  $\mu$ A at  $T_A$  = + 125 °C.

4)  $I_{PDP}$  is measured with:  $\overline{RESET} = V_{DDP}$ ,  $V_{AGND} = V_{SS}$ , RXD/INT0 =  $V_{DDP}$ ; rest of the ports are programmed to be input with either internal pull devices enabled or driven externally to ensure no floating inputs.

5) Not subjected to production test, verified by design/characterization.

# 4.3.3 Power-on Reset and PLL Timing

**Table 49** provides the characteristics of the power-on reset and PLL timing in the XC886/888.

| Table 46 | Power-On Reset and PLL Timing (Operating Conditions apply) |

|----------|------------------------------------------------------------|

|          |                                                            |

| Parameter                           | Symbol             |    | Limit Values |      |      | Unit | Test Conditions                                                              |

|-------------------------------------|--------------------|----|--------------|------|------|------|------------------------------------------------------------------------------|

|                                     |                    |    | min.         | typ. | max. |      |                                                                              |

| Pad operating voltage               | $V_{PAD}$          | CC | 2.3          | -    | -    | V    | 1)                                                                           |

| On-Chip Oscillator<br>start-up time | t <sub>OSCST</sub> | СС | -            | -    | 500  | ns   | 1)                                                                           |

| Flash initialization time           | t <sub>FINIT</sub> | CC | _            | 160  | _    | μS   | 1)                                                                           |

| RESET hold time                     | t <sub>RST</sub>   | SR | -            | 500  | _    | μS   | $V_{\rm DDP}$ rise time<br>(10% – 90%) $\leq$<br>500 $\mu$ s <sup>1)2)</sup> |

| PLL lock-in in time                 | t <sub>LOCK</sub>  | CC | -            | -    | 200  | μS   | 1)                                                                           |

| PLL accumulated jitter              | $D_{P}$            |    | -            | _    | 0.7  | ns   | 1)3)                                                                         |

1) Not all parameters are 100% tested, but are verified by design/characterization and test correlation.

2) RESET signal has to be active (low) until  $V_{\text{DDC}}$  has reached 90% of its maximum value (typ. 2.5 V).

3) PLL lock at 96 MHz using a 4 MHz external oscillator. The PLL Divider settings are K = 2, N = 48 and P = 1.

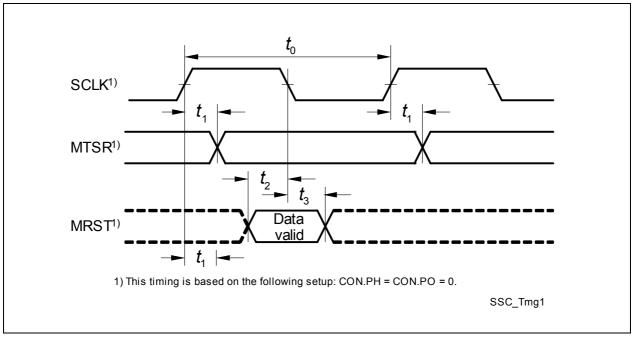

# 4.3.7 SSC Master Mode Timing

Table 51 provides the characteristics of the SSC timing in the XC886/888.

| Table 51 | SSC Master Mode Timing (Operating Conditions apply; CL = 50 pF) |

|----------|-----------------------------------------------------------------|

|----------|-----------------------------------------------------------------|

| Parameter            | Symbol                |    | Limi               | t Values | Unit | Test       |

|----------------------|-----------------------|----|--------------------|----------|------|------------|

|                      |                       |    | min.               | max.     |      | Conditions |

| SCLK clock period    | t <sub>0</sub>        | CC | 2*T <sub>SSC</sub> | –        | ns   | 1)2)       |

| MTSR delay from SCLK | t <sub>1</sub>        | CC | 0                  | 8        | ns   | 2)         |

| MRST setup to SCLK   | <i>t</i> <sub>2</sub> | SR | 24                 | -        | ns   | 2)         |

| MRST hold from SCLK  | t <sub>3</sub>        | SR | 0                  | -        | ns   | 2)         |

1)  $T_{SSCmin} = T_{CPU} = 1/f_{CPU}$ . When  $f_{CPU} = 24$  MHz,  $t_0 = 83.3$  ns.  $T_{CPU}$  is the CPU clock period.

2) Not all parameters are 100% tested, but are verified by design/characterization and test correlation.

Figure 52 SSC Master Mode Timing

www.infineon.com

Published by Infineon Technologies AG