Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Detuils                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                          |

| Core Processor             | XC800                                                                             |

| Core Size                  | 8-Bit                                                                             |

| Speed                      | 24MHz                                                                             |

| Connectivity               | LINbus, SSI, UART/USART                                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                             |

| Number of I/O              | 48                                                                                |

| Program Memory Size        | 24KB (24K x 8)                                                                    |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | •                                                                                 |

| RAM Size                   | 1.75K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                       |

| Data Converters            | A/D 8x10b                                                                         |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-LQFP                                                                           |

| Supplier Device Package    | PG-TQFP-64                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/saf-xc888lm-6ffi-5v-ac |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Summary of Features

Features: (continued)

- Power-on reset generation

- Brownout detection for core logic supply

- On-chip OSC and PLL for clock generation

- PLL loss-of-lock detection

- Power saving modes

- slow-down mode

- idle mode

- power-down mode with wake-up capability via RXD or EXINT0

- clock gating control to each peripheral

- Programmable 16-bit Watchdog Timer (WDT)

- Six ports

- Up to 48 pins as digital I/O

- 8 pins as digital/analog input

- 8-channel, 10-bit ADC

- Four 16-bit timers

- Timer 0 and Timer 1 (T0 and T1)

- Timer 2 and Timer 21 (T2 and T21)

- Multiplication/Division Unit for arithmetic operations (MDU)

- Software libraries to support floating point and MDU calculations

- CORDIC Coprocessor for computation of trigonometric, hyperbolic and linear functions

- MultiCAN with 2 nodes, 32 message objects

- Capture/compare unit for PWM signal generation (CCU6)

- Two full-duplex serial interfaces (UART and UART1)

- Synchronous serial channel (SSC)

- On-chip debug support

- 1 Kbyte of monitor ROM (part of the 12-Kbyte Boot ROM)

- 64 bytes of monitor RAM

- Packages:

- PG-TQFP-48

- PG-TQFP-64

- Temperature range *T*<sub>A</sub>:

- SAF (-40 to 85 °C)

- SAK (-40 to 125 °C)

# XC886/888CLM

### **General Device Information**

# Table 3Pin Definitions and Functions (cont'd)

| Symbol | Pin Number<br>(TQFP-48/64) | Туре | Reset<br>State | Function                     |                                                                           |

|--------|----------------------------|------|----------------|------------------------------|---------------------------------------------------------------------------|

| P1.6   | 8/10                       |      | PU             | CCPOS1_1<br>T12HR_0          | •                                                                         |

|        |                            |      |                | EXINT6_0<br>RXDC0_2<br>T21_1 | • •                                                                       |

| P1.7   | 9/11                       |      | PU             | CCPOS2_1<br>T13HR_0<br>T2 1  | CCU6 Hall Input 2<br>CCU6 Timer 13 Hardware Run<br>Input<br>Timer 2 Input |

|        |                            |      |                | TXDC0_2                      | •                                                                         |

|        |                            |      |                |                              | .6 can be used as a software chip<br>t for the SSC.                       |

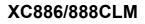

#### Figure 9 Address Extension by Paging

In order to access a register located in a page different from the actual one, the current page must be exited. This is done by reprogramming the bit field PAGE in the page register. Only then can the desired access be performed.

If an interrupt routine is initiated between the page register access and the module register access, and the interrupt needs to access a register located in another page, the current page setting can be saved, the new one programmed and the old page setting restored. This is possible with the storage fields STx (x = 0 - 3) for the save and restore action of the current page setting. By indicating which storage bit field should be used in parallel with the new page value, a single write operation can:

• Save the contents of PAGE in STx before overwriting with the new value (this is done in the beginning of the interrupt routine to save the current page setting and program the new page number); or

The page register has the following definition:

### MOD\_PAGE Page Register for module MOD

Reset Value: 00<sub>H</sub>

| 7 | 6 | 5  | 4  | 3 | 2 | 1    | 0 |

|---|---|----|----|---|---|------|---|

| 0 | Ρ | ST | NR | 0 |   | PAGE |   |

| v | V | V  | V  | r |   | rw   | I |

| Field | Bits  | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------|-------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PAGE  | [2:0] | rw   | <b>Page Bits</b><br>When written, the value indicates the new page.<br>When read, the value indicates the currently active<br>page.                                                                                                                                                                                                                                                                                                                                        |

| STNR  | [5:4] | W    | Storage NumberThis number indicates which storage bit field is the<br>target of the operation defined by bit field OP.If $OP = 10_B$ ,<br>the contents of PAGE are saved in STx before being<br>overwritten with the new value.If $OP = 11_B$ ,<br>the contents of PAGE are overwritten by the<br>contents of STx. The value written to the bit positions<br>of PAGE is ignored.00ST0 is selected.<br>0101ST1 is selected.<br>1010ST2 is selected.<br>1111ST3 is selected. |

#### Table 10Port Register Overview (cont'd)

| Addr            | Register Name                     | Bit       | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|-----------------|-----------------------------------|-----------|----|----|----|----|----|----|----|----|

| 93 <sub>H</sub> | P5_ALTSEL1 Reset: 00 <sub>H</sub> | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P5 Alternate Select 1 Register    | Туре      | rw |

| в0 <sub>Н</sub> | P3_ALTSEL0 Reset: 00 <sub>H</sub> | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P3 Alternate Select 0 Register    | Туре      | rw |

| B1 <sub>H</sub> | P3_ALTSEL1 Reset: 00 <sub>H</sub> | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P3 Alternate Select 1 Register    | Туре      | rw |

| C8 <sub>H</sub> | P4_ALTSEL0 Reset: 00 <sub>H</sub> | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P4 Alternate Select 0 Register    | Туре      | rw |

| C9 <sub>H</sub> | P4_ALTSEL1 Reset: 00 <sub>H</sub> | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P4 Alternate Select 1 Register    | Туре      | rw |

| RMAP =          | = 0, PAGE 3                       |           |    |    |    |    |    |    |    |    |

| 80 <sub>H</sub> | P0_OD Reset: 00 <sub>H</sub>      | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P0 Open Drain Control Register    | Туре      | rw |

| 90 <sub>H</sub> | P1_OD Reset: 00 <sub>H</sub>      | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P1 Open Drain Control Register    | Туре      | rw |

| 92 <sub>H</sub> | P5_OD Reset: 00 <sub>H</sub>      | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P5 Open Drain Control Register    | Туре      | rw |

| в0 <sub>Н</sub> | P3_OD Reset: 00 <sub>H</sub>      | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P3 Open Drain Control Register    | Туре      | rw |

| C8 <sub>H</sub> | P4_OD Reset: 00 <sub>H</sub>      | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P4 Open Drain Control Register    | Туре      | rw |

# 3.2.4.7 ADC Registers

The ADC SFRs can be accessed in the standard memory area (RMAP = 0).

### Table 11ADC Register Overview

|                 | •                                                                    |           |           |           |    |      |      |       |            |       |

|-----------------|----------------------------------------------------------------------|-----------|-----------|-----------|----|------|------|-------|------------|-------|

| Addr            | Register Name                                                        | Bit       | 7         | 6         | 5  | 4    | 3    | 2     | 1          | 0     |

| RMAP =          | = 0                                                                  |           |           |           |    |      |      | •     |            |       |

| D1 <sub>H</sub> | ADC_PAGE Reset: 00 <sub>H</sub>                                      | Bit Field | C         | P         | ST | NR   | 0    |       | PAGE       |       |

|                 | Page Register                                                        | Туре      | ١         | N         | ١  | N    | r    |       | rw         |       |

| RMAP =          | = 0, PAGE 0                                                          |           |           |           |    |      |      |       |            |       |

| са <sub>Н</sub> | ADC_GLOBCTR Reset: 30 <sub>H</sub>                                   | Bit Field | ANON      | DW        | C. | тс   | 0    |       |            |       |

|                 | Global Control Register                                              | Туре      | rw        | rw        | r  | W    |      |       | r          |       |

| св <sub>Н</sub> | ADC_GLOBSTR Reset: 00 <sub>H</sub><br>Global Status Register         | Bit Field | (         | 0         |    | CHNR |      | 0     | SAMP<br>LE | BUSY  |

|                 |                                                                      | Туре      |           | r         |    | rh   |      | r     | rh         | rh    |

| сс <sub>Н</sub> | ADC_PRAR Reset: 00 <sub>H</sub><br>Priority and Arbitration Register | Bit Field | ASEN<br>1 | ASEN<br>0 | 0  | ARBM | CSM1 | PRIO1 | CSM0       | PRIO0 |

|                 |                                                                      | Туре      | rw        | rw        | r  | rw   | rw   | rw    | rw         | rw    |

# Table 11ADC Register Overview (cont'd)

| Addr            | Register Name                                                          | Bit       | 7          | 6          | 5          | 4          | 3          | 2          | 1          | 0          |

|-----------------|------------------------------------------------------------------------|-----------|------------|------------|------------|------------|------------|------------|------------|------------|

| cc <sup>H</sup> | ADC_CHINSR Reset: 00 <sub>H</sub><br>Channel Interrupt Set Register    | Bit Field | CHINS<br>7 | CHINS<br>6 | CHINS<br>5 | CHINS<br>4 | CHINS<br>3 | CHINS<br>2 | CHINS<br>1 | CHINS<br>0 |

|                 |                                                                        | Туре      | w          | w          | w          | w          | w          | W          | w          | w          |

| CD <sub>H</sub> | ADC_CHINPR Reset: 00 <sub>H</sub><br>Channel Interrupt Node Pointer    | Bit Field | CHINP<br>7 | CHINP<br>6 | CHINP<br>5 | CHINP<br>4 | CHINP<br>3 | CHINP<br>2 | CHINP<br>1 | CHINP<br>0 |

|                 | Register                                                               | Туре      | rw         |

| Ceh             | ADC_EVINFR Reset: 00 <sub>H</sub><br>Event Interrupt Flag Register     | Bit Field | EVINF<br>7 | EVINF<br>6 | EVINF<br>5 | EVINF<br>4 | (          | )          | EVINF<br>1 | EVINF<br>0 |

|                 |                                                                        | Туре      | rh         | rh         | rh         | rh         |            | r          | rh         | rh         |

| CF <sub>H</sub> | ADC_EVINCR Reset: 00 <sub>H</sub><br>Event Interrupt Clear Flag        | Bit Field | EVINC<br>7 | EVINC<br>6 | EVINC<br>5 | EVINC<br>4 | (          | )          | EVINC<br>1 | EVINC<br>0 |

|                 | Register                                                               | Туре      | w          | w          | w          | w          |            | r          | w          | w          |

| D2 <sub>H</sub> | ADC_EVINSR Reset: 00 <sub>H</sub><br>Event Interrupt Set Flag Register | Bit Field | EVINS<br>7 | EVINS<br>6 | EVINS<br>5 | EVINS<br>4 | (          | )          | EVINS<br>1 | EVINS<br>0 |

|                 |                                                                        | Туре      | w          | w          | w          | w          |            | r          | w          | w          |

| D3 <sub>H</sub> | ADC_EVINPR Reset: 00 <sub>H</sub><br>Event Interrupt Node Pointer      | Bit Field | EVINP<br>7 | EVINP<br>6 | EVINP<br>5 | EVINP<br>4 | (          | )          | EVINP<br>1 | EVINP<br>0 |

|                 | Register                                                               | Туре      | rw         | rw         | rw         | rw         |            | r          | rw         | rw         |

| RMAP =          | = 0, PAGE 6                                                            |           |            |            |            |            |            |            |            |            |

| CA <sub>H</sub> | ADC_CRCR1 Reset: 00 <sub>H</sub>                                       | Bit Field | CH7        | CH6        | CH5        | CH4        |            | (          | )          |            |

|                 | Conversion Request Control<br>Register 1                               | Туре      | rwh        | rwh        | rwh        | rwh        |            | I          | r          |            |

| св <sub>Н</sub> | ADC_CRPR1 Reset: 00 <sub>H</sub>                                       | Bit Field | CHP7       | CHP6       | CHP5       | CHP4       |            | (          | )          |            |

|                 | Conversion Request Pending<br>Register 1                               | Туре      | rwh        | rwh        | rwh        | rwh        |            | I          | r          |            |

| сс <sup>н</sup> | ADC_CRMR1 Reset: 00 <sub>H</sub><br>Conversion Request Mode            | Bit Field | Rsv        | LDEV       | CLRP<br>ND | SCAN       | ENSI       | ENTR       | 0          | ENGT       |

|                 | Register 1                                                             | Туре      | r          | w          | w          | rw         | rw         | rw         | r          | rw         |

| CD <sub>H</sub> | ADC_QMR0 Reset: 00 <sub>H</sub><br>Queue Mode Register 0               | Bit Field | CEV        | TREV       | FLUS<br>H  | CLRV       | 0          | ENTR       | 0          | ENGT       |

|                 |                                                                        | Туре      | w          | w          | w          | w          | r          | rw         | r          | rw         |

| Ceh             | ADC_QSR0 Reset: 20 <sub>H</sub><br>Queue Status Register 0             | Bit Field | Rsv        | 0          | EMPT<br>Y  | EV         | 0 FILL     |            | LL         |            |

|                 |                                                                        | Туре      | r          | r          | rh         | rh         |            | r          | r          | h          |

| CF <sub>H</sub> | ADC_Q0R0 Reset: 00 <sub>H</sub>                                        | Bit Field | EXTR       | ENSI       | RF         | V          | 0          | F          | REQCHN     | २          |

|                 | Queue 0 Register 0                                                     | Туре      | rh         | rh         | rh         | rh         | r          |            | rh         |            |

| D2 <sub>H</sub> | ADC_QBUR0 Reset: 00 <sub>H</sub>                                       | Bit Field | EXTR       | ENSI       | RF         | V          | 0          | F          | REQCHN     | ۲          |

|                 | Queue Backup Register 0                                                | Туре      | rh         | rh         | rh         | rh         | r          |            | rh         |            |

| D2 <sub>H</sub> | ADC_QINR0 Reset: 00 <sub>H</sub>                                       | Bit Field | EXTR       | ENSI       | RF         | (          | )          | F          | REQCHN     | २          |

|                 | Queue Input Register 0                                                 | Туре      | w          | w          | w          |            | r          |            | w          |            |

#### Table 14CCU6 Register Overview (cont'd)

| Addr            | Register Name                                                       | Bit       | 7     | 6            | 5            | 4          | 3            | 2          | 1            | 0          |

|-----------------|---------------------------------------------------------------------|-----------|-------|--------------|--------------|------------|--------------|------------|--------------|------------|

| Fe <sub>H</sub> | CCU6_CMPSTATL Reset: 00 <sub>H</sub><br>Compare State Register Low  | Bit Field | 0     | CC63<br>ST   | CC<br>POS2   | CC<br>POS1 | CC<br>POS0   | CC62<br>ST | CC61<br>ST   | CC60<br>ST |

|                 |                                                                     | Туре      | r     | rh           | rh           | rh         | rh           | rh         | rh           | rh         |

| FF <sub>H</sub> | CCU6_CMPSTATH Reset: 00 <sub>H</sub><br>Compare State Register High | Bit Field | T13IM | COUT<br>63PS | COUT<br>62PS | CC62<br>PS | COUT<br>61PS | CC61<br>PS | COUT<br>60PS | CC60<br>PS |

|                 |                                                                     | Туре      | rwh   | rwh          | rwh          | rwh        | rwh          | rwh        | rwh          | rwh        |

# 3.2.4.11 UART1 Registers

The UART1 SFRs can be accessed in the mapped memory area (RMAP = 1).

### Table 15 UART1 Register Overview

| Addr            | Register Name                          | Bit       | 7      | 6   | 5   | 4    | 3     | 2     | 1   | 0    |

|-----------------|----------------------------------------|-----------|--------|-----|-----|------|-------|-------|-----|------|

| RMAP =          | = 1                                    | 1         |        |     |     |      |       |       |     | 1    |

| C8 <sub>H</sub> | SCON Reset: 00 <sub>H</sub>            | Bit Field | SM0    | SM1 | SM2 | REN  | TB8   | RB8   | TI  | RI   |

|                 | Serial Channel Control Register        | Туре      | rw     | rw  | rw  | rw   | rw    | rwh   | rwh | rwh  |

| C9 <sub>H</sub> | SBUF Reset: 00 <sub>H</sub>            | Bit Field |        |     |     | V    | AL    |       |     |      |

|                 | Serial Data Buffer Register            | Туре      |        |     |     | rv   | vh    |       |     |      |

| са <sub>Н</sub> | BCON Reset: 00 <sub>H</sub>            | Bit Field |        | (   | )   |      |       | BRPRE |     | R    |

|                 | Baud Rate Control Register             | Туре      |        |     | r   |      |       | rw    |     | rw   |

| св <sub>Н</sub> | BG Reset: 00 <sub>H</sub>              | Bit Field |        |     |     | BR_V | 'ALUE |       |     |      |

|                 | Baud Rate Timer/Reload<br>Register     | Туре      |        |     |     | rv   | vh    |       |     |      |

| сс <sub>Н</sub> | FDCON Reset: 00 <sub>H</sub>           | Bit Field |        |     | 0   |      |       | NDOV  | FDM | FDEN |

|                 | Fractional Divider Control<br>Register | Туре      |        |     | r   |      |       | rwh   | rw  | rw   |

| CD <sub>H</sub> | FDSTEP Reset: 00 <sub>H</sub>          | Bit Field |        |     |     | ST   | ΈP    |       |     |      |

|                 | Fractional Divider Reload<br>Register  | Туре      | rw     |     |     |      |       |       |     |      |

| Ceh             | FDRES Reset: 00 <sub>H</sub>           | Bit Field | RESULT |     |     |      |       |       |     |      |

|                 | Fractional Divider Result<br>Register  | Туре      |        |     |     | r    | h     |       |     |      |

# Table 18OCDS Register Overview (cont'd)

| Addr            | Register Name                | Bit       | 7 | 6 | 5 | 4  | 3   | 2 | 1 | 0 |

|-----------------|------------------------------|-----------|---|---|---|----|-----|---|---|---|

| EC <sub>H</sub> | MMWR2 Reset: 00 <sub>H</sub> | Bit Field |   |   |   | MM | WR2 |   |   |   |

|                 | Monitor Work Register 2      | Туре      |   |   |   | n  | w   |   |   |   |

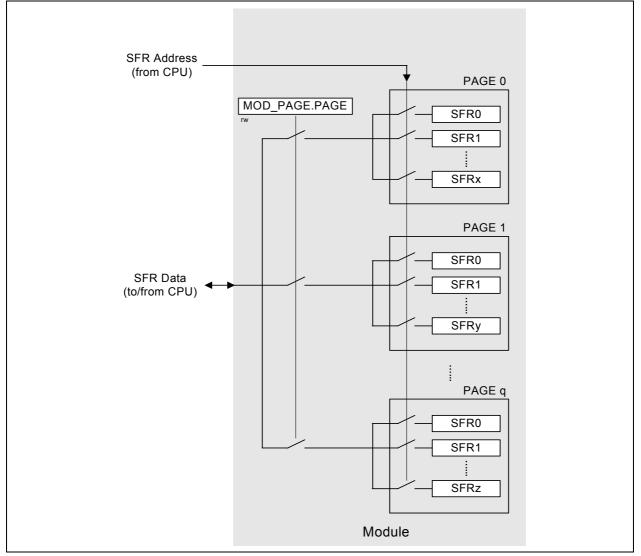

Figure 11 Flash Bank Sectorization

The internal structure of each Flash bank represents a sector architecture for flexible erase capability. The minimum erase width is always a complete sector, and sectors can be erased separately or in parallel. Contrary to standard EPROMs, erased Flash memory cells contain 0s.

The D-Flash bank is divided into more physical sectors for extended erasing and reprogramming capability; even numbers for each sector size are provided to allow greater flexibility and the ability to adapt to a wide range of application requirements.

# 3.3.2 Parallel Read Access of P-Flash

To enhance system performance, the P-Flash banks are configured for parallel read to allow two bytes of linear code to be read in 4 x CCLK cycles, compared to 6 x CCLK cycles if serial read is performed. This is achieved by reading two bytes in parallel from a P-Flash bank pair within the 3 x CCLK cycles access time and storing them in a cache. Subsequent read from the cache by the CPU does not require a wait state and can be completed within 1 x CCLK cycle. The result is the average instruction fetch time from the P-Flash banks is reduced and thus, the MIPS (Mega Instruction Per Second) of the system is increased.

However, if the parallel read feature is not desired due to certain timing constraints, it can be disabled by calling the parallel read disable subroutine.

# **Functional Description**

| Interrupt<br>Source | Vector<br>Address | Assignment for<br>XC886/888                           | Enable Bit | SFR  |

|---------------------|-------------------|-------------------------------------------------------|------------|------|

| XINTR6              | 0033 <sub>H</sub> | MultiCAN Nodes 1 and 2                                | EADC       | IEN1 |

|                     |                   | ADC[1:0]                                              |            |      |

| XINTR7              | 003B <sub>H</sub> | SSC                                                   | ESSC       |      |

| XINTR8              | 0043 <sub>H</sub> | External Interrupt 2                                  | EX2        |      |

|                     |                   | T21                                                   |            |      |

|                     |                   | CORDIC                                                |            |      |

|                     |                   | UART1                                                 | ]          |      |

|                     |                   | UART1 Fractional Divider<br>(Normal Divider Overflow) |            |      |

|                     |                   | MDU[1:0]                                              | 1          |      |

| XINTR9              | 004B <sub>H</sub> | External Interrupt 3                                  | EXM        |      |

|                     |                   | External Interrupt 4                                  | 1          |      |

|                     |                   | External Interrupt 5                                  |            |      |

|                     |                   | External Interrupt 6                                  |            |      |

|                     |                   | MultiCAN Node 3                                       |            |      |

| XINTR10             | 0053 <sub>H</sub> | CCU6 INP0                                             | ECCIP0     |      |

|                     |                   | MultiCAN Node 4                                       |            |      |

| XINTR11             | 005B <sub>H</sub> | CCU6 INP1                                             | ECCIP1     |      |

|                     |                   | MultiCAN Node 5                                       |            |      |

| XINTR12             | 0063 <sub>H</sub> | CCU6 INP2                                             | ECCIP2     |      |

|                     |                   | MultiCAN Node 6                                       |            |      |

| XINTR13             | 006B <sub>H</sub> | CCU6 INP3                                             | ECCIP3     |      |

|                     |                   | MultiCAN Node 7                                       |            |      |

# 3.7 Reset Control

The XC886/888 has five types of reset: power-on reset, hardware reset, watchdog timer reset, power-down wake-up reset, and brownout reset.

When the XC886/888 is first powered up, the status of certain pins (see **Table 23**) must be defined to ensure proper start operation of the device. At the end of a reset sequence, the sampled values are latched to select the desired boot option, which cannot be modified until the next power-on reset or hardware reset. This guarantees stable conditions during the normal operation of the device.

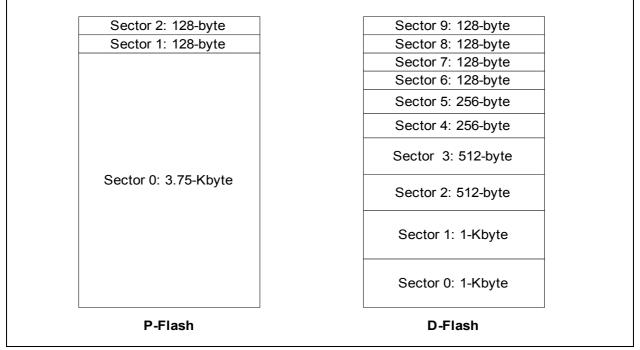

In order to power up the system properly, the external reset pin  $\overrightarrow{\text{RESET}}$  must be asserted until  $V_{\text{DDC}}$  reaches 0.9\* $V_{\text{DDC}}$ . The delay of external reset can be realized by an external capacitor at  $\overrightarrow{\text{RESET}}$  pin. This capacitor value must be selected so that  $V_{\text{RESET}}$  reaches 0.4 V, but not before  $V_{\text{DDC}}$  reaches 0.9\*  $V_{\text{DDC}}$ .

A typical application example is shown in Figure 22. The  $V_{\text{DDP}}$  capacitor value is 100 nF while the  $V_{\text{DDC}}$  capacitor value is 220 nF. The capacitor connected to RESET pin is 100 nF.

Typically, the time taken for  $V_{DDC}$  to reach  $0.9^*V_{DDC}$  is less than 50 µs once  $V_{DDP}$  reaches 2.3V. Hence, based on the condition that 10% to 90%  $V_{DDP}$  (slew rate) is less than 500 µs, the RESET pin should be held low for 500 µs typically. See Figure 23.

Figure 22 Reset Circuitry

# 3.7.1 Module Reset Behavior

**Table 22** lists the functions of the XC886/888 and the various reset types that affect these functions. The symbol "■" signifies that the particular function is reset to its default state.

| Module/               | Wake-Up                              | Watchdog                  | Hardware                  | Power-On                  | Brownout                  |

|-----------------------|--------------------------------------|---------------------------|---------------------------|---------------------------|---------------------------|

| Function              | Reset                                | Reset                     | Reset                     | Reset                     | Reset                     |

| CPU Core              |                                      |                           |                           |                           |                           |

| Peripherals           |                                      |                           |                           |                           |                           |

| On-Chip<br>Static RAM | Not affected,<br>Reliable            | Not affected,<br>Reliable | Not affected,<br>Reliable | Affected, un-<br>reliable | Affected, un-<br>reliable |

| Oscillator,<br>PLL    |                                      | Not affected              |                           |                           |                           |

| Port Pins             |                                      |                           |                           |                           |                           |

| EVR                   | The voltage regulator is switched on | Not affected              |                           |                           |                           |

| FLASH                 |                                      |                           |                           |                           |                           |

| NMI                   | Disabled                             | Disabled                  |                           |                           |                           |

#### Table 22Effect of Reset on Device Functions

# 3.7.2 Booting Scheme

When the XC886/888 is reset, it must identify the type of configuration with which to start the different modes once the reset sequence is complete. Thus, boot configuration information that is required for activation of special modes and conditions needs to be applied by the external world through input pins. After power-on reset or hardware reset, the pins MBC, TMS and P0.0 collectively select the different boot options. Table 23 shows the available boot options in the XC886/888.

| MBC TMS P0.0 |   |   | Type of Mode                                                               | PC Start Value    |  |  |  |

|--------------|---|---|----------------------------------------------------------------------------|-------------------|--|--|--|

| 1            | 0 | Х | User Mode <sup>1)</sup> ; on-chip OSC/PLL non-bypassed                     | 0000 <sub>H</sub> |  |  |  |

| 0            | 0 | Х | BSL Mode; on-chip OSC/PLL non-bypassed <sup>2)</sup>                       | 0000 <sub>H</sub> |  |  |  |

| 0            | 1 | 0 | OCDS Mode; on-chip OSC/PLL non-<br>bypassed                                | 0000 <sub>H</sub> |  |  |  |

| 1            | 1 | 0 | User (JTAG) Mode <sup>3)</sup> ; on-chip OSC/PLL non-<br>bypassed (normal) | 0000 <sub>H</sub> |  |  |  |

| Table 23 | XC886/888 Boot Selection |

|----------|--------------------------|

|          |                          |

- 1) BSL mode is automatically entered if no valid password is installed and data at memory address 0000H equals zero.

- 2) OSC is bypassed in MultiCAN BSL mode

- 3) Normal user mode with standard JTAG (TCK,TDI,TDO) pins for hot-attach purpose.

Note: The boot options are valid only with the default set of UART and JTAG pins.

# 3.8 Clock Generation Unit

The Clock Generation Unit (CGU) allows great flexibility in the clock generation for the XC886/888. The power consumption is indirectly proportional to the frequency, whereas the performance of the microcontroller is directly proportional to the frequency. During user program execution, the frequency can be programmed for an optimal ratio between performance and power consumption. Therefore the power consumption can be adapted to the actual application state.

#### Features

- Phase-Locked Loop (PLL) for multiplying clock source by different factors

- PLL Base Mode

- Prescaler Mode

- PLL Mode

- Power-down mode support

The CGU consists of an oscillator circuit and a PLL. In the XC886/888, the oscillator can be from either of these two sources: the on-chip oscillator (9.6 MHz) or the external oscillator (4 MHz to 12 MHz). The term "oscillator" is used to refer to both on-chip oscillator and external oscillator, unless otherwise stated. After the reset, the on-chip oscillator will be used by default. The external oscillator can be selected via software. In addition, the PLL provides a fail-safe logic to perform oscillator run and loss-of-lock detection. This allows emergency routines to be executed for system recovery or to perform system shut down.

# 3.11 Multiplication/Division Unit

The Multiplication/Division Unit (MDU) provides fast 16-bit multiplication, 16-bit and 32-bit division as well as shift and normalize features. It has been integrated to support the XC886/888 Core in real-time control applications, which require fast mathematical computations.

### Features

- Fast signed/unsigned 16-bit multiplication

- Fast signed/unsigned 32-bit divide by 16-bit and 16-bit divide by 16-bit operations

- 32-bit unsigned normalize operation

- 32-bit arithmetic/logical shift operations

Table 28 specifies the number of clock cycles used for calculation in various operations.

| Operation                | Result | Remainder | No. of Clock Cycles<br>used for calculation |  |  |

|--------------------------|--------|-----------|---------------------------------------------|--|--|

| Signed 32-bit/16-bit     | 32-bit | 16-bit    | 33                                          |  |  |

| Signed 16-bit/16bit      | 16-bit | 16-bit    | 17                                          |  |  |

| Signed 16-bit x 16-bit   | 32-bit | -         | 16                                          |  |  |

| Unsigned 32-bit/16-bit   | 32-bit | 16-bit    | 32                                          |  |  |

| Unsigned 16-bit/16-bit   | 16-bit | 16-bit    | 16                                          |  |  |

| Unsigned 16-bit x 16-bit | 32-bit | -         | 16                                          |  |  |

| 32-bit normalize         | -      | -         | No. of shifts + 1 (Max. 32)                 |  |  |

| 32-bit shift L/R         | -      | -         | No. of shifts + 1 (Max. 32)                 |  |  |

Table 28

MDU Operation Characteristics

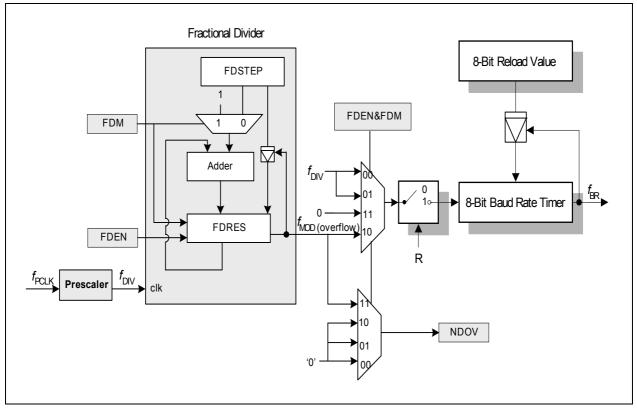

fractional divider) for generating a wide range of baud rates based on its input clock  $f_{PCLK}$ , see **Figure 30**.

### Figure 30 Baud-rate Generator Circuitry

The baud rate timer is a count-down timer and is clocked by either the output of the fractional divider ( $f_{MOD}$ ) if the fractional divider is enabled (FDCON.FDEN = 1), or the output of the prescaler ( $f_{DIV}$ ) if the fractional divider is disabled (FDEN = 0). For baud rate generation, the fractional divider must be configured to fractional divider mode (FDCON.FDM = 0). This allows the baud rate control run bit BCON.R to be used to start or stop the baud rate timer. At each timer underflow, the timer is reloaded with the 8-bit reload value in register BG and one clock pulse is generated for the serial channel.

Enabling the fractional divider in normal divider mode (FDEN = 1 and FDM = 1) stops the baud rate timer and nullifies the effect of bit BCON.R. See **Section 3.14**.

The baud rate ( $f_{BR}$ ) value is dependent on the following parameters:

- Input clock  $f_{PCLK}$

- Prescaling factor (2<sup>BRPRE</sup>) defined by bit field BRPRE in register BCON

- Fractional divider (STEP/256) defined by register FDSTEP (to be considered only if fractional divider is enabled and operating in fractional divider mode)

- 8-bit reload value (BR\_VALUE) for the baud rate timer defined by register BG

## 3.17 Timer 0 and Timer 1

Timer 0 and Timer 1 can function as both timers or counters. When functioning as a timer, Timer 0 and Timer 1 are incremented every machine cycle, i.e. every 2 input clocks (or 2 PCLKs). When functioning as a counter, Timer 0 and Timer 1 are incremented in response to a 1-to-0 transition (falling edge) at their respective external input pins, T0 or T1.

Timer 0 and 1 are fully compatible and can be configured in four different operating modes for use in a variety of applications, see **Table 32**. In modes 0, 1 and 2, the two timers operate independently, but in mode 3, their functions are specialized.

| Mode | Operation                                                                                                                                                                  |  |  |  |  |  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 0    | <b>13-bit timer</b><br>The timer is essentially an 8-bit counter with a divide-by-32 prescaler.<br>This mode is included solely for compatibility with Intel 8048 devices. |  |  |  |  |  |

| 1    | <b>16-bit timer</b><br>The timer registers, TLx and THx, are concatenated to form a 16-bit counter.                                                                        |  |  |  |  |  |

| 2    | <b>8-bit timer with auto-reload</b><br>The timer register TLx is reloaded with a user-defined 8-bit value in THx upon overflow.                                            |  |  |  |  |  |

| 3    | Timer 0 operates as two 8-bit timersThe timer registers, TL0 and TH0, operate as two separate 8-bit counters.Timer 1 is halted and retains its count even if enabled.      |  |  |  |  |  |

#### Table 32Timer 0 and Timer 1 Modes

# Table 36Chip Identification Number (cont'd)

| Product Variant | Chip Identification Number |         |         |  |  |  |  |

|-----------------|----------------------------|---------|---------|--|--|--|--|

|                 | AA-Step                    | AB-Step | AC-Step |  |  |  |  |

| XC888CM-6RFA 5V | 22891503 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC886C-6RFA 5V  | 22891542 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC888C-6RFA 5V  | 22891543 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC886-6RFA 5V   | 22891562 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC888-6RFA 5V   | 22891563 <sub>H</sub>      | -       | -       |  |  |  |  |

### **Electrical Parameters**

| Parameter                                                      | Symbol            |    | Limit Values                |                             | Unit | Test Conditions           |  |

|----------------------------------------------------------------|-------------------|----|-----------------------------|-----------------------------|------|---------------------------|--|

|                                                                |                   |    | min.                        | max.                        |      |                           |  |

| Maximum current out of $V_{\rm SS}$                            |                   |    | -                           | 120                         | mA   | 3)                        |  |

| $V_{\text{DDP}}$ = 3.3 V Range                                 |                   |    |                             |                             |      |                           |  |

| Output low voltage                                             | $V_{OL}$          | CC | _                           | 1.0                         | V    | I <sub>OL</sub> = 8 mA    |  |

|                                                                |                   |    | _                           | 0.4                         | V    | I <sub>OL</sub> = 2.5 mA  |  |

| Output high voltage                                            | V <sub>OH</sub>   | CC | V <sub>DDP</sub> -<br>1.0   | -                           | V    | I <sub>OH</sub> = -8 mA   |  |

|                                                                |                   |    | V <sub>DDP</sub> - 0.4      | -                           | V    | I <sub>OH</sub> = -2.5 mA |  |

| Input low voltage on<br>port pins<br>(all except P0.0 & P0.1)  | V <sub>ILP</sub>  | SR | _                           | $0.3 \times V_{\text{DDP}}$ | V    | CMOS Mode                 |  |

| Input low voltage on P0.0 & P0.1                               | V <sub>ILP0</sub> | SR | -0.2                        | $0.3 \times V_{ m DDP}$     | V    | CMOS Mode                 |  |

| Input low voltage on RESET pin                                 | $V_{ILR}$         | SR | -                           | $0.3 \times V_{\text{DDP}}$ | V    | CMOS Mode                 |  |

| Input low voltage on<br>TMS pin                                | V <sub>ILT</sub>  | SR | -                           | $0.3 \times V_{\text{DDP}}$ | V    | CMOS Mode                 |  |

| Input high voltage on<br>port pins<br>(all except P0.0 & P0.1) | V <sub>IHP</sub>  | SR | $0.7 \times V_{\text{DDP}}$ | -                           | V    | CMOS Mode                 |  |

| Input high voltage on P0.0 & P0.1                              | V <sub>IHP0</sub> | SR | $0.7 \times V_{\text{DDP}}$ | V <sub>DDP</sub>            | V    | CMOS Mode                 |  |

| Input high voltage on RESET pin                                | $V_{IHR}$         | SR | $0.7 \times V_{ m DDP}$     | -                           | V    | CMOS Mode                 |  |

| Input high voltage on<br>TMS pin                               | V <sub>IHT</sub>  | SR | $0.75 \times V_{ m DDP}$    | -                           | V    | CMOS Mode                 |  |

| Input Hysteresis                                               | HYS               | CC | $0.03 \times V_{ m DDP}$    | -                           | V    | CMOS Mode <sup>1)</sup>   |  |

| Input Hysteresis on XTAL1                                      | HYSX              | CC | $0.07 \times V_{ m DDC}$    | -                           | V    | 1)                        |  |

| Input low voltage at XTAL1                                     | V <sub>ILX</sub>  | SR | V <sub>SS</sub> -<br>0.5    | $0.3 \times V_{ m DDC}$     | V    |                           |  |

#### **Electrical Parameters**

### 4.3.2 Output Rise/Fall Times

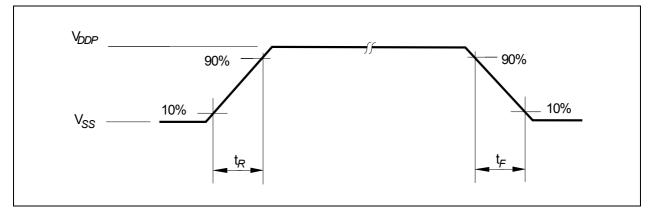

Table 45 provides the characteristics of the output rise/fall times in the XC886/888.

#### Table 45 Output Rise/Fall Times Parameters (Operating Conditions apply)

| Parameter                     | Symbol                          | Limit<br>Values |      | Unit | Test Conditions          |  |

|-------------------------------|---------------------------------|-----------------|------|------|--------------------------|--|

|                               |                                 | min.            | max. |      |                          |  |

| $V_{\rm DDP}$ = 5V Range      |                                 |                 |      |      |                          |  |

| Rise/fall times               | t <sub>R</sub> , t <sub>F</sub> | _               | 10   | ns   | 20 pF. <sup>1)2)3)</sup> |  |

| V <sub>DDP</sub> = 3.3V Range | ·                               |                 |      |      |                          |  |

| Rise/fall times               | t <sub>R</sub> , t <sub>F</sub> | _               | 10   | ns   | 20 pF. <sup>1)2)4)</sup> |  |

|                               |                                 |                 |      |      | •                        |  |

1) Rise/Fall time measurements are taken with 10% - 90% of pad supply.

2) Not all parameters are 100% tested, but are verified by design/characterization and test correlation.

3) Additional rise/fall time valid for  $C_{\rm L}$  = 20pF - 100pF @ 0.125 ns/pF.

4) Additional rise/fall time valid for  $C_{\rm L}$  = 20pF - 100pF @ 0.225 ns/pF.

Figure 43 Rise/Fall Times Parameters

#### **Electrical Parameters**

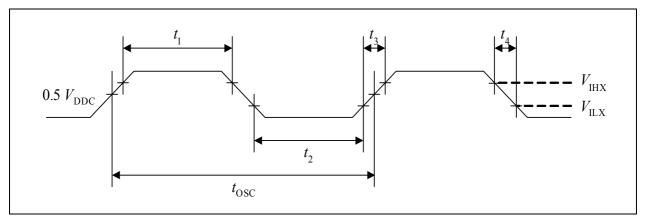

# 4.3.5 External Clock Drive XTAL1

**Table 48** shows the parameters that define the external clock supply for XC886/888. These timing parameters are based on the direct XTAL1 drive of clock input signals. They are not applicable if an external crystal or ceramic resonator is considered.

| Parameter         | Symbol                |    | Lim  | it Values | Unit | <b>Test Conditions</b> |

|-------------------|-----------------------|----|------|-----------|------|------------------------|

|                   |                       |    | Min. | Max.      |      |                        |

| Oscillator period | t <sub>osc</sub>      | SR | 83.3 | 250       | ns   | 1)2)                   |

| High time         | <i>t</i> <sub>1</sub> | SR | 25   | -         | ns   | 2)3)                   |

| Low time          | <i>t</i> <sub>2</sub> | SR | 25   | -         | ns   | 2)3)                   |

| Rise time         | t <sub>3</sub>        | SR | -    | 20        | ns   | 2)3)                   |

| Fall time         | $t_4$                 | SR | -    | 20        | ns   | 2)3)                   |

Table 48

External Clock Drive Characteristics (Operating Conditions apply)

1) The clock input signals with 45-55% duty cycle are used.

2) Not all parameters are 100% tested, but are verified by design/characterization and test correlation.

3) The clock input signal must reach the defined levels  $V_{\rm ILX}$  and  $V_{\rm IHX}$ .

Figure 45 External Clock Drive XTAL1