Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                        |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | XC800                                                                           |

| Core Size                  | 8-Bit                                                                           |

| Speed                      | 24MHz                                                                           |

| Connectivity               | SSI, UART/USART                                                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 34                                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 1.75K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                     |

| Data Converters            | A/D 8x10b                                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 48-LQFP                                                                         |

| Supplier Device Package    | PG-TQFP-48                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/sak-xc886-8ffa-5v-ac |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Edition 2009-07 Published by Infineon Technologies AG 81726 Munich, Germany © 2009 Infineon Technologies AG All Rights Reserved.

#### Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

# 8-Bit

# XC886/888CLM

8-Bit Single Chip Microcontroller

Data Sheet V1.2 2009-07

# Microcontrollers

#### **Summary of Features**

| Table 2Device Profile (cont'd) |

|--------------------------------|

|--------------------------------|

| Sales Type               | Device<br>Type | Program<br>Memory<br>(Kbytes) | Power<br>Supply<br>(V) | Temp-<br>erature<br>(°C) | Quality<br>Profile |

|--------------------------|----------------|-------------------------------|------------------------|--------------------------|--------------------|

| SAK-XC886*/888*-8FFA 3V3 | Flash          | 32                            | 3.3                    | -40 to 125               | Automotive         |

| SAK-XC886*/888*-6FFA 3V3 | Flash          | 24                            | 3.3                    | -40 to 125               | Automotive         |

| SAF-XC886*/888*-8FFA 3V3 | Flash          | 32                            | 3.3                    | -40 to 85                | Automotive         |

| SAF-XC886*/888*-6FFA 3V3 | Flash          | 24                            | 3.3                    | -40 to 85                | Automotive         |

| SAF-XC886*/888*-8FFI 3V3 | Flash          | 32                            | 3.3                    | -40 to 85                | Industrial         |

| SAF-XC886*/888*-6FFI 3V3 | Flash          | 24                            | 3.3                    | -40 to 85                | Industrial         |

- Note: The asterisk (\*) above denotes the device configuration letters from **Table 1**. Corresponding ROM derivatives will be available on request.

- Note: For variants with LIN BSL support, only LIN BSL is available regardless of the availability of the CAN module.

As this document refers to all the derivatives, some description may not apply to a specific product. For simplicity, all versions are referred to by the term XC886/888 throughout this document.

#### **Ordering Information**

The ordering code for Infineon Technologies microcontrollers provides an exact reference to the required product. This ordering code identifies:

- The derivative itself, i.e. its function set, the temperature range, and the supply voltage

- The package and the type of delivery

For the available ordering codes for the XC886/888, please refer to your responsible sales representative or your local distributor.

Note: The ordering codes for the Mask-ROM versions are defined for each product after verification of the respective ROM code.

#### **General Device Information**

# 2 General Device Information

**Chapter 2** contains the block diagram, pin configurations, definitions and functions of the XC886/888.

#### 2.1 Block Diagram

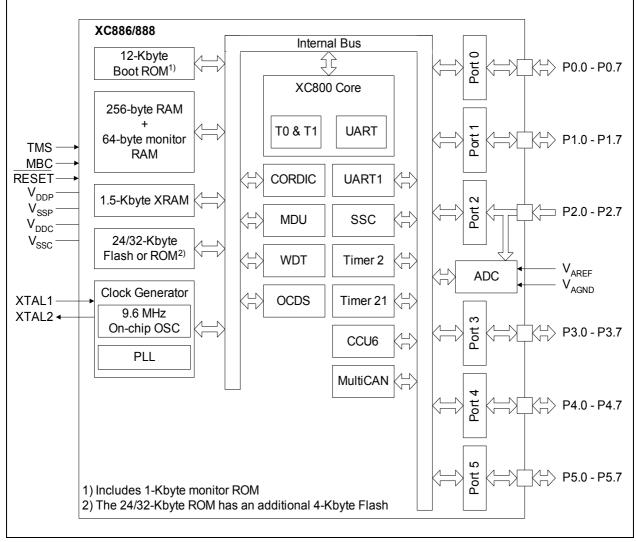

The block diagram of the XC886/888 is shown in Figure 2.

Figure 2 XC886/888 Block Diagram

#### **General Device Information**

# 2.4 Pin Definitions and Functions

The functions and default states of the XC886/888 external pins are provided in Table 3.

| Symbol | Pin Number<br>(TQFP-48/64) | Туре | Reset<br>State | Function                                                   |                                                                                                                                                                                                      |

|--------|----------------------------|------|----------------|------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P0     |                            | I/O  |                | I/O port. It ca<br>for the JTAG                            | B-bit bidirectional general purpose<br>an be used as alternate functions<br>6, CCU6, UART, UART1, Timer 2,<br>ultiCAN and SSC.                                                                       |

| P0.0   | 11/17                      |      | Hi-Z           | TCK_0<br>T12HR_1<br>CC61_1<br>CLKOUT_0<br>RXDO_1           | JTAG Clock Input<br>CCU6 Timer 12 Hardware Run<br>Input<br>Input/Output of<br>Capture/Compare channel 1<br>Clock Output<br>UART Transmit Data Output                                                 |

| P0.1   | 13/21                      |      | Hi-Z           | TDI_0<br>T13HR_1<br>RXD_1<br>RXDC1_0<br>COUT61_1<br>EXF2_1 | JTAG Serial Data Input<br>CCU6 Timer 13 Hardware Run<br>Input<br>UART Receive Data Input<br>MultiCAN Node 1 Receiver Input<br>Output of Capture/Compare<br>channel 1<br>Timer 2 External Flag Output |

| P0.2   | 12/18                      |      | PU             | CTRAP_2<br>TDO_0<br>TXD_1<br>TXDC1_0                       | CCU6 Trap Input<br>JTAG Serial Data Output<br>UART Transmit Data<br>Output/Clock Output<br>MultiCAN Node 1 Transmitter<br>Output                                                                     |

| P0.3   | 48/63                      |      | Hi-Z           | SCK_1<br>COUT63_1<br>RXDO1_0                               | SSC Clock Input/Output<br>Output of Capture/Compare<br>channel 3<br>UART1 Transmit Data Output                                                                                                       |

Table 3

Pin Definitions and Functions

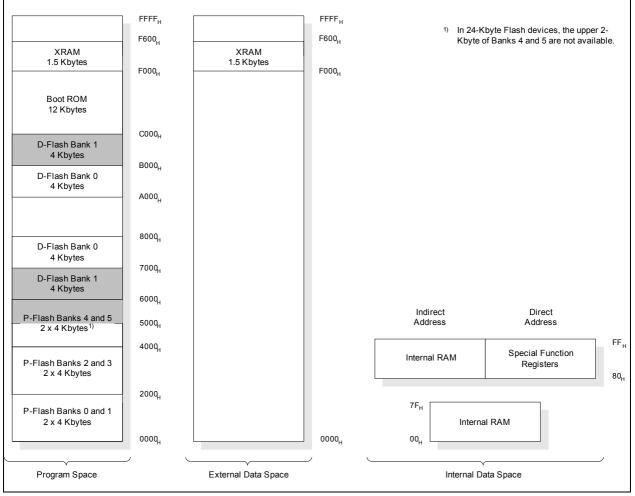

## 3.2 Memory Organization

The XC886/888 CPU operates in the following five address spaces:

- 12 Kbytes of Boot ROM program memory

- 256 bytes of internal RAM data memory

- 1.5 Kbytes of XRAM memory (XRAM can be read/written as program memory or external data memory)

- A 128-byte Special Function Register area

- 24/32 Kbytes of Flash program memory (Flash devices); or 24/32 Kbytes of ROM program memory, with additional 4 Kbytes of Flash (ROM devices)

**Figure 7** illustrates the memory address spaces of the 32-Kbyte Flash devices. For the 24-Kbyte Flash devices, the shaded banks are not available.

Figure 7 Memory Map of XC886/888 Flash Device

For both 24-Kbyte and 32-Kbyte ROM devices, the last four bytes of the ROM from  $7FFC_{H}$  to  $7FFF_{H}$  are reserved for the ROM signature and cannot be used to store user

#### Table 11ADC Register Overview (cont'd)

| Addr            | Register Name                                                | Bit       | 7             | 6               | 5    | 4      | 3    | 2      | 1       | 0    |

|-----------------|--------------------------------------------------------------|-----------|---------------|-----------------|------|--------|------|--------|---------|------|

| CDH             | ADC_LCBR Reset: B7 <sub>H</sub>                              | Bit Field |               | BOU             | IND1 |        |      | BOL    | JND0    |      |

|                 | Limit Check Boundary Register                                | Туре      |               | r               | N    |        |      | r      | w       |      |

| CEH             | ADC_INPCR0 Reset: 00 <sub>H</sub>                            | Bit Field |               |                 |      | S      | тс   |        |         |      |

|                 | Input Class 0 Register                                       | Туре      |               |                 |      | r      | w    |        |         |      |

| CF <sub>H</sub> | ADC_ETRCR Reset: 00 <sub>H</sub><br>External Trigger Control | Bit Field | SYNE<br>N1    | SYNE<br>N0      |      | ETRSEL | 1    |        | ETRSEL0 |      |

|                 | Register                                                     | Туре      | rw            | rw              |      | rw     |      |        | rw      |      |

| RMAP =          | 0, PAGE 1                                                    |           |               |                 | •    |        |      |        |         |      |

| CAH             | ADC_CHCTR0 Reset: 00 <sub>H</sub>                            | Bit Field | 0             |                 | LCC  |        | (    | )      | RESE    | RSEL |

|                 | Channel Control Register 0                                   | Туре      | r             |                 | rw   |        |      | r      | n       | N    |

| св <sub>Н</sub> | ADC_CHCTR1 Reset: 00 <sub>H</sub>                            | Bit Field | 0             |                 | LCC  |        | (    | C      | RESE    | RSEL |

|                 | Channel Control Register 1                                   | Туре      | r             |                 | rw   |        |      | r      | n       | N    |

| сс <sub>Н</sub> | ADC_CHCTR2 Reset: 00 <sub>H</sub>                            | Bit Field | 0             |                 | LCC  |        | (    | )      | RESE    | RSEL |

|                 | Channel Control Register 2                                   | Туре      | r             |                 | rw   |        |      | r      | n       | N    |

| CDH             | ADC_CHCTR3 Reset: 00 <sub>H</sub>                            | Bit Field | 0             |                 | LCC  |        | (    | C      | RESE    | RSEL |

|                 | Channel Control Register 3                                   | Туре      | r             |                 | rw   |        |      | r      | rw      |      |

| CEH             | ADC_CHCTR4 Reset: 00 <sub>H</sub>                            | Bit Field | 0             | LCC             |      |        | (    | )      | RESRSEL |      |

|                 | Channel Control Register 4                                   | Туре      | r             | rw              |      |        |      | r      | n       | N    |

| CFH             | ADC_CHCTR5 Reset: 00 <sub>H</sub>                            | Bit Field | 0             | LCC             |      |        | (    | )      | RESE    | RSEL |

|                 | Channel Control Register 5                                   | Туре      | r             | rw              |      |        |      | r      | n       | N    |

| D2 <sub>H</sub> | ADC_CHCTR6 Reset: 00 <sub>H</sub>                            | Bit Field | 0             |                 | LCC  |        | (    | C      | RESE    | RSEL |

|                 | Channel Control Register 6                                   | Туре      | r             |                 | rw   |        | r    |        | n       | N    |

| D3 <sub>H</sub> | ADC_CHCTR7 Reset: 00 <sub>H</sub>                            | Bit Field | 0             |                 | LCC  | 0      |      | 0 RESR |         | RSEL |

|                 | Channel Control Register 7                                   | Туре      | r             |                 | rw   | r      |      | r      | n       | N    |

| RMAP =          | 0, PAGE 2                                                    |           | •             |                 |      |        |      |        |         |      |

| CA <sub>H</sub> | ADC_RESR0L Reset: 00 <sub>H</sub>                            | Bit Field | RES           | SULT            | 0    | VF     | DRC  |        | CHNR    |      |

|                 | Result Register 0 Low                                        | Туре      | r             | h               | r    | rh     | rh   |        | rh      |      |

| св <sub>Н</sub> | ADC_RESR0H Reset: 00 <sub>H</sub>                            | Bit Field |               |                 |      | RES    | SULT |        |         |      |

|                 | Result Register 0 High                                       | Туре      |               |                 |      | I      | ħ    |        |         |      |

| сс <sub>Н</sub> | ADC_RESR1L Reset: 00 <sub>H</sub>                            | Bit Field | RES           | SULT            | 0    | VF     | DRC  |        | CHNR    |      |

|                 | Result Register 1 Low                                        | Туре      | r             | 'n              | r    | rh     | rh   |        | rh      |      |

| CDH             | ADC_RESR1H Reset: 00 <sub>H</sub>                            | Bit Field |               |                 |      | RES    | SULT |        |         |      |

|                 | Result Register 1 High                                       | Туре      |               |                 |      |        | 'n   |        |         |      |

| CEH             | ADC_RESR2L Reset: 00 <sub>H</sub>                            | Bit Field | RES           | RESULT 0 VF DRC |      |        |      |        | CHNR    |      |

|                 | Result Register 2 Low                                        | Туре      | rh r rh rh rh |                 |      |        |      | rh     |         |      |

| CF <sub>H</sub> | ADC_RESR2H Reset: 00 <sub>H</sub>                            | Bit Field | Field RESULT  |                 |      |        |      |        |         |      |

|                 | Result Register 2 High                                       | Туре      |               |                 |      |        | ħ    |        |         |      |

| D2 <sub>H</sub> | ADC_RESR3L Reset: 00 <sub>H</sub>                            | Bit Field | RES           | SULT            | 0    | VF     | DRC  | CHNR   |         |      |

|                 | Result Register 3 Low                                        | Туре      | r             | 'n              | r    | rh     | rh   |        | rh      |      |

## 3.2.4.8 Timer 2 Registers

The Timer 2 SFRs can be accessed in the standard memory area (RMAP = 0).

| Addr            | Register Name                                               | Bit       | 7          | 6          | 5           | 4    | 3         | 2         | 1 | 0 |  |

|-----------------|-------------------------------------------------------------|-----------|------------|------------|-------------|------|-----------|-----------|---|---|--|

| RMAP =          | = 0                                                         |           |            |            |             |      |           |           |   |   |  |

| c₀ <sub>H</sub> | T2_T2CON Reset: 00 <sub>H</sub><br>Timer 2 Control Register | Bit Field | TF2        | EXF2       | (           | )    | EXEN<br>2 |           |   |   |  |

|                 |                                                             | Туре      | rwh        | rwh        | I           | r    | rw        | rw rwh rw |   |   |  |

| C1 <sub>H</sub> | T2_T2MOD Reset: 00 <sub>H</sub><br>Timer 2 Mode Register    | Bit Field | T2RE<br>GS | T2RH<br>EN | EDGE<br>SEL | PREN |           | T2PRE     |   |   |  |

|                 |                                                             | Туре      | rw         | rw         | rw          | rw   | rw        | rw rw rw  |   |   |  |

| C2 <sub>H</sub> | T2_RC2L Reset: 00 <sub>H</sub>                              | Bit Field |            |            |             | R    | C2        |           |   |   |  |

|                 | Timer 2 Reload/Capture<br>Register Low                      | Туре      |            |            |             | rv   | vh        |           |   |   |  |

| C3 <sub>H</sub> | T2_RC2H Reset: 00 <sub>H</sub>                              | Bit Field |            |            |             | R    | C2        |           |   |   |  |

|                 | Timer 2 Reload/Capture<br>Register High                     | Туре      |            |            |             | rv   | vh        |           |   |   |  |

| C4 <sub>H</sub> | T2_T2L Reset: 00 <sub>H</sub>                               | Bit Field |            |            |             | TH   | IL2       |           |   |   |  |

|                 | Timer 2 Register Low                                        | Туре      | rwh        |            |             |      |           |           |   |   |  |

| C5 <sub>H</sub> | T2_T2H Reset: 00 <sub>H</sub>                               | Bit Field |            | THL2       |             |      |           |           |   |   |  |

|                 | Timer 2 Register High                                       | Туре      |            |            |             | rv   | vh        |           |   |   |  |

#### Table 12T2 Register Overview

# 3.2.4.9 Timer 21 Registers

The Timer 21 SFRs can be accessed in the mapped memory area (RMAP = 1).

#### Table 13T21 Register Overview

|                 | 0                                           |           |            |            |             |      |           |            |    |    |  |

|-----------------|---------------------------------------------|-----------|------------|------------|-------------|------|-----------|------------|----|----|--|

| Addr            | Register Name                               | Bit       | 7          | 6          | 5           | 4    | 3         | 2          | 1  | 0  |  |

| RMAP =          | = 1                                         |           |            |            |             |      |           |            |    |    |  |

| C0H             | T21_T2CONReset: 00HTimer 2 Control Register | Bit Field | TF2        | EXF2       | (           | 0    | EXEN<br>2 | CP/<br>RL2 |    |    |  |

|                 |                                             | Туре      | rwh        | rwh        | I           | r    | rw        | rw rwh rw  |    |    |  |

| C1 <sub>H</sub> | T21_T2MODReset: 00Timer 2 Mode Register     | Bit Field | T2RE<br>GS | T2RH<br>EN | EDGE<br>SEL | PREN |           | DCEN       |    |    |  |

|                 |                                             | Туре      | rw         | rw         | rw          | rw   | rw        | rw         | rw | rw |  |

| C2 <sub>H</sub> | T21_RC2L Reset: 00 <sub>H</sub>             | Bit Field |            |            |             | R    | C2        |            |    |    |  |

|                 | Timer 2 Reload/Capture<br>Register Low      | Туре      |            |            |             | n    | vh        |            |    |    |  |

| C3 <sub>H</sub> | T21_RC2H Reset: 00 <sub>H</sub>             | Bit Field |            |            |             | R    | C2        |            |    |    |  |

|                 | Timer 2 Reload/Capture<br>Register High     | Туре      | rwh        |            |             |      |           |            |    |    |  |

| C4 <sub>H</sub> | T21_T2L Reset: 00 <sub>H</sub>              | Bit Field | THL2       |            |             |      |           |            |    |    |  |

|                 | Timer 2 Register Low                        | Туре      |            |            |             | ٢٧   | vh        |            |    |    |  |

#### Table 13T21 Register Overview (cont'd)

| Addr            | Register Name         | Bit       | 7    | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-----------------|-----------------------|-----------|------|---|---|---|---|---|---|---|--|

| C5 <sub>H</sub> | - 1                   | Bit Field | THL2 |   |   |   |   |   |   |   |  |

|                 | Timer 2 Register High | Туре      | rwh  |   |   |   |   |   |   |   |  |

#### 3.2.4.10 CCU6 Registers

The CCU6 SFRs can be accessed in the standard memory area (RMAP = 0).

#### Table 14 CCU6 Register Overview

| Addr            | Register Name                                                                | Bit       | 7          | 6          | 5          | 4          | 3          | 2          | 1          | 0          |

|-----------------|------------------------------------------------------------------------------|-----------|------------|------------|------------|------------|------------|------------|------------|------------|

| RMAP =          | = 0                                                                          |           |            |            |            |            |            |            |            |            |

| A3 <sub>H</sub> | CCU6_PAGE Reset: 00 <sub>H</sub>                                             | Bit Field | C          | P          | ST         | NR         | 0          |            | PAGE       |            |

|                 | Page Register                                                                | Туре      | ١          | N          | ١          | N          | r          |            | rw         |            |

| RMAP =          | = 0, PAGE 0                                                                  |           |            |            |            |            |            |            |            |            |

| 9A <sub>H</sub> | CCU6_CC63SRL Reset: 00 <sub>H</sub><br>Capture/Compare Shadow Register       | Bit Field |            |            |            | CC6        | 63SL       |            |            |            |

|                 | for Channel CC63 Low                                                         | Туре      |            |            |            | r          | w          |            |            |            |

| 9B <sub>H</sub> | CCU6_CC63SRH Reset: 00 <sub>H</sub>                                          | Bit Field |            |            |            | CC6        | 3SH        |            |            |            |

|                 | Capture/Compare Shadow Register<br>for Channel CC63 High                     | Туре      |            |            |            | r          | w          |            |            |            |

| 9CH             | CCU6_TCTR4L Reset: 00 <sub>H</sub><br>Timer Control Register 4 Low           | Bit Field | T12<br>STD | T12<br>STR | (          | 0          | DT<br>RES  | T12<br>RES | T12R<br>S  | T12R<br>R  |

|                 |                                                                              | Туре      | w          | w          |            | r          | w          | w          | w          | w          |

| 9D <sub>H</sub> | CCU6_TCTR4H Reset: 00 <sub>H</sub><br>Timer Control Register 4 High          | Bit Field | T13<br>STD | T13<br>STR |            |            |            |            |            | T13R<br>R  |

|                 |                                                                              | Туре      | w          | w          |            | r w w      |            |            |            | w          |

| 9E <sub>H</sub> | CCU6_MCMOUTSL Reset: 00 <sub>H</sub><br>Multi-Channel Mode Output Shadow     | Bit Field | STRM<br>CM | 0          |            |            | MC         | MPS        |            |            |

|                 | Register Low                                                                 | Туре      | w          | r          |            |            | r          | w          |            |            |

| 9F <sub>H</sub> | CCU6_MCMOUTSH Reset: 00 <sub>H</sub><br>Multi-Channel Mode Output Shadow     | Bit Field | STRH<br>P  | 0          |            | CURHS      |            |            | EXPHS      |            |

|                 | Register High                                                                | Туре      | w          | r          |            | rw         |            |            | rw         |            |

| A4 <sub>H</sub> | CCU6_ISRL Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Status         | Bit Field | RT12<br>PM | RT12<br>OM | RCC6<br>2F | RCC6<br>2R | RCC6<br>1F | RCC6<br>1R | RCC6<br>0F | RCC6<br>0R |

|                 | Reset Register Low                                                           | Туре      | w          | w          | w          | w          | w          | w          | w          | w          |

| A5 <sub>H</sub> | CCU6_ISRH Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Status         | Bit Field | RSTR       | RIDLE      | RWH<br>E   | RCHE       | 0          | RTRP<br>F  | RT13<br>PM | RT13<br>CM |

|                 | Reset Register High                                                          | Туре      | w          | w          | w          | w          | r          | w          | w          | w          |

| A6 <sub>H</sub> | CCU6_CMPMODIFL Reset: 00 <sub>H</sub><br>Compare State Modification Register | Bit Field | 0          | MCC6<br>3S |            |            |            |            |            | MCC6<br>0S |

|                 | Low                                                                          | Туре      | r          | w          | r w w      |            |            |            | w          | w          |

| а7 <sub>Н</sub> | CCU6_CMPMODIFH Reset: 00 <sub>H</sub><br>Compare State Modification Register | Bit Field | 0          | MCC6<br>3R |            | 0          |            | MCC6<br>2R | MCC6<br>1R | MCC6<br>0R |

|                 | High                                                                         | Туре      | r          | w          |            | r          |            | w          | w          | w          |

# Table 14CCU6 Register Overview (cont'd)

| Addr            | Register Name                                                         | Bit       | 7   | 6    | 5         | 4    | 3          | 2        | 1        | 0    |

|-----------------|-----------------------------------------------------------------------|-----------|-----|------|-----------|------|------------|----------|----------|------|

| FA <sub>H</sub> | CCU6_CC60SRL Reset: 00 <sub>H</sub>                                   | Bit Field |     |      | <u> </u>  | CC6  | OSL        | <u> </u> | <u> </u> |      |

|                 | Capture/Compare Shadow Register<br>for Channel CC60 Low               | Туре      |     |      |           | rv   | vh         |          |          |      |

| FB <sub>H</sub> | CCU6_CC60SRH Reset: 00 <sub>H</sub>                                   | Bit Field |     |      |           | CC6  | 0SH        |          |          |      |

|                 | Capture/Compare Shadow Register<br>for Channel CC60 High              | Туре      |     |      |           | rv   | vh         |          |          |      |

| FC <sub>H</sub> | CCU6_CC61SRL Reset: 00 <sub>H</sub>                                   | Bit Field |     |      |           | CC6  | 51SL       |          |          |      |

|                 | Capture/Compare Shadow Register<br>for Channel CC61 Low               | Туре      |     |      |           | rv   | vh         |          |          |      |

| FD <sub>H</sub> | CCU6_CC61SRH Reset: 00 <sub>H</sub>                                   | Bit Field |     |      |           | CC6  | 1SH        |          |          |      |

|                 | Capture/Compare Shadow Register<br>for Channel CC61 High              | Туре      |     |      |           | rv   | vh         |          |          |      |

| Fe <sub>H</sub> | CCU6_CC62SRL Reset: 00 <sub>H</sub>                                   | Bit Field |     |      |           | CC6  | 2SL        |          |          |      |

|                 | Capture/Compare Shadow Register<br>for Channel CC62 Low               | Туре      |     |      |           | rv   | vh         |          |          |      |

| FF <sub>H</sub> | CCU6_CC62SRH Reset: 00 <sub>H</sub>                                   | Bit Field |     |      |           | CC6  | 2SH        |          |          |      |

|                 | Capture/Compare Shadow Register<br>for Channel CC62 High              | Туре      |     |      |           | rv   | vh         |          |          |      |

| RMAP =          | 0, PAGE 1                                                             |           |     |      |           |      |            |          |          |      |

| 9A <sub>H</sub> | CCU6_CC63RL Reset: 00 <sub>H</sub>                                    | Bit Field |     |      |           | CC6  | 3VL        |          |          |      |

|                 | Capture/Compare Register for<br>Channel CC63 Low                      | Туре      |     |      |           | r    | h          |          |          |      |

| 98 <sub>H</sub> | CCU6_CC63RH Reset: 00 <sub>H</sub>                                    | Bit Field |     |      |           | CC6  | 3VH        |          |          |      |

|                 | Capture/Compare Register for<br>Channel CC63 High                     | Туре      |     |      |           | r    | h          |          |          |      |

| 9CH             | CCU6_T12PRL Reset: 00 <sub>H</sub>                                    | Bit Field |     |      |           | T12  | PVL        |          |          |      |

|                 | Timer T12 Period Register Low                                         | Туре      |     |      |           | rv   | vh         |          |          |      |

| 9D <sub>H</sub> | CCU6_T12PRH Reset: 00 <sub>H</sub><br>Timer T12 Period Register High  | Bit Field |     |      |           | T12  | PVH        |          |          |      |

|                 |                                                                       | Туре      |     |      |           | rv   | vh         |          |          |      |

| 9E <sub>H</sub> | CCU6_T13PRLReset: 00HTimer T13 Period Register Low                    | Bit Field |     |      |           | T13  | PVL        |          |          |      |

|                 |                                                                       | Туре      |     |      |           | rv   | vh         |          |          |      |

| 9F <sub>H</sub> | CCU6_T13PRH Reset: 00 <sub>H</sub><br>Timer T13 Period Register High  | Bit Field |     |      |           | T13  | PVH        |          |          |      |

|                 |                                                                       | Туре      |     |      |           | rv   | vh         |          |          |      |

| A4 <sub>H</sub> | CCU6_T12DTCL Reset: 00 <sub>H</sub><br>Dead-Time Control Register for | Bit Field |     |      |           | D    | ΓM         |          |          |      |

|                 | Timer T12 Low                                                         | Туре      |     |      |           | r    | N          |          |          |      |

| А5 <sub>Н</sub> | CCU6_T12DTCH Reset: 00 <sub>H</sub><br>Dead-Time Control Register for | Bit Field | 0   | DTR2 | DTR1      | DTR0 | 0          | DTE2     | DTE1     | DTE0 |

|                 | Timer T12 High                                                        | Туре      | r   | rh   | rh        | rh   | r          | rw       | rw       | rw   |

| A6 <sub>H</sub> | CCU6_TCTR0L Reset: 00 <sub>H</sub><br>Timer Control Register 0 Low    | Bit Field | СТМ | CDIR | STE1<br>2 | T12R | T12<br>PRE |          | T12CLK   |      |

|                 |                                                                       | Туре      | rw  | rh   | rh        | rh   | rw         |          | rw       |      |

| А7 <sub>Н</sub> | CCU6_TCTR0H Reset: 00 <sub>H</sub><br>Timer Control Register 0 High   | Bit Field |     | 0    | STE1<br>3 | T13R | T13<br>PRE |          | T13CLK   |      |

|                 |                                                                       | Туре      |     | r    | rh        | rh   | rw         |          | rw       |      |

| FA <sub>H</sub> | CCU6_CC60RL Reset: 00 <sub>H</sub>                                    | Bit Field |     |      |           | CC6  | 60VL       |          |          |      |

|                 | Capture/Compare Register for<br>Channel CC60 Low                      | Туре      |     |      |           | r    | h          |          |          |      |

#### Table 14CCU6 Register Overview (cont'd)

| Addr            | Register Name                                                       | Bit       | 7     | 6            | 5            | 4          | 3            | 2          | 1            | 0          |

|-----------------|---------------------------------------------------------------------|-----------|-------|--------------|--------------|------------|--------------|------------|--------------|------------|

| Fe <sub>H</sub> | CCU6_CMPSTATL Reset: 00 <sub>H</sub><br>Compare State Register Low  | Bit Field | 0     | CC63<br>ST   | CC<br>POS2   | CC<br>POS1 | CC<br>POS0   | CC62<br>ST | CC61<br>ST   | CC60<br>ST |

|                 |                                                                     | Туре      | r     | rh           | rh           | rh         | rh           | rh         | rh           | rh         |

| FF <sub>H</sub> | CCU6_CMPSTATH Reset: 00 <sub>H</sub><br>Compare State Register High | Bit Field | T13IM | COUT<br>63PS | COUT<br>62PS | CC62<br>PS | COUT<br>61PS | CC61<br>PS | COUT<br>60PS | CC60<br>PS |

|                 |                                                                     | Туре      | rwh   | rwh          | rwh          | rwh        | rwh          | rwh        | rwh          | rwh        |

#### 3.2.4.11 UART1 Registers

The UART1 SFRs can be accessed in the mapped memory area (RMAP = 1).

#### Table 15 UART1 Register Overview

| Addr            | Register Name                          | Bit       | 7         | 6                   | 5   | 4    | 3     | 2    | 1   | 0    |  |  |  |    |  |  |  |

|-----------------|----------------------------------------|-----------|-----------|---------------------|-----|------|-------|------|-----|------|--|--|--|----|--|--|--|

| RMAP =          | = 1                                    | 1         |           |                     |     |      |       |      |     | 1    |  |  |  |    |  |  |  |

| C8 <sub>H</sub> | SCON Reset: 00 <sub>H</sub>            | Bit Field | SM0       | SM1                 | SM2 | REN  | TB8   | RB8  | TI  | RI   |  |  |  |    |  |  |  |

|                 | Serial Channel Control Register        | Туре      | rw        | rw rw rw rw rwh rwh |     |      |       |      |     | rwh  |  |  |  |    |  |  |  |

| C9 <sub>H</sub> | SBUF Reset: 00 <sub>H</sub>            | Bit Field | VAL       |                     |     |      |       |      |     |      |  |  |  |    |  |  |  |

|                 | Serial Data Buffer Register            | Туре      | rwh       |                     |     |      |       |      |     |      |  |  |  |    |  |  |  |

| са <sub>Н</sub> | BCON Reset: 00 <sub>H</sub>            | Bit Field | 0 BRPRE R |                     |     |      |       |      |     | 0    |  |  |  | R  |  |  |  |

|                 | Baud Rate Control Register             | Туре      | r rw rw   |                     |     |      |       |      |     | r    |  |  |  | rw |  |  |  |

| св <sub>Н</sub> | BG Reset: 00 <sub>H</sub>              | Bit Field |           |                     |     | BR_V | 'ALUE |      |     |      |  |  |  |    |  |  |  |

|                 | Baud Rate Timer/Reload<br>Register     | Туре      |           |                     |     | rv   | vh    |      |     |      |  |  |  |    |  |  |  |

| сс <sub>Н</sub> | FDCON Reset: 00 <sub>H</sub>           | Bit Field |           |                     | 0   |      |       | NDOV | FDM | FDEN |  |  |  |    |  |  |  |

|                 | Fractional Divider Control<br>Register | Туре      |           |                     | r   |      |       | rwh  | rw  | rw   |  |  |  |    |  |  |  |

| CD <sub>H</sub> | FDSTEP Reset: 00 <sub>H</sub>          | Bit Field |           |                     |     | ST   | ΈP    |      |     |      |  |  |  |    |  |  |  |

|                 | Fractional Divider Reload<br>Register  | Туре      | rw        |                     |     |      |       |      |     |      |  |  |  |    |  |  |  |

| Ceh             | FDRES Reset: 00 <sub>H</sub>           | Bit Field |           |                     |     | RES  | SULT  |      |     |      |  |  |  |    |  |  |  |

|                 | Fractional Divider Result<br>Register  | Туре      |           |                     |     | r    | h     |      |     |      |  |  |  |    |  |  |  |

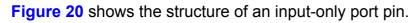

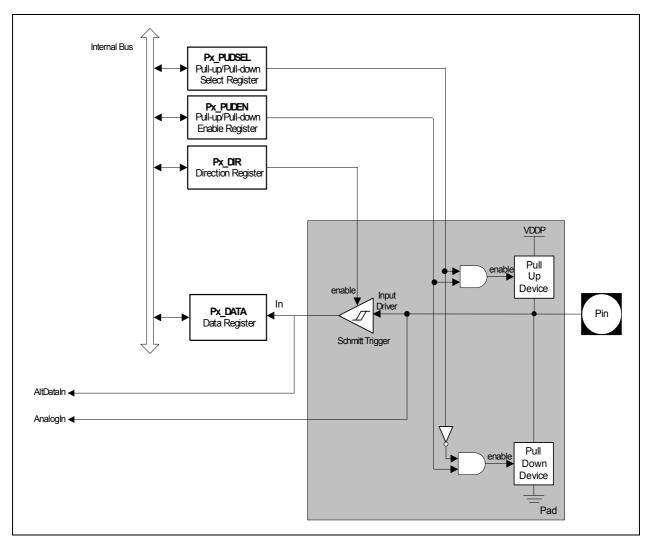

Figure 20 General Structure of Input Port

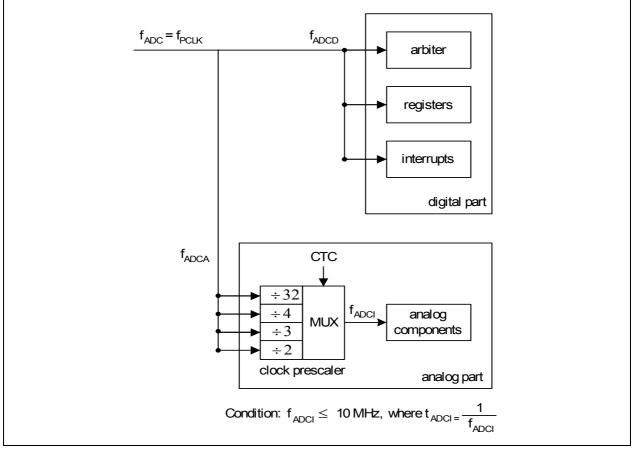

GLOBCTR. A prescaling ratio of 32 can be selected when the maximum performance of the ADC is not required.

#### Figure 35 ADC Clocking Scheme

For module clock  $f_{ADC}$  = 24 MHz, the analog clock  $f_{ADCI}$  frequency can be selected as shown in **Table 34**.

| Table 34 | f <sub>ADCI</sub> Frequency Selection |

|----------|---------------------------------------|

|----------|---------------------------------------|

| Module Clock $f_{ADC}$ | СТС                       | Prescaling Ratio | Analog Clock $f_{ADCI}$ |

|------------------------|---------------------------|------------------|-------------------------|

| 24 MHz                 | 00 <sub>B</sub>           | ÷ 2              | 12 MHz (N.A)            |

|                        | 01 <sub>B</sub>           | ÷ 3              | 8 MHz                   |

|                        | 10 <sub>B</sub>           | ÷ 4              | 6 MHz                   |

|                        | 11 <sub>B</sub> (default) | ÷ 32             | 750 kHz                 |

As  $f_{\rm ADCI}$  cannot exceed 10 MHz, bit field CTC should not be set to  $00_{\rm B}$  when  $f_{\rm ADC}$  is 24 MHz. During slow-down mode where  $f_{\rm ADC}$  may be reduced to 12 MHz, 6 MHz etc., CTC can be set to  $00_{\rm B}$  as long as the divided analog clock  $f_{\rm ADCI}$  does not exceed 10 MHz.

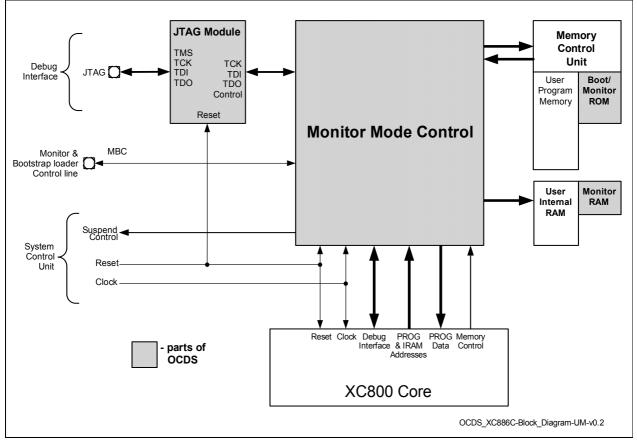

#### 3.22.1 JTAG ID Register

This is a read-only register located inside the JTAG module, and is used to recognize the device(s) connected to the JTAG interface. Its content is shifted out when INSTRUCTION register contains the IDCODE command (opcode  $04_H$ ), and the same is also true immediately after reset.

The JTAG ID register contents for the XC886/888 Flash devices are given in Table 35.

| Device Type | Device Name    | JTAG ID                |  |

|-------------|----------------|------------------------|--|

| Flash       | XC886/888*-8FF | 1012 0083 <sub>H</sub> |  |

|             | XC886/888*-6FF | 1012 5083 <sub>H</sub> |  |

| ROM         | XC886/888*-8RF | 1013 C083 <sub>H</sub> |  |

|             | XC886/888*-6RF | 1013 D083 <sub>H</sub> |  |

#### Table 35JTAG ID Summary

Note: The asterisk (\*) above denotes all possible device configurations.

103

#### Table 36Chip Identification Number (cont'd)

| Product Variant   | Chip Identification Number |                       |                       |  |  |  |  |  |

|-------------------|----------------------------|-----------------------|-----------------------|--|--|--|--|--|

|                   | AA-Step                    | AB-Step               | AC-Step               |  |  |  |  |  |

| XC886-6FFA 3V3    | -                          | 095D1562 <sub>H</sub> | 0B5D1562 <sub>H</sub> |  |  |  |  |  |

| XC888-6FFA 3V3    | -                          | 095D1563 <sub>н</sub> | 0B5D1563 <sub>H</sub> |  |  |  |  |  |

| XC886CLM-8FFA 5V  | -                          | 09900102 <sub>H</sub> | 0B900102 <sub>H</sub> |  |  |  |  |  |

| XC888CLM-8FFA 5V  | -                          | 09900103 <sub>H</sub> | 0B900103 <sub>H</sub> |  |  |  |  |  |

| XC886LM-8FFA 5V   | -                          | 09900122 <sub>H</sub> | 0B900122 <sub>H</sub> |  |  |  |  |  |

| XC888LM-8FFA 5V   | -                          | 09900123 <sub>H</sub> | 0B900123 <sub>H</sub> |  |  |  |  |  |

| XC886CLM-6FFA 5V  | -                          | 09951502 <sub>H</sub> | 0B951502 <sub>H</sub> |  |  |  |  |  |

| XC888CLM-6FFA 5V  | -                          | 09951503 <sub>Н</sub> | 0B951503 <sub>H</sub> |  |  |  |  |  |

| XC886LM-6FFA 5V   | -                          | 09951522 <sub>H</sub> | 0B951522 <sub>H</sub> |  |  |  |  |  |

| XC888LM-6FFA 5V   | -                          | 09951523 <sub>Н</sub> | 0B951523 <sub>H</sub> |  |  |  |  |  |

| XC886CM-8FFA 5V   | -                          | 09980102 <sub>H</sub> | 0B980102 <sub>H</sub> |  |  |  |  |  |

| XC888CM-8FFA 5V   | -                          | 09980103 <sub>H</sub> | 0B980103 <sub>H</sub> |  |  |  |  |  |

| XC886C-8FFA 5V    | -                          | 09980142 <sub>H</sub> | 0B980142 <sub>H</sub> |  |  |  |  |  |

| XC888C-8FFA 5V    | -                          | 09980143 <sub>H</sub> | 0B980143 <sub>H</sub> |  |  |  |  |  |

| XC886-8FFA 5V     | -                          | 09980162 <sub>H</sub> | 0B980162 <sub>H</sub> |  |  |  |  |  |

| XC888-8FFA 5V     | -                          | 09980163 <sub>H</sub> | 0B980163 <sub>H</sub> |  |  |  |  |  |

| XC886CM-6FFA 5V   | -                          | 099D1502 <sub>H</sub> | 0B9D1502 <sub>H</sub> |  |  |  |  |  |

| XC888CM-6FFA 5V   | -                          | 099D1503 <sub>H</sub> | 0B9D1503 <sub>H</sub> |  |  |  |  |  |

| XC886C-6FFA 5V    | -                          | 099D1542 <sub>H</sub> | 0B9D1542 <sub>H</sub> |  |  |  |  |  |

| XC888C-6FFA 5V    | -                          | 099D1543 <sub>H</sub> | 0B9D1543 <sub>H</sub> |  |  |  |  |  |

| XC886-6FFA 5V     | -                          | 099D1562 <sub>H</sub> | 0B9D1562 <sub>H</sub> |  |  |  |  |  |

| XC888-6FFA 5V     | -                          | 099D1563 <sub>H</sub> | 0B9D1563 <sub>H</sub> |  |  |  |  |  |

| ROM Devices       | ·                          |                       | ·                     |  |  |  |  |  |

| XC886CLM-8RFA 3V3 | 22400502 <sub>H</sub>      | -                     | -                     |  |  |  |  |  |

| XC888CLM-8RFA 3V3 | 22400503 <sub>H</sub>      | -                     | -                     |  |  |  |  |  |

| XC886LM-8RFA 3V3  | 22400522 <sub>H</sub>      | -                     | -                     |  |  |  |  |  |

| XC888LM-8RFA 3V3  | 22400523 <sub>H</sub>      | -                     | -                     |  |  |  |  |  |

| XC886CLM-6RFA 3V3 | 22411502 <sub>H</sub>      | -                     | -                     |  |  |  |  |  |

| XC888CLM-6RFA 3V3 | 22411503 <sub>H</sub>      | -                     | -                     |  |  |  |  |  |

Table 37

#### **Electrical Parameters**

#### **Operating Conditions** 4.1.3

The following operating conditions must not be exceeded in order to ensure correct operation of the XC886/888. All parameters mentioned in the following table refer to these operating conditions, unless otherwise noted.

|             | operating condition raranteers |        |       |        |      |                     |  |  |  |

|-------------|--------------------------------|--------|-------|--------|------|---------------------|--|--|--|

| Parameter   |                                | Symbol | Limit | Values | Unit | Notes/<br>Condition |  |  |  |

|             |                                |        | min.  | max.   |      |                     |  |  |  |

| Distigation |                                | 17     | 4 5   |        | 11   |                     |  |  |  |

**Operating Condition Parameters**

|                                      | •                |      |       |     |                   |  |

|--------------------------------------|------------------|------|-------|-----|-------------------|--|

|                                      |                  | min. | max.  |     | Conditions        |  |

| Digital power supply voltage         | $V_{DDP}$        | 4.5  | 5.5   | V   | 5V Device         |  |

| Digital power supply voltage         | V <sub>DDP</sub> | 3.0  | 3.6   | V   | 3.3V Device       |  |

| Digital ground voltage               | V <sub>SS</sub>  | 0    |       | V   |                   |  |

| Digital core supply voltage          | V <sub>DDC</sub> | 2.3  | 2.7   | V   |                   |  |

| System Clock Frequency <sup>1)</sup> | $f_{\rm SYS}$    | 88.8 | 103.2 | MHz |                   |  |

| Ambient temperature                  | T <sub>A</sub>   | -40  | 85    | °C  | SAF-<br>XC886/888 |  |

|                                      |                  | -40  | 125   | °C  | SAK-<br>XC886/888 |  |

1)  $f_{SYS}$  is the PLL output clock. During normal operating mode, CPU clock is  $f_{SYS}$  / 4. Please refer to Figure 26 for detailed description.

#### **Electrical Parameters**

#### Table 38 Input/Output Characteristics (Operating Conditions apply) (cont'd)

| Parameter                                                                      | Symbol                |    | Limit                   | Values                 | Unit | Test Conditions                                   |  |

|--------------------------------------------------------------------------------|-----------------------|----|-------------------------|------------------------|------|---------------------------------------------------|--|

|                                                                                |                       |    |                         | min. max.              |      |                                                   |  |

| Input high voltage at XTAL1                                                    | V <sub>IHX</sub>      | SR | $0.7 \times V_{ m DDC}$ | V <sub>DDC</sub> + 0.5 | V    |                                                   |  |

| Pull-up current                                                                | $I_{\rm PU}$          | SR | _                       | -5                     | μA   | $V_{\mathrm{IHP,min}}$                            |  |

|                                                                                |                       |    | -50                     | _                      | μA   | $V_{ILP,max}$                                     |  |

| Pull-down current                                                              | $I_{\rm PD}$          | SR | -                       | 5                      | μA   | $V_{ILP,max}$                                     |  |

|                                                                                |                       |    | 50                      | _                      | μA   | V <sub>IHP,min</sub>                              |  |

| Input leakage current                                                          | I <sub>OZ1</sub>      | СС | -1                      | 1                      | μA   | $0 < V_{IN} < V_{DDP}, T_A \le 125^{\circ}C^{2)}$ |  |

| Input current at XTAL1                                                         | $I_{ILX}$             | CC | - 10                    | 10                     | μA   |                                                   |  |

| Overload current on any pin                                                    | I <sub>OV</sub>       | SR | -5                      | 5                      | mA   |                                                   |  |

| Absolute sum of overload currents                                              | $\Sigma  I_{\rm OV} $ | SR | -                       | 25                     | mA   | 3)                                                |  |

| Voltage on any pin during $V_{\rm DDP}$ power off                              | V <sub>PO</sub>       | SR | -                       | 0.3                    | V    | 4)                                                |  |

| Maximum current per pin (excluding $V_{\text{DDP}}$ and $V_{\text{SS}}$ )      | I <sub>M</sub> SR     | SR | -                       | 15                     | mA   |                                                   |  |

| Maximum current for all pins (excluding $V_{\text{DDP}}$ and $V_{\text{SS}}$ ) | $\Sigma  I_{M} $      | SR | -                       | 90                     | mA   |                                                   |  |

| Maximum current into $V_{\text{DDP}}$                                          | I <sub>MVDDP</sub>    | SR | -                       | 120                    | mA   | 3)                                                |  |

| Maximum current out of $V_{\rm SS}$                                            | I <sub>MVSS</sub>     | SR | -                       | 120                    | mA   | 3)                                                |  |

Not subjected to production test, verified by design/characterization. Hysteresis is implemented to avoid meta stable states and switching due to internal ground bounce. It cannot be guaranteed that it suppresses switching due to external system noise.

2) An additional error current ( $I_{INJ}$ ) will flow if an overload current flows through an adjacent pin. TMS pin and RESET pin have internal pull devices and are not included in the input leakage current characteristic.

3) Not subjected to production test, verified by design/characterization.

4) Not subjected to production test, verified by design/characterization. However, for applications with strict low power-down current requirements, it is mandatory that no active voltage source is supplied at any GPIO pin when  $V_{\text{DDP}}$  is powered off.

#### **Electrical Parameters**

#### Table 40ADC Characteristics (Operating Conditions apply; $V_{DDP}$ = 5V Range)

|                                                              |                    |    |      |         |                           | -    |                         |

|--------------------------------------------------------------|--------------------|----|------|---------|---------------------------|------|-------------------------|

| Parameter                                                    | Symbol             |    | Liı  | nit Val | ues                       | Unit | Test Conditions/        |

|                                                              |                    |    | min. | typ .   | max.                      |      | Remarks                 |

| Overload current coupling factor for                         | K <sub>OVD</sub>   | CC | _    | -       | 5.0 x<br>10 <sup>-3</sup> | -    | $I_{\rm OV} > 0^{1)3)}$ |

| digital I/O pins                                             |                    |    | _    | -       | 1.0 x<br>10 <sup>-2</sup> | -    | $I_{\rm OV} < 0^{1)3)}$ |

| Switched<br>capacitance at the<br>reference voltage<br>input | CAREFSW            | CC | _    | 10      | 20                        | pF   | 1)4)                    |

| Switched<br>capacitance at the<br>analog voltage<br>inputs   | C <sub>AINSW</sub> | CC | _    | 5       | 7                         | pF   | 1)5)                    |

| Input resistance of the reference input                      | R <sub>AREF</sub>  | CC | _    | 1       | 2                         | kΩ   | 1)                      |

| Input resistance of<br>the selected analog<br>channel        | R <sub>AIN</sub>   | CC | _    | 1       | 1.5                       | kΩ   | 1)                      |

1) Not subjected to production test, verified by design/characterization

2) TUE is tested at  $V_{\text{AREF}}$  = 5.0 V,  $V_{\text{AGND}}$  = 0 V,  $V_{\text{DDP}}$  = 5.0 V.

- 3) An overload current  $(I_{OV})$  through a pin injects a certain error current  $(I_{INJ})$  into the adjacent pins. This error current adds to the respective pin's leakage current  $(I_{OZ})$ . The amount of error current depends on the overload current and is defined by the overload coupling factor  $K_{OV}$ . The polarity of the injected error current is inverse compared to the polarity of the overload current that produces it. The total current through a pin is  $|I_{TOT}| = |I_{OZ1}| + (|I_{OV}| \times K_{OV})$ . The additional error current may distort the input voltage on analog inputs.

- 4) This represents an equivalent switched capacitance. This capacitance is not switched to the reference voltage at once. Instead of this, smaller capacitances are successively switched to the reference voltage.

- 5) The sampling capacity of the conversion C-Network is pre-charged to  $V_{AREF}/2$  before connecting the input to the C-Network. Because of the parasitic elements, the voltage measured at ANx is lower than  $V_{AREF}/2$ .

#### **Electrical Parameters**

# 4.3.3 Power-on Reset and PLL Timing

**Table 49** provides the characteristics of the power-on reset and PLL timing in the XC886/888.

| Table 46 | Power-On Reset and PLL Timing (Operating Conditions apply) |

|----------|------------------------------------------------------------|

|          |                                                            |

| Parameter                           | Symbol             |    | Lir  | Limit Values |      |    | Test Conditions                                                              |

|-------------------------------------|--------------------|----|------|--------------|------|----|------------------------------------------------------------------------------|

|                                     |                    |    | min. | typ.         | max. |    |                                                                              |

| Pad operating voltage               | $V_{PAD}$          | CC | 2.3  | -            | -    | V  | 1)                                                                           |

| On-Chip Oscillator<br>start-up time | t <sub>OSCST</sub> | СС | -    | -            | 500  | ns | 1)                                                                           |

| Flash initialization time           | t <sub>FINIT</sub> | CC | _    | 160          | _    | μS | 1)                                                                           |

| RESET hold time                     | t <sub>RST</sub>   | SR | -    | 500          | _    | μS | $V_{\rm DDP}$ rise time<br>(10% – 90%) $\leq$<br>500 $\mu$ s <sup>1)2)</sup> |

| PLL lock-in in time                 | t <sub>LOCK</sub>  | CC | -    | -            | 200  | μS | 1)                                                                           |

| PLL accumulated jitter              | $D_{P}$            |    | -    | _            | 0.7  | ns | 1)3)                                                                         |

1) Not all parameters are 100% tested, but are verified by design/characterization and test correlation.

2) RESET signal has to be active (low) until  $V_{\text{DDC}}$  has reached 90% of its maximum value (typ. 2.5 V).

3) PLL lock at 96 MHz using a 4 MHz external oscillator. The PLL Divider settings are K = 2, N = 48 and P = 1.