Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                        |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | XC800                                                                           |

| Core Size                  | 8-Bit                                                                           |

| Speed                      | 24MHz                                                                           |

| Connectivity               | SSI, UART/USART                                                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 48                                                                              |

| Program Memory Size        | 24KB (24K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 1.75K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                     |

| Data Converters            | A/D 8x10b                                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-LQFP                                                                         |

| Supplier Device Package    | PG-TQFP-64                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/sak-xc888-6ffa-5v-ac |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Summary of Features

Features: (continued)

- Power-on reset generation

- Brownout detection for core logic supply

- On-chip OSC and PLL for clock generation

- PLL loss-of-lock detection

- Power saving modes

- slow-down mode

- idle mode

- power-down mode with wake-up capability via RXD or EXINT0

- clock gating control to each peripheral

- Programmable 16-bit Watchdog Timer (WDT)

- Six ports

- Up to 48 pins as digital I/O

- 8 pins as digital/analog input

- 8-channel, 10-bit ADC

- Four 16-bit timers

- Timer 0 and Timer 1 (T0 and T1)

- Timer 2 and Timer 21 (T2 and T21)

- Multiplication/Division Unit for arithmetic operations (MDU)

- Software libraries to support floating point and MDU calculations

- CORDIC Coprocessor for computation of trigonometric, hyperbolic and linear functions

- MultiCAN with 2 nodes, 32 message objects

- Capture/compare unit for PWM signal generation (CCU6)

- Two full-duplex serial interfaces (UART and UART1)

- Synchronous serial channel (SSC)

- On-chip debug support

- 1 Kbyte of monitor ROM (part of the 12-Kbyte Boot ROM)

- 64 bytes of monitor RAM

- Packages:

- PG-TQFP-48

- PG-TQFP-64

- Temperature range *T*<sub>A</sub>:

- SAF (-40 to 85 °C)

- SAK (-40 to 125 °C)

## **General Device Information**

# 2.4 Pin Definitions and Functions

The functions and default states of the XC886/888 external pins are provided in Table 3.

| Symbol | Pin Number<br>(TQFP-48/64) | Туре | Reset<br>State | Function                                                   |                                                                                                                                                                                                      |

|--------|----------------------------|------|----------------|------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P0     |                            | I/O  |                | I/O port. It ca<br>for the JTAG                            | B-bit bidirectional general purpose<br>an be used as alternate functions<br>6, CCU6, UART, UART1, Timer 2,<br>ultiCAN and SSC.                                                                       |

| P0.0   | 11/17                      |      | Hi-Z           | TCK_0<br>T12HR_1<br>CC61_1<br>CLKOUT_0<br>RXDO_1           | JTAG Clock Input<br>CCU6 Timer 12 Hardware Run<br>Input<br>Input/Output of<br>Capture/Compare channel 1<br>Clock Output<br>UART Transmit Data Output                                                 |

| P0.1   | 13/21                      |      | Hi-Z           | TDI_0<br>T13HR_1<br>RXD_1<br>RXDC1_0<br>COUT61_1<br>EXF2_1 | JTAG Serial Data Input<br>CCU6 Timer 13 Hardware Run<br>Input<br>UART Receive Data Input<br>MultiCAN Node 1 Receiver Input<br>Output of Capture/Compare<br>channel 1<br>Timer 2 External Flag Output |

| P0.2   | 12/18                      |      | PU             | CTRAP_2<br>TDO_0<br>TXD_1<br>TXDC1_0                       | CCU6 Trap Input<br>JTAG Serial Data Output<br>UART Transmit Data<br>Output/Clock Output<br>MultiCAN Node 1 Transmitter<br>Output                                                                     |

| P0.3   | 48/63                      |      | Hi-Z           | SCK_1<br>COUT63_1<br>RXDO1_0                               | SSC Clock Input/Output<br>Output of Capture/Compare<br>channel 3<br>UART1 Transmit Data Output                                                                                                       |

Table 3

Pin Definitions and Functions

## **General Device Information**

| Table 0 | T III Belli                |      |                |                                                     |                                                                                                                                                                                          |  |  |

|---------|----------------------------|------|----------------|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Symbol  | Pin Number<br>(TQFP-48/64) | Туре | Reset<br>State | Function                                            |                                                                                                                                                                                          |  |  |

| P0.4    | 1/64                       |      | Hi-Z           | MTSR_1                                              | SSC Master Transmit Output/<br>Slave Receive Input                                                                                                                                       |  |  |

|         |                            |      |                | CC62_1                                              | Input/Output of<br>Capture/Compare channel 2                                                                                                                                             |  |  |

|         |                            |      |                | TXD1_0                                              | UART1 Transmit Data<br>Output/Clock Output                                                                                                                                               |  |  |

| P0.5    | 2/1                        |      | Hi-Z           | MRST_1<br>EXINT0_0<br>T2EX1_1<br>RXD1_0<br>COUT62_1 | SSC Master Receive Input/Slave<br>Transmit Output<br>External Interrupt Input 0<br>Timer 21 External Trigger Input<br>UART1 Receive Data Input<br>Output of Capture/Compare<br>channel 2 |  |  |

| P0.6    | -/2                        |      | PU             | GPIO                                                |                                                                                                                                                                                          |  |  |

| P0.7    | 47/62                      |      | PU             | CLKOUT_1                                            | Clock Output                                                                                                                                                                             |  |  |

#### Pin Definitions and Functions (cont'd) Table 3

## **General Device Information**

| Symbol | Pin Number<br>(TQFP-48/64) | Туре | Reset<br>State | Function                                       |                                                                                                                                                              |

|--------|----------------------------|------|----------------|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P1     |                            | I/O  |                | I/O port. It ca<br>for the JTAG                | B-bit bidirectional general purpose<br>an be used as alternate functions<br>6, CCU6, UART, Timer 0, Timer 1,<br>1, er 21, MultiCAN and SSC.                  |

| P1.0   | 26/34                      |      | PU             | RXD_0<br>T2EX<br>RXDC0_0                       | UART Receive Data Input<br>Timer 2 External Trigger Input<br>MultiCAN Node 0 Receiver Input                                                                  |

| P1.1   | 27/35                      |      | PU             | EXINT3<br>T0_1<br>TDO_1<br>TXD_0<br>TXDC0_0    | External Interrupt Input 3<br>Timer 0 Input<br>JTAG Serial Data Output<br>UART Transmit Data<br>Output/Clock Output<br>MultiCAN Node 0 Transmitter<br>Output |

| P1.2   | 28/36                      |      | PU             | SCK_0                                          | SSC Clock Input/Output                                                                                                                                       |

| P1.3   | 29/37                      |      | PU             | MTSR_0<br>TXDC1_3                              | SSC Master Transmit<br>Output/Slave Receive Input<br>MultiCAN Node 1 Transmitter<br>Output                                                                   |

| P1.4   | 30/38                      |      | PU             | MRST_0<br>EXINT0_1<br>RXDC1_3                  | SSC Master Receive Input/<br>Slave Transmit Output<br>External Interrupt Input 0<br>MultiCAN Node 1 Receiver Input                                           |

| P1.5   | 31/39                      |      | PU             | CCPOS0_1<br>EXINT5<br>T1_1<br>EXF2_0<br>RXDO_0 | CCU6 Hall Input 0<br>External Interrupt Input 5<br>Timer 1 Input<br>Timer 2 External Flag Output<br>UART Transmit Data Output                                |

## Table 3Pin Definitions and Functions (cont'd)

Table 3

#### **General Device Information**

#### Pin Definitions and Functions (cont'd) Type Reset Function Pin Number Symbol (TQFP-48/64) State **P2** I Port 2 Port 2 is an 8-bit general purpose input-only port. It can be used as alternate functions for

|       |       |      | 0 1                             | outs of the JTAG and CCU6. It is the analog inputs for the ADC.                        |

|-------|-------|------|---------------------------------|----------------------------------------------------------------------------------------|

| P2.0  | 14/22 | Hi-Z | CCPOS0_0<br>EXINT1_0<br>T12HR_2 | CCU6 Hall Input 0<br>External Interrupt Input 1<br>CCU6 Timer 12 Hardware Run<br>Input |

|       |       |      | TCK_1                           | JTAG Clock Input                                                                       |

|       |       |      | CC61_3                          | Input of Capture/Compare<br>channel 1                                                  |

|       |       |      | AN0                             | Analog Input 0                                                                         |

| P2.1  | 15/23 | Hi-Z | CCPOS1_0<br>EXINT2_0<br>T13HR_2 | CCU6 Hall Input 1<br>External Interrupt Input 2<br>CCU6 Timer 13 Hardware Run<br>Input |

|       |       |      | TDI_1<br>CC62_3<br>AN1          | JTAG Serial Data Input<br>Input of Capture/Compare<br>channel 2<br>Analog Input 1      |

| P2.2  | 16/24 | Hi-Z | CCPOS2_0                        | CCU6 Hall Input 2                                                                      |

| 1 2.2 | 10/24 |      | CTRAP_1                         | CCU6 Trap Input                                                                        |

|       |       |      | CC60_3                          | Input of Capture/Compare<br>channel 0                                                  |

|       |       |      | AN2                             | Analog Input 2                                                                         |

| P2.3  | 19/27 | Hi-Z | AN3                             | Analog Input 3                                                                         |

| P2.4  | 20/28 | Hi-Z | AN4                             | Analog Input 4                                                                         |

| P2.5  | 21/29 | Hi-Z | AN5                             | Analog Input 5                                                                         |

| P2.6  | 22/30 | Hi-Z | AN6                             | Analog Input 6                                                                         |

| P2.7  | 25/33 | Hi-Z | AN7                             | Analog Input 7                                                                         |

## XC886/888CLM

## **General Device Information**

| Symbol | Pin Number<br>(TQFP-48/64) | Туре | Reset<br>State | Function                                                                                                                                                        |                                                                                                                                                           |  |

|--------|----------------------------|------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Р3     |                            | I/O  |                | <b>Port 3</b><br>Port 3 is an 8-bit bidirectional general purpose<br>I/O port. It can be used as alternate functions<br>for CCU6, UART1, Timer 21 and MultiCAN. |                                                                                                                                                           |  |

| P3.0   | 35/43                      |      | Hi-Z           | CCPOS1_2<br>CC60_0<br>RXDO1_1                                                                                                                                   | CCU6 Hall Input 1<br>Input/Output of<br>Capture/Compare channel 0<br>UART1 Transmit Data Output                                                           |  |

| P3.1   | 36/44                      |      | Hi-Z           | CCPOS0_2<br>CC61_2<br>COUT60_0<br>TXD1_1                                                                                                                        | CCU6 Hall Input 0<br>Input/Output of<br>Capture/Compare channel 1<br>Output of Capture/Compare<br>channel 0<br>UART1 Transmit Data<br>Output/Clock Output |  |

| P3.2   | 37/49                      |      | Hi-Z           | CCPOS2_2<br>RXDC1_1<br>RXD1_1<br>CC61_0                                                                                                                         | CCU6 Hall Input 2<br>MultiCAN Node 1 Receiver Input<br>UART1 Receive Data Input<br>Input/Output of<br>Capture/Compare channel 1                           |  |

| P3.3   | 38/50                      |      | Hi-Z           | COUT61_0<br>TXDC1_1                                                                                                                                             | Output of Capture/Compare<br>channel 1<br>MultiCAN Node 1 Transmitter<br>Output                                                                           |  |

| P3.4   | 39/51                      |      | Hi-Z           | CC62_0<br>RXDC0_1<br>T2EX1_0                                                                                                                                    | Input/Output of<br>Capture/Compare channel 2<br>MultiCAN Node 0 Receiver Input<br>Timer 21 External Trigger Input                                         |  |

| P3.5   | 40/52                      |      | Hi-Z           | COUT62_0<br>EXF21_0<br>TXDC0_1                                                                                                                                  | Output of Capture/Compare<br>channel 2<br>Timer 21 External Flag Output<br>MultiCAN Node 0 Transmitter<br>Output                                          |  |

| P3.6   | 33/41                      |      | PD             | CTRAP_0                                                                                                                                                         | CCU6 Trap Input                                                                                                                                           |  |

## Table 3Pin Definitions and Functions (cont'd)

## XC886/888CLM

#### **General Device Information**

| Symbol            | Pin Number<br>(TQFP-48/64) | Туре | Reset<br>State | Function                                                                                                     |

|-------------------|----------------------------|------|----------------|--------------------------------------------------------------------------------------------------------------|

| V <sub>DDP</sub>  | 7, 17, 43/<br>7, 25, 55    | _    | -              | <b>I/O Port Supply (3.3 or 5.0 V)</b><br>Also used by EVR and analog modules. All<br>pins must be connected. |

| $V_{\rm SSP}$     | 18, 42/26, 54              | _    | -              | I/O Port Ground<br>All pins must be connected.                                                               |

| $V_{DDC}$         | 6/6                        | _    | _              | Core Supply Monitor (2.5 V)                                                                                  |

| V <sub>SSC</sub>  | 5/5                        | _    | _              | Core Supply Ground                                                                                           |

| $V_{AREF}$        | 24/32                      | _    | _              | ADC Reference Voltage                                                                                        |

| $V_{AGND}$        | 23/31                      | _    | _              | ADC Reference Ground                                                                                         |

| XTAL1             | 4/4                        | I    | Hi-Z           | External Oscillator Input<br>(backup for on-chip OSC, normally NC)                                           |

| XTAL2             | 3/3                        | 0    | Hi-Z           | External Oscillator Output<br>(backup for on-chip OSC, normally NC)                                          |

| TMS               | 10/16                      | 1    | PD             | Test Mode Select                                                                                             |

| RESET             | 41/53                      | 1    | PU             | Reset Input                                                                                                  |

| MBC <sup>1)</sup> | 44/58                      | 1    | PU             | Monitor & BootStrap Loader Control                                                                           |

| NC                | -/56, 57                   | _    | -              | No Connection                                                                                                |

#### Table 3Pin Definitions and Functions (cont'd)

1) An external pull-up device in the range of 4.7 k $\Omega$  to 100 k $\Omega$ . is required to enter user mode. Alternatively MBC can be tied to high if alternate functions (for debugging) of the pin are not utilized.

| Addr            | Register Name                                                     | Bit       | 7           | 6           | 5           | 4           | 3    | 2    | 1         | 0         |

|-----------------|-------------------------------------------------------------------|-----------|-------------|-------------|-------------|-------------|------|------|-----------|-----------|

| A8 <sub>H</sub> | IEN0 Reset: 00 <sub>H</sub>                                       | Bit Field | EA          | 0           | ET2         | ES          | ET1  | EX1  | ET0       | EX0       |

|                 | Interrupt Enable Register 0                                       | Туре      | rw          | r           | rw          | rw          | rw   | rw   | rw        | rw        |

| B8 <sub>H</sub> | IP Reset: 00 <sub>H</sub>                                         | Bit Field | (           | )           | PT2         | PS          | PT1  | PX1  | PT0       | PX0       |

|                 | Interrupt Priority Register                                       | Туре      |             | r           | rw          | rw          | rw   | rw   | rw        | rw        |

| в9 <sub>Н</sub> | IPH Reset: 00 <sub>H</sub>                                        | Bit Field | (           | )           | PT2H        | PSH         | PT1H | PX1H | PT0H      | PX0H      |

|                 | Interrupt Priority High Register                                  | Туре      |             | r           | rw          | rw          | rw   | rw   | rw        | rw        |

| D0 <sub>H</sub> | PSW Reset: 00 <sub>H</sub>                                        | Bit Field | CY          | AC          | F0          | RS1         | RS0  | OV   | F1        | Р         |

|                 | Program Status Word Register                                      | Туре      | rwh         | rwh         | rw          | rw          | rw   | rwh  | rw        | rh        |

| E0 <sub>H</sub> | ACC Reset: 00 <sub>H</sub>                                        | Bit Field | ACC7        | ACC6        | ACC5        | ACC4        | ACC3 | ACC2 | ACC1      | ACC0      |

|                 | Accumulator Register                                              | Туре      | rw          | rw          | rw          | rw          | rw   | rw   | rw        | rw        |

| E8 <sub>H</sub> | IEN1 Reset: 00 <sub>H</sub><br>Interrupt Enable Register 1        | Bit Field | ECCIP<br>3  | ECCIP<br>2  | ECCIP<br>1  | ECCIP<br>0  | EXM  | EX2  | ESSC      | EADC      |

|                 |                                                                   | Туре      | rw          | rw          | rw          | rw          | rw   | rw   | rw        | rw        |

| F0 <sub>H</sub> | B Reset: 00 <sub>H</sub>                                          | Bit Field | B7          | B6          | B5          | B4          | B3   | B2   | B1        | B0        |

|                 | B Register                                                        | Туре      | rw          | rw          | rw          | rw          | rw   | rw   | rw        | rw        |

| F8 <sub>H</sub> | H IP1 Reset: 00 <sub>H</sub><br>Interrupt Priority 1 Register     | Bit Field | PCCIP<br>3  | PCCIP<br>2  | PCCIP<br>1  | PCCIP<br>0  | PXM  | PX2  | PSSC      | PADC      |

|                 |                                                                   | Туре      | rw          | rw          | rw          | rw          | rw   | rw   | rw        | rw        |

| F9 <sub>H</sub> | IPH1 Reset: 00 <sub>H</sub><br>Interrupt Priority 1 High Register | Bit Field | PCCIP<br>3H | PCCIP<br>2H | PCCIP<br>1H | PCCIP<br>0H | PXMH | PX2H | PSSC<br>H | PADC<br>H |

|                 |                                                                   | Туре      | rw          | rw          | rw          | rw          | rw   | rw   | rw        | rw        |

#### Table 5CPU Register Overview (cont'd)

## 3.2.4.2 MDU Registers

The MDU SFRs can be accessed in the mapped memory area (RMAP = 1).

#### Table 6MDU Register Overview

| Addr            | Register Name                                         | Bit       | 7       | 6  | 5    | 4         | 3 | 2   | 1    | 0    |

|-----------------|-------------------------------------------------------|-----------|---------|----|------|-----------|---|-----|------|------|

| RMAP =          | = 1                                                   | •         |         | •  | •    | •         | • | •   | •    |      |

| в0 <sub>Н</sub> | MDUSTAT Reset: 00 <sub>H</sub>                        | Bit Field |         |    | 0    |           |   | BSY | IERR | IRDY |

|                 | MDU Status Register                                   | Туре      |         |    | r    |           |   | rh  | rwh  | rwh  |

| в1 <sub>Н</sub> | MDUCON Reset: 00 <sub>H</sub><br>MDU Control Register | Bit Field | IE      | IR | RSEL | STAR<br>T |   | OPC | ODE  |      |

|                 |                                                       |           | rw      | rw | rw   | rwh       |   | r   | w    |      |

| B2 <sub>H</sub> | MD0 Reset: 00 <sub>H</sub>                            | Bit Field | ld DATA |    |      |           |   |     |      |      |

|                 | MDU Operand Register 0                                | Туре      |         |    |      | r         | W |     |      |      |

| B2 <sub>H</sub> | MR0 Reset: 00 <sub>H</sub>                            | Bit Field | DATA    |    |      |           |   |     |      |      |

|                 | MDU Result Register 0                                 |           | rh      |    |      |           |   |     |      |      |

| вз <sub>Н</sub> | MD1 Reset: 00 <sub>H</sub>                            | Bit Field | DATA    |    |      |           |   |     |      |      |

|                 | MDU Operand Register 1                                |           |         |    |      | r         | W |     |      |      |

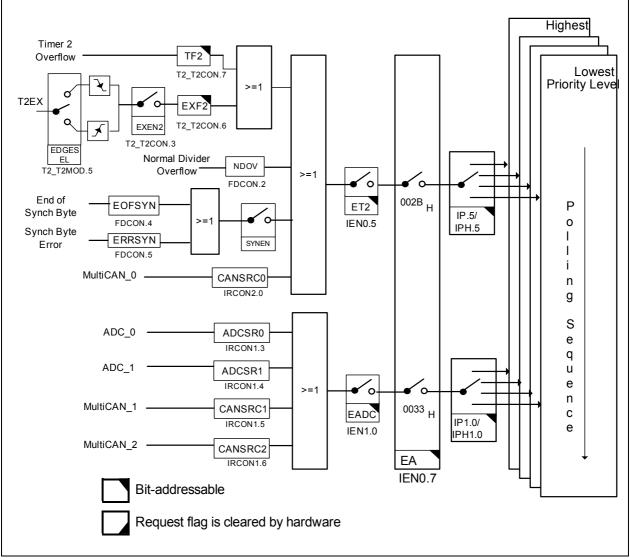

Figure 15 Interrupt Request Sources (Part 2)

- 1) BSL mode is automatically entered if no valid password is installed and data at memory address 0000H equals zero.

- 2) OSC is bypassed in MultiCAN BSL mode

- 3) Normal user mode with standard JTAG (TCK,TDI,TDO) pins for hot-attach purpose.

Note: The boot options are valid only with the default set of UART and JTAG pins.

## 3.8 Clock Generation Unit

The Clock Generation Unit (CGU) allows great flexibility in the clock generation for the XC886/888. The power consumption is indirectly proportional to the frequency, whereas the performance of the microcontroller is directly proportional to the frequency. During user program execution, the frequency can be programmed for an optimal ratio between performance and power consumption. Therefore the power consumption can be adapted to the actual application state.

#### Features

- Phase-Locked Loop (PLL) for multiplying clock source by different factors

- PLL Base Mode

- Prescaler Mode

- PLL Mode

- Power-down mode support

The CGU consists of an oscillator circuit and a PLL. In the XC886/888, the oscillator can be from either of these two sources: the on-chip oscillator (9.6 MHz) or the external oscillator (4 MHz to 12 MHz). The term "oscillator" is used to refer to both on-chip oscillator and external oscillator, unless otherwise stated. After the reset, the on-chip oscillator will be used by default. The external oscillator can be selected via software. In addition, the PLL provides a fail-safe logic to perform oscillator run and loss-of-lock detection. This allows emergency routines to be executed for system recovery or to perform system shut down.

If the WDT is not serviced before the timer overflow, a system malfunction is assumed. As a result, the WDT NMI is triggered (assert FNMIWDT) and the reset prewarning is entered. The prewarning period lasts for  $30_{\rm H}$  count, after which the system is reset (assert WDTRST).

The WDT has a "programmable window boundary" which disallows any refresh during the WDT's count-up. A refresh during this window boundary constitutes an invalid access to the WDT, causing the reset prewarning to be entered but without triggering the WDT NMI. The system will still be reset after the prewarning period is over. The window boundary is from  $0000_{\rm H}$  to the value obtained from the concatenation of WDTWINB and  $00_{\rm H}$ .

After being serviced, the WDT continues counting up from the value ( $\langle WDTREL \rangle * 2^8$ ). The time period for an overflow of the WDT is programmable in two ways:

- The input frequency to the WDT can be selected to be either  $f_{\rm PCLK}/2$  or  $f_{\rm PCLK}/128$

- The reload value WDTREL for the high byte of WDT can be programmed in register WDTREL

The period,  $P_{\rm WDT}$ , between servicing the WDT and the next overflow can be determined by the following formula:

$$P_{WDT} = \frac{2^{(1 + WDTIN \times 6)} \times (2^{16} - WDTREL \times 2^8)}{f_{PCLK}}$$

(3.4)

If the Window-Boundary Refresh feature of the WDT is enabled, the period  $P_{\rm WDT}$  between servicing the WDT and the next overflow is shortened if WDTWINB is greater than WDTREL, see **Figure 29**. This period can be calculated using the same formula by replacing WDTREL with WDTWINB. For this feature to be useful, WDTWINB cannot be smaller than WDTREL.

The following formulas calculate the final baud rate without and with the fractional divider respectively:

baud rate =

$$\frac{f_{PCLK}}{16 \times 2^{BRPRE} \times (BR VALUE + 1)}$$

where  $2^{BRPRE} \times (BR_VALUE + 1) > 1$

(3.5)

baud rate =  $\frac{f_{PCLK}}{16 \times 2^{BRPRE} \times (BR_VALUE + 1)} \times \frac{STEP}{256}$

(3.6)

The maximum baud rate that can be generated is limited to  $f_{\text{PCLK}}/32$ . Hence, for a module clock of 24 MHz, the maximum achievable baud rate is 0.75 MBaud.

Standard LIN protocol can support a maximum baud rate of 20 kHz, the baud rate accuracy is not critical and the fractional divider can be disabled. Only the prescaler is used for auto baud rate calculation. For LIN fast mode, which supports the baud rate of 20 kHz to 115.2 kHz, the higher baud rates require the use of the fractional divider for greater accuracy.

**Table 30** lists the various commonly used baud rates with their corresponding parameter settings and deviation errors. The fractional divider is disabled and a module clock of 24 MHz is used.

| Baud rate  | Prescaling Factor<br>(2BRPRE) | Reload Value<br>(BR_VALUE + 1) | Deviation Error |  |  |  |  |

|------------|-------------------------------|--------------------------------|-----------------|--|--|--|--|

| 19.2 kBaud | 1 (BRPRE=000 <sub>B</sub> )   | 78 (4E <sub>H</sub> )          | 0.17 %          |  |  |  |  |

| 9600 Baud  | 1 (BRPRE=000 <sub>B</sub> )   | 156 (9C <sub>H</sub> )         | 0.17 %          |  |  |  |  |

| 4800 Baud  | 2 (BRPRE=001 <sub>B</sub> )   | 156 (9C <sub>H</sub> )         | 0.17 %          |  |  |  |  |

| 2400 Baud  | 4 (BRPRE=010 <sub>B</sub> )   | 156 (9С <sub>Н</sub> )         | 0.17 %          |  |  |  |  |

Table 30

Typical Baud rates for UART with Fractional Divider disabled

The fractional divider allows baud rates of higher accuracy (lower deviation error) to be generated. **Table 31** lists the resulting deviation errors from generating a baud rate of 115.2 kHz, using different module clock frequencies. The fractional divider is enabled (fractional divider mode) and the corresponding parameter settings are shown.

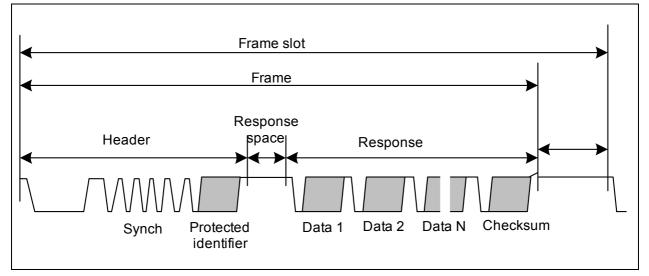

## 3.15 LIN Protocol

The UART module can be used to support the Local Interconnect Network (LIN) protocol for both master and slave operations. The LIN baud rate detection feature, which consists of the hardware logic for Break and Synch Byte detection, provides the capability to detect the baud rate within LIN protocol using Timer 2. This allows the UART to be synchronized to the LIN baud rate for data transmission and reception.

Note: The LIN baud rate detection feature is available for use only with UART. To use UART1 for LIN communication, software has to be implemented to detect the Break and Synch Byte.

LIN is a holistic communication concept for local interconnected networks in vehicles. The communication is based on the SCI (UART) data format, a single-master/multipleslave concept, a clock synchronization for nodes without stabilized time base. An attractive feature of LIN is self-synchronization of the slave nodes without a crystal or ceramic resonator, which significantly reduces the cost of hardware platform. Hence, the baud rate must be calculated and returned with every message frame.

The structure of a LIN frame is shown in **Figure 31**. The frame consists of the:

- Header, which comprises a Break (13-bit time low), Synch Byte (55<sub>H</sub>), and ID field

- Response time

- Data bytes (according to UART protocol)

- Checksum

Figure 31 Structure of LIN Frame

## 3.15.1 LIN Header Transmission

LIN header transmission is only applicable in master mode. In the LIN communication, a master task decides when and which frame is to be transferred on the bus. It also identifies a slave task to provide the data transported by each frame. The information

## 3.19 Capture/Compare Unit 6

The Capture/Compare Unit 6 (CCU6) provides two independent timers (T12, T13), which can be used for Pulse Width Modulation (PWM) generation, especially for AC-motor control. The CCU6 also supports special control modes for block commutation and multi-phase machines.

The timer T12 can function in capture and/or compare mode for its three channels. The timer T13 can work in compare mode only.

The multi-channel control unit generates output patterns, which can be modulated by T12 and/or T13. The modulation sources can be selected and combined for the signal modulation.

#### Timer T12 Features

- Three capture/compare channels, each channel can be used either as a capture or as a compare channel

- Supports generation of a three-phase PWM (six outputs, individual signals for highside and lowside switches)

- 16-bit resolution, maximum count frequency = peripheral clock frequency

- Dead-time control for each channel to avoid short-circuits in the power stage

- Concurrent update of the required T12/13 registers

- · Generation of center-aligned and edge-aligned PWM

- Supports single-shot mode

- Supports many interrupt request sources

- Hysteresis-like control mode

#### **Timer T13 Features**

- One independent compare channel with one output

- 16-bit resolution, maximum count frequency = peripheral clock frequency

- Can be synchronized to T12

- Interrupt generation at period-match and compare-match

- Supports single-shot mode

#### Additional Features

- Implements block commutation for Brushless DC-drives

- Position detection via Hall-sensor pattern

- Automatic rotational speed measurement for block commutation

- Integrated error handling

- Fast emergency stop without CPU load via external signal (CTRAP)

- · Control modes for multi-channel AC-drives

- Output levels can be selected and adapted to the power stage

The block diagram of the CCU6 module is shown in **Figure 33**.

- CAN functionality according to CAN specification V2.0 B active.

- Dedicated control registers are provided for each CAN node.

- A data transfer rate up to 1 MBaud is supported.

- Flexible and powerful message transfer control and error handling capabilities are implemented.

- Advanced CAN bus bit timing analysis and baud rate detection can be performed for each CAN node via the frame counter.

- Full-CAN functionality: A set of 32 message objects can be individually

- allocated (assigned) to any CAN node

- configured as transmit or receive object

- setup to handle frames with 11-bit or 29-bit identifier

- counted or assigned a timestamp via a frame counter

- configured to remote monitoring mode

- Advanced Acceptance Filtering:

- Each message object provides an individual acceptance mask to filter incoming frames.

- A message object can be configured to accept only standard or only extended frames or to accept both standard and extended frames.

- Message objects can be grouped into 4 priority classes.

- The selection of the message to be transmitted first can be performed on the basis of frame identifier, IDE bit and RTR bit according to CAN arbitration rules.

- Advanced Message Object Functionality:

- Message Objects can be combined to build FIFO message buffers of arbitrary size, which is only limited by the total number of message objects.

- Message objects can be linked to form a gateway to automatically transfer frames between 2 different CAN buses. A single gateway can link any two CAN nodes. An arbitrary number of gateways may be defined.

- Advanced Data Management:

- The Message objects are organized in double chained lists.

- List reorganizations may be performed any time, even during full operation of the CAN nodes.

- A powerful, command driven list controller manages the organization of the list structure and ensures consistency of the list.

- Message FIFOs are based on the list structure and can easily be scaled in size during CAN operation.

- Static Allocation Commands offer compatibility with TwinCAN applications, which are not list based.

- Advanced Interrupt Handling:

- Up to 8 interrupt output lines are available. Most interrupt requests can be individually routed to one of the 8 interrupt output lines.

- Message postprocessing notifications can be flexibly aggregated into a dedicated register field of 64 notification bits.

## Table 36Chip Identification Number (cont'd)

| Product Variant   | Chip Identification Number |                       |                       |  |  |  |  |

|-------------------|----------------------------|-----------------------|-----------------------|--|--|--|--|

|                   | AA-Step                    | AB-Step               | AC-Step               |  |  |  |  |

| XC886-6FFA 3V3    | -                          | 095D1562 <sub>H</sub> | 0B5D1562 <sub>H</sub> |  |  |  |  |

| XC888-6FFA 3V3    | -                          | 095D1563 <sub>H</sub> | 0B5D1563 <sub>H</sub> |  |  |  |  |

| XC886CLM-8FFA 5V  | -                          | 09900102 <sub>H</sub> | 0B900102 <sub>H</sub> |  |  |  |  |

| XC888CLM-8FFA 5V  | -                          | 09900103 <sub>H</sub> | 0B900103 <sub>H</sub> |  |  |  |  |

| XC886LM-8FFA 5V   | -                          | 09900122 <sub>H</sub> | 0B900122 <sub>H</sub> |  |  |  |  |

| XC888LM-8FFA 5V   | -                          | 09900123 <sub>H</sub> | 0B900123 <sub>H</sub> |  |  |  |  |

| XC886CLM-6FFA 5V  | -                          | 09951502 <sub>H</sub> | 0B951502 <sub>H</sub> |  |  |  |  |

| XC888CLM-6FFA 5V  | -                          | 09951503 <sub>H</sub> | 0B951503 <sub>H</sub> |  |  |  |  |

| XC886LM-6FFA 5V   | -                          | 09951522 <sub>Н</sub> | 0B951522 <sub>H</sub> |  |  |  |  |

| XC888LM-6FFA 5V   | -                          | 09951523 <sub>H</sub> | 0B951523 <sub>H</sub> |  |  |  |  |

| XC886CM-8FFA 5V   | -                          | 09980102 <sub>H</sub> | 0B980102 <sub>H</sub> |  |  |  |  |

| XC888CM-8FFA 5V   | -                          | 09980103 <sub>H</sub> | 0B980103 <sub>H</sub> |  |  |  |  |

| XC886C-8FFA 5V    | -                          | 09980142 <sub>H</sub> | 0B980142 <sub>H</sub> |  |  |  |  |

| XC888C-8FFA 5V    | -                          | 09980143 <sub>H</sub> | 0B980143 <sub>H</sub> |  |  |  |  |

| XC886-8FFA 5V     | -                          | 09980162 <sub>H</sub> | 0B980162 <sub>H</sub> |  |  |  |  |

| XC888-8FFA 5V     | -                          | 09980163 <sub>H</sub> | 0B980163 <sub>H</sub> |  |  |  |  |

| XC886CM-6FFA 5V   | -                          | 099D1502 <sub>H</sub> | 0B9D1502 <sub>H</sub> |  |  |  |  |

| XC888CM-6FFA 5V   | -                          | 099D1503 <sub>H</sub> | 0B9D1503 <sub>H</sub> |  |  |  |  |

| XC886C-6FFA 5V    | -                          | 099D1542 <sub>H</sub> | 0B9D1542 <sub>H</sub> |  |  |  |  |

| XC888C-6FFA 5V    | -                          | 099D1543 <sub>H</sub> | 0B9D1543 <sub>H</sub> |  |  |  |  |

| XC886-6FFA 5V     | -                          | 099D1562 <sub>H</sub> | 0B9D1562 <sub>H</sub> |  |  |  |  |

| XC888-6FFA 5V     | -                          | 099D1563 <sub>H</sub> | 0B9D1563 <sub>H</sub> |  |  |  |  |

| ROM Devices       |                            |                       |                       |  |  |  |  |

| XC886CLM-8RFA 3V3 | 22400502 <sub>H</sub>      | -                     | -                     |  |  |  |  |

| XC888CLM-8RFA 3V3 | 22400503 <sub>H</sub>      | -                     | -                     |  |  |  |  |

| XC886LM-8RFA 3V3  | 22400522 <sub>H</sub>      | -                     | -                     |  |  |  |  |

| XC888LM-8RFA 3V3  | 22400523 <sub>H</sub>      | -                     | -                     |  |  |  |  |

| XC886CLM-6RFA 3V3 | 22411502 <sub>H</sub>      | -                     | -                     |  |  |  |  |

| XC888CLM-6RFA 3V3 | 22411503 <sub>H</sub>      | -                     | -                     |  |  |  |  |

#### **Electrical Parameters**

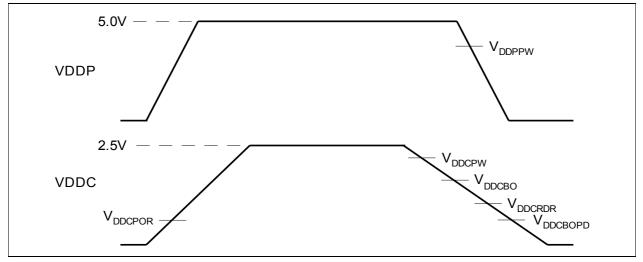

## 4.2.2 Supply Threshold Characteristics

Table 39 provides the characteristics of the supply threshold in the XC886/888.

Figure 38 Supply Threshold Parameters

| Table 39 | Supply Threshold Parameters | (Operating Conditions apply) |

|----------|-----------------------------|------------------------------|

|----------|-----------------------------|------------------------------|

| Parameters                                                         | Symbol               |    | Limit Values |      |      | Unit |

|--------------------------------------------------------------------|----------------------|----|--------------|------|------|------|

|                                                                    |                      |    | min.         | typ. | max. |      |

| $V_{\rm DDC}$ prewarning voltage <sup>1)</sup>                     | V <sub>DDCPW</sub>   | CC | 2.2          | 2.3  | 2.4  | V    |

| $V_{\text{DDC}}$ brownout voltage in active mode <sup>1)</sup>     | V <sub>DDCBO</sub>   | СС | 2.0          | 2.1  | 2.2  | V    |

| RAM data retention voltage                                         | V <sub>DDCRDR</sub>  | CC | 0.9          | 1.0  | 1.1  | V    |

| $V_{\text{DDC}}$ brownout voltage in power-down mode <sup>2)</sup> | V <sub>DDCBOPD</sub> | СС | 1.3          | 1.5  | 1.7  | V    |

| $V_{\rm DDP}$ prewarning voltage <sup>3)</sup>                     | V <sub>DDPPW</sub>   | CC | 3.4          | 4.0  | 4.6  | V    |

| Power-on reset voltage <sup>2)4)</sup>                             | VDDCPOR              | CC | 1.3          | 1.5  | 1.7  | V    |

1) Detection is disabled in power-down mode.

2) Detection is enabled in both active and power-down mode.

Detection is enabled for external power supply of 5.0V. Detection must be disabled for external power supply of 3.3V.

4) The reset of EVR is extended by 300 µs typically after the VDDC reaches the power-on reset voltage.

#### **Electrical Parameters**

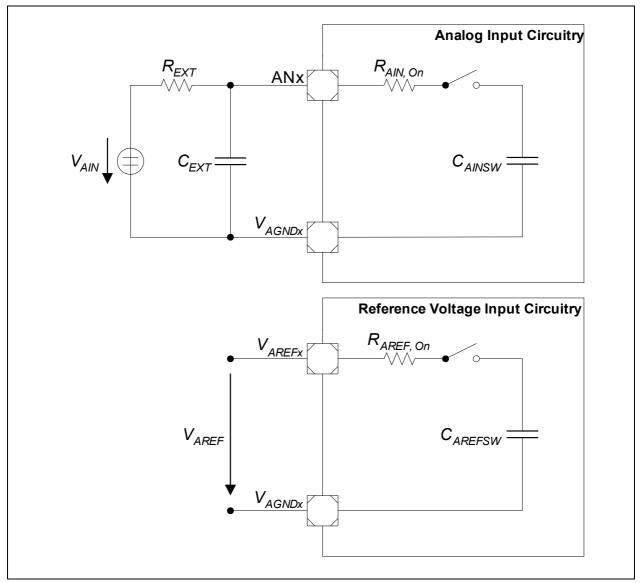

Figure 39 ADC Input Circuits

#### **Electrical Parameters**

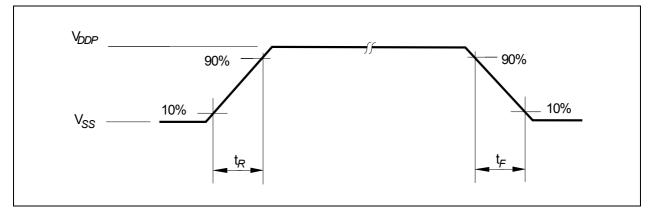

## 4.3.2 Output Rise/Fall Times

Table 45 provides the characteristics of the output rise/fall times in the XC886/888.

#### Table 45 Output Rise/Fall Times Parameters (Operating Conditions apply)

| Parameter                     | Symbol                          | Limit<br>Values |      | Unit | Test Conditions          |  |

|-------------------------------|---------------------------------|-----------------|------|------|--------------------------|--|

|                               |                                 | min.            | max. |      |                          |  |

| $V_{\rm DDP}$ = 5V Range      |                                 |                 |      |      |                          |  |

| Rise/fall times               | t <sub>R</sub> , t <sub>F</sub> | _               | 10   | ns   | 20 pF. <sup>1)2)3)</sup> |  |

| V <sub>DDP</sub> = 3.3V Range | ·                               |                 |      |      |                          |  |

| Rise/fall times               | t <sub>R</sub> , t <sub>F</sub> | _               | 10   | ns   | 20 pF. <sup>1)2)4)</sup> |  |

|                               |                                 |                 |      |      | •                        |  |

1) Rise/Fall time measurements are taken with 10% - 90% of pad supply.

2) Not all parameters are 100% tested, but are verified by design/characterization and test correlation.

3) Additional rise/fall time valid for  $C_{\rm L}$  = 20pF - 100pF @ 0.125 ns/pF.

4) Additional rise/fall time valid for  $C_{\rm L}$  = 20pF - 100pF @ 0.225 ns/pF.

Figure 43 Rise/Fall Times Parameters

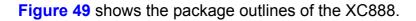

#### Package and Quality Declaration

## Figure 49 PG-TQFP-64 Package Outline