Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| 2 0 0 0 0 0 0              |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | XC800                                                                            |

| Core Size                  | 8-Bit                                                                            |

| Speed                      | 24MHz                                                                            |

| Connectivity               | CANbus, SSI, UART/USART                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 48                                                                               |

| Program Memory Size        | 24KB (24K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | · .                                                                              |

| RAM Size                   | 1.75K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                      |

| Data Converters            | A/D 8x10b                                                                        |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-LQFP                                                                          |

| Supplier Device Package    | PG-TQFP-64                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/sak-xc888c-6ffi-5v-ac |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **General Device Information**

| Table 0 | T III Belli                |      |                |                                                     | u)                                                                                                                                                                                       |

|---------|----------------------------|------|----------------|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol  | Pin Number<br>(TQFP-48/64) | Туре | Reset<br>State | Function                                            |                                                                                                                                                                                          |

| P0.4    | 1/64                       |      | Hi-Z           | MTSR_1                                              | SSC Master Transmit Output/<br>Slave Receive Input                                                                                                                                       |

|         |                            |      |                | CC62_1                                              | Input/Output of<br>Capture/Compare channel 2                                                                                                                                             |

|         |                            |      |                | TXD1_0                                              | UART1 Transmit Data<br>Output/Clock Output                                                                                                                                               |

| P0.5    | 2/1                        |      | Hi-Z           | MRST_1<br>EXINT0_0<br>T2EX1_1<br>RXD1_0<br>COUT62_1 | SSC Master Receive Input/Slave<br>Transmit Output<br>External Interrupt Input 0<br>Timer 21 External Trigger Input<br>UART1 Receive Data Input<br>Output of Capture/Compare<br>channel 2 |

| P0.6    | -/2                        |      | PU             | GPIO                                                |                                                                                                                                                                                          |

| P0.7    | 47/62                      |      | PU             | CLKOUT_1                                            | Clock Output                                                                                                                                                                             |

#### Pin Definitions and Functions (cont'd) Table 3

# Table 14CCU6 Register Overview (cont'd)

| Addr            | Register Name                                                        | Bit       | 7          | 6          | 5          | 4          | 3          | 2          | 1           | 0           |

|-----------------|----------------------------------------------------------------------|-----------|------------|------------|------------|------------|------------|------------|-------------|-------------|

| FB <sub>H</sub> | CCU6_CC60RH Reset: 00 <sub>H</sub>                                   | Bit Field |            | 1          | 1          | CC6        | 60VH       | 1          | 1           | 1           |

|                 | Capture/Compare Register for<br>Channel CC60 High                    | Туре      |            |            |            | r          | 'n         |            |             |             |

| FC <sub>H</sub> | CCU6_CC61RL Reset: 00 <sub>H</sub>                                   | Bit Field | CC61VL     |            |            |            |            |            |             |             |

|                 | Capture/Compare Register for<br>Channel CC61 Low                     | Туре      |            |            |            | r          | 'n         |            |             |             |

| FD <sub>H</sub> | CCU6_CC61RH Reset: 00 <sub>H</sub>                                   | Bit Field |            |            |            | CC6        | 61VH       |            |             |             |

|                 | Capture/Compare Register for<br>Channel CC61 High                    | Туре      |            |            |            | r          | 'n         |            |             |             |

| FE <sub>H</sub> | CCU6_CC62RL Reset: 00 <sub>H</sub>                                   | Bit Field |            |            |            | CC6        | 62VL       |            |             |             |

|                 | Capture/Compare Register for<br>Channel CC62 Low                     | Туре      |            |            |            | r          | h          |            |             |             |

| FF <sub>H</sub> | CCU6_CC62RH Reset: 00 <sub>H</sub>                                   | Bit Field |            |            |            | CC6        | 62VH       |            |             |             |

|                 | Capture/Compare Register for<br>Channel CC62 High                    | Туре      |            |            |            | r          | 'n         |            |             |             |

| RMAP =          | 0, PAGE 2                                                            | _         |            |            |            |            | _          |            |             |             |

| 9A <sub>H</sub> | CCU6_T12MSELL Reset: 00 <sub>H</sub>                                 | Bit Field |            | MS         | EL61       |            |            | MSE        | EL60        |             |

|                 | T12 Capture/Compare Mode Select<br>Register Low                      | Туре      |            | r          | w          |            |            | r          | w           |             |

| 9В <sub>Н</sub> | CCU6_T12MSELH Reset: 00 <sub>H</sub>                                 | Bit Field | DBYP       |            | HSYNC      |            |            | MSE        | EL62        |             |

|                 | T12 Capture/Compare Mode Select<br>Register High                     | Туре      | rw         |            | rw         |            | rw         |            |             |             |

| 9CH             | CCU6_IENL Reset: 00 <sub>H</sub>                                     | Bit Field | ENT1       | ENT1       | ENCC       | ENCC       | ENCC       | ENCC       | ENCC        | ENCC        |

|                 | Capture/Compare Interrupt Enable<br>Register Low                     |           | 2<br>PM    | 2<br>OM    | 62F        | 62R        | 61F        | 61R        | 60F         | 60R         |

|                 |                                                                      | Туре      | rw          | rw          |

| 9D <sub>H</sub> | CCU6_IENH Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Enable | Bit Field | EN<br>STR  | EN<br>IDLE | EN<br>WHE  | EN<br>CHE  | 0          | EN<br>TRPF | ENT1<br>3PM | ENT1<br>3CM |

|                 | Register High                                                        | Туре      | rw         | rw         | rw         | rw         | r          | rw         | rw          | rw          |

| 9E <sub>H</sub> | CCU6_INPL Reset: 40 <sub>H</sub>                                     | Bit Field | INP        | CHE        | INPO       | CC62       | INPCC61    |            | INPCC60     |             |

|                 | Capture/Compare Interrupt Node<br>Pointer Register Low               | Туре      | r          | w          | rw         |            | r          | w          | rw          |             |

| 9F <sub>H</sub> | CCU6_INPH Reset: 39 <sub>H</sub>                                     | Bit Field | (          | 0          | INP        | T13        | INF        | PT12       | INPERR      |             |

|                 | Capture/Compare Interrupt Node<br>Pointer Register High              | Туре      |            | r          | r          | w          | r          | w          | r           | w           |

| A4 <sub>H</sub> | CCU6_ISSL Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Status | Bit Field | ST12<br>PM | ST12<br>OM | SCC6<br>2F | SCC6<br>2R | SCC6<br>1F | SCC6<br>1R | SCC6<br>0F  | SCC6<br>0R  |

|                 | Set Register Low                                                     | Туре      | w          | w          | w          | w          | w          | w          | w           | w           |

| A5 <sub>H</sub> | CCU6_ISSH Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Status | Bit Field | SSTR       | SIDLE      | SWHE       | SCHE       | SWH<br>C   | STRP<br>F  | ST13<br>PM  | ST13<br>CM  |

|                 | Set Register High                                                    | Туре      | w          | w          | w          | w          | w          | w          | w           | w           |

| A6 <sub>H</sub> | CCU6_PSLR Reset: 00 <sub>H</sub>                                     | Bit Field | PSL63      | 0          |            |            | P          | SL         | •           |             |

|                 | Passive State Level Register                                         | Туре      | rwh        | r          | rwh        |            |            |            |             |             |

| а7 <sub>Н</sub> | CCU6_MCMCTR Reset: 00 <sub>H</sub>                                   | Bit Field | (          | 0          | SW         | SYN        | 0          |            | SWSEL       |             |

|                 | Multi-Channel Mode Control Register                                  | Туре      |            | r          | r          | w          | r          |            | rw          |             |

| FA <sub>H</sub> | CCU6_TCTR2LReset: 00HTimer Control Register 2 Low                    | Bit Field | 0          | T13        | TED        |            | T13TEC     |            | T13<br>SSC  | T12<br>SSC  |

|                 |                                                                      | Туре      | r          | r          | w rw       |            | rw         |            | rw          | rw          |

#### Table 14CCU6 Register Overview (cont'd)

| Addr            | Register Name                                                       | Bit       | 7     | 6            | 5            | 4          | 3            | 2          | 1            | 0          |

|-----------------|---------------------------------------------------------------------|-----------|-------|--------------|--------------|------------|--------------|------------|--------------|------------|

| Fe <sub>H</sub> | CCU6_CMPSTATL Reset: 00 <sub>H</sub><br>Compare State Register Low  | Bit Field | 0     | CC63<br>ST   | CC<br>POS2   | CC<br>POS1 | CC<br>POS0   | CC62<br>ST | CC61<br>ST   | CC60<br>ST |

|                 |                                                                     | Туре      | r     | rh           | rh           | rh         | rh           | rh         | rh           | rh         |

| FF <sub>H</sub> | CCU6_CMPSTATH Reset: 00 <sub>H</sub><br>Compare State Register High | Bit Field | T13IM | COUT<br>63PS | COUT<br>62PS | CC62<br>PS | COUT<br>61PS | CC61<br>PS | COUT<br>60PS | CC60<br>PS |

|                 |                                                                     | Туре      | rwh   | rwh          | rwh          | rwh        | rwh          | rwh        | rwh          | rwh        |

## 3.2.4.11 UART1 Registers

The UART1 SFRs can be accessed in the mapped memory area (RMAP = 1).

#### Table 15 UART1 Register Overview

| Addr            | Register Name                          | Bit       | 7        | 6   | 5   | 4   | 3     | 2    | 1   | 0    |  |  |

|-----------------|----------------------------------------|-----------|----------|-----|-----|-----|-------|------|-----|------|--|--|

| RMAP =          | = 1                                    | 1         |          |     |     |     |       |      |     | 1    |  |  |

| C8 <sub>H</sub> | SCON Reset: 00 <sub>H</sub>            | Bit Field | SM0      | SM1 | SM2 | REN | TB8   | RB8  | TI  | RI   |  |  |

|                 | Serial Channel Control Register        | Туре      | rw       | rw  | rw  | rw  | rw    | rwh  | rwh | rwh  |  |  |

| C9 <sub>H</sub> | SBUF Reset: 00 <sub>H</sub>            | Bit Field |          |     |     | V   | AL    |      |     |      |  |  |

|                 | Serial Data Buffer Register            | Туре      | rwh      |     |     |     |       |      |     |      |  |  |

| са <sub>Н</sub> | BCON Reset: 00 <sub>H</sub>            | Bit Field | 0        |     |     |     | BRPRE |      | R   |      |  |  |

|                 | Baud Rate Control Register             | Туре      |          |     | r   |     | rw    |      |     | rw   |  |  |

| св <sub>Н</sub> | BG Reset: 00 <sub>H</sub>              | Bit Field | BR_VALUE |     |     |     |       |      |     |      |  |  |

|                 | Baud Rate Timer/Reload<br>Register     | Туре      | rwh      |     |     |     |       |      |     |      |  |  |

| сс <sub>Н</sub> | FDCON Reset: 00 <sub>H</sub>           | Bit Field |          |     | 0   |     |       | NDOV | FDM | FDEN |  |  |

|                 | Fractional Divider Control<br>Register | Туре      |          |     | r   |     |       | rwh  | rw  | rw   |  |  |

| CD <sub>H</sub> | FDSTEP Reset: 00 <sub>H</sub>          | Bit Field |          |     |     | ST  | ΈP    |      |     |      |  |  |

|                 | Fractional Divider Reload<br>Register  | Туре      | rw       |     |     |     |       |      |     |      |  |  |

| Ceh             | FDRES Reset: 00 <sub>H</sub>           | Bit Field |          |     |     | RES | SULT  |      |     |      |  |  |

|                 | Fractional Divider Result<br>Register  | Туре      |          |     | rh  |     |       |      |     |      |  |  |

# 3.2.4.12 SSC Registers

The SSC SFRs can be accessed in the standard memory area (RMAP = 0).

| Addr            | Register Name                                                                | Bit       | 7           | 6  | 5  | 4    | 3    | 2   | 1   | 0   |

|-----------------|------------------------------------------------------------------------------|-----------|-------------|----|----|------|------|-----|-----|-----|

| RMAP =          | = 0                                                                          |           |             |    |    |      |      |     |     |     |

| A9 <sub>H</sub> | SSC_PISEL Reset: 00 <sub>H</sub>                                             | Bit Field |             | 0  |    |      |      | CIS | SIS | MIS |

|                 | Port Input Select Register                                                   | Туре      |             |    | r  |      |      | rw  | rw  | rw  |

| AA <sub>H</sub> | SSC_CONL Reset: 00 <sub>H</sub>                                              | Bit Field | LB          | PO | PH | HB   |      | В   | М   |     |

|                 | Control Register Low<br>Programming Mode                                     | Туре      | rw          | rw | rw | rw   | rw   |     |     |     |

| AA <sub>H</sub> | SSC_CONL Reset: 00 <sub>H</sub>                                              | Bit Field |             | (  | )  |      |      | В   | С   |     |

|                 | Control Register Low<br>Operating Mode                                       | Туре      | r           |    |    |      |      | r   | h   |     |

| ав <sub>Н</sub> | SSC_CONH Reset: 00 <sub>H</sub><br>Control Register High<br>Programming Mode | Bit Field | EN          | MS | 0  | AREN | BEN  | PEN | REN | TEN |

|                 |                                                                              | Туре      | rw          | rw | r  | rw   | rw   | rw  | rw  | rw  |

| ав <sub>Н</sub> | SSC_CONH Reset: 00 <sub>H</sub>                                              | Bit Field | EN          | MS | 0  | BSY  | BE   | PE  | RE  | TE  |

|                 | Control Register High<br>Operating Mode                                      | Туре      | rw          | rw | r  | rh   | rwh  | rwh | rwh | rwh |

| ac <sub>h</sub> | SSC_TBL Reset: 00 <sub>H</sub>                                               | Bit Field |             |    |    | TB_V | ALUE |     |     |     |

|                 | Transmitter Buffer Register Low                                              | Туре      |             |    |    | n    | N    |     |     |     |

| ad <sub>H</sub> | SSC_RBL Reset: 00 <sub>H</sub>                                               | Bit Field | ld RB_VALUE |    |    |      |      |     |     |     |

|                 | Receiver Buffer Register Low                                                 | Туре      | rh          |    |    |      |      |     |     |     |

| ае <sub>Н</sub> | SSC_BRL Reset: 00 <sub>H</sub>                                               | Bit Field | BR_VALUE    |    |    |      |      |     |     |     |

|                 | Baud Rate Timer Reload<br>Register Low                                       | Туре      | rw          |    |    |      |      |     |     |     |

| af <sub>h</sub> | SSC_BRH Reset: 00 <sub>H</sub>                                               | Bit Field |             |    |    | BR_V | ALUE |     |     |     |

|                 | Baud Rate Timer Reload<br>Register High                                      | Туре      |             |    |    | n    | N    |     |     |     |

#### Table 16 SSC Register Overview

## 3.2.4.13 MultiCAN Registers

The MultiCAN SFRs can be accessed in the standard memory area (RMAP = 0).

| Addr            | Register Name                        | Bit       | 7   | 6   | 5   | 4   | 3    | 2    | 1    | 0    |

|-----------------|--------------------------------------|-----------|-----|-----|-----|-----|------|------|------|------|

| RMAP =          | : 0                                  |           |     |     |     |     |      |      |      |      |

| D8 <sub>H</sub> | ADCON Reset: 00 <sub>H</sub>         | Bit Field | V3  | V2  | V1  | V0  | AU   | AD   | BSY  | RWEN |

|                 | CAN Address/Data Control<br>Register | Туре      | rw  | rw  | rw  | rw  | rw   |      | rh   | rw   |

| D9 <sub>H</sub> | ADL Reset: 00 <sub>H</sub>           | Bit Field | CA9 | CA8 | CA7 | CA6 | CA5  | CA4  | CA3  | CA2  |

|                 | CAN Address Register Low             | Туре      | rwh | rwh | rwh | rwh | rwh  | rwh  | rwh  | rwh  |

| da <sub>h</sub> | ADH Reset: 00 <sub>H</sub>           | Bit Field | 0   |     |     |     | CA13 | CA12 | CA11 | CA10 |

|                 | CAN Address Register High            | Туре      |     |     | ſ   |     | rwh  | rwh  | rwh  | rwh  |

## Table 18OCDS Register Overview (cont'd)

| Addr            | Register Name                | Bit       | 7     | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-----------------|------------------------------|-----------|-------|---|---|---|---|---|---|---|

| EC <sub>H</sub> | MMWR2 Reset: 00 <sub>H</sub> | Bit Field | MMWR2 |   |   |   |   |   |   |   |

|                 | Monitor Work Register 2      | Туре      | rw    |   |   |   |   |   |   |   |

## 3.4.2 Interrupt Source and Vector

Each interrupt event source has an associated interrupt vector address for the interrupt node it belongs to. This vector is accessed to service the corresponding interrupt node request. The interrupt service of each interrupt source can be individually enabled or disabled via an enable bit. The assignment of the XC886/888 interrupt sources to the interrupt vector address and the corresponding interrupt node enable bits are summarized in Table 20.

| Interrupt<br>Source   | Vector<br>Address | Assignment for<br>XC886/888                          | Enable Bit | SFR    |

|-----------------------|-------------------|------------------------------------------------------|------------|--------|

| NMI 0073 <sub>H</sub> |                   | Watchdog Timer NMI                                   | NMIWDT     | NMICON |

|                       |                   | PLL NMI                                              | NMIPLL     |        |

|                       |                   | Flash NMI                                            | NMIFLASH   |        |

|                       |                   | VDDC Prewarning NMI                                  | NMIVDD     |        |

|                       |                   | VDDP Prewarning NMI                                  | NMIVDDP    |        |

|                       |                   | Flash ECC NMI                                        | NMIECC     |        |

| XINTR0                | 0003 <sub>H</sub> | External Interrupt 0                                 | EX0        | IEN0   |

| XINTR1                | 000B <sub>H</sub> | Timer 0                                              | ET0        |        |

| XINTR2                | 0013 <sub>H</sub> | External Interrupt 1                                 | EX1        |        |

| XINTR3                | 001B <sub>H</sub> | Timer 1                                              | ET1        |        |

| XINTR4                | 0023 <sub>H</sub> | UART                                                 | ES         |        |

| XINTR5                | 002B <sub>H</sub> | T2                                                   | ET2        |        |

|                       |                   | UART Fractional Divider<br>(Normal Divider Overflow) |            |        |

|                       |                   | MultiCAN Node 0                                      |            |        |

|                       |                   | LIN                                                  | 1          |        |

#### Table 20 Interrupt Vector Addresses

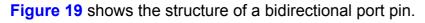

Figure 19 General Structure of Bidirectional Port

- 1) BSL mode is automatically entered if no valid password is installed and data at memory address 0000H equals zero.

- 2) OSC is bypassed in MultiCAN BSL mode

- 3) Normal user mode with standard JTAG (TCK,TDI,TDO) pins for hot-attach purpose.

Note: The boot options are valid only with the default set of UART and JTAG pins.

## 3.8 Clock Generation Unit

The Clock Generation Unit (CGU) allows great flexibility in the clock generation for the XC886/888. The power consumption is indirectly proportional to the frequency, whereas the performance of the microcontroller is directly proportional to the frequency. During user program execution, the frequency can be programmed for an optimal ratio between performance and power consumption. Therefore the power consumption can be adapted to the actual application state.

#### Features

- Phase-Locked Loop (PLL) for multiplying clock source by different factors

- PLL Base Mode

- Prescaler Mode

- PLL Mode

- Power-down mode support

The CGU consists of an oscillator circuit and a PLL. In the XC886/888, the oscillator can be from either of these two sources: the on-chip oscillator (9.6 MHz) or the external oscillator (4 MHz to 12 MHz). The term "oscillator" is used to refer to both on-chip oscillator and external oscillator, unless otherwise stated. After the reset, the on-chip oscillator will be used by default. The external oscillator can be selected via software. In addition, the PLL provides a fail-safe logic to perform oscillator run and loss-of-lock detection. This allows emergency routines to be executed for system recovery or to perform system shut down.

If the WDT is not serviced before the timer overflow, a system malfunction is assumed. As a result, the WDT NMI is triggered (assert FNMIWDT) and the reset prewarning is entered. The prewarning period lasts for  $30_{\rm H}$  count, after which the system is reset (assert WDTRST).

The WDT has a "programmable window boundary" which disallows any refresh during the WDT's count-up. A refresh during this window boundary constitutes an invalid access to the WDT, causing the reset prewarning to be entered but without triggering the WDT NMI. The system will still be reset after the prewarning period is over. The window boundary is from  $0000_{\rm H}$  to the value obtained from the concatenation of WDTWINB and  $00_{\rm H}$ .

After being serviced, the WDT continues counting up from the value ( $\langle WDTREL \rangle * 2^8$ ). The time period for an overflow of the WDT is programmable in two ways:

- The input frequency to the WDT can be selected to be either  $f_{\rm PCLK}/2$  or  $f_{\rm PCLK}/128$

- The reload value WDTREL for the high byte of WDT can be programmed in register WDTREL

The period,  $P_{\rm WDT}$ , between servicing the WDT and the next overflow can be determined by the following formula:

$$P_{WDT} = \frac{2^{(1 + WDTIN \times 6)} \times (2^{16} - WDTREL \times 2^8)}{f_{PCLK}}$$

(3.4)

If the Window-Boundary Refresh feature of the WDT is enabled, the period  $P_{\rm WDT}$  between servicing the WDT and the next overflow is shortened if WDTWINB is greater than WDTREL, see **Figure 29**. This period can be calculated using the same formula by replacing WDTREL with WDTWINB. For this feature to be useful, WDTWINB cannot be smaller than WDTREL.

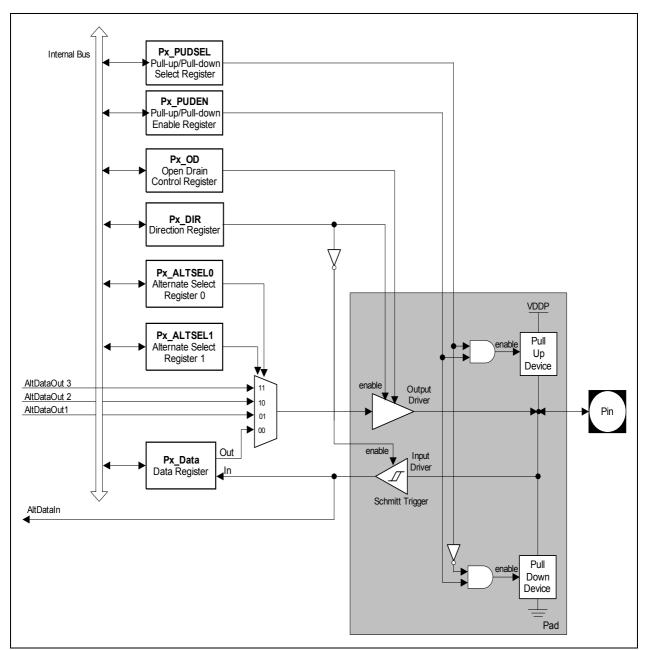

fractional divider) for generating a wide range of baud rates based on its input clock  $f_{PCLK}$ , see **Figure 30**.

#### Figure 30 Baud-rate Generator Circuitry

The baud rate timer is a count-down timer and is clocked by either the output of the fractional divider ( $f_{MOD}$ ) if the fractional divider is enabled (FDCON.FDEN = 1), or the output of the prescaler ( $f_{DIV}$ ) if the fractional divider is disabled (FDEN = 0). For baud rate generation, the fractional divider must be configured to fractional divider mode (FDCON.FDM = 0). This allows the baud rate control run bit BCON.R to be used to start or stop the baud rate timer. At each timer underflow, the timer is reloaded with the 8-bit reload value in register BG and one clock pulse is generated for the serial channel.

Enabling the fractional divider in normal divider mode (FDEN = 1 and FDM = 1) stops the baud rate timer and nullifies the effect of bit BCON.R. See **Section 3.14**.

The baud rate ( $f_{BR}$ ) value is dependent on the following parameters:

- Input clock  $f_{PCLK}$

- Prescaling factor (2<sup>BRPRE</sup>) defined by bit field BRPRE in register BCON

- Fractional divider (STEP/256) defined by register FDSTEP (to be considered only if fractional divider is enabled and operating in fractional divider mode)

- 8-bit reload value (BR\_VALUE) for the baud rate timer defined by register BG

The following formulas calculate the final baud rate without and with the fractional divider respectively:

baud rate =

$$\frac{f_{PCLK}}{16 \times 2^{BRPRE} \times (BR VALUE + 1)}$$

where  $2^{BRPRE} \times (BR_VALUE + 1) > 1$

(3.5)

baud rate =  $\frac{f_{PCLK}}{16 \times 2^{BRPRE} \times (BR_VALUE + 1)} \times \frac{STEP}{256}$

(3.6)

The maximum baud rate that can be generated is limited to  $f_{\text{PCLK}}/32$ . Hence, for a module clock of 24 MHz, the maximum achievable baud rate is 0.75 MBaud.

Standard LIN protocol can support a maximum baud rate of 20 kHz, the baud rate accuracy is not critical and the fractional divider can be disabled. Only the prescaler is used for auto baud rate calculation. For LIN fast mode, which supports the baud rate of 20 kHz to 115.2 kHz, the higher baud rates require the use of the fractional divider for greater accuracy.

**Table 30** lists the various commonly used baud rates with their corresponding parameter settings and deviation errors. The fractional divider is disabled and a module clock of 24 MHz is used.

| Baud rate  | Prescaling Factor<br>(2BRPRE) | Reload Value<br>(BR_VALUE + 1) | Deviation Error |  |  |  |  |  |

|------------|-------------------------------|--------------------------------|-----------------|--|--|--|--|--|

| 19.2 kBaud | 1 (BRPRE=000 <sub>B</sub> )   | 78 (4E <sub>H</sub> )          | 0.17 %          |  |  |  |  |  |

| 9600 Baud  | 1 (BRPRE=000 <sub>B</sub> )   | 156 (9C <sub>H</sub> )         | 0.17 %          |  |  |  |  |  |

| 4800 Baud  | 2 (BRPRE=001 <sub>B</sub> )   | 156 (9C <sub>H</sub> )         | 0.17 %          |  |  |  |  |  |

| 2400 Baud  | 4 (BRPRE=010 <sub>B</sub> )   | 156 (9С <sub>Н</sub> )         | 0.17 %          |  |  |  |  |  |

Table 30

Typical Baud rates for UART with Fractional Divider disabled

The fractional divider allows baud rates of higher accuracy (lower deviation error) to be generated. **Table 31** lists the resulting deviation errors from generating a baud rate of 115.2 kHz, using different module clock frequencies. The fractional divider is enabled (fractional divider mode) and the corresponding parameter settings are shown.

## 3.16 High-Speed Synchronous Serial Interface

The High-Speed Synchronous Serial Interface (SSC) supports full-duplex and half-duplex synchronous communication. The serial clock signal can be generated by the SSC internally (master mode), using its own 16-bit baud-rate generator, or can be received from an external master (slave mode). Data width, shift direction, clock polarity and phase are programmable. This allows communication with SPI-compatible devices or devices using other synchronous serial interfaces.

#### Features

- Master and slave mode operation

- Full-duplex or half-duplex operation

- Transmit and receive buffered

- Flexible data format

- Programmable number of data bits: 2 to 8 bits

- Programmable shift direction: LSB or MSB shift first

- Programmable clock polarity: idle low or high state for the shift clock

- Programmable clock/data phase: data shift with leading or trailing edge of the shift clock

- Variable baud rate

- Compatible with Serial Peripheral Interface (SPI)

- Interrupt generation

- On a transmitter empty condition

- On a receiver full condition

- On an error condition (receive, phase, baud rate, transmit error)

Data is transmitted or received on lines TXD and RXD, which are normally connected to the pins MTSR (Master Transmit/Slave Receive) and MRST (Master Receive/Slave Transmit). The clock signal is output via line MS\_CLK (Master Serial Shift Clock) or input via line SS\_CLK (Slave Serial Shift Clock). Both lines are normally connected to the pin SCLK. Transmission and reception of data are double-buffered.

Figure 32 shows the block diagram of the SSC.

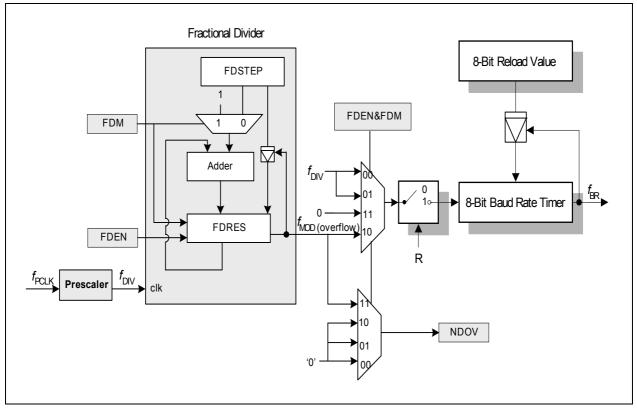

# 3.20 Controller Area Network (MultiCAN)

The MultiCAN module contains two Full-CAN nodes operating independently or exchanging data and remote frames via a gateway function. Transmission and reception of CAN frames is handled in accordance to CAN specification V2.0 B active. Each CAN node can receive and transmit standard frames with 11-bit identifiers as well as extended frames with 29-bit identifiers.

Both CAN nodes share a common set of message objects, where each message object may be individually allocated to one of the CAN nodes. Besides serving as a storage container for incoming and outgoing frames, message objects may be combined to build gateways between the CAN nodes or to setup a FIFO buffer.

The message objects are organized in double chained lists, where each CAN node has it's own list of message objects. A CAN node stores frames only into message objects that are allocated to the list of the CAN node. It only transmits messages from objects of this list. A powerful, command driven list controller performs all list operations.

The bit timings for the CAN nodes are derived from the peripheral clock ( $f_{CAN}$ ) and are programmable up to a data rate of 1 MBaud. A pair of receive and transmit pins connects each CAN node to a bus transceiver.

Figure 34 Overview of the MultiCAN

## Features

Compliant to ISO 11898.

## 4.2.2 Supply Threshold Characteristics

Table 39 provides the characteristics of the supply threshold in the XC886/888.

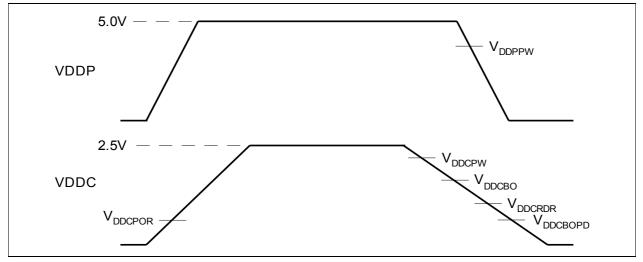

Figure 38 Supply Threshold Parameters

| Table 39 | Supply Threshold Parameters | (Operating Conditions apply) |

|----------|-----------------------------|------------------------------|

|----------|-----------------------------|------------------------------|

| Parameters                                                         | Symbol               |    | L    | Unit |      |   |

|--------------------------------------------------------------------|----------------------|----|------|------|------|---|

|                                                                    |                      |    | min. | typ. | max. |   |

| $V_{\rm DDC}$ prewarning voltage <sup>1)</sup>                     | V <sub>DDCPW</sub>   | CC | 2.2  | 2.3  | 2.4  | V |

| $V_{\text{DDC}}$ brownout voltage in active mode <sup>1)</sup>     | V <sub>DDCBO</sub>   | СС | 2.0  | 2.1  | 2.2  | V |

| RAM data retention voltage                                         | V <sub>DDCRDR</sub>  | CC | 0.9  | 1.0  | 1.1  | V |

| $V_{\text{DDC}}$ brownout voltage in power-down mode <sup>2)</sup> | V <sub>DDCBOPD</sub> | СС | 1.3  | 1.5  | 1.7  | V |

| $V_{\rm DDP}$ prewarning voltage <sup>3)</sup>                     | V <sub>DDPPW</sub>   | CC | 3.4  | 4.0  | 4.6  | V |

| Power-on reset voltage <sup>2)4)</sup>                             | VDDCPOR              | CC | 1.3  | 1.5  | 1.7  | V |

1) Detection is disabled in power-down mode.

2) Detection is enabled in both active and power-down mode.

Detection is enabled for external power supply of 5.0V. Detection must be disabled for external power supply of 3.3V.

4) The reset of EVR is extended by 300 µs typically after the VDDC reaches the power-on reset voltage.

| Parameter                   | Symbol           | Limit              | Values             | Unit | <b>Test Condition</b>                 |

|-----------------------------|------------------|--------------------|--------------------|------|---------------------------------------|

|                             |                  | typ. <sup>1)</sup> | max. <sup>2)</sup> |      |                                       |

| V <sub>DDP</sub> = 5V Range |                  |                    |                    |      | •                                     |

| Power-Down Mode             | I <sub>PDP</sub> | 1                  | 10                 | μA   | $T_{\rm A}$ = + 25 °C <sup>3)4)</sup> |

|                             |                  | -                  | 30                 | μA   | $T_{\rm A}$ = + 85 °C <sup>4)5)</sup> |

Power Down Current (Operating Conditions apply: U able 10 - E (1 - C )

1) The typical  $I_{PDP}$  values are measured at  $V_{DDP}$  = 5.0 V.

2) The maximum  $I_{PDP}$  values are measured at  $V_{DDP}$  = 5.5 V.

3)  $I_{PDP}$  has a maximum value of 200  $\mu$ A at  $T_A$  = + 125 °C.

4)  $I_{PDP}$  is measured with: RESET =  $V_{DDP}$ ,  $V_{AGND}$ =  $V_{SS}$ , RXD/INT0 =  $V_{DDP}$ ; rest of the ports are programmed to be input with either internal pull devices enabled or driven externally to ensure no floating inputs.

5) Not subjected to production test, verified by design/characterization.

## 4.3 AC Parameters

The electrical characteristics of the AC Parameters are detailed in this section.

## 4.3.1 Testing Waveforms

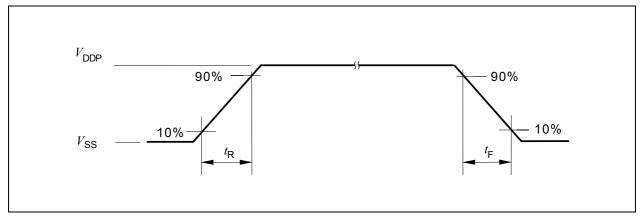

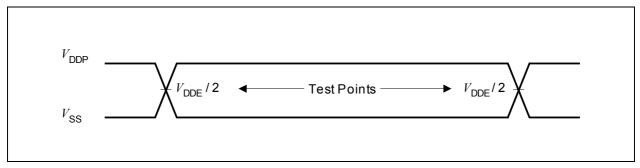

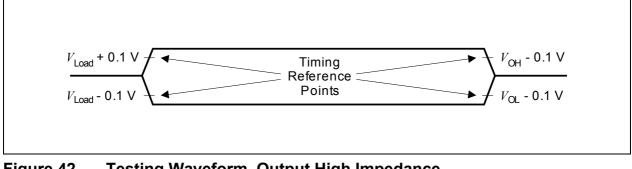

The testing waveforms for rise/fall time, output delay and output high impedance are shown in **Figure 40**, **Figure 41** and **Figure 42**.

Figure 40 Rise/Fall Time Parameters

Figure 41 Testing Waveform, Output Delay

Figure 42 Testing Waveform, Output High Impedance

# 4.3.3 Power-on Reset and PLL Timing

**Table 49** provides the characteristics of the power-on reset and PLL timing in the XC886/888.

| Table 46 | Power-On Reset and PLL Timing (Operating Conditions apply) |

|----------|------------------------------------------------------------|

|          |                                                            |

| Parameter Symbol                    |                    |    | Limit Values |      |      | Unit | Test Conditions                                                              |  |

|-------------------------------------|--------------------|----|--------------|------|------|------|------------------------------------------------------------------------------|--|

|                                     |                    |    | min.         | typ. | max. |      |                                                                              |  |

| Pad operating voltage               | $V_{PAD}$          | CC | 2.3          | -    | -    | V    | 1)                                                                           |  |

| On-Chip Oscillator<br>start-up time | t <sub>OSCST</sub> | СС | -            | -    | 500  | ns   | 1)                                                                           |  |

| Flash initialization time           | t <sub>FINIT</sub> | CC | _            | 160  | _    | μS   | 1)                                                                           |  |

| RESET hold time                     | t <sub>RST</sub>   | SR | -            | 500  | _    | μS   | $V_{\rm DDP}$ rise time<br>(10% – 90%) $\leq$<br>500 $\mu$ s <sup>1)2)</sup> |  |

| PLL lock-in in time                 | t <sub>LOCK</sub>  | CC | -            | -    | 200  | μS   | 1)                                                                           |  |

| PLL accumulated jitter              | $D_{P}$            |    | -            | _    | 0.7  | ns   | 1)3)                                                                         |  |

1) Not all parameters are 100% tested, but are verified by design/characterization and test correlation.

2) RESET signal has to be active (low) until  $V_{\text{DDC}}$  has reached 90% of its maximum value (typ. 2.5 V).

3) PLL lock at 96 MHz using a 4 MHz external oscillator. The PLL Divider settings are K = 2, N = 48 and P = 1.

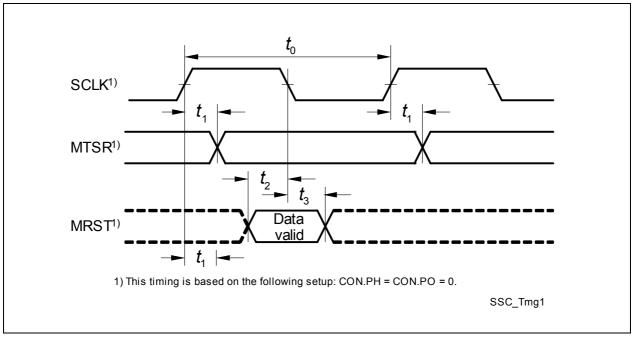

## 4.3.7 SSC Master Mode Timing

Table 51 provides the characteristics of the SSC timing in the XC886/888.

| Table 51 | SSC Master Mode Timing (Operating Conditions apply; CL = 50 pF) |

|----------|-----------------------------------------------------------------|

|----------|-----------------------------------------------------------------|

| Parameter            | Symbol                |    | Limi               | t Values | Unit | Test       |

|----------------------|-----------------------|----|--------------------|----------|------|------------|

|                      |                       |    | min.               | max.     |      | Conditions |

| SCLK clock period    | t <sub>0</sub>        | CC | 2*T <sub>SSC</sub> | –        | ns   | 1)2)       |

| MTSR delay from SCLK | t <sub>1</sub>        | CC | 0                  | 8        | ns   | 2)         |

| MRST setup to SCLK   | <i>t</i> <sub>2</sub> | SR | 24                 | -        | ns   | 2)         |

| MRST hold from SCLK  | t <sub>3</sub>        | SR | 0                  | -        | ns   | 2)         |

1)  $T_{SSCmin} = T_{CPU} = 1/f_{CPU}$ . When  $f_{CPU} = 24$  MHz,  $t_0 = 83.3$  ns.  $T_{CPU}$  is the CPU clock period.

2) Not all parameters are 100% tested, but are verified by design/characterization and test correlation.

Figure 52 SSC Master Mode Timing

#### Package and Quality Declaration

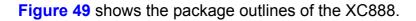

### Figure 49 PG-TQFP-64 Package Outline

### Package and Quality Declaration

## 5.3 Quality Declaration

Table 2 shows the characteristics of the quality parameters in the XC886/888.

#### Table 2Quality Parameters

| Parameter                                                             | Symbol           | Limit V | alues | Unit | Notes                                                |

|-----------------------------------------------------------------------|------------------|---------|-------|------|------------------------------------------------------|

|                                                                       |                  | Min.    | Max.  |      |                                                      |

| ESD susceptibility<br>according to Human Body<br>Model (HBM)          | V <sub>HBM</sub> | -       | 2000  | V    | Conforming to<br>EIA/JESD22-<br>A114-B <sup>1)</sup> |

| ESD susceptibility<br>according to Charged<br>Device Model (CDM) pins | V <sub>CDM</sub> | -       | 500   | V    | Conforming to JESD22-C101-C <sup>1)</sup>            |

1) Not all parameters are 100% tested, but are verified by design/characterization and test correlation.