Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                    |

|----------------------------|------------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                           |

| Core Processor             | XC800                                                                              |

| Core Size                  | 8-Bit                                                                              |

| Speed                      | 24MHz                                                                              |

| Connectivity               | CANbus, LINbus, SSI, UART/USART                                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                              |

| Number of I/O              | 48                                                                                 |

| Program Memory Size        | 24KB (24K x 8)                                                                     |

| Program Memory Type        | FLASH                                                                              |

| EEPROM Size                | -                                                                                  |

| RAM Size                   | 1.75K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                        |

| Data Converters            | A/D 8x10b                                                                          |

| Oscillator Type            | Internal                                                                           |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                      |

| Package / Case             | 64-LQFP                                                                            |

| Supplier Device Package    | PG-TQFP-64                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/sak-xc888clm-6ffi-5v-ac |

|                            |                                                                                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Edition 2009-07 Published by Infineon Technologies AG 81726 Munich, Germany © 2009 Infineon Technologies AG All Rights Reserved.

#### Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

## **General Device Information**

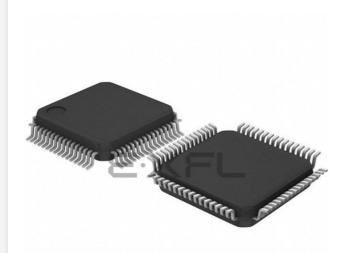

# 2.2 Logic Symbol

The logic symbols of the XC886/888 are shown in Figure 3.

Figure 3 XC886/888 Logic Symbol

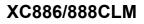

Address Extension by Mapping

# 3.2.4 XC886/888 Register Overview

The SFRs of the XC886/888 are organized into groups according to their functional units. The contents (bits) of the SFRs are summarized in **Chapter 3.2.4.1** to **Chapter 3.2.4.14**.

Note: The addresses of the bitaddressable SFRs appear in bold typeface.

# 3.2.4.1 CPU Registers

The CPU SFRs can be accessed in both the standard and mapped memory areas (RMAP = 0 or 1).

| Addr            | Register Name                                                            | Bit                                | 7         | 6    | 5    | 4           | 3         | 2    | 1    | 0          |  |  |

|-----------------|--------------------------------------------------------------------------|------------------------------------|-----------|------|------|-------------|-----------|------|------|------------|--|--|

| RMAP =          | = 0 or 1                                                                 | I.                                 |           |      |      |             |           |      |      |            |  |  |

| 81 <sub>H</sub> | SP Reset: 07 <sub>H</sub>                                                | Bit Field                          | SP        |      |      |             |           |      |      |            |  |  |

|                 | Stack Pointer Register                                                   | Туре                               | rw        |      |      |             |           |      |      |            |  |  |

| 82 <sub>H</sub> | DPL Reset: 00 <sub>H</sub>                                               | Bit Field                          | DPL7      | DPL6 | DPL5 | DPL4        | DPL3      | DPL2 | DPL1 | DPL0       |  |  |

|                 | Data Pointer Register Low                                                | Туре                               | rw        | rw   | rw   | rw          | rw        | rw   | rw   | rw         |  |  |

| 83 <sub>H</sub> | DPH Reset: 00 <sub>H</sub>                                               | Bit Field                          | DPH7      | DPH6 | DPH5 | DPH4        | DPH3      | DPH2 | DPH1 | DPH0       |  |  |

|                 | Data Pointer Register High                                               | Туре                               | rw        | rw   | rw   | rw          | rw        | rw   | rw   | rw         |  |  |

| 87 <sub>H</sub> | PCON Reset: 00 <sub>H</sub>                                              | Bit Field                          | SMOD      |      | 0    |             | GF1       | GF0  | 0    | IDLE       |  |  |

|                 | Power Control Register                                                   | Туре                               | rw        |      | r    |             | rw        | rw   | r    | rw         |  |  |

| <sup>88</sup> H | TCON Reset: 00 <sub>H</sub>                                              | Bit Field                          | TF1       | TR1  | TF0  | TR0         | IE1       | IT1  | IE0  | IT0        |  |  |

|                 | Timer Control Register                                                   | Туре                               | rwh       | rw   | rwh  | rw          | rwh       | rw   | rwh  | rw         |  |  |

| 89 <sub>H</sub> | TMOD Reset: 00 <sub>H</sub><br>Timer Mode Register                       | Bit Field                          | GATE<br>1 | T1S  | T1M  |             | GATE<br>0 | TOS  | том  |            |  |  |

|                 |                                                                          | Туре                               | rw        | rw   | r    | w           | rw        | rw   | r    | w          |  |  |

| 8A <sub>H</sub> | TL0 Reset: 00 <sub>H</sub>                                               | set: 00 <sub>H</sub> Bit Field VAL |           |      |      |             |           |      |      |            |  |  |

|                 | Timer 0 Register Low                                                     | Туре                               |           |      |      | rv          | vh        |      |      |            |  |  |

| 8B <sub>H</sub> | TL1 Reset: 00 <sub>H</sub>                                               | Bit Field                          | VAL       |      |      |             |           |      |      |            |  |  |

|                 | Timer 1 Register Low                                                     | Туре                               | rwh       |      |      |             |           |      |      |            |  |  |

| 8C <sub>H</sub> | THO Reset: 00 <sub>H</sub>                                               | Bit Field                          |           |      | VAL  |             |           |      |      |            |  |  |

|                 | Timer 0 Register High                                                    | Туре                               |           |      |      | rv          | vh        |      |      |            |  |  |

| 8D <sub>H</sub> | TH1 Reset: 00 <sub>H</sub>                                               | Bit Field                          |           |      |      | V           | AL        |      |      |            |  |  |

|                 | Timer 1 Register High                                                    | Туре                               |           |      |      | rv          | vh        |      |      |            |  |  |

| 98 <sub>H</sub> | SCON Reset: 00 <sub>H</sub>                                              | Bit Field                          | SM0       | SM1  | SM2  | REN         | TB8       | RB8  | TI   | RI         |  |  |

|                 | Serial Channel Control Register                                          | Туре                               | rw        | rw   | rw   | rw          | rw        | rwh  | rwh  | rwh        |  |  |

| 99 <sub>H</sub> | SBUF Reset: 00 <sub>H</sub>                                              | Bit Field                          |           |      |      | V           | AL        |      |      |            |  |  |

|                 | Serial Data Buffer Register                                              | Туре                               |           |      |      | rv          | vh        |      |      |            |  |  |

| A2 <sub>H</sub> | A2 <sub>H</sub> EO Reset: 00 <sub>H</sub><br>Extended Operation Register |                                    |           | 0    |      | TRAP_<br>EN |           | 0    |      | DPSE<br>L0 |  |  |

|                 |                                                                          | Туре                               |           | r    |      | rw          | r         |      |      | rw         |  |  |

### Table 5 CPU Register Overview

| Addr            | Register Name              | Bit       | 7        | 6    | 5 | 4  | 3  | 2 | 1 | 0 |  |  |

|-----------------|----------------------------|-----------|----------|------|---|----|----|---|---|---|--|--|

| B3 <sub>H</sub> | MR1 Reset: 00 <sub>H</sub> | Bit Field |          | DATA |   |    |    |   |   |   |  |  |

|                 | MDU Result Register 1      | Туре      |          | rh   |   |    |    |   |   |   |  |  |

| B4 <sub>H</sub> | MD2 Reset: 00 <sub>H</sub> | Bit Field |          |      |   | DA | TA |   |   |   |  |  |

|                 | MDU Operand Register 2     | Туре      |          |      |   | r  | w  |   |   |   |  |  |

| B4 <sub>H</sub> | MR2 Reset: 00 <sub>H</sub> | Bit Field |          |      |   | DA | TA |   |   |   |  |  |

|                 | MDU Result Register 2      | Туре      |          |      |   | r  | h  |   |   |   |  |  |

| в5 <sub>Н</sub> | MD3 Reset: 00 <sub>H</sub> | Bit Field | DATA     |      |   |    |    |   |   |   |  |  |

|                 | MDU Operand Register 3     | Туре      |          | rw   |   |    |    |   |   |   |  |  |

| в5 <sub>Н</sub> | MR3 Reset: 00 <sub>H</sub> | Bit Field | d DATA   |      |   |    |    |   |   |   |  |  |

|                 | MDU Result Register 3      | Туре      |          |      |   | r  | h  |   |   |   |  |  |

| B6 <sub>H</sub> | MD4 Reset: 00 <sub>H</sub> | Bit Field | DATA     |      |   |    |    |   |   |   |  |  |

|                 | MDU Operand Register 4     | Туре      |          |      |   | r  | w  |   |   |   |  |  |

| B6 <sub>H</sub> | MR4 Reset: 00 <sub>H</sub> | Bit Field |          |      |   | DA | TA |   |   |   |  |  |

|                 | MDU Result Register 4      | Туре      |          |      |   | r  | h  |   |   |   |  |  |

| в7 <sub>Н</sub> | MD5 Reset: 00 <sub>H</sub> | Bit Field | eld DATA |      |   |    |    |   |   |   |  |  |

|                 | MDU Operand Register 5     | Туре      | rw       |      |   |    |    |   |   |   |  |  |

| в7 <sub>Н</sub> | MR5 Reset: 00 <sub>H</sub> | Bit Field |          |      |   | DA | TA |   |   |   |  |  |

|                 | MDU Result Register 5      | Туре      |          |      |   | r  | 'n |   |   |   |  |  |

### Table 6MDU Register Overview (cont'd)

# 3.2.4.3 CORDIC Registers

The CORDIC SFRs can be accessed in the mapped memory area (RMAP = 1).

### Table 7 CORDIC Register Overview

| Addr            | Register Name                    | Bit       | 7     | 6 | 5 | 4  | 3   | 2 | 1 | 0 |

|-----------------|----------------------------------|-----------|-------|---|---|----|-----|---|---|---|

| RMAP =          | = 1                              |           |       |   |   |    |     | 1 |   |   |

| 9A <sub>H</sub> | CD_CORDXL Reset: 00 <sub>H</sub> | Bit Field |       |   |   | DA | TAL |   |   |   |

|                 | CORDIC X Data Low Byte           | Туре      |       |   |   | r  | W   |   |   |   |

| 9B <sub>H</sub> | CD_CORDXH Reset: 00 <sub>H</sub> | Bit Field |       |   |   | DA | TAH |   |   |   |

|                 | CORDIC X Data High Byte          | Туре      |       |   |   | r  | W   |   |   |   |

| 9CH             | CD_CORDYL Reset: 00 <sub>H</sub> | Bit Field | DATAL |   |   |    |     |   |   |   |

|                 | CORDIC Y Data Low Byte           | Туре      |       |   |   | r  | W   |   |   |   |

| 9D <sub>H</sub> | CD_CORDYH Reset: 00 <sub>H</sub> | Bit Field | DATAH |   |   |    |     |   |   |   |

|                 | CORDIC Y Data High Byte          | Туре      |       |   |   | r  | W   |   |   |   |

| 9E <sub>H</sub> | CD_CORDZL Reset: 00 <sub>H</sub> | Bit Field |       |   |   | DA | TAL |   |   |   |

|                 | CORDIC Z Data Low Byte           | Туре      | rw    |   |   |    |     |   |   |   |

| 9F <sub>H</sub> | CD_CORDZH Reset: 00 <sub>H</sub> | Bit Field |       |   |   | DA | ТАН |   |   |   |

|                 | CORDIC Z Data High Byte          | Туре      |       |   |   | r  | W   |   |   |   |

# Table 11ADC Register Overview (cont'd)

| Addr            | Register Name                                                         | Bit       | 7                  | 6          | 5          | 4          | 3          | 2          | 1          | 0          |

|-----------------|-----------------------------------------------------------------------|-----------|--------------------|------------|------------|------------|------------|------------|------------|------------|

| D3 <sub>H</sub> | ADC_RESR3H Reset: 00 <sub>H</sub>                                     | Bit Field |                    |            |            | RES        | ULT        |            |            |            |

|                 | Result Register 3 High                                                | Туре      |                    |            |            | r          | h          |            |            |            |

| RMAP =          | 0, PAGE 3                                                             |           |                    |            |            |            |            |            |            |            |

| CA <sub>H</sub> | ADC_RESRA0L Reset: 00 <sub>H</sub>                                    | Bit Field | RESULT VF DRC CHNR |            |            |            |            |            |            |            |

|                 | Result Register 0, View A Low                                         | Туре      |                    | rh         |            | rh         | rh         |            | rh         |            |

| св <sub>Н</sub> | ADC_RESRA0H Reset: 00 <sub>H</sub>                                    | Bit Field |                    |            |            | RES        | SULT       |            |            |            |

|                 | Result Register 0, View A High                                        | Туре      |                    |            |            | r          | h          |            |            |            |

| сс <sub>Н</sub> | ADC_RESRA1L Reset: 00 <sub>H</sub>                                    | Bit Field |                    | RESULT     |            | VF         | DRC        |            | CHNR       |            |

|                 | Result Register 1, View A Low                                         | Туре      |                    | rh         |            | rh         | rh         |            | rh         |            |

| CD <sub>H</sub> | ADC_RESRA1H Reset: 00 <sub>H</sub>                                    | Bit Field |                    |            |            | RES        | SULT       |            |            |            |

|                 | Result Register 1, View A High                                        | Туре      |                    |            |            | r          | h          |            |            |            |

| Ce <sub>H</sub> | ADC_RESRA2L Reset: 00 <sub>H</sub>                                    | Bit Field |                    | RESULT     |            | VF         | DRC        |            | CHNR       |            |

|                 | Result Register 2, View A Low                                         | Туре      |                    | rh         |            | rh         | rh         |            | rh         |            |

| CF <sub>H</sub> | ADC_RESRA2H Reset: 00 <sub>H</sub>                                    | Bit Field |                    |            |            | RES        | SULT       |            |            |            |

|                 | Result Register 2, View A High                                        | Туре      |                    |            |            | r          | h          |            |            |            |

| D2 <sub>H</sub> | ADC_RESRA3L Reset: 00 <sub>H</sub>                                    | Bit Field | RESULT VF          |            | DRC CHNR   |            |            |            |            |            |

|                 | Result Register 3, View A Low                                         | Туре      |                    | rh         |            | rh         | rh         |            | rh         |            |

| D3 <sub>H</sub> | ADC_RESRA3H Reset: 00 <sub>H</sub>                                    | Bit Field |                    |            |            | RES        | ULT        |            |            |            |

|                 | Result Register 3, View A High                                        | Туре      |                    |            |            | r          | h          |            |            |            |

| RMAP =          | = 0, PAGE 4                                                           |           |                    |            |            |            |            |            |            |            |

| CA <sub>H</sub> | ADC_RCR0 Reset: 00 <sub>H</sub><br>Result Control Register 0          | Bit Field | VFCT<br>R          | WFR        | 0          | IEN        |            | 0          |            | DRCT<br>R  |

|                 |                                                                       | Туре      | rw                 | rw         | r          | rw         |            | r          |            | rw         |

| св <sub>Н</sub> | ADC_RCR1 Reset: 00 <sub>H</sub><br>Result Control Register 1          | Bit Field | VFCT<br>R          | WFR        | 0          | IEN        |            | 0          |            | DRCT<br>R  |

|                 |                                                                       | Туре      | rw                 | rw         | r          | rw         |            | r          |            | rw         |

| сс <sup>н</sup> | ADC_RCR2 Reset: 00 <sub>H</sub><br>Result Control Register 2          | Bit Field | VFCT<br>R          | WFR        | 0          | IEN        |            | 0          |            | DRCT<br>R  |

|                 |                                                                       | Туре      | rw                 | rw         | r          | rw         |            | r          |            | rw         |

| CDH             | ADC_RCR3 Reset: 00 <sub>H</sub><br>Result Control Register 3          | Bit Field | VFCT<br>R          | WFR        | 0          | IEN        |            | 0          |            | DRCT<br>R  |

|                 |                                                                       | Туре      | rw                 | rw         | r          | rw         |            | r          |            | rw         |

| Ce <sub>H</sub> | ADC_VFCR Reset: 00 <sub>H</sub>                                       | Bit Field |                    |            | ט          |            | VFC3       | VFC2       | VFC1       | VFC0       |

|                 | Valid Flag Clear Register                                             | Туре      |                    |            | r          |            | w          | w          | w          | w          |

| RMAP =          | = 0, PAGE 5                                                           |           |                    |            |            |            |            |            |            |            |

| CA <sub>H</sub> | ADC_CHINFR Reset: 00 <sub>H</sub><br>Channel Interrupt Flag Register  | Bit Field | CHINF<br>7         | CHINF<br>6 | CHINF<br>5 | CHINF<br>4 | CHINF<br>3 | CHINF<br>2 | CHINF<br>1 | CHINF<br>0 |

|                 |                                                                       | Туре      | rh                 | rh         | rh         | rh         | rh         | rh         | rh         | rh         |

| св <sub>Н</sub> | ADC_CHINCR Reset: 00 <sub>H</sub><br>Channel Interrupt Clear Register | Bit Field | CHINC<br>7         | CHINC<br>6 | CHINC<br>5 | CHINC<br>4 | CHINC<br>3 | CHINC<br>2 | CHINC<br>1 | CHINC<br>0 |

|                 |                                                                       | Туре      | w                  | w          | w          | w          | w          | w          | w          | w          |

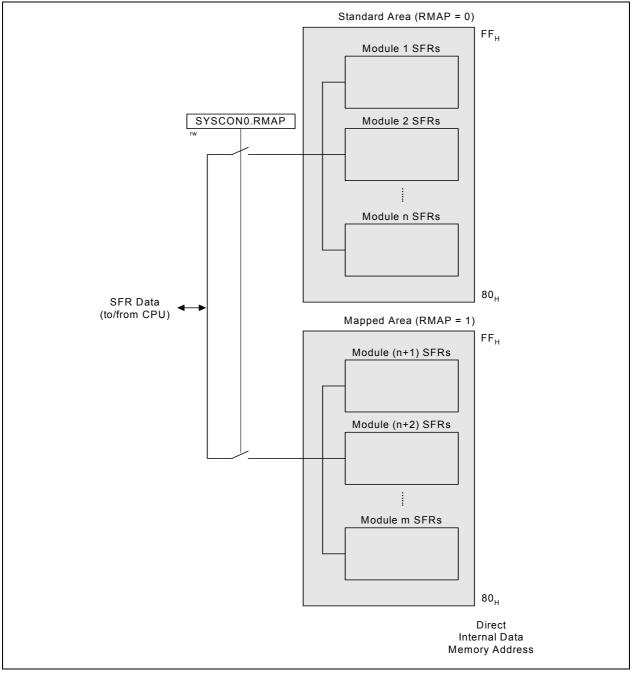

Figure 17 Interrupt Request Sources (Part 4)

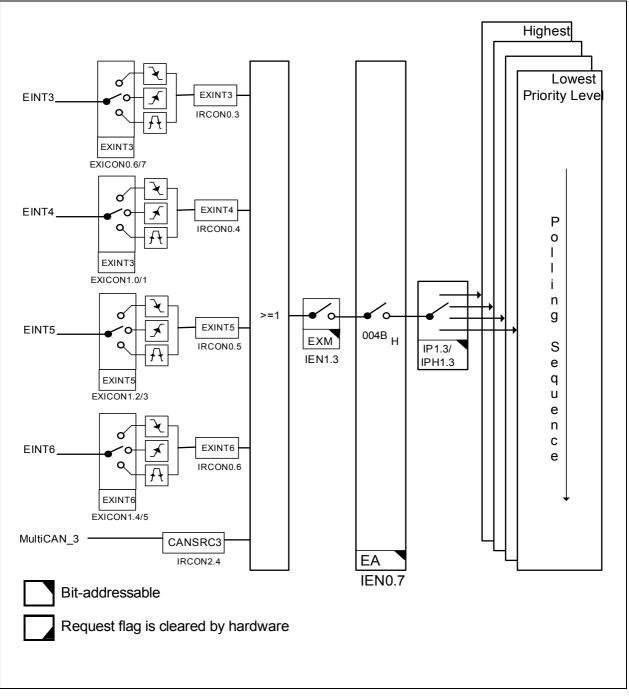

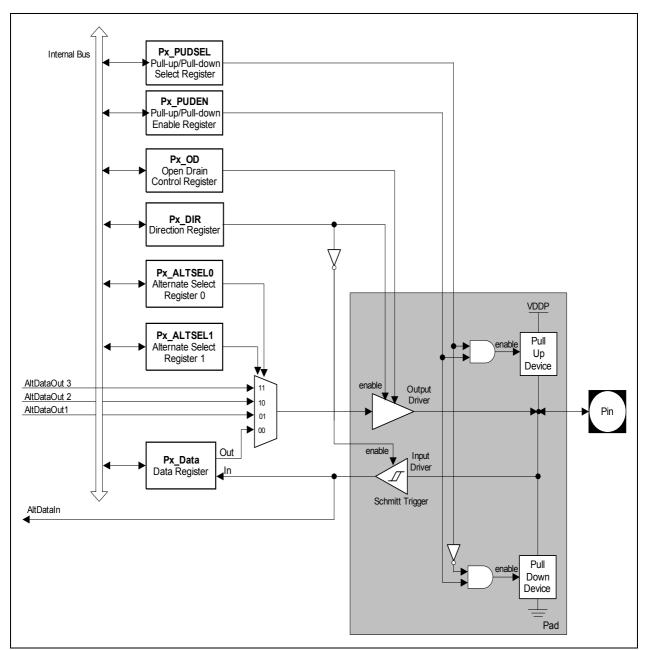

# 3.5 Parallel Ports

The XC886 has 34 port pins organized into five parallel ports, Port 0 (P0) to Port 4 (P4), while the XC888 has 48 port pins organized into six parallel ports, Port 0 (P0) to Port 5 (P5). Each pin has a pair of internal pull-up and pull-down devices that can be individually enabled or disabled. Ports P0, P1, P3, P4 and P5 are bidirectional and can be used as general purpose input/output (GPIO) or to perform alternate input/output functions for the on-chip peripherals. When configured as an output, the open drain mode can be selected. Port P2 is an input-only port, providing general purpose input functions, alternate input functions for the on-chip peripherals. Converter (ADC).

### **Bidirectional Port Features**

- Configurable pin direction

- Configurable pull-up/pull-down devices

- Configurable open drain mode

- Transfer of data through digital inputs and outputs (general purpose I/O)

- Alternate input/output for on-chip peripherals

#### Input Port Features

- Configurable input driver

- Configurable pull-up/pull-down devices

- Receive of data through digital input (general purpose input)

- Alternate input for on-chip peripherals

- Analog input for ADC module

Figure 19 General Structure of Bidirectional Port

If the WDT is not serviced before the timer overflow, a system malfunction is assumed. As a result, the WDT NMI is triggered (assert FNMIWDT) and the reset prewarning is entered. The prewarning period lasts for  $30_{\rm H}$  count, after which the system is reset (assert WDTRST).

The WDT has a "programmable window boundary" which disallows any refresh during the WDT's count-up. A refresh during this window boundary constitutes an invalid access to the WDT, causing the reset prewarning to be entered but without triggering the WDT NMI. The system will still be reset after the prewarning period is over. The window boundary is from  $0000_{\rm H}$  to the value obtained from the concatenation of WDTWINB and  $00_{\rm H}$ .

After being serviced, the WDT continues counting up from the value ( $\langle WDTREL \rangle * 2^8$ ). The time period for an overflow of the WDT is programmable in two ways:

- The input frequency to the WDT can be selected to be either  $f_{\rm PCLK}/2$  or  $f_{\rm PCLK}/128$

- The reload value WDTREL for the high byte of WDT can be programmed in register WDTREL

The period,  $P_{\rm WDT}$ , between servicing the WDT and the next overflow can be determined by the following formula:

$$P_{WDT} = \frac{2^{(1 + WDTIN \times 6)} \times (2^{16} - WDTREL \times 2^8)}{f_{PCLK}}$$

(3.4)

If the Window-Boundary Refresh feature of the WDT is enabled, the period  $P_{\rm WDT}$  between servicing the WDT and the next overflow is shortened if WDTWINB is greater than WDTREL, see **Figure 29**. This period can be calculated using the same formula by replacing WDTREL with WDTWINB. For this feature to be useful, WDTWINB cannot be smaller than WDTREL.

## 3.18 Timer 2 and Timer 21

Timer 2 and Timer 21 are 16-bit general purpose timers (THL2) that are fully compatible and have two modes of operation, a 16-bit auto-reload mode and a 16-bit one channel capture mode, see **Table 33**. As a timer, the timers count with an input clock of PCLK/12 (if prescaler is disabled). As a counter, they count 1-to-0 transitions on pin T2. In the counter mode, the maximum resolution for the count is PCLK/24 (if prescaler is disabled).

| Table 33           | Timer 2 Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mode               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Auto-reload        | <ul> <li>Up/Down Count Disabled</li> <li>Count up only</li> <li>Start counting from 16-bit reload value, overflow at FFFF<sub>H</sub></li> <li>Reload event configurable for trigger by overflow condition only, or by negative/positive edge at input pin T2EX as well</li> <li>Programmble reload value in register RC2</li> <li>Interrupt is generated with reload event</li> </ul>                                                                                                                                                                                                                                                                                                |

|                    | <ul> <li>Up/Down Count Enabled</li> <li>Count up or down, direction determined by level at input pin T2EX</li> <li>No interrupt is generated</li> <li>Count up <ul> <li>Start counting from 16-bit reload value, overflow at FFFF<sub>H</sub></li> <li>Reload event triggered by overflow condition</li> <li>Programmble reload value in register RC2</li> </ul> </li> <li>Count down <ul> <li>Start counting from FFFF<sub>H</sub>, underflow at value defined in register RC2</li> <li>Reload event triggered by underflow condition <ul> <li>Reload event triggered by underflow condition</li> <li>Reload event triggered by underflow condition</li> </ul> </li> </ul></li></ul> |

| Channel<br>capture | <ul> <li>Count up only</li> <li>Start counting from 0000<sub>H</sub>, overflow at FFFF<sub>H</sub></li> <li>Reload event triggered by overflow condition</li> <li>Reload value fixed at 0000<sub>H</sub></li> <li>Capture event triggered by falling/rising edge at pin T2EX</li> <li>Captured timer value stored in register RC2</li> <li>Interrupt is generated with reload or capture event</li> </ul>                                                                                                                                                                                                                                                                             |

# XC886/888CLM

## **Functional Description**

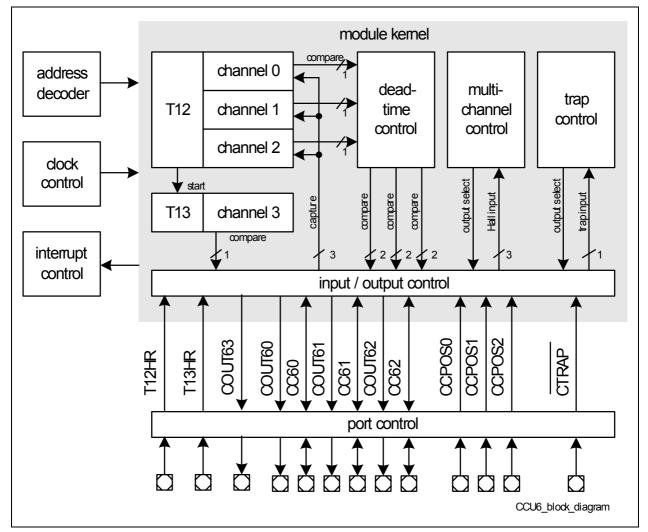

Figure 33 CCU6 Block Diagram

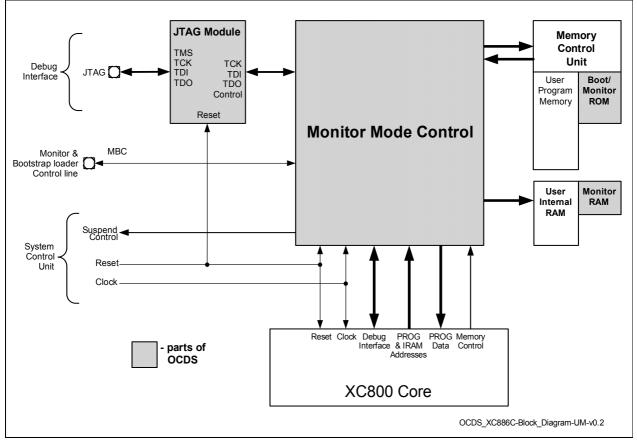

# 3.22.1 JTAG ID Register

This is a read-only register located inside the JTAG module, and is used to recognize the device(s) connected to the JTAG interface. Its content is shifted out when INSTRUCTION register contains the IDCODE command (opcode  $04_H$ ), and the same is also true immediately after reset.

The JTAG ID register contents for the XC886/888 Flash devices are given in Table 35.

| Device Type | Device Name    | JTAG ID                |  |

|-------------|----------------|------------------------|--|

| Flash       | XC886/888*-8FF | 1012 0083 <sub>H</sub> |  |

|             | XC886/888*-6FF | 1012 5083 <sub>H</sub> |  |

| ROM         | XC886/888*-8RF | 1013 C083 <sub>H</sub> |  |

|             | XC886/888*-6RF | 1013 D083 <sub>H</sub> |  |

## Table 35JTAG ID Summary

Note: The asterisk (\*) above denotes all possible device configurations.

103

# Table 36Chip Identification Number (cont'd)

| Product Variant   | Chip Identification Number |                       |                       |  |  |  |  |  |  |  |

|-------------------|----------------------------|-----------------------|-----------------------|--|--|--|--|--|--|--|

|                   | AA-Step                    | AB-Step               | AC-Step               |  |  |  |  |  |  |  |

| XC886-6FFA 3V3    | -                          | 095D1562 <sub>H</sub> | 0B5D1562 <sub>H</sub> |  |  |  |  |  |  |  |

| XC888-6FFA 3V3    | -                          | 095D1563 <sub>H</sub> | 0B5D1563 <sub>H</sub> |  |  |  |  |  |  |  |

| XC886CLM-8FFA 5V  | -                          | 09900102 <sub>H</sub> | 0B900102 <sub>H</sub> |  |  |  |  |  |  |  |

| XC888CLM-8FFA 5V  | -                          | 09900103 <sub>H</sub> | 0B900103 <sub>H</sub> |  |  |  |  |  |  |  |

| XC886LM-8FFA 5V   | -                          | 09900122 <sub>H</sub> | 0B900122 <sub>H</sub> |  |  |  |  |  |  |  |

| XC888LM-8FFA 5V   | -                          | 09900123 <sub>H</sub> | 0B900123 <sub>H</sub> |  |  |  |  |  |  |  |

| XC886CLM-6FFA 5V  | -                          | 09951502 <sub>H</sub> | 0B951502 <sub>H</sub> |  |  |  |  |  |  |  |

| XC888CLM-6FFA 5V  | -                          | 09951503 <sub>H</sub> | 0B951503 <sub>H</sub> |  |  |  |  |  |  |  |

| XC886LM-6FFA 5V   | -                          | 09951522 <sub>Н</sub> | 0B951522 <sub>H</sub> |  |  |  |  |  |  |  |

| XC888LM-6FFA 5V   | -                          | 09951523 <sub>H</sub> | 0B951523 <sub>H</sub> |  |  |  |  |  |  |  |

| XC886CM-8FFA 5V   | -                          | 09980102 <sub>H</sub> | 0B980102 <sub>H</sub> |  |  |  |  |  |  |  |

| XC888CM-8FFA 5V   | -                          | 09980103 <sub>H</sub> | 0B980103 <sub>H</sub> |  |  |  |  |  |  |  |

| XC886C-8FFA 5V    | -                          | 09980142 <sub>H</sub> | 0B980142 <sub>H</sub> |  |  |  |  |  |  |  |

| XC888C-8FFA 5V    | -                          | 09980143 <sub>H</sub> | 0B980143 <sub>H</sub> |  |  |  |  |  |  |  |

| XC886-8FFA 5V     | -                          | 09980162 <sub>H</sub> | 0B980162 <sub>H</sub> |  |  |  |  |  |  |  |

| XC888-8FFA 5V     | -                          | 09980163 <sub>H</sub> | 0B980163 <sub>H</sub> |  |  |  |  |  |  |  |

| XC886CM-6FFA 5V   | -                          | 099D1502 <sub>H</sub> | 0B9D1502 <sub>H</sub> |  |  |  |  |  |  |  |

| XC888CM-6FFA 5V   | -                          | 099D1503 <sub>H</sub> | 0B9D1503 <sub>H</sub> |  |  |  |  |  |  |  |

| XC886C-6FFA 5V    | -                          | 099D1542 <sub>H</sub> | 0B9D1542 <sub>H</sub> |  |  |  |  |  |  |  |

| XC888C-6FFA 5V    | -                          | 099D1543 <sub>H</sub> | 0B9D1543 <sub>H</sub> |  |  |  |  |  |  |  |

| XC886-6FFA 5V     | -                          | 099D1562 <sub>H</sub> | 0B9D1562 <sub>H</sub> |  |  |  |  |  |  |  |

| XC888-6FFA 5V     | -                          | 099D1563 <sub>H</sub> | 0B9D1563 <sub>H</sub> |  |  |  |  |  |  |  |

| ROM Devices       |                            |                       |                       |  |  |  |  |  |  |  |

| XC886CLM-8RFA 3V3 | 22400502 <sub>H</sub>      | -                     | -                     |  |  |  |  |  |  |  |

| XC888CLM-8RFA 3V3 | 22400503 <sub>H</sub>      | -                     | -                     |  |  |  |  |  |  |  |

| XC886LM-8RFA 3V3  | 22400522 <sub>H</sub>      | -                     | -                     |  |  |  |  |  |  |  |

| XC888LM-8RFA 3V3  | 22400523 <sub>H</sub>      | -                     | -                     |  |  |  |  |  |  |  |

| XC886CLM-6RFA 3V3 | 22411502 <sub>H</sub>      | -                     | -                     |  |  |  |  |  |  |  |

| XC888CLM-6RFA 3V3 | 22411503 <sub>H</sub>      | -                     | -                     |  |  |  |  |  |  |  |

# Table 36Chip Identification Number (cont'd)

| Product Variant | Chip Identification Number |         |         |  |  |  |  |  |  |

|-----------------|----------------------------|---------|---------|--|--|--|--|--|--|

|                 | AA-Step                    | AB-Step | AC-Step |  |  |  |  |  |  |

| XC888CM-6RFA 5V | 22891503 <sub>H</sub>      | -       | -       |  |  |  |  |  |  |

| XC886C-6RFA 5V  | 22891542 <sub>H</sub>      | -       | -       |  |  |  |  |  |  |

| XC888C-6RFA 5V  | 22891543 <sub>H</sub>      | -       | -       |  |  |  |  |  |  |

| XC886-6RFA 5V   | 22891562 <sub>H</sub>      | -       | -       |  |  |  |  |  |  |

| XC888-6RFA 5V   | 22891563 <sub>H</sub>      | -       | -       |  |  |  |  |  |  |

### **Electrical Parameters**

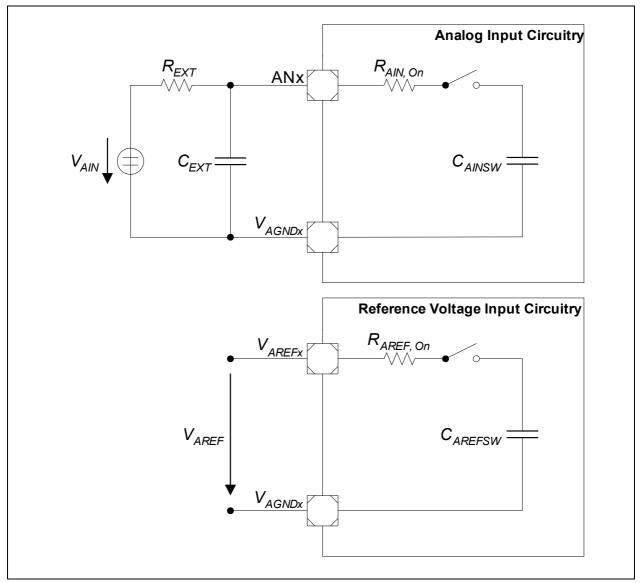

Figure 39 ADC Input Circuits

#### **Electrical Parameters**

## 4.3 AC Parameters

The electrical characteristics of the AC Parameters are detailed in this section.

## 4.3.1 Testing Waveforms

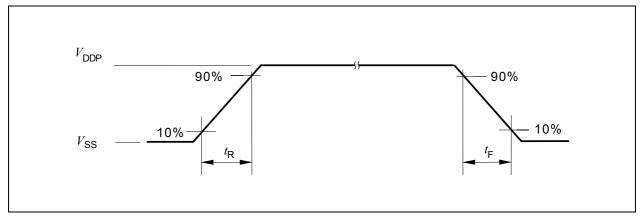

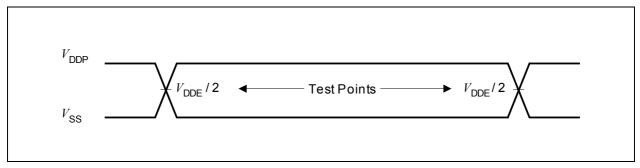

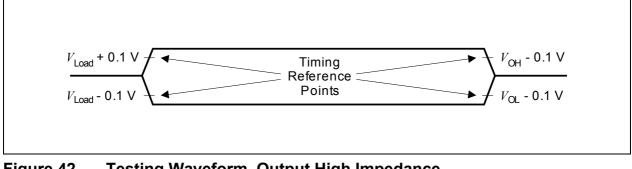

The testing waveforms for rise/fall time, output delay and output high impedance are shown in **Figure 40**, **Figure 41** and **Figure 42**.

Figure 40 Rise/Fall Time Parameters

Figure 41 Testing Waveform, Output Delay

Figure 42 Testing Waveform, Output High Impedance

# XC886/888CLM

**Electrical Parameters**

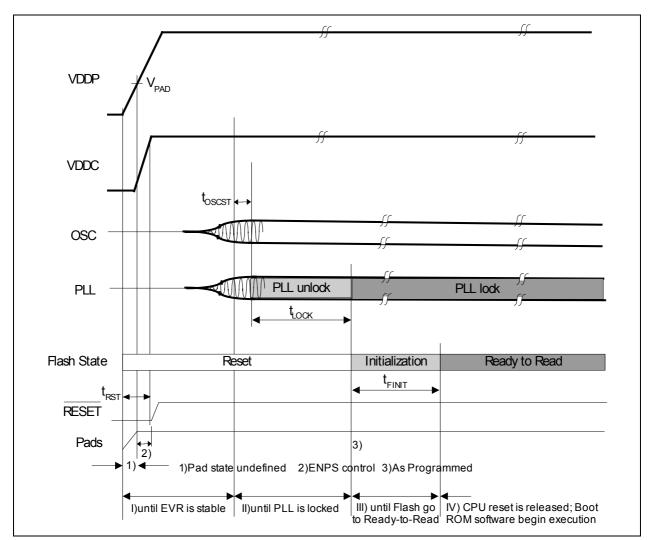

Figure 44 Power-on Reset Timing

#### **Electrical Parameters**

# 4.3.4 On-Chip Oscillator Characteristics

Table 47 provides the characteristics of the on-chip oscillator in the XC886/888.

| Table 47 | On-chip Oscillator Characteristics (Operating Conditions apply) |

|----------|-----------------------------------------------------------------|

|----------|-----------------------------------------------------------------|

| Parameter                      | Sym              | bol | Lin  | nit Va | lues | Unit | Test Conditions                                                                                                                    |

|--------------------------------|------------------|-----|------|--------|------|------|------------------------------------------------------------------------------------------------------------------------------------|

|                                |                  |     | min. | typ.   | max. |      |                                                                                                                                    |

| Nominal frequency              | f <sub>nom</sub> | CC  | 9.36 | 9.6    | 9.84 | MHz  | under nominal conditions <sup>1)</sup>                                                                                             |

| Long term frequency deviation  | Δf <sub>LT</sub> | CC  | -5.0 | -      | 5.0  | %    | with respect to $f_{\text{NOM}}$ , over<br>lifetime and temperature<br>(-10°C to 125°C), for one<br>given device after<br>trimming |

|                                |                  |     | -6.0 | -      | 0    | %    | with respect to $f_{NOM}$ , over<br>lifetime and temperature<br>(-40°C to<br>-10°C), for one given<br>device after trimming        |

| Short term frequency deviation | $\Delta f_{ST}$  | CC  | -1.0 | -      | 1.0  | %    | within one LIN message<br>(<10 ms 100 ms)                                                                                          |

1) Nominal condition:  $V_{\text{DDC}}$  = 2.5 V,  $T_{\text{A}}$  = + 25°C.

#### **Electrical Parameters**

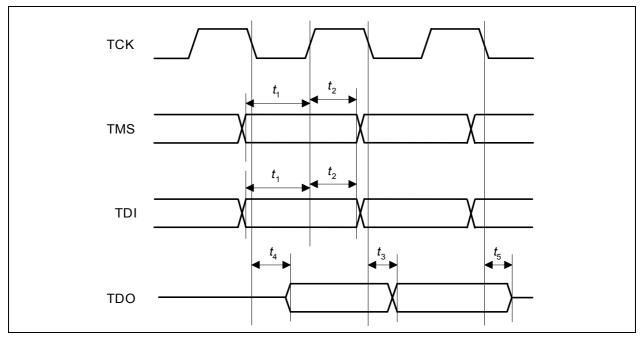

| Table 50JTAG Timing (Operating Conditions apply; CL = 50 pF) (cont'd) |                       |    |     |      |      |                           |  |  |  |

|-----------------------------------------------------------------------|-----------------------|----|-----|------|------|---------------------------|--|--|--|

| Parameter                                                             | Symbol                |    | Lir | nits | Unit | Test                      |  |  |  |

|                                                                       |                       |    | min | max  |      | Conditions                |  |  |  |

| TDO high impedance to valid                                           | <i>t</i> <sub>4</sub> | CC | -   | 27   | ns   | 5V Device <sup>1)</sup>   |  |  |  |

| output from TCK                                                       |                       |    | -   | 36   | ns   | 3.3V Device <sup>1)</sup> |  |  |  |

| TDO valid output to high                                              | <i>t</i> <sub>5</sub> | CC | -   | 22   | ns   | 5V Device <sup>1)</sup>   |  |  |  |

| impedance from TCK                                                    |                       |    | -   | 28   | ns   | 3.3V Device <sup>1)</sup> |  |  |  |

1) Not all parameters are 100% tested, but are verified by design/characterization and test correlation.