Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                          |

| Core Processor             | XC800                                                                             |

| Core Size                  | 8-Bit                                                                             |

| Speed                      | 24MHz                                                                             |

| Connectivity               | CANbus, SSI, UART/USART                                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                             |

| Number of I/O              | 48                                                                                |

| Program Memory Size        | 24KB (24K x 8)                                                                    |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 1.75K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                       |

| Data Converters            | A/D 8x10b                                                                         |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-LQFP                                                                           |

| Supplier Device Package    | PG-TQFP-64                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/sak-xc888cm-6ffa-5v-ac |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

8-Bit

XC886/888CLM

8-Bit Single Chip Microcontroller

Data Sheet V1.2 2009-07

Microcontrollers

## **Table of Contents**

# **Table of Contents**

| 1                      | Summary of Features                                     | . 1 |

|------------------------|---------------------------------------------------------|-----|

| <b>2</b><br>2.1<br>2.2 | General Device Information  Block Diagram  Logic Symbol | . 5 |

| 2.3                    | Pin Configuration                                       |     |

| 2.4                    | Pin Definitions and Functions                           |     |

|                        |                                                         |     |

| 3                      | Functional Description                                  |     |

| 3.1                    | Processor Architecture                                  |     |

| 3.2                    | Memory Organization                                     |     |

| 3.2.1                  | Memory Protection Strategy                              |     |

| 3.2.1.1                | Flash Memory Protection                                 |     |

| 3.2.2                  | Special Function Register                               |     |

| 3.2.2.1                | Address Extension by Mapping                            | 23  |

| 3.2.2.2                | Address Extension by Paging                             |     |

| 3.2.3                  | Bit Protection Scheme                                   | 29  |

| 3.2.3.1                | Password Register                                       | 30  |

| 3.2.4                  | XC886/888 Register Overview                             | 31  |

| 3.2.4.1                | CPU Registers                                           | 31  |

| 3.2.4.2                | MDU Registers                                           | 32  |

| 3.2.4.3                | CORDIC Registers                                        | 33  |

| 3.2.4.4                | System Control Registers                                |     |

| 3.2.4.5                | WDT Registers                                           |     |

| 3.2.4.6                | Port Registers                                          |     |

| 3.2.4.7                | ADC Registers                                           |     |

| 3.2.4.8                | Timer 2 Registers                                       |     |

| 3.2.4.9                | Timer 21 Registers                                      | 43  |

| 3.2.4.10               | CCU6 Registers                                          |     |

| 3.2.4.11               | UART1 Registers                                         |     |

| 3.2.4.12               | SSC Registers                                           |     |

| 3.2.4.13               | MultiCAN Registers                                      | 49  |

| 3.2.4.14               | OCDS Registers                                          |     |

| 3.3                    | Flash Memory                                            | 52  |

| 3.3.1                  | Flash Bank Sectorization                                |     |

| 3.3.2                  | Parallel Read Access of P-Flash                         | 54  |

| 3.3.3                  | Flash Programming Width                                 |     |

| 3.4                    | Interrupt System                                        |     |

| 3.4.1                  | Interrupt Source                                        |     |

| 3.4.2                  | Interrupt Source and Vector                             |     |

| 3.4.3                  | Interrupt Priority                                      |     |

| 3.5                    | Parallel Ports                                          |     |

|                        |                                                         |     |

### 8-Bit Single Chip Microcontroller

XC886/888CLM

## 1 Summary of Features

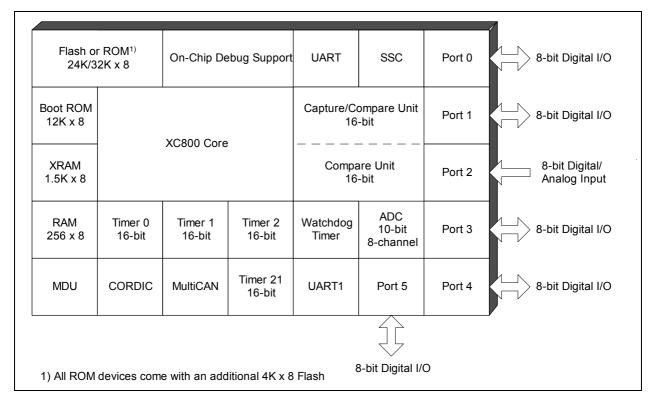

The XC886/888 has the following features:

- · High-performance XC800 Core

- compatible with standard 8051 processor

- two clocks per machine cycle architecture (for memory access without wait state)

- two data pointers

- · On-chip memory

- 12 Kbytes of Boot ROM

- 256 bytes of RAM

- 1.5 Kbytes of XRAM

- 24/32 Kbytes of Flash; or

24/32 Kbytes of ROM, with additional 4 Kbytes of Flash (includes memory protection strategy)

- I/O port supply at 3.3 V or 5.0 V and core logic supply at 2.5 V (generated by embedded voltage regulator)

(more features on next page)

Figure 1 XC886/888 Functional Units

## **General Device Information**

Table 3

Pin Definitions and Functions (cont'd)

| Symbol | Pin Number<br>(TQFP-48/64) | Туре | Reset<br>State | Function                                                  |                                                                                                                                                        |

|--------|----------------------------|------|----------------|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| P2     |                            | I    |                | port. It can b<br>the digital inp                         | B-bit general purpose input-only e used as alternate functions for outs of the JTAG and CCU6. It is the analog inputs for the ADC.                     |

| P2.0   | 14/22                      |      | Hi-Z           | CCPOS0_0<br>EXINT1_0<br>T12HR_2<br>TCK_1<br>CC61_3<br>AN0 | CCU6 Hall Input 0 External Interrupt Input 1 CCU6 Timer 12 Hardware Run Input JTAG Clock Input Input of Capture/Compare channel 1 Analog Input 0       |

| P2.1   | 15/23                      |      | Hi-Z           | CCPOS1_0<br>EXINT2_0<br>T13HR_2<br>TDI_1<br>CC62_3<br>AN1 | CCU6 Hall Input 1 External Interrupt Input 2 CCU6 Timer 13 Hardware Run Input JTAG Serial Data Input Input of Capture/Compare channel 2 Analog Input 1 |

| P2.2   | 16/24                      |      | Hi-Z           | CCPOS2_0<br>CTRAP_1<br>CC60_3<br>AN2                      | CCU6 Hall Input 2<br>CCU6 Trap Input<br>Input of Capture/Compare<br>channel 0<br>Analog Input 2                                                        |

| P2.3   | 19/27                      |      | Hi-Z           | AN3                                                       | Analog Input 3                                                                                                                                         |

| P2.4   | 20/28                      |      | Hi-Z           | AN4                                                       | Analog Input 4                                                                                                                                         |

| P2.5   | 21/29                      |      | Hi-Z           | AN5                                                       | Analog Input 5                                                                                                                                         |

| P2.6   | 22/30                      |      | Hi-Z           | AN6                                                       | Analog Input 6                                                                                                                                         |

| P2.7   | 25/33                      |      | Hi-Z           | AN7                                                       | Analog Input 7                                                                                                                                         |

## **General Device Information**

Table 3

Pin Definitions and Functions (cont'd)

| Symbol | Pin Number<br>(TQFP-48/64) | Туре | Reset<br>State | Function                     |                                                                                                                                           |  |  |  |  |

|--------|----------------------------|------|----------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| P4     |                            | I/O  |                | I/O port. It ca              | Port 4 is an 8-bit bidirectional general purpose I/O port. It can be used as alternate functions for CCU6, Timer 0, Timer 1, Timer 21 and |  |  |  |  |

| P4.0   | 45/59                      |      | Hi-Z           | RXDC0_3<br>CC60_1            | MultiCAN Node 0 Receiver Input<br>Output of Capture/Compare<br>channel 0                                                                  |  |  |  |  |

| P4.1   | 46/60                      |      | Hi-Z           | TXDC0_3<br>COUT60_1          | MultiCAN Node 0 Transmitter Output Output of Capture/Compare channel 0                                                                    |  |  |  |  |

| P4.2   | <b>-</b> /61               |      | PU             | EXINT6_1<br>T21_0            | External Interrupt Input 6 Timer 21 Input                                                                                                 |  |  |  |  |

| P4.3   | 32/40                      |      | Hi-Z           | EXF21_1<br>COUT63_2          | Timer 21 External Flag Output<br>Output of Capture/Compare<br>channel 3                                                                   |  |  |  |  |

| P4.4   | <b>-/45</b>                |      | Hi-Z           | CCPOS0_3<br>T0_0<br>CC61_4   | CCU6 Hall Input 0 Timer 0 Input Output of Capture/Compare channel 1                                                                       |  |  |  |  |

| P4.5   | -/46                       |      | Hi-Z           | CCPOS1_3<br>T1_0<br>COUT61_2 | CCU6 Hall Input 1 Timer 1 Input Output of Capture/Compare channel 1                                                                       |  |  |  |  |

| P4.6   | -/47                       |      | Hi-Z           | CCPOS2_3<br>T2_0<br>CC62_2   | CCU6 Hall Input 2 Timer 2 Input Output of Capture/Compare channel 2                                                                       |  |  |  |  |

| P4.7   | -/48                       |      | Hi-Z           | CTRAP_3<br>COUT62_2          | CCU6 Trap Input<br>Output of Capture/Compare<br>channel 2                                                                                 |  |  |  |  |

Table 8 SCU Register Overview (cont'd)

| Addr            | Register Name                                                        | Bit       | 7            | 6 | 5           | 4               | 3           | 2           | 1             | 0             |

|-----------------|----------------------------------------------------------------------|-----------|--------------|---|-------------|-----------------|-------------|-------------|---------------|---------------|

| BE <sub>H</sub> | COCON Reset: 00 <sub>H</sub><br>Clock Output Control Register        | Bit Field |              | 0 | TLEN        | COUT            |             | COREL       |               |               |

|                 |                                                                      | Туре      |              | r | rw          | rw              | rw          |             |               |               |

| E9 <sub>H</sub> | MISC_CON Reset: 00 <sub>H</sub><br>Miscellaneous Control Register    | Bit Field |              |   |             | 0               |             |             |               | DFLAS<br>HEN  |

|                 |                                                                      | Туре      |              |   |             | r               |             |             |               | rwh           |

| RMAP =          | = 0, PAGE 3                                                          |           |              |   |             |                 |             |             |               |               |

| B3 <sub>H</sub> | XADDRH Reset: F0H                                                    | Bit Field |              |   |             | ADI             | ORH         |             |               |               |

|                 | On-chip XRAM Address Higher Order                                    | Туре      |              |   |             | r               | W           |             |               |               |

| B4 <sub>H</sub> | IRCON3 Reset: 00 <sub>H</sub> Interrupt Request Register 3           | Bit Field |              |   | CANS<br>RC5 | CCU6<br>SR1     | 0           |             | CANS<br>RC4   | CCU6<br>SR0   |

|                 |                                                                      | Туре      | r            |   | rwh         | rwh             | r           |             | rwh           | rwh           |

| в5 <sub>Н</sub> | IRCON4 Reset: 00 <sub>H</sub> Interrupt Request Register 4           | Bit Field |              | 0 | CANS<br>RC7 | CCU6<br>SR3     | -           |             | CANS<br>RC6   | CCU6<br>SR2   |

|                 |                                                                      | Туре      |              | r | rwh         | rwh             |             | r           | rwh           | rwh           |

| В7 <sub>Н</sub> | MODPISEL1 Reset: 00 <sub>H</sub><br>Peripheral Input Select Register | Bit Field | EXINT<br>6IS |   | 0           | UR <sup>2</sup> | RIS         | T21EX<br>IS | JTAGT<br>DIS1 | JTAGT<br>CKS1 |

|                 | 1                                                                    | Туре      | rw           |   | r           | r               | W           | rw          | rw            | rw            |

| BA <sub>H</sub> | MODPISEL2 Reset: 00H                                                 | Bit Field |              | ( | 0           |                 | T21IS       | T2IS        | T1IS          | TOIS          |

|                 | Peripheral Input Select Register 2                                   | Туре      | r            |   |             |                 | rw          | rw          | rw            | rw            |

| ввн             | PMCON2 Reset: 00 <sub>H</sub><br>Power Mode Control Register 2       | Bit Field |              |   |             | UART<br>1_DIS   | T21_D<br>IS |             |               |               |

|                 |                                                                      | Туре      |              |   |             | r               | ı           |             |               | rw            |

| BD <sub>H</sub> | MODSUSP Reset: 01 <sub>H</sub> Module Suspend Control                | Bit Field |              | 0 |             | T21SU<br>SP     | T2SUS<br>P  | T13SU<br>SP | T12SU<br>SP   | WDTS<br>USP   |

|                 | Register                                                             | Туре      |              | r |             | rw              | rw          | rw          | rw            | rw            |

## 3.2.4.5 WDT Registers

The WDT SFRs can be accessed in the mapped memory area (RMAP = 1).

Table 9 WDT Register Overview

| Addr   | Register Name                           | Bit       | 7      | 6 | 5          | 4         | 3    | 2         | 1         | 0         |

|--------|-----------------------------------------|-----------|--------|---|------------|-----------|------|-----------|-----------|-----------|

| RMAP = | : 1                                     |           |        |   |            |           |      |           |           |           |

| ввн    | Watchdog Timer Control                  |           | (      | ) | WINB<br>EN | WDTP<br>R | 0    | WDTE<br>N | WDTR<br>S | WDTI<br>N |

|        | Register                                | Туре      |        | r | rw         | rh        | r    | rw        | rwh       | rw        |

| всн    | WDTREL Reset: 00 <sub>H</sub>           | Bit Field | WDTREL |   |            |           |      |           |           |           |

|        | Watchdog Timer Reload Register Type     |           |        |   |            | r         | w    |           |           |           |

| вDН    | H WDTWINB Reset: 00H                    |           |        |   |            | WDT       | WINB |           |           |           |

|        | Watchdog Window-Boundary Count Register | Туре      |        |   |            | r         | W    |           |           |           |

Table 17 CAN Register Overview (cont'd)

| Addr            | Register Name                | Bit                           |          | 7  | 6   | 5 | 4  | 3  | 2 | 1 | 0 |  |

|-----------------|------------------------------|-------------------------------|----------|----|-----|---|----|----|---|---|---|--|

| DB <sub>H</sub> | DATA0 Reset                  | : <b>00<sub>H</sub></b> Bit F | ield     |    |     |   | С  | :D |   |   |   |  |

|                 | CAN Data Register 0          | Туре                          |          |    | rwh |   |    |    |   |   |   |  |

| DCH             | DATA1 Reset                  | : <b>00<sub>H</sub></b> Bit F | ield     |    |     |   | С  | :D |   |   |   |  |

|                 | CAN Data Register 1          |                               |          |    |     |   | rv | vh |   |   |   |  |

| DDH             | DATA2 Reset                  | : <b>00<sub>H</sub></b> Bit F | ield     | CD |     |   |    |    |   |   |   |  |

|                 | CAN Data Register 2          |                               | ,        |    |     |   | rv | vh |   |   |   |  |

| DE <sub>H</sub> | DATA3 Reset: 00 <sub>H</sub> |                               | ield     |    |     |   | С  | :D |   |   |   |  |

|                 | CAN Data Register 3          | Туре                          | Type rwh |    |     |   |    |    |   |   |   |  |

## 3.2.4.14 OCDS Registers

The OCDS SFRs can be accessed in the mapped memory area (RMAP = 1).

Table 18 OCDS Register Overview

| Addr            | Register Name                                               | Bit       | 7           | 6         | 5          | 4           | 3           | 2         | 1          | 0         |

|-----------------|-------------------------------------------------------------|-----------|-------------|-----------|------------|-------------|-------------|-----------|------------|-----------|

| RMAP =          | : 1                                                         |           |             |           |            |             |             |           |            |           |

| E9 <sub>H</sub> | MMCR2 Reset: 1U <sub>H</sub> Monitor Mode Control 2         | Bit Field | STMO<br>DE  | EXBC      | DSUS<br>P  | MBCO<br>N   | ALTDI       | MMEP      | MMOD<br>E  | JENA      |

|                 | Register                                                    | Туре      | rw          | rw        | rw         | rwh         | rw          | rwh       | rh         | rh        |

| F1 <sub>H</sub> | MMCR Reset: 00 <sub>H</sub> Monitor Mode Control Register   | Bit Field | MEXIT<br>_P | MEXIT     | 0          | MSTE<br>P   | MRAM<br>S_P | MRAM<br>S | TRF        | RRF       |

|                 |                                                             | Туре      | w           | rwh       | r          | rw          | W           | rwh       | rh         | rh        |

| F2 <sub>H</sub> | MMSR Reset: 00 <sub>H</sub> Monitor Mode Status Register    | Bit Field | MBCA<br>M   | MBCIN     | EXBF       | SWBF        | HWB3<br>F   | HWB2<br>F | HWB1<br>F  | HWB0<br>F |

|                 |                                                             | Туре      | rw          | rwh       | rwh        | rwh         | rwh         | rwh       | rwh        | rwh       |

| F3 <sub>H</sub> | MMBPCR Reset: 00 <sub>H</sub> Breakpoints Control Register  | Bit Field | SWBC        | HW        | B3C        | HW          | B2C         | HWB1<br>C | HW         | B0C       |

|                 |                                                             | Туре      | rw          | r         | W          | r           | W           | rw        | n          | W         |

| F4 <sub>H</sub> | MMICR Reset: 00 <sub>H</sub> Monitor Mode Interrupt Control | Bit Field | DVEC<br>T   | DRET<br>R | COMR<br>ST | MSTS<br>EL  | MMUI<br>E_P | MMUI<br>E | RRIE_<br>P | RRIE      |

|                 | Register                                                    | Туре      | rwh         | rwh       | rwh        | rh          | W           | rw        | w          | rw        |

| F5 <sub>H</sub> | MMDR Reset: 00 <sub>H</sub>                                 | Bit Field | MMRR        |           |            |             |             |           |            |           |

|                 | Monitor Mode Data Transfer<br>Register<br>Receive           | Туре      |             |           |            | r           | h           |           |            |           |

| F6 <sub>H</sub> | HWBPSR Reset: 00 <sub>H</sub> Bit Fig.                      |           |             | 0         |            | BPSEL<br>_P |             | BPS       | SEL        |           |

|                 | Register                                                    | Туре      |             | r         |            | w           |             | r         | W          |           |

| F7 <sub>H</sub> | HWBPDR Reset: 00 <sub>H</sub>                               | Bit Field |             |           |            | HWI         | ЗРхх        |           |            |           |

|                 | Hardware Breakpoints Data<br>Register                       | Туре      | rw          |           |            |             |             |           |            |           |

| EBH             | MMWR1 Reset: 00 <sub>H</sub>                                | Bit Field |             |           |            | MM          | WR1         |           |            |           |

|                 | Monitor Work Register 1                                     | Туре      |             |           |            | r           | W           |           |            |           |

### 3.4.3 Interrupt Priority

An interrupt that is currently being serviced can only be interrupted by a higher-priority interrupt, but not by another interrupt of the same or lower priority. Hence, an interrupt of the highest priority cannot be interrupted by any other interrupt request.

If two or more requests of different priority levels are received simultaneously, the request of the highest priority is serviced first. If requests of the same priority are received simultaneously, then an internal polling sequence determines which request is serviced first. Thus, within each priority level, there is a second priority structure determined by the polling sequence shown in **Table 21**.

Table 21 Priority Structure within Interrupt Level

| Level     |

|-----------|

| (highest) |

| 1         |

| 2         |

| 3         |

| 4         |

| 5         |

| 6         |

| 7         |

| 8         |

| 9         |

| 10        |

| 11        |

| 12        |

| 13        |

| 14        |

|           |

#### 3.7 Reset Control

The XC886/888 has five types of reset: power-on reset, hardware reset, watchdog timer reset, power-down wake-up reset, and brownout reset.

When the XC886/888 is first powered up, the status of certain pins (see **Table 23**) must be defined to ensure proper start operation of the device. At the end of a reset sequence, the sampled values are latched to select the desired boot option, which cannot be modified until the next power-on reset or hardware reset. This guarantees stable conditions during the normal operation of the device.

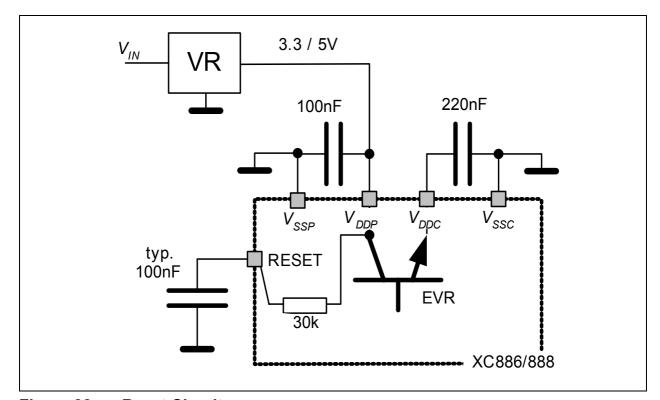

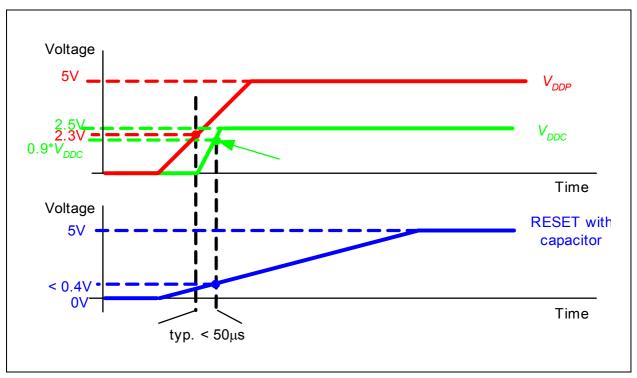

In order to power up the system properly, the external reset pin RESET must be asserted until  $V_{\rm DDC}$  reaches 0.9\* $V_{\rm DDC}$ . The delay of external reset can be realized by an external capacitor at RESET pin. This capacitor value must be selected so that  $V_{\rm RESET}$  reaches 0.4 V, but not before  $V_{\rm DDC}$  reaches 0.9\*  $V_{\rm DDC}$

A typical application example is shown in Figure 22. The  $V_{\rm DDP}$  capacitor value is 100 nF while the  $V_{\rm DDC}$  capacitor value is 220 nF. The capacitor connected to RESET pin is 100 nF.

Typically, the time taken for  $V_{\rm DDC}$  to reach  $0.9^*V_{\rm DDC}$  is less than 50  $\mu s$  once  $V_{\rm DDP}$  reaches 2.3V. Hence, based on the condition that 10% to 90%  $V_{\rm DDP}$  (slew rate) is less than 500  $\mu s$ , the RESET pin should be held low for 500  $\mu s$  typically. See Figure 23.

Figure 22 Reset Circuitry

Figure 23  $V_{\rm DDP}$ ,  $V_{\rm DDC}$  and  $V_{\rm RESET}$  during Power-on Reset

The second type of reset in XC886/888 is the hardware reset. This reset function can be used during normal operation or when the chip is in power-down mode. A reset input pin RESET is provided for the hardware reset.

The Watchdog Timer (WDT) module is also capable of resetting the device if it detects a malfunction in the system.

Another type of reset that needs to be detected is a reset while the device is in power-down mode (wake-up reset). While the contents of the static RAM are undefined after a power-on reset, they are well defined after a wake-up reset from power-down mode.

#### 3.7.1 Module Reset Behavior

Table 22 lists the functions of the XC886/888 and the various reset types that affect these functions. The symbol "■" signifies that the particular function is reset to its default state.

Table 22 Effect of Reset on Device Functions

| Module/<br>Function   | Wake-Up<br>Reset                     | Watchdog<br>Reset         | Hardware<br>Reset         | Power-On<br>Reset         | Brownout<br>Reset         |

|-----------------------|--------------------------------------|---------------------------|---------------------------|---------------------------|---------------------------|

| CPU Core              |                                      |                           |                           |                           |                           |

| Peripherals           |                                      |                           |                           |                           |                           |

| On-Chip<br>Static RAM | Not affected,<br>Reliable            | Not affected,<br>Reliable | Not affected,<br>Reliable | Affected, un-<br>reliable | Affected, un-<br>reliable |

| Oscillator,<br>PLL    |                                      | Not affected              |                           |                           |                           |

| Port Pins             |                                      |                           |                           |                           |                           |

| EVR                   | The voltage regulator is switched on | Not affected              |                           |                           |                           |

| FLASH                 |                                      |                           |                           |                           |                           |

| NMI                   | Disabled                             | Disabled                  |                           |                           |                           |

## 3.7.2 Booting Scheme

When the XC886/888 is reset, it must identify the type of configuration with which to start the different modes once the reset sequence is complete. Thus, boot configuration information that is required for activation of special modes and conditions needs to be applied by the external world through input pins. After power-on reset or hardware reset, the pins MBC, TMS and P0.0 collectively select the different boot options. **Table 23** shows the available boot options in the XC886/888.

Table 23 XC886/888 Boot Selection

| MBC | TMS | P0.0 | Type of Mode                                                           | PC Start Value    |

|-----|-----|------|------------------------------------------------------------------------|-------------------|

| 1   | 0   | X    | User Mode <sup>1)</sup> ; on-chip OSC/PLL non-bypassed                 | 0000 <sub>H</sub> |

| 0   | 0   | X    | BSL Mode; on-chip OSC/PLL non-bypassed <sup>2)</sup>                   | 0000 <sub>H</sub> |

| 0   | 1   | 0    | OCDS Mode; on-chip OSC/PLL non-bypassed                                | 0000 <sub>H</sub> |

| 1   | 1   | 0    | User (JTAG) Mode <sup>3)</sup> ; on-chip OSC/PLL non-bypassed (normal) | 0000 <sub>H</sub> |

- 1) BSL mode is automatically entered if no valid password is installed and data at memory address 0000H equals zero.

- 2) OSC is bypassed in MultiCAN BSL mode

- 3) Normal user mode with standard JTAG (TCK,TDI,TDO) pins for hot-attach purpose.

Note: The boot options are valid only with the default set of UART and JTAG pins.

#### 3.8 Clock Generation Unit

The Clock Generation Unit (CGU) allows great flexibility in the clock generation for the XC886/888. The power consumption is indirectly proportional to the frequency, whereas the performance of the microcontroller is directly proportional to the frequency. During user program execution, the frequency can be programmed for an optimal ratio between performance and power consumption. Therefore the power consumption can be adapted to the actual application state.

#### **Features**

- Phase-Locked Loop (PLL) for multiplying clock source by different factors

- PLL Base Mode

- Prescaler Mode

- PLL Mode

- Power-down mode support

The CGU consists of an oscillator circuit and a PLL. In the XC886/888, the oscillator can be from either of these two sources: the on-chip oscillator (9.6 MHz) or the external oscillator (4 MHz to 12 MHz). The term "oscillator" is used to refer to both on-chip oscillator and external oscillator, unless otherwise stated. After the reset, the on-chip oscillator will be used by default. The external oscillator can be selected via software. In addition, the PLL provides a fail-safe logic to perform oscillator run and loss-of-lock detection. This allows emergency routines to be executed for system recovery or to perform system shut down.

Data Sheet 72 V1.2, 2009-07

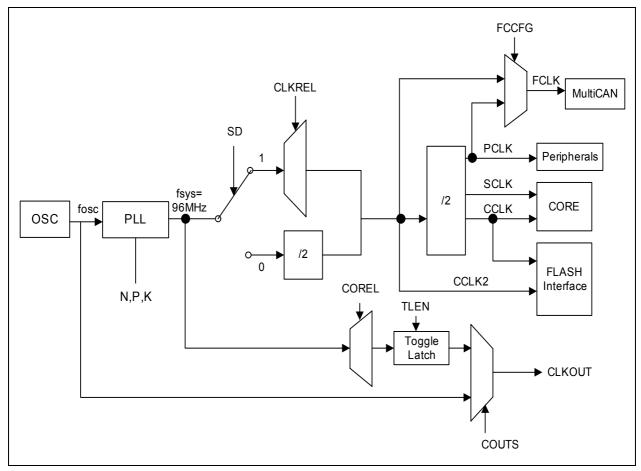

### 3.8.2 Clock Management

The CGU generates all clock signals required within the microcontroller from a single clock,  $f_{\rm sys}$ . During normal system operation, the typical frequencies of the different modules are as follow:

- CPU clock: CCLK, SCLK = 24 MHz

- Fast clock (used by MultiCAN): FCLK = 24 or 48 MHz

- Peripheral clock: PCLK = 24 MHz

- Flash Interface clock: CCLK2 = 48 MHz and CCLK = 24 MHz

In addition, different clock frequencies can be output to pin CLKOUT (P0.0 or P0.7). The clock output frequency, which is derived from the clock output divider (bit COREL), can further be divided by 2 using toggle latch (bit TLEN is set to 1). The resulting output frequency has a 50% duty cycle. **Figure 26** shows the clock distribution of the XC886/888.

Figure 26 Clock Generation from  $f_{\text{sys}}$

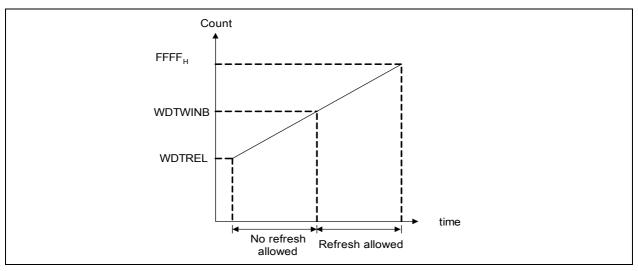

## 3.10 Watchdog Timer

The Watchdog Timer (WDT) provides a highly reliable and secure way to detect and recover from software or hardware failures. The WDT is reset at a regular interval that is predefined by the user. The CPU must service the WDT within this interval to prevent the WDT from causing an XC886/888 system reset. Hence, routine service of the WDT confirms that the system is functioning properly. This ensures that an accidental malfunction of the XC886/888 will be aborted in a user-specified time period.

In debug mode, the WDT is default suspended and stops counting. Therefore, there is no need to refresh the WDT during debugging.

#### **Features**

- 16-bit Watchdog Timer

- Programmable reload value for upper 8 bits of timer

- Programmable window boundary

- Selectable input frequency of  $f_{PCLK}/2$  or  $f_{PCLK}/128$

- Time-out detection with NMI generation and reset prewarning activation (after which a system reset will be performed)

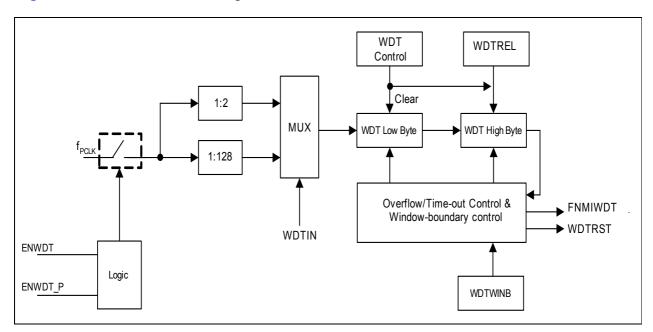

The WDT is a 16-bit timer incremented by a count rate of  $f_{\rm PCLK}/2$  or  $f_{\rm PCLK}/128$ . This 16-bit timer is realized as two concatenated 8-bit timers. The upper 8 bits of the WDT can be preset to a user-programmable value via a watchdog service access in order to modify the watchdog expire time period. The lower 8 bits are reset on each service access. Figure 28 shows the block diagram of the WDT unit.

Figure 28 WDT Block Diagram

Figure 29 WDT Timing Diagram

**Table 27** lists the possible watchdog time ranges that can be achieved using a certain module clock. Some numbers are rounded to 3 significant digits.

Table 27 Watchdog Time Ranges

| Reload value                     | Prescaler for $f_{\sf PCLK}$ |                 |  |  |  |  |  |  |

|----------------------------------|------------------------------|-----------------|--|--|--|--|--|--|

| In WDTREL                        | 2 (WDTIN = 0)                | 128 (WDTIN = 1) |  |  |  |  |  |  |

|                                  | 24 MHz                       | 24 MHz          |  |  |  |  |  |  |

| FF <sub>H</sub>                  | 21.3 μs                      | 1.37 ms         |  |  |  |  |  |  |

| $\frac{FF_{H}}{7F_{H}}$ $00_{H}$ | 2.75 ms                      | 176 ms          |  |  |  |  |  |  |

| 00 <sub>H</sub>                  | 5.46 ms                      | 350 ms          |  |  |  |  |  |  |

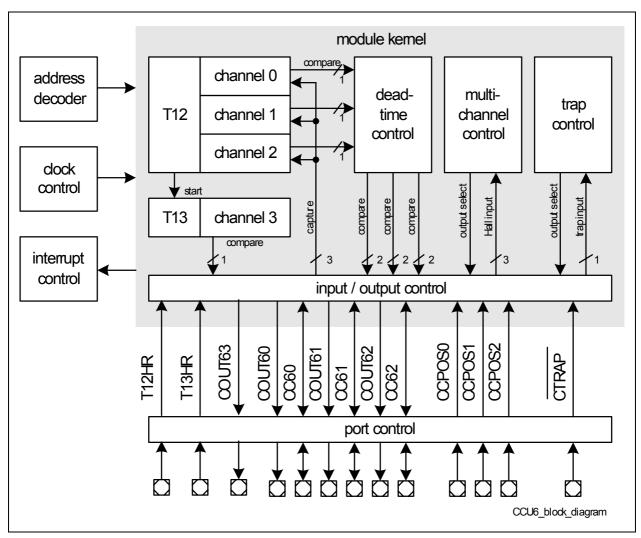

Figure 33 CCU6 Block Diagram

Data Sheet 96 V1.2, 2009-07

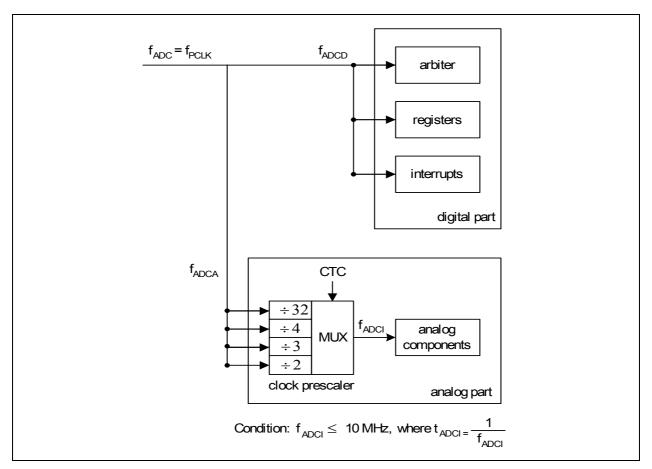

GLOBCTR. A prescaling ratio of 32 can be selected when the maximum performance of the ADC is not required.

Figure 35 ADC Clocking Scheme

For module clock  $f_{\rm ADC}$  = 24 MHz, the analog clock  $f_{\rm ADCI}$  frequency can be selected as shown in **Table 34**.

Table 34  $f_{ADCI}$  Frequency Selection

| Module Clock $f_{ADC}$ | СТС                       | Prescaling Ratio | Analog Clock $f_{ADCI}$ |

|------------------------|---------------------------|------------------|-------------------------|

| 24 MHz                 | 00 <sub>B</sub>           | ÷ 2              | 12 MHz (N.A)            |

|                        | 01 <sub>B</sub>           | ÷ 3              | 8 MHz                   |

|                        | 10 <sub>B</sub>           | ÷ 4              | 6 MHz                   |

|                        | 11 <sub>B</sub> (default) | ÷ 32             | 750 kHz                 |

As  $f_{\rm ADCI}$  cannot exceed 10 MHz, bit field CTC should not be set to  $00_{\rm B}$  when  $f_{\rm ADC}$  is 24 MHz. During slow-down mode where  $f_{\rm ADC}$  may be reduced to 12 MHz, 6 MHz etc., CTC can be set to  $00_{\rm B}$  as long as the divided analog clock  $f_{\rm ADCI}$  does not exceed 10 MHz.

Data Sheet 100 V1.2, 2009-07

#### **Electrical Parameters**

### 4 Electrical Parameters

**Chapter 4** provides the characteristics of the electrical parameters which are implementation-specific for the XC886/888.

#### 4.1 General Parameters

The general parameters are described here to aid the users in interpreting the parameters mainly in **Section 4.2** and **Section 4.3**.

### 4.1.1 Parameter Interpretation

The parameters listed in this section represent partly the characteristics of the XC886/888 and partly its requirements on the system. To aid interpreting the parameters easily when evaluating them for a design, they are indicated by the abbreviations in the "Symbol" column:

### · cc

These parameters indicate Controller Characteristics, which are distinctive features of the XC886/888 and must be regarded for a system design.

#### SR

These parameters indicate **S**ystem **R**equirements, which must be provided by the microcontroller system in which the XC886/888 is designed in.

Data Sheet 108 V1.2, 2009-07

## **Electrical Parameters**

Table 38 Input/Output Characteristics (Operating Conditions apply) (cont'd)

| Parameter                                                                  | Symbol            |    | Limit Values                 |                               | Unit | Test Conditions                                          |  |

|----------------------------------------------------------------------------|-------------------|----|------------------------------|-------------------------------|------|----------------------------------------------------------|--|

|                                                                            |                   |    | min.                         | max.                          |      |                                                          |  |

| Input high voltage on RESET pin                                            | $V_{IHR}$         | SR | $0.7 	imes V_{ m DDP}$       | _                             | V    | CMOS Mode                                                |  |

| Input high voltage on TMS pin                                              | $V_{IHT}$         | SR | $0.75 \times V_{\text{DDP}}$ | _                             | V    | CMOS Mode                                                |  |

| Input Hysteresis on port pins                                              | HYSP              | CC | $V_{\mathrm{DDP}}$           | _                             | V    | CMOS Mode <sup>1)</sup>                                  |  |

| Input Hysteresis on<br>XTAL1                                               | HYSX              | CC | $V_{ m DDC}$                 | _                             | V    | 1)                                                       |  |

| Input low voltage at XTAL1                                                 | $V_{ILX}$         | SR | V <sub>SS</sub> - 0.5        | $V_{ m DDC}$                  | V    |                                                          |  |

| Input high voltage at XTAL1                                                | $V_{IHX}$         | SR | $V_{ m DDC}$                 | <i>V</i> <sub>DDC</sub> + 0.5 | V    |                                                          |  |

| Pull-up current                                                            | $I_{PU}$          | SR | _                            | -10                           | μΑ   | $V_{IHP,min}$                                            |  |

|                                                                            |                   |    | -150                         | _                             | μΑ   | $V_{ILP,max}$                                            |  |

| Pull-down current                                                          | $I_{PD}$          | SR | _                            | 10                            | μΑ   | $V_{ILP,max}$                                            |  |

|                                                                            |                   |    | 150                          | _                             | μΑ   | $V_{IHP,min}$                                            |  |

| Input leakage current                                                      | $I_{OZ1}$         | CC | -1                           | 1                             | μΑ   | $0 < V_{IN} < V_{DDP},$<br>$T_{A} \le 125^{\circ}C^{2)}$ |  |

| Input current at XTAL1                                                     | $I_{ILX}$         | CC | -10                          | 10                            | μΑ   |                                                          |  |

| Overload current on any pin                                                | $I_{OV}$          | SR | -5                           | 5                             | mA   |                                                          |  |

| Absolute sum of overload currents                                          | $\Sigma  I_{OV} $ | SR | _                            | 25                            | mA   | 3)                                                       |  |

|                                                                            | $V_{PO}$          | SR | _                            | 0.3                           | V    | 4)                                                       |  |

| Maximum current per pin (excluding $V_{\rm DDP}$ and $V_{\rm SS}$ )        | $I_{M}SR$         | SR | -                            | 15                            | mA   |                                                          |  |

| Maximum current for all pins (excluding $V_{\rm DDP}$ and $V_{\rm SS}$ )   | $\Sigma  I_{M} $  | SR | _                            | 90                            | mA   |                                                          |  |

| $\begin{array}{c} {\rm Maximum~current~into} \\ {V_{\rm DDP}} \end{array}$ | $I_{MVDDP}$       | SR | _                            | 120                           | mA   | 3)                                                       |  |

#### **Electrical Parameters**

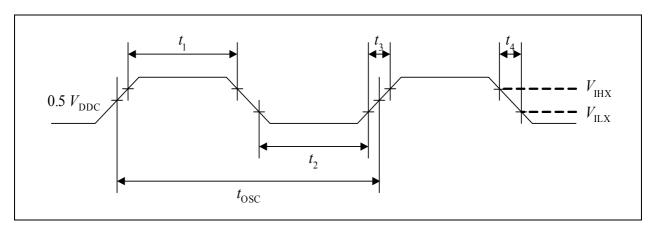

#### 4.3.5 External Clock Drive XTAL1

**Table 48** shows the parameters that define the external clock supply for XC886/888. These timing parameters are based on the direct XTAL1 drive of clock input signals. They are not applicable if an external crystal or ceramic resonator is considered.

Table 48 External Clock Drive Characteristics (Operating Conditions apply)

| Parameter         | Symbol        |    | Limit Values |      | Unit | Test Conditions |

|-------------------|---------------|----|--------------|------|------|-----------------|

|                   |               |    | Min.         | Max. |      |                 |

| Oscillator period | $t_{\rm osc}$ | SR | 83.3         | 250  | ns   | 1)2)            |

| High time         | $t_1$         | SR | 25           | -    | ns   | 2)3)            |

| Low time          | $t_2$         | SR | 25           | -    | ns   | 2)3)            |

| Rise time         | $t_3$         | SR | -            | 20   | ns   | 2)3)            |

| Fall time         | $t_4$         | SR | -            | 20   | ns   | 2)3)            |

- 1) The clock input signals with 45-55% duty cycle are used.

- 2) Not all parameters are 100% tested, but are verified by design/characterization and test correlation.

- 3) The clock input signal must reach the defined levels  $V_{\rm ILX}$  and  $V_{\rm IHX}$ .

Figure 45 External Clock Drive XTAL1

Data Sheet 129 V1.2, 2009-07