Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                          |

| Core Processor             | XC800                                                                             |

| Core Size                  | 8-Bit                                                                             |

| Speed                      | 24MHz                                                                             |

| Connectivity               | CANbus, SSI, UART/USART                                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                             |

| Number of I/O              | 48                                                                                |

| Program Memory Size        | 32KB (32K x 8)                                                                    |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 1.75K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                       |

| Data Converters            | A/D 8x10b                                                                         |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-LQFP                                                                           |

| Supplier Device Package    | PG-TQFP-64                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/sak-xc888cm-8ffi-5v-ac |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 8-Bit

# XC886/888CLM

8-Bit Single Chip Microcontroller

Data Sheet V1.2 2009-07

# Microcontrollers

#### Summary of Features

#### XC886/888 Variant Devices

The XC886/888 product family features devices with different configurations, program memory sizes, package options, power supply voltage, temperature and quality profiles (Automotive or Industrial), to offer cost-effective solutions for different application requirements.

The list of XC886/888 device configurations are summarized in **Table 1**. For each configuration, 2 types of packages are available:

- PG-TQFP-48, which is denoted by XC886 and;

- PG-TQFP-64, which is denoted by XC888.

| Device Name  | CAN<br>Module | LIN BSL<br>Support | MDU<br>Module |

|--------------|---------------|--------------------|---------------|

| XC886/888    | No            | No                 | No            |

| XC886/888C   | Yes           | No                 | No            |

| XC886/888CM  | Yes           | No                 | Yes           |

| XC886/888LM  | No            | Yes                | Yes           |

| XC886/888CLM | Yes           | Yes                | Yes           |

#### Table 1Device Configuration

Note: For variants with LIN BSL support, only LIN BSL is available regardless of the availability of the CAN module.

From these 10 different combinations of configuration and package type, each are further made available in many sales types, which are grouped according to device type, program memory sizes, power supply voltage, temperature and quality profile (Automotive or Industrial), as shown in Table 2.

#### Table 2Device Profile

| Sales Type              | Device<br>Type | Program<br>Memory<br>(Kbytes) | Power<br>Supply<br>(V) | Temp-<br>erature<br>(°C) | Quality<br>Profile |

|-------------------------|----------------|-------------------------------|------------------------|--------------------------|--------------------|

| SAK-XC886*/888*-8FFA 5V | Flash          | 32                            | 5.0                    | -40 to 125               | Automotive         |

| SAK-XC886*/888*-6FFA 5V | Flash          | 24                            | 5.0                    | -40 to 125               | Automotive         |

| SAF-XC886*/888*-8FFA 5V | Flash          | 32                            | 5.0                    | -40 to 85                | Automotive         |

| SAF-XC886*/888*-6FFA 5V | Flash          | 24                            | 5.0                    | -40 to 85                | Automotive         |

| SAF-XC886*/888*-8FFI 5V | Flash          | 32                            | 5.0                    | -40 to 85                | Industrial         |

| SAF-XC886*/888*-6FFI 5V | Flash          | 24                            | 5.0                    | -40 to 85                | Industrial         |

#### **General Device Information**

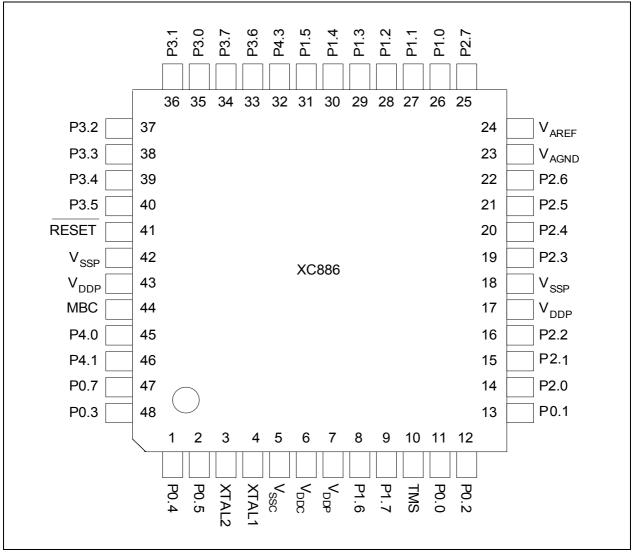

### 2.3 Pin Configuration

The pin configuration of the XC886, which is based on the PG-TQFP-48 package, is shown in **Figure 4**, while that of the XC888, which is based on the PG-TQFP-64 package, is shown in **Figure 5**.

Figure 4 XC886 Pin Configuration, PG-TQFP-48 Package (top view)

#### **General Device Information**

| Table 0 | T III Belli                |      |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | u)                                                            |  |  |

|---------|----------------------------|------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|--|--|

| Symbol  | Pin Number<br>(TQFP-48/64) | Туре | Reset<br>State | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                               |  |  |

| P0.4    | 1/64                       |      | Hi-Z           | MTSR_1                                                                                                                                                                                                                                                                                                                                                                                                                                                              | SSC Master Transmit Output/<br>Slave Receive Input            |  |  |

|         |                            |      |                | CC62_1                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Input/Output of<br>Capture/Compare channel 2                  |  |  |

|         |                            |      |                | MTSR_1       SSC Master Transmit Output<br>Slave Receive Input         CC62_1       Input/Output of<br>Capture/Compare channel 2         TXD1_0       UART1 Transmit Data<br>Output/Clock Output         MRST_1       SSC Master Receive Input/S<br>Transmit Output         EXINT0_0       External Interrupt Input 0         T2EX1_1       Timer 21 External Trigger In<br>RXD1_0         UART1 Receive Data Input         OUT62_1       Output of Capture/Compare |                                                               |  |  |

| P0.5    | 2/1                        |      | Hi-Z           | –<br>EXINT0_0<br>T2EX1_1<br>RXD1_0                                                                                                                                                                                                                                                                                                                                                                                                                                  | External Interrupt Input 0<br>Timer 21 External Trigger Input |  |  |

| P0.6    | -/2                        |      | PU             | GPIO                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                               |  |  |

| P0.7    | 47/62                      |      | PU             | CLKOUT_1                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Clock Output                                                  |  |  |

#### Pin Definitions and Functions (cont'd) Table 3

#### XC886/888CLM

#### **General Device Information**

#### Reset **Function** Symbol **Pin Number** Type (TQFP-48/64) State **P4** I/O Port 4 Port 4 is an 8-bit bidirectional general purpose I/O port. It can be used as alternate functions for CCU6, Timer 0, Timer 1, Timer 21 and MultiCAN. RXDC0 3 MultiCAN Node 0 Receiver Input P4.0 Hi-Z 45/59 CC60 1 Output of Capture/Compare channel 0 P4.1 46/60 Hi-Z TXDC0 3 MultiCAN Node 0 Transmitter Output Output of Capture/Compare COUT60 1 channel 0 P4.2 -/61 PU EXINT6 1 **External Interrupt Input 6** T21 0 Timer 21 Input P4.3 32/40 Hi-Z EXF21 1 Timer 21 External Flag Output COUT63 2 **Output of Capture/Compare** channel 3 CCPOS0\_3 -/45 Hi-Z CCU6 Hall Input 0 P4.4 Timer 0 Input T0 0 CC61 4 **Output of Capture/Compare** channel 1 CCPOS1 3 CCU6 Hall Input 1 P4.5 -/46 Hi-Z T1 0 Timer 1 Input COUT61 2 Output of Capture/Compare channel 1 P4.6 -/47 Hi-Z CCPOS2 3 CCU6 Hall Input 2 T2 0 Timer 2 Input CC62 2 **Output of Capture/Compare** channel 2 CTRAP 3 CCU6 Trap Input P4.7 -/48 Hi-Z COUT62 2 Output of Capture/Compare channel 2

#### Table 3Pin Definitions and Functions (cont'd)

The page register has the following definition:

#### MOD\_PAGE Page Register for module MOD

Reset Value: 00<sub>H</sub>

| 7 | 6 | 5  | 4  | 3 | 2 | 1    | 0 |

|---|---|----|----|---|---|------|---|

| 0 | Ρ | ST | NR | 0 |   | PAGE |   |

| v | V | V  | V  | r |   | rw   | I |

| Field | Bits  | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------|-------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PAGE  | [2:0] | rw   | <b>Page Bits</b><br>When written, the value indicates the new page.<br>When read, the value indicates the currently active<br>page.                                                                                                                                                                                                                                                                                                                                        |

| STNR  | [5:4] | W    | Storage NumberThis number indicates which storage bit field is the<br>target of the operation defined by bit field OP.If $OP = 10_B$ ,<br>the contents of PAGE are saved in STx before being<br>overwritten with the new value.If $OP = 11_B$ ,<br>the contents of PAGE are overwritten by the<br>contents of STx. The value written to the bit positions<br>of PAGE is ignored.00ST0 is selected.<br>0101ST1 is selected.<br>1010ST2 is selected.<br>1111ST3 is selected. |

| Field | Bits  | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------|-------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OP    | [7:6] | w    | <ul> <li>Operation         <ul> <li>Manual page mode. The value of STNR is ignored and PAGE is directly written.</li> <li>New page programming with automatic page saving. The value written to the bit positions of PAGE is stored. In parallel, the previous contents of PAGE are saved in the storage bit field STx indicated by STNR.</li> </ul> </li> <li>Automatic restore page action. The value written to the bit positions of PAGE is ignored and instead, PAGE is overwritten by the contents of the storage bit field STx indicated by STNR.</li> </ul> |

| 0     | 3     | r    | <b>Reserved</b><br>Returns 0 if read; should be written with 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

#### 3.2.3 Bit Protection Scheme

The bit protection scheme prevents direct software writing of selected bits (i.e., protected bits) using the PASSWD register. When the bit field MODE is  $11_B$ , writing  $10011_B$  to the bit field PASS opens access to writing of all protected bits, and writing  $10101_B$  to the bit field PASS closes access to writing of all protected bits. In both cases, the value of the bit field MODE is not changed even if PASSWD register is written with  $98_H$  or  $A8_H$ . It can only be changed when bit field PASS is written with  $11000_B$ , for example, writing D0<sub>H</sub> to PASSWD register disables the bit protection scheme.

Note that access is opened for maximum 32 CCLKs if the "close access" password is not written. If "open access" password is written again before the end of 32 CCLK cycles, there will be a recount of 32 CCLK cycles. The protected bits include the N- and K-Divider bits, NDIV and KDIV; the Watchdog Timer enable bit, WDTEN; and the power-down and slow-down enable bits, PD and SD.

#### Table 14CCU6 Register Overview (cont'd)

| Addr            | Register Name                                                       | Bit       | 7     | 6            | 5            | 4          | 3            | 2          | 1            | 0          |

|-----------------|---------------------------------------------------------------------|-----------|-------|--------------|--------------|------------|--------------|------------|--------------|------------|

| Fe <sub>H</sub> | CCU6_CMPSTATL Reset: 00 <sub>H</sub><br>Compare State Register Low  | Bit Field | 0     | CC63<br>ST   | CC<br>POS2   | CC<br>POS1 | CC<br>POS0   | CC62<br>ST | CC61<br>ST   | CC60<br>ST |

|                 |                                                                     | Туре      | r     | rh           | rh           | rh         | rh           | rh         | rh           | rh         |

| FF <sub>H</sub> | CCU6_CMPSTATH Reset: 00 <sub>H</sub><br>Compare State Register High | Bit Field | T13IM | COUT<br>63PS | COUT<br>62PS | CC62<br>PS | COUT<br>61PS | CC61<br>PS | COUT<br>60PS | CC60<br>PS |

|                 |                                                                     | Туре      | rwh   | rwh          | rwh          | rwh        | rwh          | rwh        | rwh          | rwh        |

### 3.2.4.11 UART1 Registers

The UART1 SFRs can be accessed in the mapped memory area (RMAP = 1).

#### Table 15 UART1 Register Overview

| Addr            | Register Name                          | Bit       | 7        | 6   | 5   | 4   | 3    | 2     | 1   | 0    |

|-----------------|----------------------------------------|-----------|----------|-----|-----|-----|------|-------|-----|------|

| RMAP =          | = 1                                    | 1         |          |     |     |     |      |       |     | 1    |

| C8 <sub>H</sub> | SCON Reset: 00 <sub>H</sub>            | Bit Field | SM0      | SM1 | SM2 | REN | TB8  | RB8   | TI  | RI   |

|                 | Serial Channel Control Register        | Туре      | rw       | rw  | rw  | rw  | rw   | rwh   | rwh | rwh  |

| C9 <sub>H</sub> | SBUF Reset: 00 <sub>H</sub>            | Bit Field |          |     |     | V   | AL   |       |     |      |

|                 | Serial Data Buffer Register            | Туре      |          |     |     | rv  | vh   |       |     |      |

| са <sub>Н</sub> | BCON Reset: 00 <sub>H</sub>            | Bit Field |          | (   | )   |     |      | BRPRE |     | R    |

|                 | Baud Rate Control Register             | Туре      |          |     | r   |     | ſW   |       |     | rw   |

| св <sub>Н</sub> | BG Reset: 00 <sub>H</sub>              | Bit Field | BR_VALUE |     |     |     |      |       |     |      |

|                 | Baud Rate Timer/Reload<br>Register     | Туре      | rwh      |     |     |     |      |       |     |      |

| сс <sub>Н</sub> | FDCON Reset: 00 <sub>H</sub>           | Bit Field |          |     | 0   |     |      | NDOV  | FDM | FDEN |

|                 | Fractional Divider Control<br>Register | Туре      |          | r   |     |     |      |       | rw  | rw   |

| CD <sub>H</sub> | FDSTEP Reset: 00 <sub>H</sub>          | Bit Field |          |     |     | ST  | ΈP   |       |     |      |

|                 | Fractional Divider Reload<br>Register  | Туре      | rw       |     |     |     |      |       |     |      |

| Ceh             | FDRES Reset: 00 <sub>H</sub>           | Bit Field |          |     |     | RES | SULT |       |     |      |

|                 | Fractional Divider Result<br>Register  | Туре      | rh       |     |     |     |      |       |     |      |

# 3.2.4.12 SSC Registers

The SSC SFRs can be accessed in the standard memory area (RMAP = 0).

| Addr            | Register Name                                                                  | Bit       | 7  | 6  | 5  | 4    | 3    | 2   | 1   | 0   |

|-----------------|--------------------------------------------------------------------------------|-----------|----|----|----|------|------|-----|-----|-----|

| RMAP =          | = 0                                                                            |           |    |    |    |      |      |     |     |     |

| A9 <sub>H</sub> | SSC_PISEL Reset: 00 <sub>H</sub>                                               | Bit Field |    |    | 0  |      |      | CIS | SIS | MIS |

|                 | Port Input Select Register                                                     | Туре      |    |    | r  |      |      | rw  | rw  | rw  |

| AA <sub>H</sub> | SSC_CONL Reset: 00 <sub>H</sub>                                                | Bit Field | LB | PO | PH | HB   |      | В   | М   |     |

|                 | Control Register Low<br>Programming Mode                                       | Туре      | rw | rw | rw | rw   | rw   |     |     |     |

| AA <sub>H</sub> | SSC_CONL Reset: 00 <sub>H</sub>                                                | Bit Field |    | (  | )  |      |      | В   | С   |     |

|                 | Control Register Low<br>Operating Mode                                         | Туре      |    | l  | r  |      |      | r   | h   |     |

| ав <sub>Н</sub> | H SSC_CONH Reset: 00 <sub>H</sub><br>Control Register High<br>Programming Mode | Bit Field | EN | MS | 0  | AREN | BEN  | PEN | REN | TEN |

|                 |                                                                                | Туре      | rw | rw | r  | rw   | rw   | rw  | rw  | rw  |

| ав <sub>Н</sub> | SSC_CONH Reset: 00 <sub>H</sub>                                                | Bit Field | EN | MS | 0  | BSY  | BE   | PE  | RE  | TE  |

|                 | Control Register High<br>Operating Mode                                        | Туре      | rw | rw | r  | rh   | rwh  | rwh | rwh | rwh |

| ac <sub>h</sub> | SSC_TBL Reset: 00 <sub>H</sub>                                                 | Bit Field |    |    |    | TB_V | ALUE |     |     |     |

|                 | Transmitter Buffer Register Low                                                | Туре      | rw |    |    |      |      |     |     |     |

| ad <sub>H</sub> | SSC_RBL Reset: 00 <sub>H</sub>                                                 | Bit Field |    |    |    | RB_V | ALUE |     |     |     |

|                 | Receiver Buffer Register Low                                                   | Туре      |    |    |    | rl   | า    |     |     |     |

| ае <sub>Н</sub> | SSC_BRL Reset: 00 <sub>H</sub>                                                 | Bit Field |    |    |    | BR_V | ALUE |     |     |     |

|                 | Baud Rate Timer Reload<br>Register Low                                         | Туре      | rw |    |    |      |      |     |     |     |

| af <sub>h</sub> | SSC_BRH Reset: 00 <sub>H</sub>                                                 | Bit Field |    |    |    | BR_V | ALUE |     |     |     |

|                 | Baud Rate Timer Reload<br>Register High                                        | Туре      |    |    |    | n    | N    |     |     |     |

#### Table 16 SSC Register Overview

### 3.2.4.13 MultiCAN Registers

The MultiCAN SFRs can be accessed in the standard memory area (RMAP = 0).

| Addr            | Register Name                        | Bit       | 7   | 6   | 5   | 4   | 3    | 2    | 1    | 0    |

|-----------------|--------------------------------------|-----------|-----|-----|-----|-----|------|------|------|------|

| RMAP =          | : 0                                  |           |     |     |     |     |      |      |      |      |

| D8 <sub>H</sub> | ADCON Reset: 00 <sub>H</sub>         | Bit Field | V3  | V2  | V1  | V0  | AU   | AD   | BSY  | RWEN |

|                 | CAN Address/Data Control<br>Register | Туре      | rw  | rw  | rw  | rw  | rw   |      | rh   | rw   |

| D9 <sub>H</sub> | ADL Reset: 00 <sub>H</sub>           | Bit Field | CA9 | CA8 | CA7 | CA6 | CA5  | CA4  | CA3  | CA2  |

|                 | CAN Address Register Low             | Туре      | rwh | rwh | rwh | rwh | rwh  | rwh  | rwh  | rwh  |

| da <sub>h</sub> | ADH Reset: 00 <sub>H</sub>           | Bit Field |     | (   | )   |     | CA13 | CA12 | CA11 | CA10 |

|                 | CAN Address Register High            | Туре      |     |     | ſ   |     | rwh  | rwh  | rwh  | rwh  |

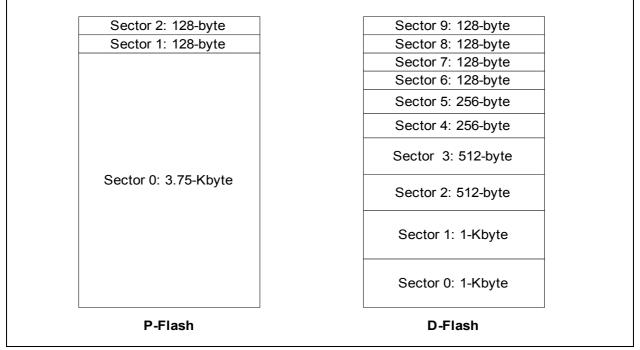

Figure 11 Flash Bank Sectorization

The internal structure of each Flash bank represents a sector architecture for flexible erase capability. The minimum erase width is always a complete sector, and sectors can be erased separately or in parallel. Contrary to standard EPROMs, erased Flash memory cells contain 0s.

The D-Flash bank is divided into more physical sectors for extended erasing and reprogramming capability; even numbers for each sector size are provided to allow greater flexibility and the ability to adapt to a wide range of application requirements.

# 3.3.2 Parallel Read Access of P-Flash

To enhance system performance, the P-Flash banks are configured for parallel read to allow two bytes of linear code to be read in 4 x CCLK cycles, compared to 6 x CCLK cycles if serial read is performed. This is achieved by reading two bytes in parallel from a P-Flash bank pair within the 3 x CCLK cycles access time and storing them in a cache. Subsequent read from the cache by the CPU does not require a wait state and can be completed within 1 x CCLK cycle. The result is the average instruction fetch time from the P-Flash banks is reduced and thus, the MIPS (Mega Instruction Per Second) of the system is increased.

However, if the parallel read feature is not desired due to certain timing constraints, it can be disabled by calling the parallel read disable subroutine.

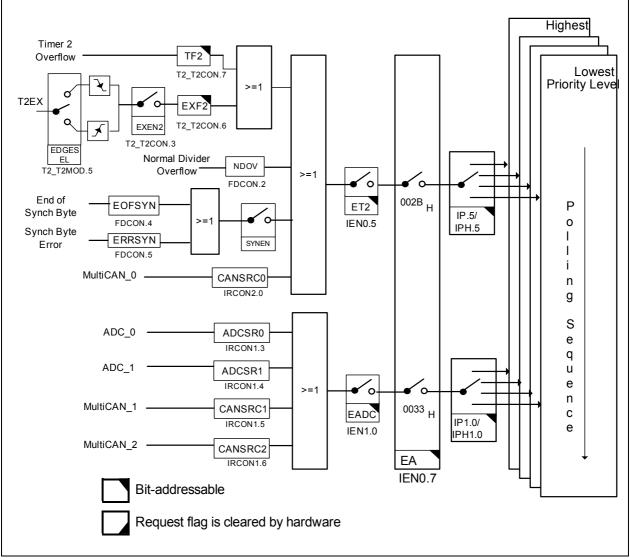

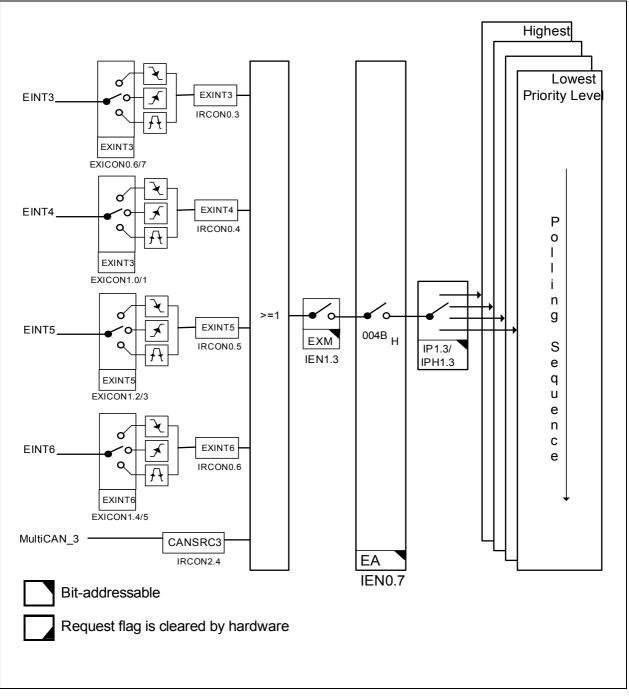

Figure 15 Interrupt Request Sources (Part 2)

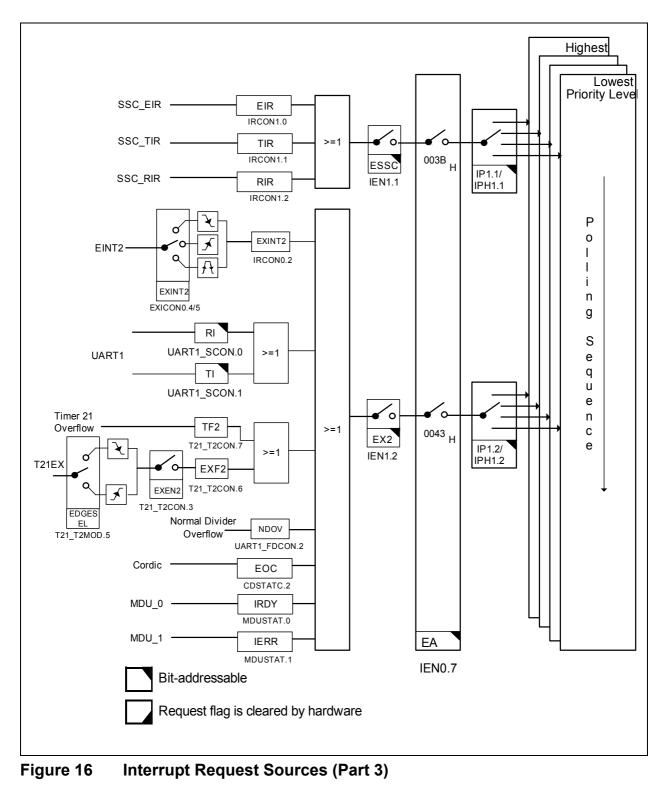

Figure 17 Interrupt Request Sources (Part 4)

If the WDT is not serviced before the timer overflow, a system malfunction is assumed. As a result, the WDT NMI is triggered (assert FNMIWDT) and the reset prewarning is entered. The prewarning period lasts for  $30_{\rm H}$  count, after which the system is reset (assert WDTRST).

The WDT has a "programmable window boundary" which disallows any refresh during the WDT's count-up. A refresh during this window boundary constitutes an invalid access to the WDT, causing the reset prewarning to be entered but without triggering the WDT NMI. The system will still be reset after the prewarning period is over. The window boundary is from  $0000_{\rm H}$  to the value obtained from the concatenation of WDTWINB and  $00_{\rm H}$ .

After being serviced, the WDT continues counting up from the value ( $\langle WDTREL \rangle * 2^8$ ). The time period for an overflow of the WDT is programmable in two ways:

- The input frequency to the WDT can be selected to be either  $f_{\rm PCLK}/2$  or  $f_{\rm PCLK}/128$

- The reload value WDTREL for the high byte of WDT can be programmed in register WDTREL

The period,  $P_{\rm WDT}$ , between servicing the WDT and the next overflow can be determined by the following formula:

$$P_{WDT} = \frac{2^{(1 + WDTIN \times 6)} \times (2^{16} - WDTREL \times 2^8)}{f_{PCLK}}$$

(3.4)

If the Window-Boundary Refresh feature of the WDT is enabled, the period  $P_{\rm WDT}$  between servicing the WDT and the next overflow is shortened if WDTWINB is greater than WDTREL, see **Figure 29**. This period can be calculated using the same formula by replacing WDTREL with WDTWINB. For this feature to be useful, WDTWINB cannot be smaller than WDTREL.

## 3.16 High-Speed Synchronous Serial Interface

The High-Speed Synchronous Serial Interface (SSC) supports full-duplex and half-duplex synchronous communication. The serial clock signal can be generated by the SSC internally (master mode), using its own 16-bit baud-rate generator, or can be received from an external master (slave mode). Data width, shift direction, clock polarity and phase are programmable. This allows communication with SPI-compatible devices or devices using other synchronous serial interfaces.

#### Features

- Master and slave mode operation

- Full-duplex or half-duplex operation

- Transmit and receive buffered

- Flexible data format

- Programmable number of data bits: 2 to 8 bits

- Programmable shift direction: LSB or MSB shift first

- Programmable clock polarity: idle low or high state for the shift clock

- Programmable clock/data phase: data shift with leading or trailing edge of the shift clock

- Variable baud rate

- Compatible with Serial Peripheral Interface (SPI)

- Interrupt generation

- On a transmitter empty condition

- On a receiver full condition

- On an error condition (receive, phase, baud rate, transmit error)

Data is transmitted or received on lines TXD and RXD, which are normally connected to the pins MTSR (Master Transmit/Slave Receive) and MRST (Master Receive/Slave Transmit). The clock signal is output via line MS\_CLK (Master Serial Shift Clock) or input via line SS\_CLK (Slave Serial Shift Clock). Both lines are normally connected to the pin SCLK. Transmission and reception of data are double-buffered.

Figure 32 shows the block diagram of the SSC.

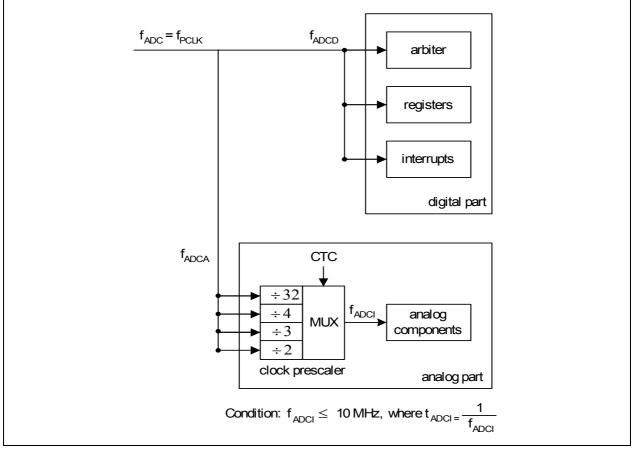

GLOBCTR. A prescaling ratio of 32 can be selected when the maximum performance of the ADC is not required.

#### Figure 35 ADC Clocking Scheme

For module clock  $f_{ADC}$  = 24 MHz, the analog clock  $f_{ADCI}$  frequency can be selected as shown in **Table 34**.

| Table 34 | f <sub>ADCI</sub> Frequency Selection |

|----------|---------------------------------------|

|----------|---------------------------------------|

| Module Clock $f_{ADC}$ | СТС                       | Prescaling Ratio | Analog Clock $f_{ADCI}$ |

|------------------------|---------------------------|------------------|-------------------------|

| 24 MHz                 | 00 <sub>B</sub>           | ÷ 2              | 12 MHz (N.A)            |

|                        | 01 <sub>B</sub>           | ÷ 3              | 8 MHz                   |

|                        | 10 <sub>B</sub>           | ÷ 4              | 6 MHz                   |

|                        | 11 <sub>B</sub> (default) | ÷ 32             | 750 kHz                 |

As  $f_{\rm ADCI}$  cannot exceed 10 MHz, bit field CTC should not be set to  $00_{\rm B}$  when  $f_{\rm ADC}$  is 24 MHz. During slow-down mode where  $f_{\rm ADC}$  may be reduced to 12 MHz, 6 MHz etc., CTC can be set to  $00_{\rm B}$  as long as the divided analog clock  $f_{\rm ADCI}$  does not exceed 10 MHz.

### Table 36Chip Identification Number (cont'd)

| Product Variant  | Chip Identification Number |         |         |  |  |  |  |

|------------------|----------------------------|---------|---------|--|--|--|--|

|                  | AA-Step                    | AB-Step | AC-Step |  |  |  |  |

| XC886LM-6RFA 3V3 | 22411522 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC888LM-6RFA 3V3 | 22411523 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC886CM-8RFA 3V3 | 22480502 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC888CM-8RFA 3V3 | 22480503 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC886C-8RFA 3V3  | 22480542 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC888C-8RFA 3V3  | 22480543 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC886-8RFA 3V3   | 22480562 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC888-8RFA 3V3   | 22480563 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC886CM-6RFA 3V3 | 22491502 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC888CM-6RFA 3V3 | 22491503 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC886C-6RFA 3V3  | 22491542 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC888C-6RFA 3V3  | 22491543 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC886-6RFA 3V3   | 22491562 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC888-6RFA 3V3   | 22491563 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC886CLM-8RFA 5V | 22800502 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC888CLM-8RFA 5V | 22800503 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC886LM-8RFA 5V  | 22800522 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC888LM-8RFA 5V  | 22800523 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC886CLM-6RFA 5V | 22811502 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC888CLM-6RFA 5V | 22811503 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC886LM-6RFA 5V  | 22811522 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC888LM-6RFA 5V  | 22811523 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC886CM-8RFA 5V  | 22880502 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC888CM-8RFA 5V  | 22880503 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC886C-8RFA 5V   | 22880542 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC888C-8RFA 5V   | 22880543 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC886-8RFA 5V    | 22880562 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC888-8RFA 5V    | 22880563 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC886CM-6RFA 5V  | 22891502 <sub>H</sub>      | -       | -       |  |  |  |  |

### Table 36Chip Identification Number (cont'd)

| Product Variant | Chip Identification Number |         |         |  |  |  |  |

|-----------------|----------------------------|---------|---------|--|--|--|--|

|                 | AA-Step                    | AB-Step | AC-Step |  |  |  |  |

| XC888CM-6RFA 5V | 22891503 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC886C-6RFA 5V  | 22891542 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC888C-6RFA 5V  | 22891543 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC886-6RFA 5V   | 22891562 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC888-6RFA 5V   | 22891563 <sub>H</sub>      | -       | -       |  |  |  |  |

#### **Electrical Parameters**

#### 4.2 DC Parameters

The electrical characteristics of the DC Parameters are detailed in this section.

#### 4.2.1 Input/Output Characteristics

Table 38 provides the characteristics of the input/output pins of the XC886/888.

| Table 38 | Input/Output Characteristics | s (Operating Conditions apply) |

|----------|------------------------------|--------------------------------|

|----------|------------------------------|--------------------------------|

| Parameter                                                      | Symbo             | ol | Limit                       | Values                      | Unit | Test Conditions                                             |

|----------------------------------------------------------------|-------------------|----|-----------------------------|-----------------------------|------|-------------------------------------------------------------|

|                                                                |                   |    | min.                        | max.                        |      |                                                             |

| V <sub>DDP</sub> = 5 V Range                                   |                   |    |                             |                             |      | ·                                                           |

| Output low voltage                                             | V <sub>OL</sub>   | CC | -                           | 1.0                         | V    | I <sub>OL</sub> = 15 mA                                     |

|                                                                |                   |    | -                           | 1.0                         | V    | $I_{\rm OL}$ = 5 mA, current into<br>all pins > 60 mA       |

|                                                                |                   |    | -                           | 0.4                         | V    | $I_{\rm OL}$ = 5 mA, current into all pins $\leq$ 60 mA     |

| Output high voltage                                            | V <sub>OH</sub>   | CC | V <sub>DDP</sub> -<br>1.0   | -                           | V    | I <sub>ОН</sub> = -15 mA                                    |

|                                                                |                   |    | V <sub>DDP</sub> -<br>1.0   | -                           | V    | $I_{\rm OH}$ = -5 mA, current<br>from all pins > 60 mA      |

|                                                                |                   |    | V <sub>DDP</sub> - 0.4      | -                           | V    | $I_{\rm OH}$ = -5 mA, current<br>from all pins $\leq$ 60 mA |

| Input low voltage on<br>port pins<br>(all except P0.0 & P0.1)  | V <sub>ILP</sub>  | SR | -                           | $0.3 \times V_{\text{DDP}}$ | V    | CMOS Mode                                                   |

| Input low voltage on P0.0 & P0.1                               | V <sub>ILP0</sub> | SR | -0.2                        | $0.3 \times V_{ m DDP}$     | V    | CMOS Mode                                                   |

| Input low voltage on<br>RESET pin                              | V <sub>ILR</sub>  | SR | -                           | $0.3 \times V_{\text{DDP}}$ | V    | CMOS Mode                                                   |

| Input low voltage on<br>TMS pin                                | V <sub>ILT</sub>  | SR | -                           | $0.3 \times V_{ m DDP}$     | V    | CMOS Mode                                                   |

| Input high voltage on<br>port pins<br>(all except P0.0 & P0.1) | V <sub>IHP</sub>  | SR | $0.7 \times V_{\text{DDP}}$ | -                           | V    | CMOS Mode                                                   |

| Input high voltage on P0.0 & P0.1                              | V <sub>IHP0</sub> | SR | $0.7 \times V_{ m DDP}$     | V <sub>DDP</sub>            | V    | CMOS Mode                                                   |

#### Package and Quality Declaration

# 5 Package and Quality Declaration

Chapter 5 provides the information of the XC886/888 package and reliability section.

#### 5.1 Package Parameters

Table 1 provides the thermal characteristics of the package used in XC886 and XC888.

| Parameter                        | Symbol           |    | Limit Values |      | Unit | Notes |

|----------------------------------|------------------|----|--------------|------|------|-------|

|                                  |                  |    | Min.         | Max. |      |       |

| PG-TQFP-48 (XC886)               | 1                |    |              | L    | l    |       |

| Thermal resistance junction case | R <sub>TJC</sub> | CC | -            | 13   | K/W  | 1)2)  |

| Thermal resistance junction lead | R <sub>TJL</sub> | CC | -            | 32.5 | K/W  | 1)2)_ |

| PG-TQFP-64 (XC888)               | •                |    |              |      |      |       |

| Thermal resistance junction case | R <sub>TJC</sub> | CC | -            | 12.6 | K/W  | 1)2)  |

| Thermal resistance junction lead | $R_{TJL}$        | CC | -            | 33.4 | K/W  | 1)2)  |

#### Table 1 Thermal Characteristics of the Packages

1) The thermal resistances between the case and the ambient  $(R_{TCA})$ , the lead and the ambient  $(R_{TLA})$  are to be combined with the thermal resistances between the junction and the case  $(R_{TJC})$ , the junction and the lead  $(R_{TJL})$  given above, in order to calculate the total thermal resistance between the junction and the ambient  $(R_{TJA})$ . The thermal resistances between the case and the ambient  $(R_{TCA})$ , the lead and the ambient  $(R_{TLA})$ . The thermal resistances between the case and the ambient  $(R_{TCA})$ , the lead and the ambient  $(R_{TLA})$  depend on the external system (PCB, case) characteristics, and are under user responsibility.

The junction temperature can be calculated using the following equation:  $T_J = T_A + R_{TJA} \times P_D$ , where the  $R_{TJA}$  is the total thermal resistance between the junction and the ambient. This total junction ambient resistance  $R_{TJA}$  can be obtained from the upper four partial thermal resistances, by

a) simply adding only the two thermal resistances (junction lead and lead ambient), or

b) by taking all four resistances into account, depending on the precision needed.

2) Not all parameters are 100% tested, but are verified by design/characterization and test correlation.