Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                          |

| Core Processor             | XC800                                                                             |

| Core Size                  | 8-Bit                                                                             |

| Speed                      | 24MHz                                                                             |

| Connectivity               | LINbus, SSI, UART/USART                                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                             |

| Number of I/O              | 48                                                                                |

| Program Memory Size        | 32KB (32K x 8)                                                                    |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 1.75K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                       |

| Data Converters            | A/D 8x10b                                                                         |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-LQFP                                                                           |

| Supplier Device Package    | PG-TQFP-64                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/sak-xc888lm-8ffi-5v-ac |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 8-Bit

# XC886/888CLM

8-Bit Single Chip Microcontroller

Data Sheet V1.2 2009-07

# Microcontrollers

#### **Table of Contents**

| 4.3.3 | Power-on Reset and PLL Timing 126      |

|-------|----------------------------------------|

| 4.3.4 | On-Chip Oscillator Characteristics 128 |

| 4.3.5 | External Clock Drive XTAL1 129         |

| 4.3.6 | JTAG Timing                            |

| 4.3.7 | SSC Master Mode Timing 132             |

| 5     | Package and Quality Declaration        |

| 5.1   | Package Parameters                     |

| 5.2   | Package Outline                        |

| 5.3   | Quality Declaration                    |

#### Summary of Features

#### XC886/888 Variant Devices

The XC886/888 product family features devices with different configurations, program memory sizes, package options, power supply voltage, temperature and quality profiles (Automotive or Industrial), to offer cost-effective solutions for different application requirements.

The list of XC886/888 device configurations are summarized in **Table 1**. For each configuration, 2 types of packages are available:

- PG-TQFP-48, which is denoted by XC886 and;

- PG-TQFP-64, which is denoted by XC888.

| Device Name  | CAN<br>Module | LIN BSL<br>Support | MDU<br>Module |

|--------------|---------------|--------------------|---------------|

| XC886/888    | No            | No                 | No            |

| XC886/888C   | Yes           | No                 | No            |

| XC886/888CM  | Yes           | No                 | Yes           |

| XC886/888LM  | No            | Yes                | Yes           |

| XC886/888CLM | Yes           | Yes                | Yes           |

#### Table 1Device Configuration

Note: For variants with LIN BSL support, only LIN BSL is available regardless of the availability of the CAN module.

From these 10 different combinations of configuration and package type, each are further made available in many sales types, which are grouped according to device type, program memory sizes, power supply voltage, temperature and quality profile (Automotive or Industrial), as shown in Table 2.

#### Table 2Device Profile

| Sales Type              | Device<br>Type | Program<br>Memory<br>(Kbytes) | Power<br>Supply<br>(V) | Temp-<br>erature<br>(°C) | Quality<br>Profile |

|-------------------------|----------------|-------------------------------|------------------------|--------------------------|--------------------|

| SAK-XC886*/888*-8FFA 5V | Flash          | 32                            | 5.0                    | -40 to 125               | Automotive         |

| SAK-XC886*/888*-6FFA 5V | Flash          | 24                            | 5.0                    | -40 to 125               | Automotive         |

| SAF-XC886*/888*-8FFA 5V | Flash          | 32                            | 5.0                    | -40 to 85                | Automotive         |

| SAF-XC886*/888*-6FFA 5V | Flash          | 24                            | 5.0                    | -40 to 85                | Automotive         |

| SAF-XC886*/888*-8FFI 5V | Flash          | 32                            | 5.0                    | -40 to 85                | Industrial         |

| SAF-XC886*/888*-6FFI 5V | Flash          | 24                            | 5.0                    | -40 to 85                | Industrial         |

#### **General Device Information**

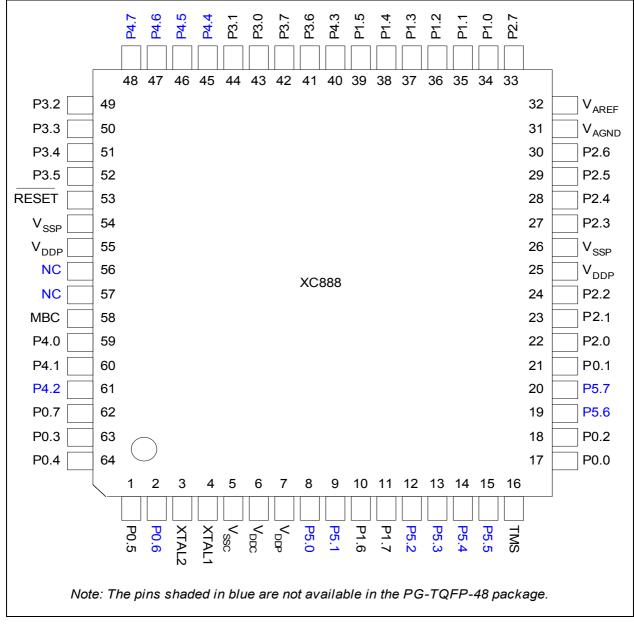

Figure 5 XC888 Pin Configuration, PG-TQFP-64 Package (top view)

#### XC886/888CLM

#### **General Device Information**

#### Table 3Pin Definitions and Functions (cont'd)

| Symbol | Pin Number<br>(TQFP-48/64) | Туре | Reset<br>State | Function                     |                                                                           |

|--------|----------------------------|------|----------------|------------------------------|---------------------------------------------------------------------------|

| P1.6   | 8/10                       |      | PU             | CCPOS1_1<br>T12HR_0          | •                                                                         |

|        |                            |      |                | EXINT6_0<br>RXDC0_2<br>T21_1 | • •                                                                       |

| P1.7   | 9/11                       |      | PU             | CCPOS2_1<br>T13HR_0<br>T2 1  | CCU6 Hall Input 2<br>CCU6 Timer 13 Hardware Run<br>Input<br>Timer 2 Input |

|        |                            |      |                | TXDC0_2                      | •                                                                         |

|        |                            |      |                |                              | .6 can be used as a software chip<br>t for the SSC.                       |

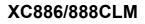

#### Figure 9 Address Extension by Paging

In order to access a register located in a page different from the actual one, the current page must be exited. This is done by reprogramming the bit field PAGE in the page register. Only then can the desired access be performed.

If an interrupt routine is initiated between the page register access and the module register access, and the interrupt needs to access a register located in another page, the current page setting can be saved, the new one programmed and the old page setting restored. This is possible with the storage fields STx (x = 0 - 3) for the save and restore action of the current page setting. By indicating which storage bit field should be used in parallel with the new page value, a single write operation can:

• Save the contents of PAGE in STx before overwriting with the new value (this is done in the beginning of the interrupt routine to save the current page setting and program the new page number); or

#### XC886/888CLM

#### **Functional Description**

#### Table 10Port Register Overview (cont'd)

| Addr            | Register Name                                                       | Bit       | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|-----------------|---------------------------------------------------------------------|-----------|----|----|----|----|----|----|----|----|

| RMAP =          | = 0, PAGE 1                                                         |           |    |    |    |    |    |    | L  |    |

| 80 <sub>H</sub> | P0_PUDSEL Reset: FF <sub>H</sub>                                    | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P0 Pull-Up/Pull-Down Select<br>Register                             | Туре      | rw |

| 86 <sub>H</sub> | P0_PUDEN Reset: C4 <sub>H</sub>                                     | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P0 Pull-Up/Pull-Down Enable Register                                | Туре      | rw |

| 90 <sub>H</sub> | P1_PUDSEL Reset: FF <sub>H</sub>                                    | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P1 Pull-Up/Pull-Down Select<br>Register                             | Туре      | rw |

| 91 <sub>H</sub> | P1_PUDEN Reset: FF <sub>H</sub>                                     | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P1 Pull-Up/Pull-Down Enable Register                                | Туре      | rw |

| 92 <sub>H</sub> | P5_PUDSEL Reset: FF <sub>H</sub>                                    | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P5 Pull-Up/Pull-Down Select<br>Register                             | Туре      | rw |

| 93 <sub>H</sub> | P5_PUDEN Reset: FF <sub>H</sub>                                     | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P5 Pull-Up/Pull-Down Enable Register                                | Туре      | rw |

| A0 <sub>H</sub> | P2_PUDSEL Reset: FF <sub>H</sub>                                    | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P2 Pull-Up/Pull-Down Select<br>Register                             | Туре      | rw |

| A1 <sub>H</sub> | P2_PUDEN Reset: 00 <sub>H</sub>                                     | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P2 Pull-Up/Pull-Down Enable<br>Register                             | Туре      | rw |

| во <sub>Н</sub> | P3_PUDSEL Reset: BF <sub>H</sub>                                    | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P3 Pull-Up/Pull-Down Select<br>Register                             | Туре      | rw |

| в1 <sub>Н</sub> | P3_PUDEN Reset: 40 <sub>H</sub>                                     | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P3 Pull-Up/Pull-Down Enable<br>Register                             | Туре      | rw |

| C8 <sub>H</sub> | P4_PUDSEL Reset: FF <sub>H</sub>                                    | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P4 Pull-Up/Pull-Down Select<br>Register                             | Туре      | rw |

| C9 <sub>H</sub> | P4_PUDEN Reset: 04 <sub>H</sub>                                     | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P4 Pull-Up/Pull-Down Enable<br>Register                             | Туре      | rw |

| RMAP =          | = 0, PAGE 2                                                         |           |    |    |    |    |    |    |    |    |

| <sup>80</sup> H | P0_ALTSEL0 Reset: 00 <sub>H</sub>                                   | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P0 Alternate Select 0 Register                                      | Туре      | rw |

| 86 <sub>H</sub> | P0_ALTSEL1 Reset: 00 <sub>H</sub><br>P0 Alternate Select 1 Register | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 |                                                                     | Туре      | rw |

| 90 <sub>H</sub> | P1_ALTSEL0 Reset: 00 <sub>H</sub><br>P1 Alternate Select 0 Register | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 |                                                                     | Туре      | rw |

| 91 <sub>H</sub> | P1_ALTSEL1 Reset: 00 <sub>H</sub><br>P1 Alternate Select 1 Register | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 |                                                                     | Туре      | rw |

| 92 <sub>H</sub> | P5_ALTSEL0 Reset: 00 <sub>H</sub><br>P5 Alternate Select 0 Register | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 |                                                                     | Туре      | rw |

#### Table 10Port Register Overview (cont'd)

| Addr            | Register Name                     | Bit       | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|-----------------|-----------------------------------|-----------|----|----|----|----|----|----|----|----|

| 93 <sub>H</sub> | P5_ALTSEL1 Reset: 00 <sub>H</sub> | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P5 Alternate Select 1 Register    | Туре      | rw |

| во <sub>Н</sub> | P3_ALTSEL0 Reset: 00 <sub>H</sub> | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P3 Alternate Select 0 Register    | Туре      | rw |

| B1 <sub>H</sub> | P3_ALTSEL1 Reset: 00 <sub>H</sub> | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P3 Alternate Select 1 Register    | Туре      | rw |

| C8 <sub>H</sub> | P4_ALTSEL0 Reset: 00 <sub>H</sub> | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P4 Alternate Select 0 Register    | Туре      | rw |

| C9 <sub>H</sub> | P4_ALTSEL1 Reset: 00 <sub>H</sub> | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P4 Alternate Select 1 Register    | Туре      | rw |

| RMAP =          | = 0, PAGE 3                       |           |    |    |    |    |    |    |    |    |

| 80 <sub>H</sub> | P0_OD Reset: 00 <sub>H</sub>      | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P0 Open Drain Control Register    | Туре      | rw |

| 90 <sub>H</sub> | P1_OD Reset: 00 <sub>H</sub>      | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P1 Open Drain Control Register    | Туре      | rw |

| 92 <sub>H</sub> | P5_OD Reset: 00 <sub>H</sub>      | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P5 Open Drain Control Register    | Туре      | rw |

| в0 <sub>Н</sub> | P3_OD Reset: 00 <sub>H</sub>      | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P3 Open Drain Control Register    | Туре      | rw |

| C8 <sub>H</sub> | P4_OD Reset: 00 <sub>H</sub>      | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P4 Open Drain Control Register    | Туре      | rw |

#### 3.2.4.7 ADC Registers

The ADC SFRs can be accessed in the standard memory area (RMAP = 0).

#### Table 11ADC Register Overview

|                 | •                                                                    |           |           |           |     |      |      |       |            |       |  |

|-----------------|----------------------------------------------------------------------|-----------|-----------|-----------|-----|------|------|-------|------------|-------|--|

| Addr            | Register Name                                                        | Bit       | 7         | 6         | 5   | 4    | 3    | 2 1 0 |            |       |  |

| RMAP =          | = 0                                                                  |           |           |           |     |      |      | •     |            |       |  |

| D1 <sub>H</sub> | ADC_PAGE Reset: 00 <sub>H</sub>                                      | Bit Field | C         | P         | ST  | NR   | 0    | PAGE  |            |       |  |

|                 | Page Register                                                        | Туре      | ١         | N         | ١   | N    | r    |       | rw         |       |  |

| RMAP =          | = 0, PAGE 0                                                          |           |           |           |     |      |      |       |            |       |  |

| са <sub>Н</sub> | ADC_GLOBCTR Reset: 30 <sub>H</sub>                                   | Bit Field | ANON      | DW        | CTC |      | 0    |       |            |       |  |

|                 | Global Control Register                                              | Туре      | rw        | rw        | r   | rw   |      |       | r          |       |  |

| св <sub>Н</sub> | ADC_GLOBSTR Reset: 00 <sub>H</sub><br>Global Status Register         | Bit Field | (         | 0         |     | CHNR |      | 0     | SAMP<br>LE | BUSY  |  |

|                 |                                                                      | Туре      |           | r         |     | rh   | r rh |       | rh         | rh    |  |

| сс <sub>Н</sub> | ADC_PRAR Reset: 00 <sub>H</sub><br>Priority and Arbitration Register | Bit Field | ASEN<br>1 | ASEN<br>0 | 0   | ARBM | CSM1 | PRIO1 | CSM0       | PRIO0 |  |

|                 |                                                                      | Туре      | rw        | rw        | r   | rw   | rw   | rw    | rw         | rw    |  |

### 3.2.4.12 SSC Registers

The SSC SFRs can be accessed in the standard memory area (RMAP = 0).

| Addr            | Register Name                                  | Bit       | 7  | 6  | 5  | 4    | 3    | 2   | 1   | 0   |  |

|-----------------|------------------------------------------------|-----------|----|----|----|------|------|-----|-----|-----|--|

| RMAP =          | = 0                                            |           |    |    |    |      |      |     |     |     |  |

| A9 <sub>H</sub> | SSC_PISEL Reset: 00 <sub>H</sub>               | Bit Field |    |    | 0  |      |      | CIS | SIS | MIS |  |

|                 | Port Input Select Register                     | Туре      |    |    | r  |      |      | rw  | rw  | rw  |  |

| AA <sub>H</sub> | SSC_CONL Reset: 00 <sub>H</sub>                | Bit Field | LB | PO | PH | HB   |      | В   | М   |     |  |

|                 | Control Register Low<br>Programming Mode       | Туре      | rw | rw | rw | rw   | rw   |     |     |     |  |

| AA <sub>H</sub> | SSC_CONL Reset: 00 <sub>H</sub>                | Bit Field |    | (  | )  |      |      | В   | С   |     |  |

|                 | Control Register Low<br>Operating Mode         | Туре      |    | l  | r  |      |      | r   | h   |     |  |

| ав <sub>Н</sub> | B <sub>H</sub> SSC_CONH Reset: 00 <sub>H</sub> | Bit Field | EN | MS | 0  | AREN | BEN  | PEN | REN | TEN |  |

|                 | Control Register High<br>Programming Mode      | Туре      | rw | rw | r  | rw   | rw   | rw  | rw  | rw  |  |

| ав <sub>Н</sub> | SSC_CONH Reset: 00 <sub>H</sub>                | Bit Field | EN | MS | 0  | BSY  | BE   | PE  | RE  | TE  |  |

|                 | Control Register High<br>Operating Mode        | Туре      | rw | rw | r  | rh   | rwh  | rwh | rwh | rwh |  |

| ac <sub>h</sub> | SSC_TBL Reset: 00 <sub>H</sub>                 | Bit Field |    |    |    | TB_V | ALUE |     |     |     |  |

|                 | Transmitter Buffer Register Low                | Туре      |    |    |    | n    | N    |     |     |     |  |

| ad <sub>H</sub> | SSC_RBL Reset: 00 <sub>H</sub>                 | Bit Field |    |    |    | RB_V | ALUE |     |     |     |  |

|                 | Receiver Buffer Register Low                   | Туре      |    |    |    | rl   | า    |     |     |     |  |

| ае <sub>Н</sub> | SSC_BRL Reset: 00 <sub>H</sub>                 | Bit Field |    |    |    | BR_V | ALUE |     |     |     |  |

|                 | Baud Rate Timer Reload<br>Register Low         | Туре      | rw |    |    |      |      |     |     |     |  |

| af <sub>h</sub> | SSC_BRH Reset: 00 <sub>H</sub>                 | Bit Field |    |    |    | BR_V | ALUE |     |     |     |  |

|                 | Baud Rate Timer Reload<br>Register High        |           |    |    |    | n    | N    |     |     |     |  |

#### Table 16 SSC Register Overview

#### 3.2.4.13 MultiCAN Registers

The MultiCAN SFRs can be accessed in the standard memory area (RMAP = 0).

| Addr            | Register Name                        | Bit       | 7   | 6   | 5   | 4   | 3    | 2    | 1    | 0    |

|-----------------|--------------------------------------|-----------|-----|-----|-----|-----|------|------|------|------|

| RMAP =          | : 0                                  |           |     |     |     |     |      |      |      |      |

| D8 <sub>H</sub> | ADCON Reset: 00 <sub>H</sub>         | Bit Field | V3  | V2  | V1  | V0  | AU   | AD   | BSY  | RWEN |

|                 | CAN Address/Data Control<br>Register | Туре      | rw  | rw  | rw  | rw  | r    | W    | rh   | rw   |

| D9 <sub>H</sub> | ADL Reset: 00 <sub>H</sub>           | Bit Field | CA9 | CA8 | CA7 | CA6 | CA5  | CA4  | CA3  | CA2  |

|                 | CAN Address Register Low             | Туре      | rwh | rwh | rwh | rwh | rwh  | rwh  | rwh  | rwh  |

| DA <sub>H</sub> | ADH Reset: 00 <sub>H</sub>           | Bit Field |     | (   | )   |     | CA13 | CA12 | CA11 | CA10 |

|                 | CAN Address Register High            |           |     |     | ſ   |     | rwh  | rwh  | rwh  | rwh  |

#### XC886/888CLM

#### **Functional Description**

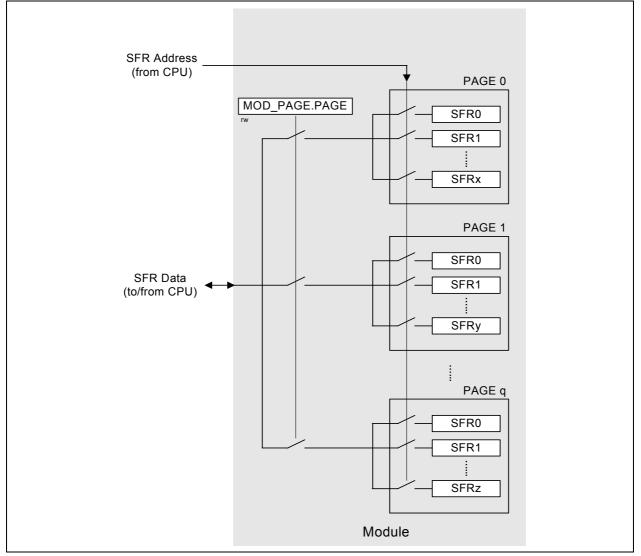

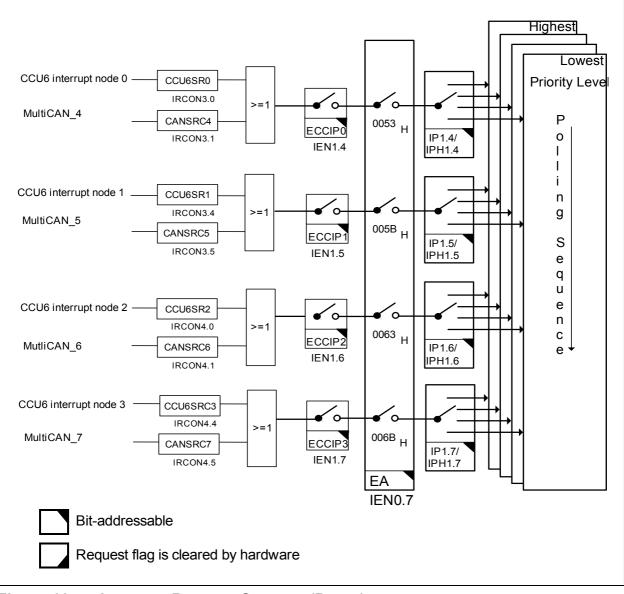

Figure 14 Interrupt Request Sources (Part 1)

Figure 18 Interrupt Request Sources (Part 5)

Table 25 shows the VCO range for the XC886/888.

| <i>f</i> <sub>vcomin</sub> | f <sub>VCOmax</sub> | $f_{\sf VCOFREEmin}$ | <b><i>f</i></b> <sub>VCOFREEmax</sub> | Unit |

|----------------------------|---------------------|----------------------|---------------------------------------|------|

| 150                        | 200                 | 20                   | 80                                    | MHz  |

| 100                        | 150                 | 10                   | 80                                    | MHz  |

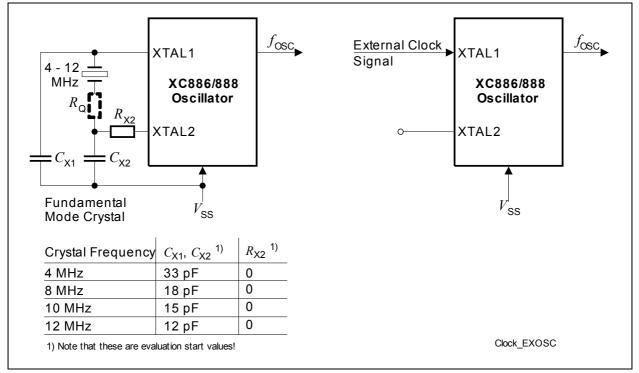

#### 3.8.1 Recommended External Oscillator Circuits

The oscillator circuit, a Pierce oscillator, is designed to work with both, an external crystal oscillator or an external stable clock source. It basically consists of an inverting amplifier and a feedback element with XTAL1 as input, and XTAL2 as output.

When using a crystal, a proper external oscillator circuitry must be connected to both pins, XTAL1 and XTAL2. The crystal frequency can be within the range of 4 MHz to 12 MHz. Additionally, it is necessary to have two load capacitances  $C_{X1}$  and  $C_{X2}$ , and depending on the crystal type, a series resistor  $R_{X2}$ , to limit the current. A test resistor  $R_Q$  may be temporarily inserted to measure the oscillation allowance (negative resistance) of the oscillator circuitry.  $R_Q$  values are typically specified by the crystal vendor. The  $C_{X1}$  and  $C_{X2}$  values shown in **Figure 25** can be used as starting points for the negative resistance evaluation and for non-productive systems. The exact values and related operating range are dependent on the crystal frequency and have to be determined and optimized together with the final target system is strongly recommended to verify the input amplitude at XTAL1 and to determine the actual oscillation allowance (margin negative resistance) for the oscillator-crystal system.

When using an external clock signal, the signal must be connected to XTAL1. XTAL2 is left open (unconnected).

The oscillator can also be used in combination with a ceramic resonator. The final circuitry must also be verified by the resonator vendor. **Figure 25** shows the recommended external oscillator circuitries for both operating modes, external crystal mode and external input clock mode.

#### Figure 25 External Oscillator Circuitry

Note: For crystal operation, it is strongly recommended to measure the negative resistance in the final target system (layout) to determine the optimum parameters for the oscillator operation. Please refer to the minimum and maximum values of the negative resistance specified by the crystal supplier.

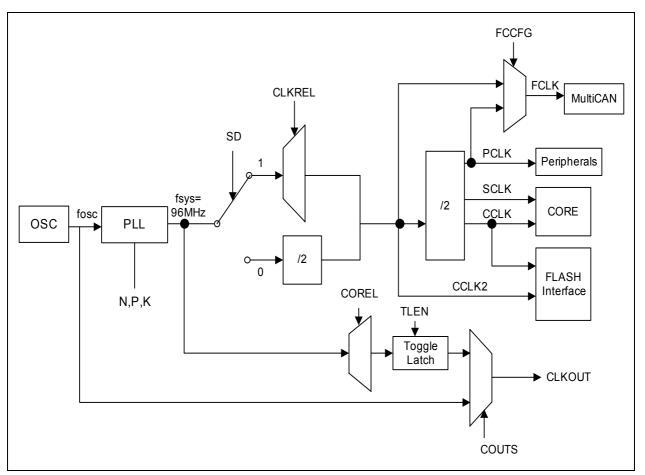

#### 3.8.2 Clock Management

The CGU generates all clock signals required within the microcontroller from a single clock,  $f_{sys}$ . During normal system operation, the typical frequencies of the different modules are as follow:

- CPU clock: CCLK, SCLK = 24 MHz

- Fast clock (used by MultiCAN): FCLK = 24 or 48 MHz

- Peripheral clock: PCLK = 24 MHz

- Flash Interface clock: CCLK2 = 48 MHz and CCLK = 24 MHz

In addition, different clock frequencies can be output to pin CLKOUT (P0.0 or P0.7). The clock output frequency, which is derived from the clock output divider (bit COREL), can further be divided by 2 using toggle latch (bit TLEN is set to 1). The resulting output frequency has a 50% duty cycle. **Figure 26** shows the clock distribution of the XC886/888.

Figure 26 Clock Generation from  $f_{sys}$

#### 3.16 High-Speed Synchronous Serial Interface

The High-Speed Synchronous Serial Interface (SSC) supports full-duplex and half-duplex synchronous communication. The serial clock signal can be generated by the SSC internally (master mode), using its own 16-bit baud-rate generator, or can be received from an external master (slave mode). Data width, shift direction, clock polarity and phase are programmable. This allows communication with SPI-compatible devices or devices using other synchronous serial interfaces.

#### Features

- Master and slave mode operation

- Full-duplex or half-duplex operation

- Transmit and receive buffered

- Flexible data format

- Programmable number of data bits: 2 to 8 bits

- Programmable shift direction: LSB or MSB shift first

- Programmable clock polarity: idle low or high state for the shift clock

- Programmable clock/data phase: data shift with leading or trailing edge of the shift clock

- Variable baud rate

- Compatible with Serial Peripheral Interface (SPI)

- Interrupt generation

- On a transmitter empty condition

- On a receiver full condition

- On an error condition (receive, phase, baud rate, transmit error)

Data is transmitted or received on lines TXD and RXD, which are normally connected to the pins MTSR (Master Transmit/Slave Receive) and MRST (Master Receive/Slave Transmit). The clock signal is output via line MS\_CLK (Master Serial Shift Clock) or input via line SS\_CLK (Slave Serial Shift Clock). Both lines are normally connected to the pin SCLK. Transmission and reception of data are double-buffered.

Figure 32 shows the block diagram of the SSC.

#### 3.18 Timer 2 and Timer 21

Timer 2 and Timer 21 are 16-bit general purpose timers (THL2) that are fully compatible and have two modes of operation, a 16-bit auto-reload mode and a 16-bit one channel capture mode, see **Table 33**. As a timer, the timers count with an input clock of PCLK/12 (if prescaler is disabled). As a counter, they count 1-to-0 transitions on pin T2. In the counter mode, the maximum resolution for the count is PCLK/24 (if prescaler is disabled).

| Table 33           | Timer 2 Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Mode               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| Auto-reload        | <ul> <li>Up/Down Count Disabled</li> <li>Count up only</li> <li>Start counting from 16-bit reload value, overflow at FFFF<sub>H</sub></li> <li>Reload event configurable for trigger by overflow condition only, or by negative/positive edge at input pin T2EX as well</li> <li>Programmble reload value in register RC2</li> <li>Interrupt is generated with reload event</li> </ul>                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

|                    | <ul> <li>Up/Down Count Enabled</li> <li>Count up or down, direction determined by level at input pin T2EX</li> <li>No interrupt is generated</li> <li>Count up <ul> <li>Start counting from 16-bit reload value, overflow at FFFF<sub>H</sub></li> <li>Reload event triggered by overflow condition</li> <li>Programmble reload value in register RC2</li> </ul> </li> <li>Count down <ul> <li>Start counting from FFFF<sub>H</sub>, underflow at value defined in register RC2</li> <li>Reload event triggered by underflow condition <ul> <li>Reload event triggered by underflow condition</li> <li>Reload event triggered by underflow condition</li> </ul> </li> </ul></li></ul> |  |  |  |  |  |  |

| Channel<br>capture | <ul> <li>Count up only</li> <li>Start counting from 0000<sub>H</sub>, overflow at FFFF<sub>H</sub></li> <li>Reload event triggered by overflow condition</li> <li>Reload value fixed at 0000<sub>H</sub></li> <li>Capture event triggered by falling/rising edge at pin T2EX</li> <li>Captured timer value stored in register RC2</li> <li>Interrupt is generated with reload or capture event</li> </ul>                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

## 3.22 On-Chip Debug Support

The On-Chip Debug Support (OCDS) provides the basic functionality required for the software development and debugging of XC800-based systems.

The OCDS design is based on these principles:

- Use the built-in debug functionality of the XC800 Core

- · Add a minimum of hardware overhead

- Provide support for most of the operations by a Monitor Program

- Use standard interfaces to communicate with the Host (a Debugger)

#### Features

- Set breakpoints on instruction address and on address range within the Program Memory

- Set breakpoints on internal RAM address range

- Support unlimited software breakpoints in Flash/RAM code region

- Process external breaks via JTAG and upon activating a dedicated pin

- Step through the program code

The OCDS functional blocks are shown in **Figure 37**. The Monitor Mode Control (MMC) block at the center of OCDS system brings together control signals and supports the overall functionality. The MMC communicates with the XC800 Core, primarily via the Debug Interface, and also receives reset and clock signals.

After processing memory address and control signals from the core, the MMC provides proper access to the dedicated extra-memories: a Monitor ROM (holding the code) and a Monitor RAM (for work-data and Monitor-stack).

The OCDS system is accessed through the JTAG<sup>1)</sup>, which is an interface dedicated exclusively for testing and debugging activities and is not normally used in an application. The dedicated MBC pin is used for external configuration and debugging control.

Note: All the debug functionality described here can normally be used only after XC886/888 has been started in OCDS mode.

<sup>1)</sup> The pins of the JTAG port can be assigned to either the primary port (Port 0) or either of the secondary ports (Ports 1 and 2/Port 5).

User must set the JTAG pins (TCK and TDI) as input during connection with the OCDS system.

#### **Electrical Parameters**

#### 4.2.4 **Power Supply Current**

Table 41, Table 42, Table 43 and Table 44 provide the characteristics of the power supply current in the XC886/888.

## Table 41Power Supply Current Parameters (Operating Conditions apply; $V_{\text{DDP}}$ = 5V range)

| Parameter                   | Symbol           | Limit Values       |                    | Unit | <b>Test Condition</b>      |

|-----------------------------|------------------|--------------------|--------------------|------|----------------------------|

|                             |                  | typ. <sup>1)</sup> | max. <sup>2)</sup> |      |                            |

| V <sub>DDP</sub> = 5V Range | ·                | •                  |                    |      | •                          |

| Active Mode                 | I <sub>DDP</sub> | 27.2               | 32.8               | mA   | Flash Device <sup>3)</sup> |

|                             |                  | 24.3               | 29.8               | mA   | ROM Device <sup>3)</sup>   |

| Idle Mode                   | I <sub>DDP</sub> | 21.1               | 25.3               | mA   | Flash Device <sup>4)</sup> |

|                             |                  | 18.2               | 21.6               | mA   | ROM Device <sup>4)</sup>   |

| Active Mode with slow-down  | I <sub>DDP</sub> | 14.1               | 17.0               | mA   | Flash Device <sup>5)</sup> |

| enabled                     |                  | 11.9               | 14.3               | mA   | ROM Device <sup>5)</sup>   |

| Idle Mode with slow-down    | I <sub>DDP</sub> | 11.7               | 15.0               | mA   | Flash Device <sup>6)</sup> |

| enabled                     |                  | 9.7                | 11.9               | mA   | ROM Device <sup>6)</sup>   |

1) The typical  $I_{\text{DDP}}$  values are periodically measured at  $T_{\text{A}}$  = + 25 °C and  $V_{\text{DDP}}$  = 5.0 V.

2) The maximum  $I_{\text{DDP}}$  values are measured under worst case conditions ( $T_{\text{A}}$  = + 125 °C and  $V_{\text{DDP}}$  = 5.5 V).

3)  $I_{\text{DDP}}$  (active mode) is measured with: CPU clock and input clock to all peripherals running at 24 MHz(set by on-chip oscillator of 9.6 MHz and NDIV in PLL\_CON to 1001<sub>B</sub>), RESET =  $V_{\text{DDP}}$ , no load on ports.

4)  $I_{\text{DDP}}$  (idle mode) is measured with: CPU clock disabled, watchdog timer disabled, input clock to all peripherals enabled and running at 24 MHz, RESET =  $V_{\text{DDP}}$ , no load on ports.

5)  $I_{\text{DDP}}$  (active mode with slow-down mode) is measured with: CPU clock and input clock to all peripherals running at 8 MHz by setting CLKREL in CMCON to 0110<sub>B</sub>, RESET =  $V_{\text{DDP}}$ , no load on ports.

6)  $I_{\text{DDP}}$  (idle mode with slow-down mode) is measured with: CPU clock disabled, watchdog timer disabled, input clock to all peripherals enabled and running at 8 MHz by setting CLKREL in CMCON to 0110<sub>B</sub>, RESET =  $V_{\text{DDP}}$ , no load on ports.

#### **Electrical Parameters**

## 4.3.3 Power-on Reset and PLL Timing

**Table 49** provides the characteristics of the power-on reset and PLL timing in the XC886/888.

| Table 46 | Power-On Reset and PLL Timing (Operating Conditions apply) |

|----------|------------------------------------------------------------|

|          |                                                            |

| Parameter                           | Symbol             |    | Limit Values |      |      | Unit | Test Conditions                                                              |

|-------------------------------------|--------------------|----|--------------|------|------|------|------------------------------------------------------------------------------|

|                                     |                    |    | min.         | typ. | max. |      |                                                                              |

| Pad operating voltage               | $V_{PAD}$          | CC | 2.3          | -    | -    | V    | 1)                                                                           |

| On-Chip Oscillator<br>start-up time | t <sub>OSCST</sub> | СС | -            | -    | 500  | ns   | 1)                                                                           |

| Flash initialization time           | t <sub>FINIT</sub> | CC | _            | 160  | _    | μS   | 1)                                                                           |

| RESET hold time                     | t <sub>RST</sub>   | SR | -            | 500  | _    | μS   | $V_{\rm DDP}$ rise time<br>(10% – 90%) $\leq$<br>500 $\mu$ s <sup>1)2)</sup> |

| PLL lock-in in time                 | t <sub>LOCK</sub>  | CC | -            | -    | 200  | μS   | 1)                                                                           |

| PLL accumulated jitter              | $D_{P}$            |    | -            | _    | 0.7  | ns   | 1)3)                                                                         |

1) Not all parameters are 100% tested, but are verified by design/characterization and test correlation.

2) RESET signal has to be active (low) until  $V_{\text{DDC}}$  has reached 90% of its maximum value (typ. 2.5 V).

3) PLL lock at 96 MHz using a 4 MHz external oscillator. The PLL Divider settings are K = 2, N = 48 and P = 1.

#### Package and Quality Declaration

#### 5.3 Quality Declaration

Table 2 shows the characteristics of the quality parameters in the XC886/888.

#### Table 2Quality Parameters

| Parameter                                                             | Symbol           | Limit Values |      | Unit | Notes                                                |

|-----------------------------------------------------------------------|------------------|--------------|------|------|------------------------------------------------------|

|                                                                       |                  | Min.         | Max. |      |                                                      |

| ESD susceptibility<br>according to Human Body<br>Model (HBM)          | V <sub>HBM</sub> | -            | 2000 | V    | Conforming to<br>EIA/JESD22-<br>A114-B <sup>1)</sup> |

| ESD susceptibility<br>according to Charged<br>Device Model (CDM) pins | V <sub>CDM</sub> | -            | 500  | V    | Conforming to JESD22-C101-C <sup>1)</sup>            |

1) Not all parameters are 100% tested, but are verified by design/characterization and test correlation.