Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Last Time Buy                                                                  |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | XC800                                                                          |

| Core Size                  | 8-Bit                                                                          |

| Speed                      | 24MHz                                                                          |

| Connectivity               | SSI, UART/USART                                                                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                          |

| Number of I/O              | 34                                                                             |

| Program Memory Size        | 32KB (32K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 1.75K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                    |

| Data Converters            | A/D 8x10b                                                                      |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 48-LQFP                                                                        |

| Supplier Device Package    | PG-TQFP-48                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xc8868ffi5vacfxuma1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Edition 2009-07 Published by Infineon Technologies AG 81726 Munich, Germany © 2009 Infineon Technologies AG All Rights Reserved.

#### Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

#### **General Device Information**

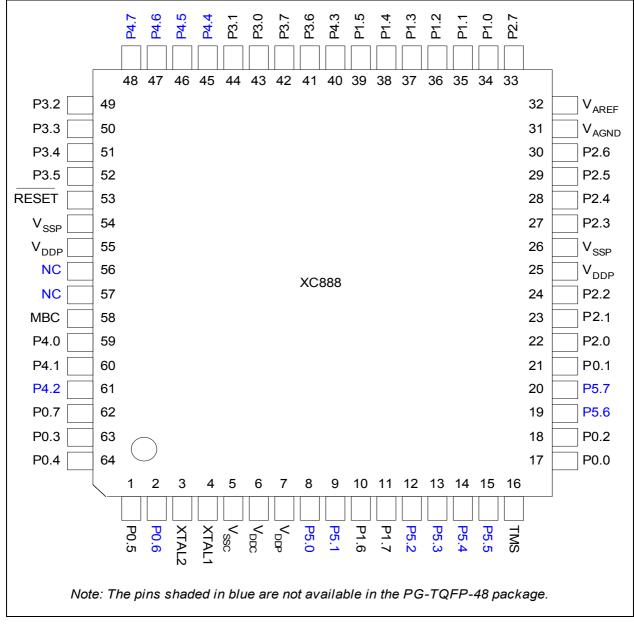

Figure 5 XC888 Pin Configuration, PG-TQFP-64 Package (top view)

### **General Device Information**

| Symbol | Pin Number<br>(TQFP-48/64) | Туре | Reset<br>State | Function                                                                                                                                                                                       |                                                                                                                                                              |  |  |  |  |

|--------|----------------------------|------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| P1     |                            | I/O  |                | Port 1<br>Port 1 is an 8-bit bidirectional general purpo<br>I/O port. It can be used as alternate function<br>for the JTAG, CCU6, UART, Timer 0, Timer<br>Timer 2, Timer 21, MultiCAN and SSC. |                                                                                                                                                              |  |  |  |  |

| P1.0   | 26/34                      |      | PU             | RXD_0<br>T2EX<br>RXDC0_0                                                                                                                                                                       | UART Receive Data Input<br>Timer 2 External Trigger Input<br>MultiCAN Node 0 Receiver Input                                                                  |  |  |  |  |

| P1.1   | 27/35                      |      | PU             | EXINT3<br>T0_1<br>TDO_1<br>TXD_0<br>TXDC0_0                                                                                                                                                    | External Interrupt Input 3<br>Timer 0 Input<br>JTAG Serial Data Output<br>UART Transmit Data<br>Output/Clock Output<br>MultiCAN Node 0 Transmitter<br>Output |  |  |  |  |

| P1.2   | 28/36                      |      | PU             | SCK_0                                                                                                                                                                                          | SSC Clock Input/Output                                                                                                                                       |  |  |  |  |

| P1.3   | 29/37                      |      | PU             | MTSR_0<br>TXDC1_3                                                                                                                                                                              | SSC Master Transmit<br>Output/Slave Receive Input<br>MultiCAN Node 1 Transmitter<br>Output                                                                   |  |  |  |  |

| P1.4   | 30/38                      |      | PU             | MRST_0<br>EXINT0_1<br>RXDC1_3                                                                                                                                                                  | SSC Master Receive Input/<br>Slave Transmit Output<br>External Interrupt Input 0<br>MultiCAN Node 1 Receiver Input                                           |  |  |  |  |

| P1.5   | 31/39                      |      | PU             | CCPOS0_1<br>EXINT5<br>T1_1<br>EXF2_0<br>RXDO_0                                                                                                                                                 | CCU6 Hall Input 0<br>External Interrupt Input 5<br>Timer 1 Input<br>Timer 2 External Flag Output<br>UART Transmit Data Output                                |  |  |  |  |

### Table 3Pin Definitions and Functions (cont'd)

### XC886/888CLM

### **General Device Information**

### Table 3Pin Definitions and Functions (cont'd)

| Symbol | Pin Number<br>(TQFP-48/64) | Туре | Reset<br>State | Function                     |                                                                           |

|--------|----------------------------|------|----------------|------------------------------|---------------------------------------------------------------------------|

| P1.6   | 8/10                       |      | PU             | CCPOS1_1<br>T12HR_0          | •                                                                         |

|        |                            |      |                | EXINT6_0<br>RXDC0_2<br>T21_1 | • •                                                                       |

| P1.7   | 9/11                       |      | PU             | CCPOS2_1<br>T13HR_0<br>T2 1  | CCU6 Hall Input 2<br>CCU6 Timer 13 Hardware Run<br>Input<br>Timer 2 Input |

|        |                            |      |                | TXDC0_2                      | •                                                                         |

|        |                            |      |                |                              | .6 can be used as a software chip<br>t for the SSC.                       |

| Flash Protection                      | Without hardware protection             | With hardware protection                                                                                               |                                             |  |  |  |  |

|---------------------------------------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|--|--|--|--|

| P-Flash program and erase             | Possible                                | Not possible                                                                                                           | Not possible                                |  |  |  |  |

| D-Flash<br>contents can be<br>read by | Read instructions in any program memory | Read instructions in any program memory                                                                                | Read instructions in the P-Flash or D-Flash |  |  |  |  |

| External access to D-Flash            | Not possible                            | Not possible                                                                                                           | Not possible                                |  |  |  |  |

| D-Flash<br>program                    | Possible                                | Possible                                                                                                               | Not possible                                |  |  |  |  |

| D-Flash erase                         | Possible                                | Possible, on<br>condition that bit<br>DFLASHEN in<br>register MISC_CON<br>is set to 1 prior to<br>each erase operation | Not possible                                |  |  |  |  |

#### Table 4Flash Protection Modes (cont'd)

BSL mode 6, which is used for enabling Flash protection, can also be used for disabling Flash protection. Here, the programmed password must be provided by the user. A password match triggers an automatic erase of the protected P-Flash and D-Flash contents, including the programmed password. The Flash protection is then disabled upon the next reset.

For the ROM device, the ROM is protected at all times and BSL mode 6 is used only to block external access to the device. However, unlike the Flash device, it is not possible to disable the memory protection of the ROM device. Here, entering BSL mode 6 will result in a protection error.

Note: If ROM read-out protection is enabled, only read instructions in the ROM memory can target the ROM contents.

Although no protection scheme can be considered infallible, the XC886/888 memory protection strategy provides a very high level of protection for a general purpose microcontroller.

SYSCON0

#### **Functional Description**

#### System Control Register 0 Reset Value: 04 7 5 4 3 2 1 0 6 IMODE 1 RMAP 0 0 0 r r r r rw rw

| Field | Bits          | Туре | Description                                                                                                                                                    |

|-------|---------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RMAP  | 0             | rw   | <ul> <li>Interrupt Node XINTR0 Enable</li> <li>The access to the standard SFR area is enabled</li> <li>The access to the mapped SFR area is enabled</li> </ul> |

| 1     | 2             | r    | <b>Reserved</b><br>Returns 1 if read; should be written with 1.                                                                                                |

| 0     | [7:5],<br>3,1 | r    | <b>Reserved</b><br>Returns 0 if read; should be written with 0.                                                                                                |

Note: The RMAP bit should be cleared/set by ANL or ORL instructions.

### 3.2.2.2 Address Extension by Paging

Address extension is further performed at the module level by paging. With the address extension by mapping, the XC886/888 has a 256-SFR address range. However, this is still less than the total number of SFRs needed by the on-chip peripherals. To meet this requirement, some peripherals have a built-in local address extension mechanism for increasing the number of addressable SFRs. The extended address range is not directly controlled by the CPU instruction itself, but is derived from bit field PAGE in the module page register MOD\_PAGE. Hence, the bit field PAGE must be programmed before accessing the SFR of the target module. Each module may contain a different number of pages and a different number of SFRs per page, depending on the specific requirement. Besides setting the correct RMAP bit value to select the SFR area, the user must also ensure that a valid PAGE is selected to target the desired SFR. A page inside the extended address range can be selected as shown in **Figure 9**.

### 3.2.4.8 Timer 2 Registers

The Timer 2 SFRs can be accessed in the standard memory area (RMAP = 0).

| Addr            | Register Name                                               | Bit       | 7          | 6          | 5           | 4    | 3         | 2     | 1    | 0          |

|-----------------|-------------------------------------------------------------|-----------|------------|------------|-------------|------|-----------|-------|------|------------|

| RMAP =          | = 0                                                         |           |            |            |             |      |           |       |      |            |

| c₀H             | T2_T2CON Reset: 00 <sub>H</sub><br>Timer 2 Control Register | Bit Field | TF2        | EXF2       | (           | )    | EXEN<br>2 | TR2   | C/T2 | CP/<br>RL2 |

|                 |                                                             | Туре      | rwh        | rwh        | I           | r    | rw        | rwh   | rw   | rw         |

| C1 <sub>H</sub> | T2_T2MOD Reset: 00 <sub>H</sub><br>Timer 2 Mode Register    | Bit Field | T2RE<br>GS | T2RH<br>EN | EDGE<br>SEL | PREN |           | T2PRE |      | DCEN       |

|                 |                                                             | Туре      | rw         | rw         | rw          | rw   | rw        | rw    | rw   | rw         |

| C2 <sub>H</sub> | T2_RC2L Reset: 00 <sub>H</sub>                              | Bit Field | RC2        |            |             |      |           |       |      |            |

|                 | Timer 2 Reload/Capture<br>Register Low                      | Туре      | rwh        |            |             |      |           |       |      |            |

| C3 <sub>H</sub> | T2_RC2H Reset: 00 <sub>H</sub>                              | Bit Field |            |            |             | R    | C2        |       |      |            |

|                 | Timer 2 Reload/Capture<br>Register High                     | Туре      |            |            |             | rv   | vh        |       |      |            |

| C4 <sub>H</sub> | T2_T2L Reset: 00 <sub>H</sub>                               | Bit Field |            |            |             | TH   | IL2       |       |      |            |

|                 | Timer 2 Register Low                                        | Туре      | rwh        |            |             |      |           |       |      |            |

| C5 <sub>H</sub> | 5 <sub>H</sub> T2_T2H Reset: 00 <sub>H</sub>                |           | d THL2     |            |             |      |           |       |      |            |

|                 | Timer 2 Register High                                       | Туре      |            |            |             | rv   | vh        |       |      |            |

#### Table 12T2 Register Overview

# 3.2.4.9 Timer 21 Registers

The Timer 21 SFRs can be accessed in the mapped memory area (RMAP = 1).

#### Table 13T21 Register Overview

|                 | 0                                           |           |            |            |             |      |           |       |      |            |  |

|-----------------|---------------------------------------------|-----------|------------|------------|-------------|------|-----------|-------|------|------------|--|

| Addr            | Register Name                               | Bit       | 7          | 6          | 5           | 4    | 3         | 2     | 1    | 0          |  |

| RMAP =          | = 1                                         |           |            |            |             |      |           |       |      |            |  |

| C0H             | T21_T2CONReset: 00HTimer 2 Control Register | Bit Field | TF2        | EXF2       | (           | 0    | EXEN<br>2 | TR2   | C/T2 | CP/<br>RL2 |  |

|                 |                                             | Туре      | rwh        | rwh        | I           | r    | rw        | rwh   | rw   | rw         |  |

| C1 <sub>H</sub> | T21_T2MODReset: 00Timer 2 Mode Register     | Bit Field | T2RE<br>GS | T2RH<br>EN | EDGE<br>SEL | PREN |           | T2PRE |      | DCEN       |  |

|                 |                                             | Туре      | rw         | rw         | rw          | rw   | rw        | rw    | rw   | rw         |  |

| C2 <sub>H</sub> | T21_RC2L Reset: 00 <sub>H</sub>             | Bit Field | RC2        |            |             |      |           |       |      |            |  |

|                 | Timer 2 Reload/Capture<br>Register Low      | Туре      | rwh        |            |             |      |           |       |      |            |  |

| C3 <sub>H</sub> | T21_RC2H Reset: 00 <sub>H</sub>             | Bit Field |            |            |             | R    | C2        |       |      |            |  |

|                 | Timer 2 Reload/Capture<br>Register High     | Туре      | rwh        |            |             |      |           |       |      |            |  |

| C4 <sub>H</sub> | T21_T2L Reset: 00 <sub>H</sub>              | Bit Field | THL2       |            |             |      |           |       |      |            |  |

|                 | Timer 2 Register Low                        | Туре      |            |            |             | ٢٧   | vh        |       |      |            |  |

# Table 14CCU6 Register Overview (cont'd)

| Addr            | Register Name                                                        | Bit       | 7          | 6          | 5          | 4          | 3          | 2          | 1           | 0           |  |

|-----------------|----------------------------------------------------------------------|-----------|------------|------------|------------|------------|------------|------------|-------------|-------------|--|

| FB <sub>H</sub> | CCU6_CC60RH Reset: 00 <sub>H</sub>                                   | Bit Field |            | 1          | 1          | CC6        | 60VH       | 1          | 1           | 1           |  |

|                 | Capture/Compare Register for<br>Channel CC60 High                    | Туре      |            |            |            | r          | 'n         |            |             |             |  |

| FC <sub>H</sub> | CCU6_CC61RL Reset: 00 <sub>H</sub>                                   | Bit Field |            |            |            | CC6        | 61VL       |            |             |             |  |

|                 | Capture/Compare Register for<br>Channel CC61 Low                     | Туре      |            | rh         |            |            |            |            |             |             |  |

| FD <sub>H</sub> | CCU6_CC61RH Reset: 00 <sub>H</sub>                                   | Bit Field |            |            |            | CC6        | 61VH       |            |             |             |  |

|                 | Capture/Compare Register for<br>Channel CC61 High                    | Туре      |            |            |            | r          | 'n         |            |             |             |  |

| FE <sub>H</sub> | CCU6_CC62RL Reset: 00 <sub>H</sub>                                   | Bit Field |            |            |            | CC6        | 62VL       |            |             |             |  |

|                 | Capture/Compare Register for<br>Channel CC62 Low                     | Туре      |            |            |            | r          | h          |            |             |             |  |

| FF <sub>H</sub> | CCU6_CC62RH Reset: 00 <sub>H</sub>                                   | Bit Field |            |            |            | CC6        | 62VH       |            |             |             |  |

|                 | Capture/Compare Register for<br>Channel CC62 High                    | Туре      |            |            |            | r          | 'n         |            |             |             |  |

| RMAP =          | 0, PAGE 2                                                            | _         |            |            |            |            | _          |            |             |             |  |

| 9A <sub>H</sub> | CCU6_T12MSELL Reset: 00 <sub>H</sub>                                 | Bit Field |            | MS         | EL61       |            |            | MSE        | EL60        |             |  |

|                 | T12 Capture/Compare Mode Select<br>Register Low                      | Туре      |            | r          | w          |            |            | r          | w           |             |  |

| 9В <sub>Н</sub> | CCU6_T12MSELH Reset: 00H                                             |           | DBYP       |            | HSYNC      |            |            | MSE        | EL62        |             |  |

|                 | T12 Capture/Compare Mode Select<br>Register High                     | Туре      | rw         |            | rw         |            | r          |            | w           |             |  |

| 9CH             | CCU6_IENL Reset: 00 <sub>H</sub>                                     | Bit Field | ENT1       | ENT1       | ENCC       | ENCC       | ENCC       | ENCC       | ENCC        | ENCC        |  |

|                 | Capture/Compare Interrupt Enable<br>Register Low                     |           | 2<br>PM    | 2<br>OM    | 62F        | 62R        | 61F        | 61R        | 60F         | 60R         |  |

|                 |                                                                      | Туре      | rw          | rw          |  |

| 9D <sub>H</sub> | CCU6_IENH Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Enable | Bit Field | EN<br>STR  | EN<br>IDLE | EN<br>WHE  | EN<br>CHE  | 0          | EN<br>TRPF | ENT1<br>3PM | ENT1<br>3CM |  |

|                 | Register High                                                        | Туре      | rw         | rw         | rw         | rw         | r          | rw         | rw          | rw          |  |

| 9E <sub>H</sub> | CCU6_INPL Reset: 40 <sub>H</sub>                                     | Bit Field | INP        | CHE        | INPO       | CC62       | INPCC61    |            | INPCC60     |             |  |

|                 | Capture/Compare Interrupt Node<br>Pointer Register Low               | Туре      | r          | w          | r          | w          | r          | w          | rw          |             |  |

| 9F <sub>H</sub> | CCU6_INPH Reset: 39 <sub>H</sub>                                     | Bit Field | (          | 0          | INPT13     |            | INF        | PT12       | INPERR      |             |  |

|                 | Capture/Compare Interrupt Node<br>Pointer Register High              | Туре      |            | r          | r          | w          | r          | w          | r           | w           |  |

| A4 <sub>H</sub> | CCU6_ISSL Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Status | Bit Field | ST12<br>PM | ST12<br>OM | SCC6<br>2F | SCC6<br>2R | SCC6<br>1F | SCC6<br>1R | SCC6<br>0F  | SCC6<br>0R  |  |

|                 | Set Register Low                                                     | Туре      | w          | w          | w          | w          | w          | w          | w           | w           |  |

| A5 <sub>H</sub> | CCU6_ISSH Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Status | Bit Field | SSTR       | SIDLE      | SWHE       | SCHE       | SWH<br>C   | STRP<br>F  | ST13<br>PM  | ST13<br>CM  |  |

|                 | Set Register High                                                    | Туре      | w          | w          | w          | w          | w          | w          | w           | w           |  |

| A6 <sub>H</sub> | CCU6_PSLR Reset: 00 <sub>H</sub>                                     | Bit Field | PSL63      | 0          |            |            | P          | SL         | •           |             |  |

|                 | Passive State Level Register                                         | Туре      | rwh        | r          | rwh        |            |            |            |             |             |  |

| а7 <sub>Н</sub> | CCU6_MCMCTR Reset: 00 <sub>H</sub>                                   | Bit Field | (          | 0          | SW         | SYN        | 0          |            | SWSEL       |             |  |

|                 | Multi-Channel Mode Control Register                                  | Туре      |            | r          | r          | w          | r          |            | rw          |             |  |

| FA <sub>H</sub> | CCU6_TCTR2LReset: 00HTimer Control Register 2 Low                    | Bit Field | 0          | T13        | TED        |            | T13TEC     |            | T13<br>SSC  | T12<br>SSC  |  |

|                 |                                                                      | Туре      | r          | r          | W          |            | rw         |            | rw          | rw          |  |

# 3.2.4.12 SSC Registers

The SSC SFRs can be accessed in the standard memory area (RMAP = 0).

| Addr            | Register Name                             | Bit       | 7                  | 6  | 5  | 4    | 3    | 2   | 1   | 0   |

|-----------------|-------------------------------------------|-----------|--------------------|----|----|------|------|-----|-----|-----|

| RMAP =          | = 0                                       |           |                    |    |    |      |      |     |     |     |

| A9 <sub>H</sub> | SSC_PISEL Reset: 00 <sub>H</sub>          | Bit Field |                    | 0  |    |      |      | CIS | SIS | MIS |

|                 | Port Input Select Register                | Туре      |                    |    | r  |      |      | rw  | rw  | rw  |

| AA <sub>H</sub> | SSC_CONL Reset: 00 <sub>H</sub>           | Bit Field | LB                 | PO | PH | HB   |      | В   | М   |     |

|                 | Control Register Low<br>Programming Mode  | Туре      | rw                 | rw | rw | rw   | rw   |     |     |     |

| AA <sub>H</sub> | SSC_CONL Reset: 00 <sub>H</sub>           | Bit Field |                    | (  | )  |      |      | В   | С   |     |

|                 | Control Register Low<br>Operating Mode    | Туре      |                    | r  |    |      | rh   |     |     |     |

| ав <sub>Н</sub> | SSC_CONH Reset: 00 <sub>H</sub>           | Bit Field | EN                 | MS | 0  | AREN | BEN  | PEN | REN | TEN |

|                 | Control Register High<br>Programming Mode | Туре      | rw                 | rw | r  | rw   | rw   | rw  | rw  | rw  |

| ав <sub>Н</sub> | SSC_CONH Reset: 00 <sub>H</sub>           | Bit Field | EN                 | MS | 0  | BSY  | BE   | PE  | RE  | TE  |

|                 | Control Register High<br>Operating Mode   | Туре      | rw                 | rw | r  | rh   | rwh  | rwh | rwh | rwh |

| ac <sub>h</sub> | SSC_TBL Reset: 00 <sub>H</sub>            | Bit Field | Bit Field TB_VALUE |    |    |      |      |     |     |     |

|                 | Transmitter Buffer Register Low           | Туре      | rw                 |    |    |      |      |     |     |     |

| ad <sub>H</sub> | SSC_RBL Reset: 00 <sub>H</sub>            | Bit Field |                    |    |    | RB_V | ALUE |     |     |     |

|                 | Receiver Buffer Register Low              | Туре      |                    |    |    | rl   | า    |     |     |     |

| ае <sub>Н</sub> | SSC_BRL Reset: 00 <sub>H</sub>            | Bit Field | ld BR_VALUE        |    |    |      |      |     |     |     |

|                 | Baud Rate Timer Reload<br>Register Low    | Туре      | rw                 |    |    |      |      |     |     |     |

| af <sub>h</sub> | SSC_BRH Reset: 00 <sub>H</sub>            | Bit Field |                    |    |    | BR_V | ALUE |     |     |     |

|                 | Baud Rate Timer Reload<br>Register High   | Туре      |                    |    |    | n    | N    |     |     |     |

#### Table 16 SSC Register Overview

### 3.2.4.13 MultiCAN Registers

The MultiCAN SFRs can be accessed in the standard memory area (RMAP = 0).

| Addr            | Register Name                                | Bit       | 7   | 6   | 5   | 4   | 3    | 2    | 1    | 0    |  |

|-----------------|----------------------------------------------|-----------|-----|-----|-----|-----|------|------|------|------|--|

| RMAP =          | RMAP = 0                                     |           |     |     |     |     |      |      |      |      |  |

| D8 <sub>H</sub> | D8 <sub>H</sub> ADCON Reset: 00 <sub>H</sub> |           | V3  | V2  | V1  | V0  | AU   | AD   | BSY  | RWEN |  |

|                 | CAN Address/Data Control<br>Register         | Туре      | rw  | rw  | rw  | rw  | rw   |      | rh   | rw   |  |

| D9 <sub>H</sub> | ADL Reset: 00 <sub>H</sub>                   | Bit Field | CA9 | CA8 | CA7 | CA6 | CA5  | CA4  | CA3  | CA2  |  |

|                 | CAN Address Register Low                     | Туре      | rwh | rwh | rwh | rwh | rwh  | rwh  | rwh  | rwh  |  |

| da <sub>h</sub> | ADH Reset: 00 <sub>H</sub>                   | Bit Field | 0   |     |     |     | CA13 | CA12 | CA11 | CA10 |  |

|                 | CAN Address Register High                    | Туре      |     |     | ſ   |     | rwh  | rwh  | rwh  | rwh  |  |

### 3.3.3 Flash Programming Width

For the P-Flash banks, a programmed wordline (WL) must be erased before it can be reprogrammed as the Flash cells can only withstand one gate disturb. This means that the entire sector containing the WL must be erased since it is impossible to erase a single WL.

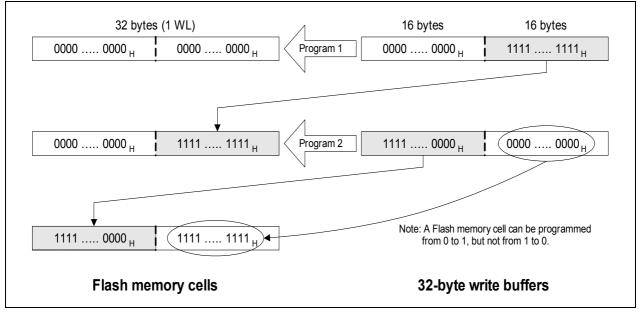

For the D-Flash bank, the same WL can be programmed twice before erasing is required as the Flash cells are able to withstand two gate disturbs. This means if the number of data bytes that needs to be written is smaller than the 32-byte minimum programming width, the user can opt to program this number of data bytes (x; where x can be any integer from 1 to 31) first and program the remaining bytes (32 - x) later. Hence, it is possible to program the same WL, for example, with 16 bytes of data two times (see **Figure 12**)

#### Figure 12 D-Flash Programming

Note: When programming a D-Flash WL the second time, the previously programmed Flash memory cells (whether 0s or 1s) should be reprogrammed with 0s to retain its original contents and to prevent "over-programming".

### 3.7.1 Module Reset Behavior

**Table 22** lists the functions of the XC886/888 and the various reset types that affect these functions. The symbol "■" signifies that the particular function is reset to its default state.

| Module/               | Wake-Up                              | Watchdog                  | Hardware                  | Power-On                  | Brownout                  |

|-----------------------|--------------------------------------|---------------------------|---------------------------|---------------------------|---------------------------|

| Function              | Reset                                | Reset                     | Reset                     | Reset                     | Reset                     |

| CPU Core              |                                      |                           |                           |                           |                           |

| Peripherals           |                                      |                           |                           |                           |                           |

| On-Chip<br>Static RAM | Not affected,<br>Reliable            | Not affected,<br>Reliable | Not affected,<br>Reliable | Affected, un-<br>reliable | Affected, un-<br>reliable |

| Oscillator,<br>PLL    |                                      | Not affected              |                           |                           |                           |

| Port Pins             |                                      |                           |                           |                           |                           |

| EVR                   | The voltage regulator is switched on | Not affected              |                           |                           |                           |

| FLASH                 |                                      |                           |                           |                           |                           |

| NMI                   | Disabled                             | Disabled                  |                           |                           |                           |

#### Table 22Effect of Reset on Device Functions

# 3.7.2 Booting Scheme

When the XC886/888 is reset, it must identify the type of configuration with which to start the different modes once the reset sequence is complete. Thus, boot configuration information that is required for activation of special modes and conditions needs to be applied by the external world through input pins. After power-on reset or hardware reset, the pins MBC, TMS and P0.0 collectively select the different boot options. Table 23 shows the available boot options in the XC886/888.

| MBC | TMS | P0.0 | Type of Mode                                                               | PC Start Value    |  |  |  |  |

|-----|-----|------|----------------------------------------------------------------------------|-------------------|--|--|--|--|

| 1   | 0   | Х    | User Mode <sup>1)</sup> ; on-chip OSC/PLL non-bypassed                     | 0000 <sub>H</sub> |  |  |  |  |

| 0   | 0   | Х    | BSL Mode; on-chip OSC/PLL non-bypassed <sup>2)</sup>                       | 0000 <sub>H</sub> |  |  |  |  |

| 0   | 1   | 0    | OCDS Mode; on-chip OSC/PLL non-<br>bypassed                                | 0000 <sub>H</sub> |  |  |  |  |

| 1   | 1   | 0    | User (JTAG) Mode <sup>3)</sup> ; on-chip OSC/PLL non-<br>bypassed (normal) | 0000 <sub>H</sub> |  |  |  |  |

| Table 23 | XC886/888 Boot Selection |

|----------|--------------------------|

|          |                          |

#### PLL Mode

The system clock is derived from the oscillator clock, multiplied by the N factor, and divided by the P and K factors. Both VCO bypass and PLL bypass must be inactive for this PLL mode. The PLL mode is used during normal system operation.

$$f_{SYS} = f_{OSC} \times \frac{N}{P \times K}$$

(3.3)

#### System Frequency Selection

For the XC886/888, the value of P is fixed to 1. In order to obtain the required fsys, the value of N and K can be selected by bits NDIV and KDIV respectively for different oscillator inputs. The output frequency must always be configured for 96 MHz. Table 24 provides examples on how  $f_{\rm sys}$  = 96 MHz can be obtained for the different oscillator sources.

| Table 24 | System frequency (f <sub>svs</sub> = 96 MHz) |

|----------|----------------------------------------------|

|----------|----------------------------------------------|

| Oscillator | Fosc    | Ν  | Р | К | Fsys   |

|------------|---------|----|---|---|--------|

| On-chip    | 9.6 MHz | 20 | 1 | 2 | 96 MHz |

| External   | 8 MHz   | 24 | 1 | 2 | 96 MHz |

|            | 6 MHz   | 32 | 1 | 2 | 96 MHz |

|            | 4 MHz   | 48 | 1 | 2 | 96 MHz |

For power saving purposes, the clocks may be disabled or slowed down according to **Table 26**.

# Table 26System frequency ( $f_{sys}$ = 96 MHz)

| Power Saving Mode | Action                                                                                                                   |  |  |  |  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Idle              | Clock to the CPU is disabled.                                                                                            |  |  |  |  |

| Slow-down         | Clocks to the CPU and all the peripherals are divided by a common programmable factor defined by bit field CMCON.CLKREL. |  |  |  |  |

| Power-down        | Oscillator and PLL are switched off.                                                                                     |  |  |  |  |

### 3.18 Timer 2 and Timer 21

Timer 2 and Timer 21 are 16-bit general purpose timers (THL2) that are fully compatible and have two modes of operation, a 16-bit auto-reload mode and a 16-bit one channel capture mode, see **Table 33**. As a timer, the timers count with an input clock of PCLK/12 (if prescaler is disabled). As a counter, they count 1-to-0 transitions on pin T2. In the counter mode, the maximum resolution for the count is PCLK/24 (if prescaler is disabled).

| Table 33           | Timer 2 Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mode               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Auto-reload        | <ul> <li>Up/Down Count Disabled</li> <li>Count up only</li> <li>Start counting from 16-bit reload value, overflow at FFFF<sub>H</sub></li> <li>Reload event configurable for trigger by overflow condition only, or by negative/positive edge at input pin T2EX as well</li> <li>Programmble reload value in register RC2</li> <li>Interrupt is generated with reload event</li> </ul>                                                                                                                                                                                                                                                                                                |

|                    | <ul> <li>Up/Down Count Enabled</li> <li>Count up or down, direction determined by level at input pin T2EX</li> <li>No interrupt is generated</li> <li>Count up <ul> <li>Start counting from 16-bit reload value, overflow at FFFF<sub>H</sub></li> <li>Reload event triggered by overflow condition</li> <li>Programmble reload value in register RC2</li> </ul> </li> <li>Count down <ul> <li>Start counting from FFFF<sub>H</sub>, underflow at value defined in register RC2</li> <li>Reload event triggered by underflow condition <ul> <li>Reload event triggered by underflow condition</li> <li>Reload event triggered by underflow condition</li> </ul> </li> </ul></li></ul> |

| Channel<br>capture | <ul> <li>Count up only</li> <li>Start counting from 0000<sub>H</sub>, overflow at FFFF<sub>H</sub></li> <li>Reload event triggered by overflow condition</li> <li>Reload value fixed at 0000<sub>H</sub></li> <li>Capture event triggered by falling/rising edge at pin T2EX</li> <li>Captured timer value stored in register RC2</li> <li>Interrupt is generated with reload or capture event</li> </ul>                                                                                                                                                                                                                                                                             |

### Table 36Chip Identification Number (cont'd)

| Product Variant  | Chip Identification Number |         |         |  |  |

|------------------|----------------------------|---------|---------|--|--|

|                  | AA-Step                    | AB-Step | AC-Step |  |  |

| XC886LM-6RFA 3V3 | 22411522 <sub>H</sub>      | -       | -       |  |  |

| XC888LM-6RFA 3V3 | 22411523 <sub>H</sub>      | -       | -       |  |  |

| XC886CM-8RFA 3V3 | 22480502 <sub>H</sub>      | -       | -       |  |  |

| XC888CM-8RFA 3V3 | 22480503 <sub>H</sub>      | -       | -       |  |  |

| XC886C-8RFA 3V3  | 22480542 <sub>H</sub>      | -       | -       |  |  |

| XC888C-8RFA 3V3  | 22480543 <sub>H</sub>      | -       | -       |  |  |

| XC886-8RFA 3V3   | 22480562 <sub>H</sub>      | -       | -       |  |  |

| XC888-8RFA 3V3   | 22480563 <sub>H</sub>      | -       | -       |  |  |

| XC886CM-6RFA 3V3 | 22491502 <sub>H</sub>      | -       | -       |  |  |

| XC888CM-6RFA 3V3 | 22491503 <sub>H</sub>      | -       | -       |  |  |

| XC886C-6RFA 3V3  | 22491542 <sub>H</sub>      | -       | -       |  |  |

| XC888C-6RFA 3V3  | 22491543 <sub>H</sub>      | -       | -       |  |  |

| XC886-6RFA 3V3   | 22491562 <sub>H</sub>      | -       | -       |  |  |

| XC888-6RFA 3V3   | 22491563 <sub>H</sub>      | -       | -       |  |  |

| XC886CLM-8RFA 5V | 22800502 <sub>H</sub>      | -       | -       |  |  |

| XC888CLM-8RFA 5V | 22800503 <sub>H</sub>      | -       | -       |  |  |

| XC886LM-8RFA 5V  | 22800522 <sub>H</sub>      | -       | -       |  |  |

| XC888LM-8RFA 5V  | 22800523 <sub>H</sub>      | -       | -       |  |  |

| XC886CLM-6RFA 5V | 22811502 <sub>H</sub>      | -       | -       |  |  |

| XC888CLM-6RFA 5V | 22811503 <sub>H</sub>      | -       | -       |  |  |

| XC886LM-6RFA 5V  | 22811522 <sub>H</sub>      | -       | -       |  |  |

| XC888LM-6RFA 5V  | 22811523 <sub>H</sub>      | -       | -       |  |  |

| XC886CM-8RFA 5V  | 22880502 <sub>H</sub>      | -       | -       |  |  |

| XC888CM-8RFA 5V  | 22880503 <sub>H</sub>      | -       | -       |  |  |

| XC886C-8RFA 5V   | 22880542 <sub>H</sub>      | -       | -       |  |  |

| XC888C-8RFA 5V   | 22880543 <sub>H</sub>      | -       | -       |  |  |

| XC886-8RFA 5V    | 22880562 <sub>H</sub>      | -       | -       |  |  |

| XC888-8RFA 5V    | 22880563 <sub>H</sub>      | -       | -       |  |  |

| XC886CM-6RFA 5V  | 22891502 <sub>H</sub>      | -       | -       |  |  |

# 4 Electrical Parameters

**Chapter 4** provides the characteristics of the electrical parameters which are implementation-specific for the XC886/888.

### 4.1 General Parameters

The general parameters are described here to aid the users in interpreting the parameters mainly in **Section 4.2** and **Section 4.3**.

### 4.1.1 Parameter Interpretation

The parameters listed in this section represent partly the characteristics of the XC886/888 and partly its requirements on the system. To aid interpreting the parameters easily when evaluating them for a design, they are indicated by the abbreviations in the "Symbol" column:

• CC

These parameters indicate **C**ontroller **C**haracteristics, which are distinctive features of the XC886/888 and must be regarded for a system design.

• SR

These parameters indicate **S**ystem **R**equirements, which must be provided by the microcontroller system in which the XC886/888 is designed in.

### 4.1.2 Absolute Maximum Rating

Maximum ratings are the extreme limits to which the XC886/888 can be subjected to without permanent damage.

| Parameter                                                    | Symbol            | Limit Values |                                        | Unit | Notes                               |

|--------------------------------------------------------------|-------------------|--------------|----------------------------------------|------|-------------------------------------|

|                                                              |                   | min.         | max.                                   |      |                                     |

| Ambient temperature                                          | T <sub>A</sub>    | -40          | 125                                    | °C   | under bias                          |

| Storage temperature                                          | T <sub>ST</sub>   | -65          | 150                                    | °C   | 1)                                  |

| Junction temperature                                         | T <sub>J</sub>    | -40          | 150                                    | °C   | under bias <sup>1)</sup>            |

| Voltage on power supply pin with respect to $V_{\rm SS}$     | V <sub>DDP</sub>  | -0.5         | 6                                      | V    | 1)                                  |

| Voltage on any pin with respect to $V_{\rm SS}$              | V <sub>IN</sub>   | -0.5         | V <sub>DDP</sub> +<br>0.5 or<br>max. 6 | V    | whichever is<br>lower <sup>1)</sup> |

| Input current on any pin during overload condition           | I <sub>IN</sub>   | -10          | 10                                     | mA   | 1)                                  |

| Absolute sum of all input currents during overload condition | $\Sigma  I_{IN} $ | -            | 50                                     | mA   | 1)                                  |

| Table 4-1 | Absolute Maximum Rating Parameters |

|-----------|------------------------------------|

|-----------|------------------------------------|

1) Not subjected to production test, verified by design/characterization.

Note: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. During absolute maximum rating overload conditions ( $V_{IN} > V_{DDP}$  or  $V_{IN} < V_{SS}$ ) the voltage on  $V_{DDP}$  pin with respect to ground ( $V_{SS}$ ) must not exceed the values defined by the absolute maximum ratings.

| Parameter                   | Symbol           | Limit Values       |                    | Unit | <b>Test Condition</b>                 |  |

|-----------------------------|------------------|--------------------|--------------------|------|---------------------------------------|--|

|                             |                  | typ. <sup>1)</sup> | max. <sup>2)</sup> |      |                                       |  |

| V <sub>DDP</sub> = 5V Range |                  |                    |                    |      | •                                     |  |

| Power-Down Mode             | I <sub>PDP</sub> | 1                  | 10                 | μA   | $T_{\rm A}$ = + 25 °C <sup>3)4)</sup> |  |

|                             |                  | -                  | 30                 | μA   | $T_{\rm A}$ = + 85 °C <sup>4)5)</sup> |  |

Power Down Current (Operating Conditions apply: U able 10 - E V (man ma)

1) The typical  $I_{PDP}$  values are measured at  $V_{DDP}$  = 5.0 V.

2) The maximum  $I_{PDP}$  values are measured at  $V_{DDP}$  = 5.5 V.

3)  $I_{PDP}$  has a maximum value of 200  $\mu$ A at  $T_A$  = + 125 °C.

4)  $I_{PDP}$  is measured with: RESET =  $V_{DDP}$ ,  $V_{AGND}$ =  $V_{SS}$ , RXD/INT0 =  $V_{DDP}$ ; rest of the ports are programmed to be input with either internal pull devices enabled or driven externally to ensure no floating inputs.

5) Not subjected to production test, verified by design/characterization.

### 4.3 AC Parameters

The electrical characteristics of the AC Parameters are detailed in this section.

### 4.3.1 Testing Waveforms

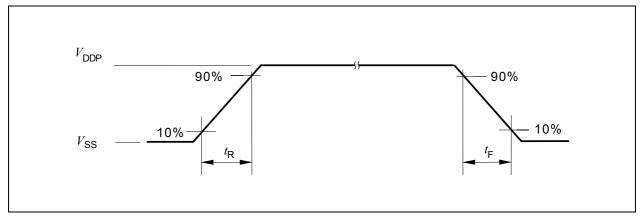

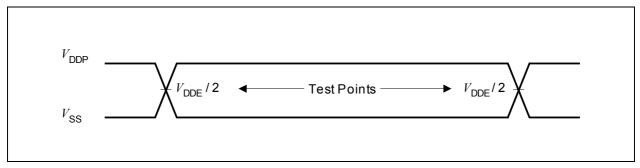

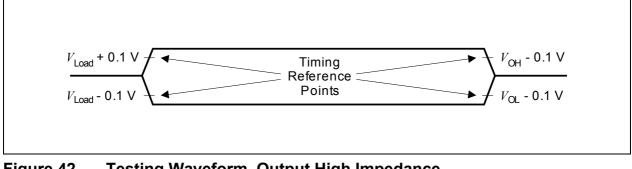

The testing waveforms for rise/fall time, output delay and output high impedance are shown in **Figure 40**, **Figure 41** and **Figure 42**.

Figure 40 Rise/Fall Time Parameters

Figure 41 Testing Waveform, Output Delay

Figure 42 Testing Waveform, Output High Impedance

# 4.3.5 External Clock Drive XTAL1

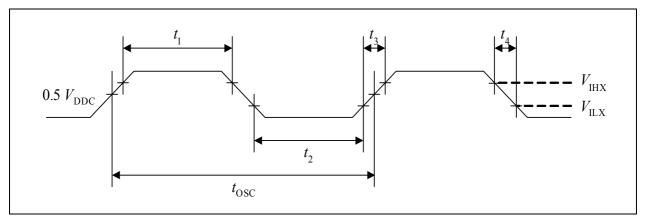

**Table 48** shows the parameters that define the external clock supply for XC886/888. These timing parameters are based on the direct XTAL1 drive of clock input signals. They are not applicable if an external crystal or ceramic resonator is considered.

| Parameter         | Symbol                |    | Limit Values |      | Unit | <b>Test Conditions</b> |

|-------------------|-----------------------|----|--------------|------|------|------------------------|

|                   |                       |    | Min.         | Max. |      |                        |

| Oscillator period | t <sub>osc</sub>      | SR | 83.3         | 250  | ns   | 1)2)                   |

| High time         | <i>t</i> <sub>1</sub> | SR | 25           | -    | ns   | 2)3)                   |

| Low time          | <i>t</i> <sub>2</sub> | SR | 25           | -    | ns   | 2)3)                   |

| Rise time         | t <sub>3</sub>        | SR | -            | 20   | ns   | 2)3)                   |

| Fall time         | $t_4$                 | SR | -            | 20   | ns   | 2)3)                   |

Table 48

External Clock Drive Characteristics (Operating Conditions apply)

1) The clock input signals with 45-55% duty cycle are used.

2) Not all parameters are 100% tested, but are verified by design/characterization and test correlation.

3) The clock input signal must reach the defined levels  $V_{\rm ILX}$  and  $V_{\rm IHX}$ .

Figure 45 External Clock Drive XTAL1